Optimization of Low-Voltage p-GaN Gate HEMTs for High-Efficiency Secondary Power Conversion

Abstract

1. Introduction

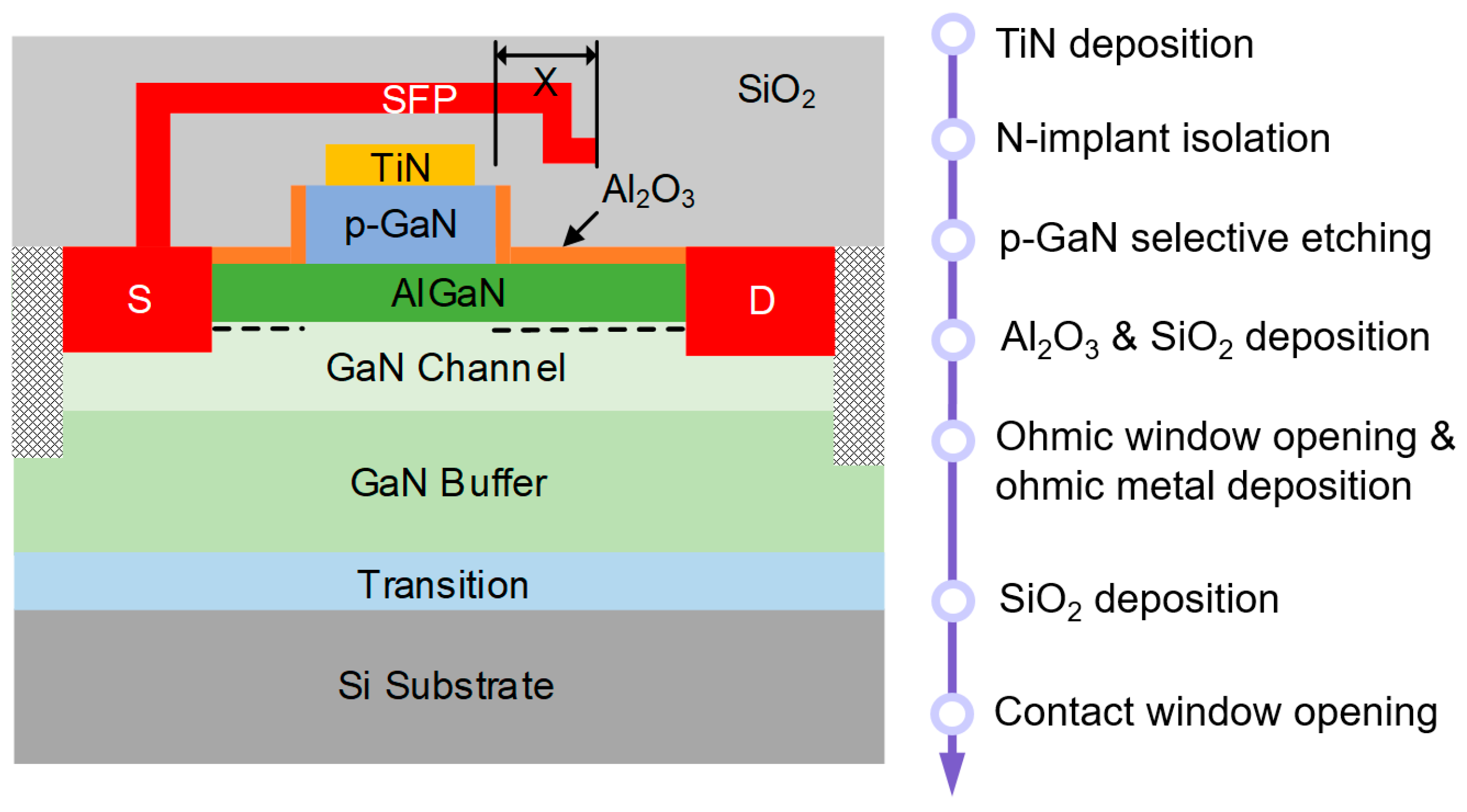

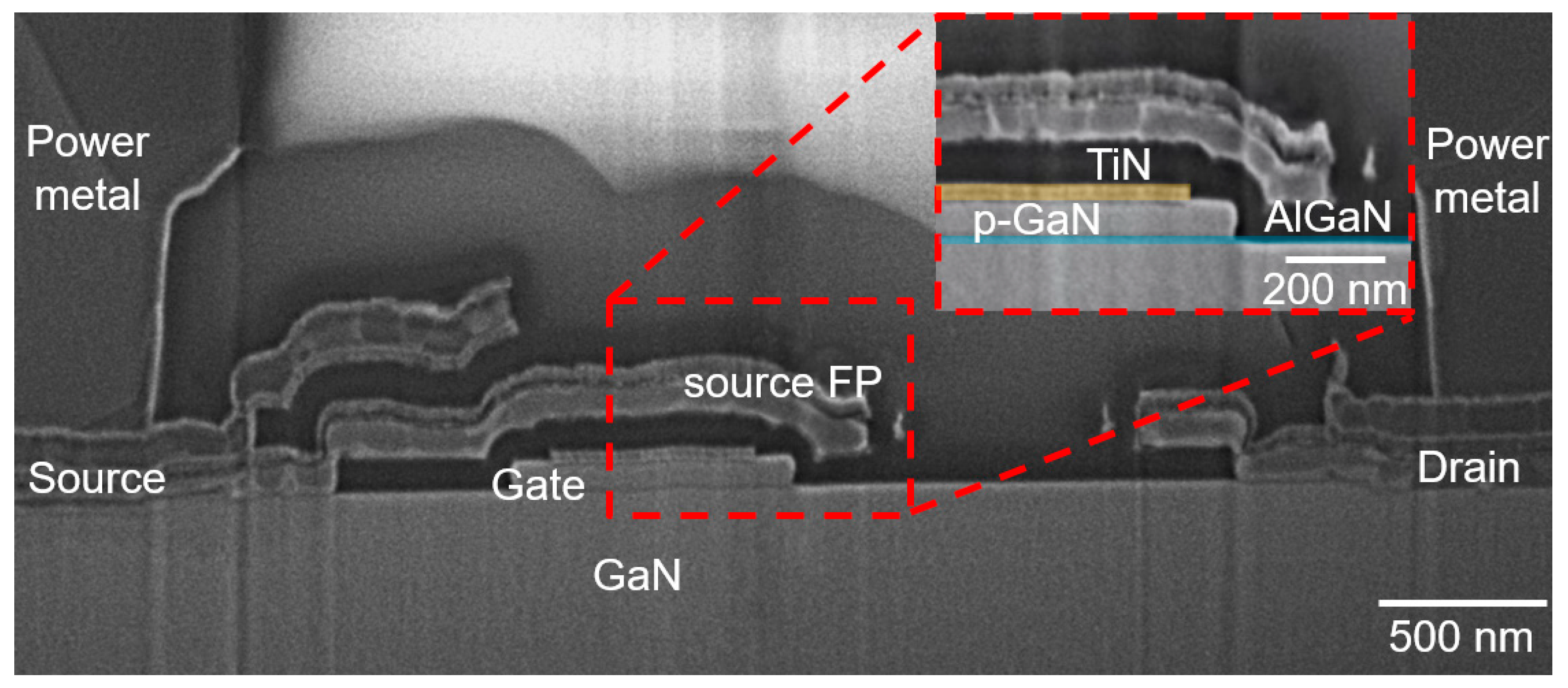

2. Materials and Methods

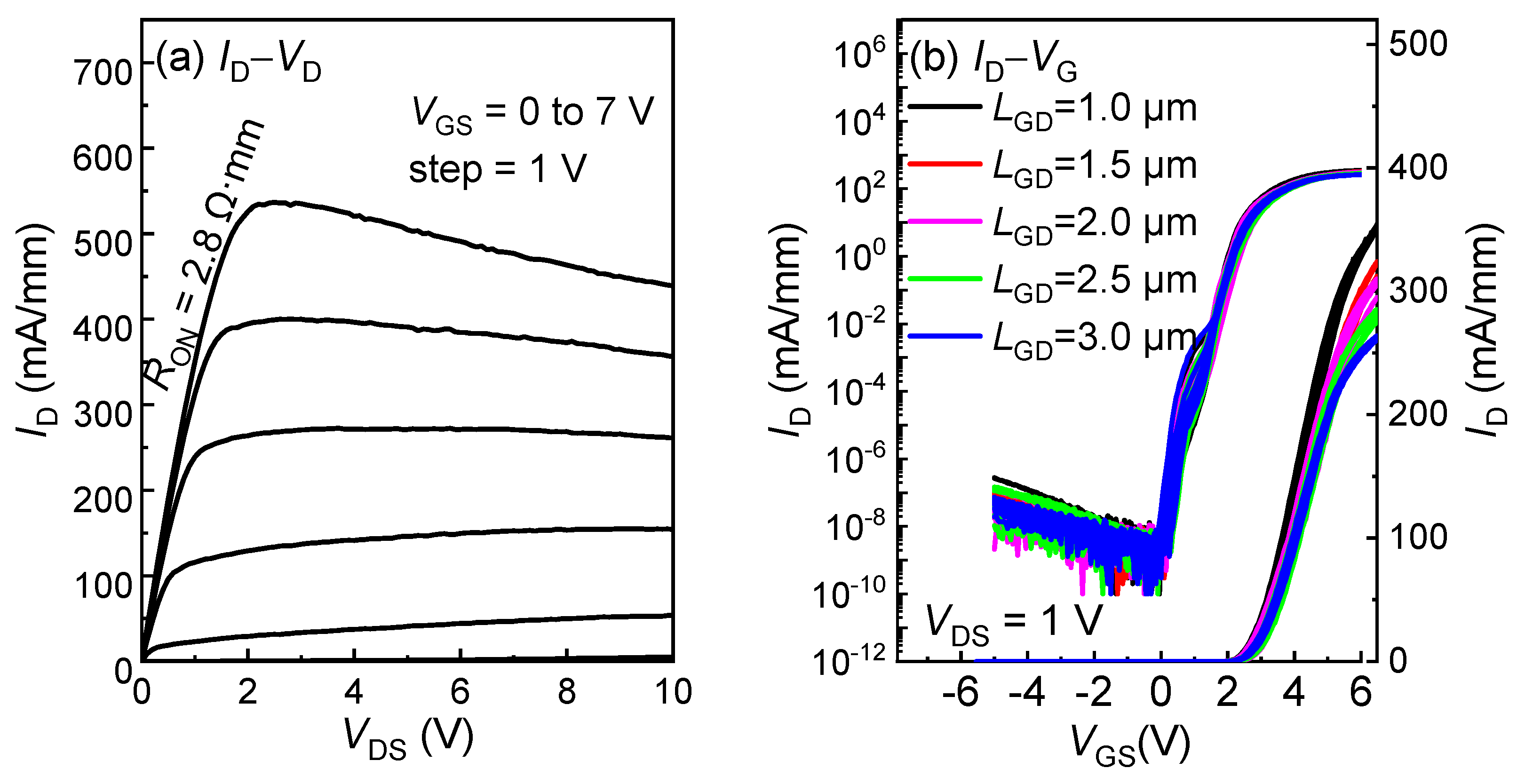

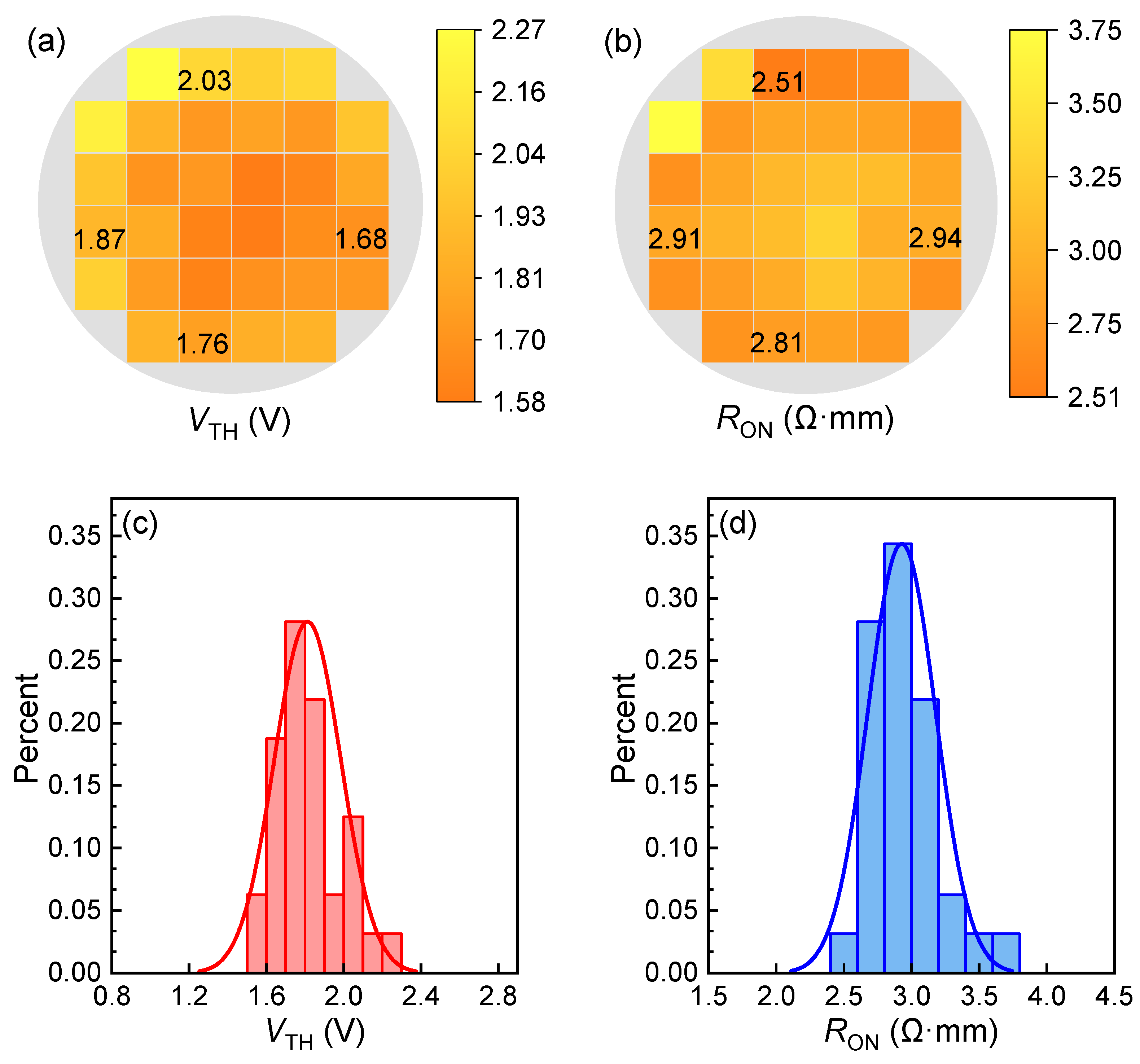

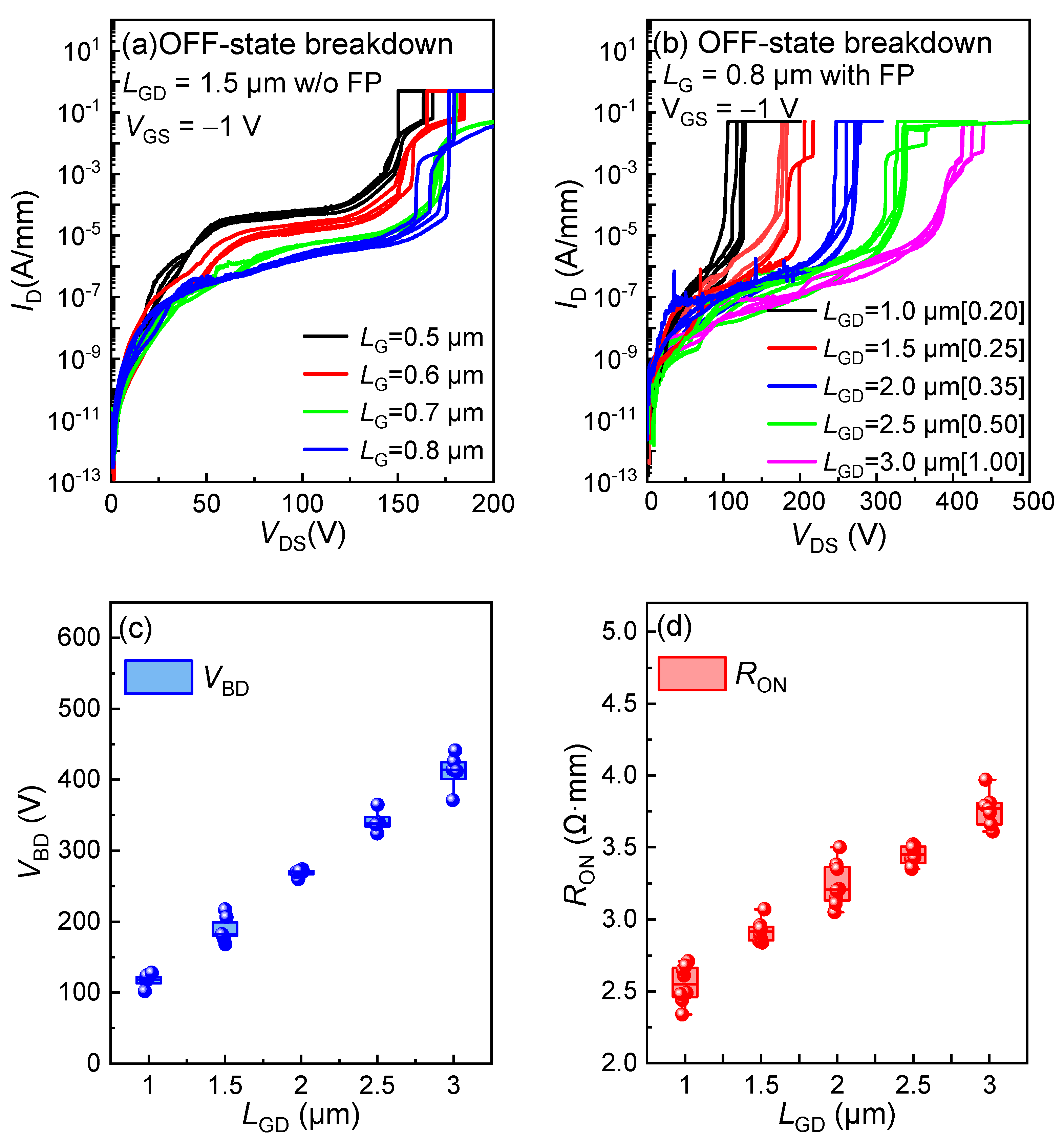

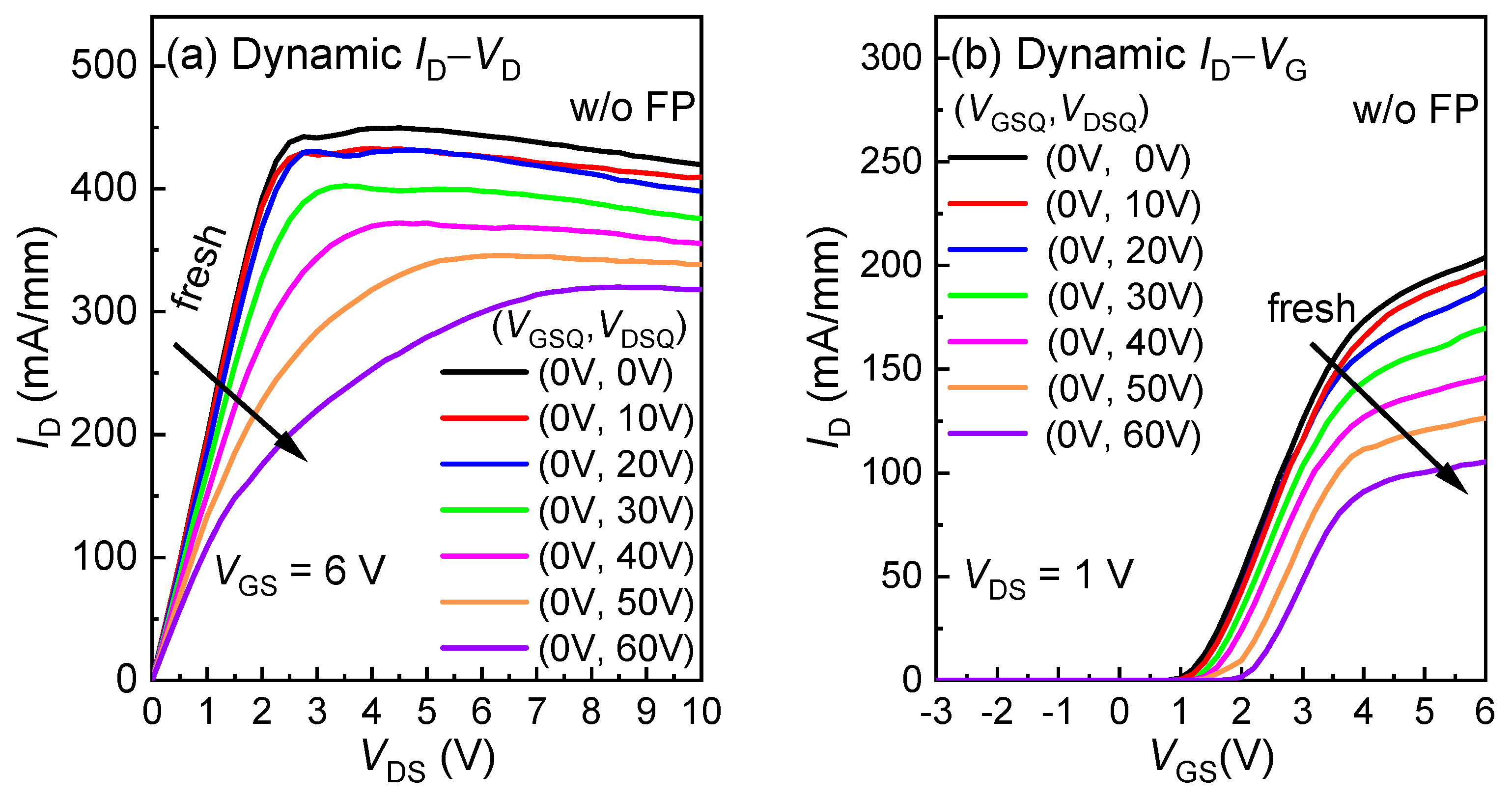

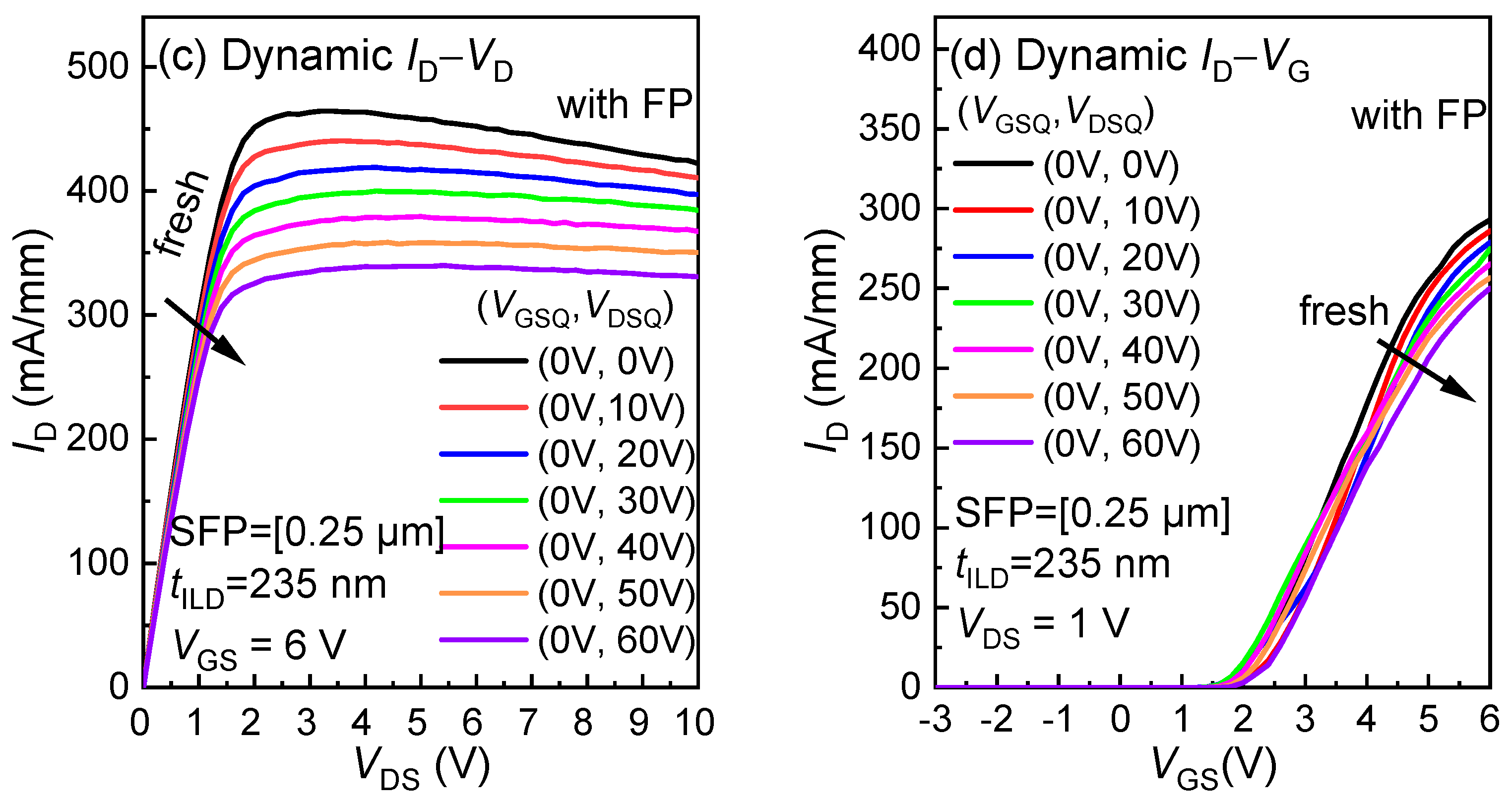

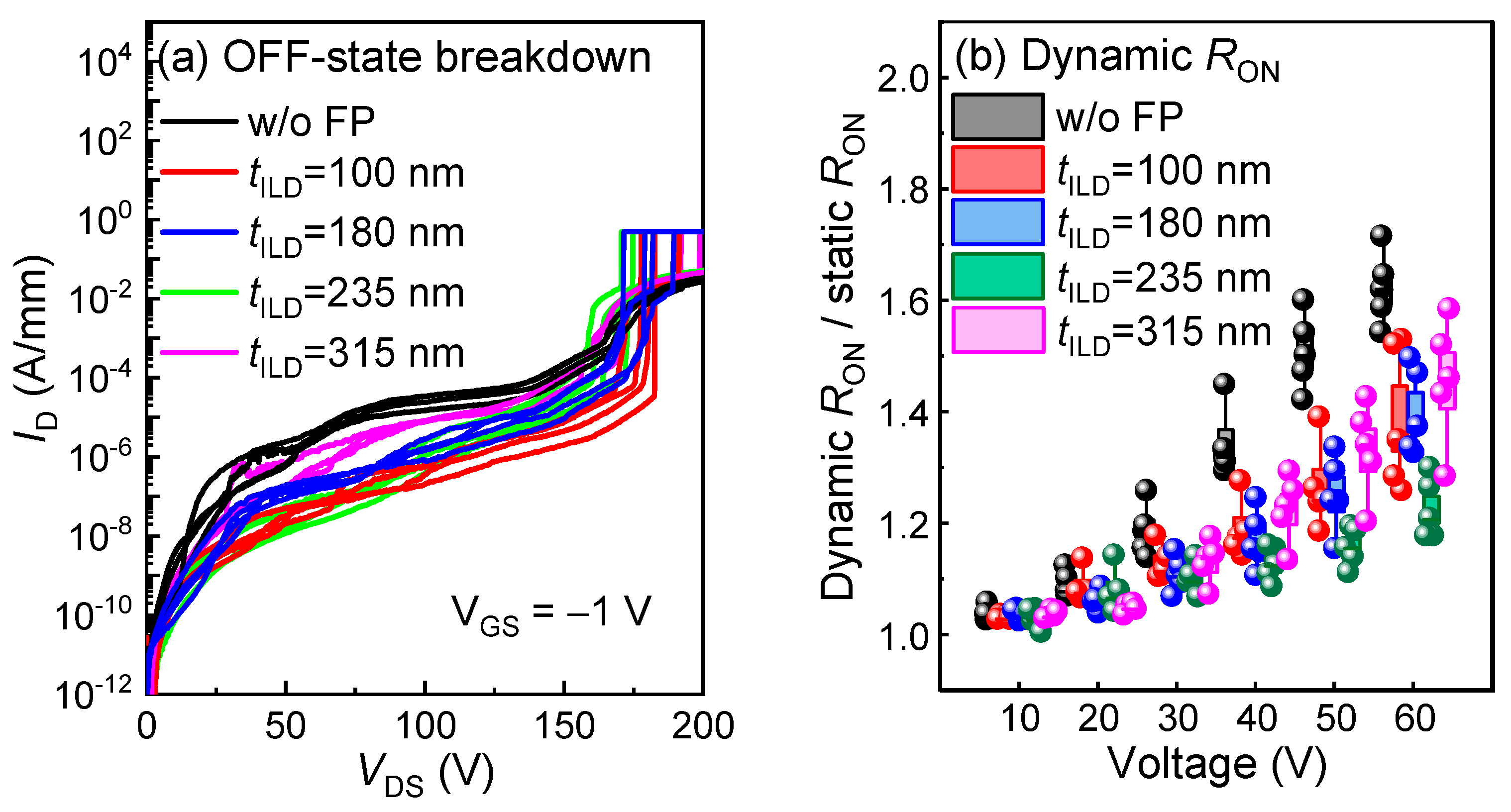

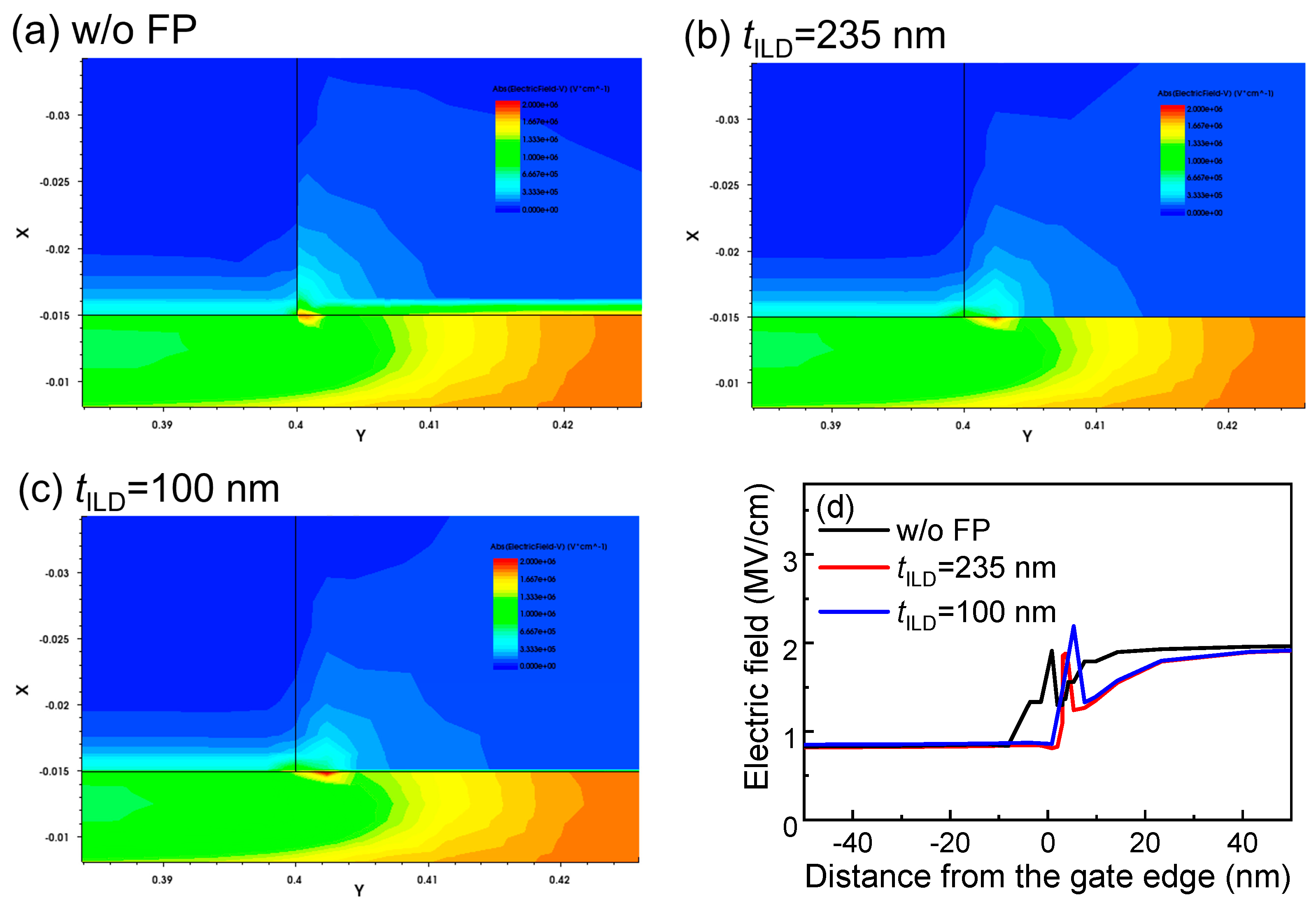

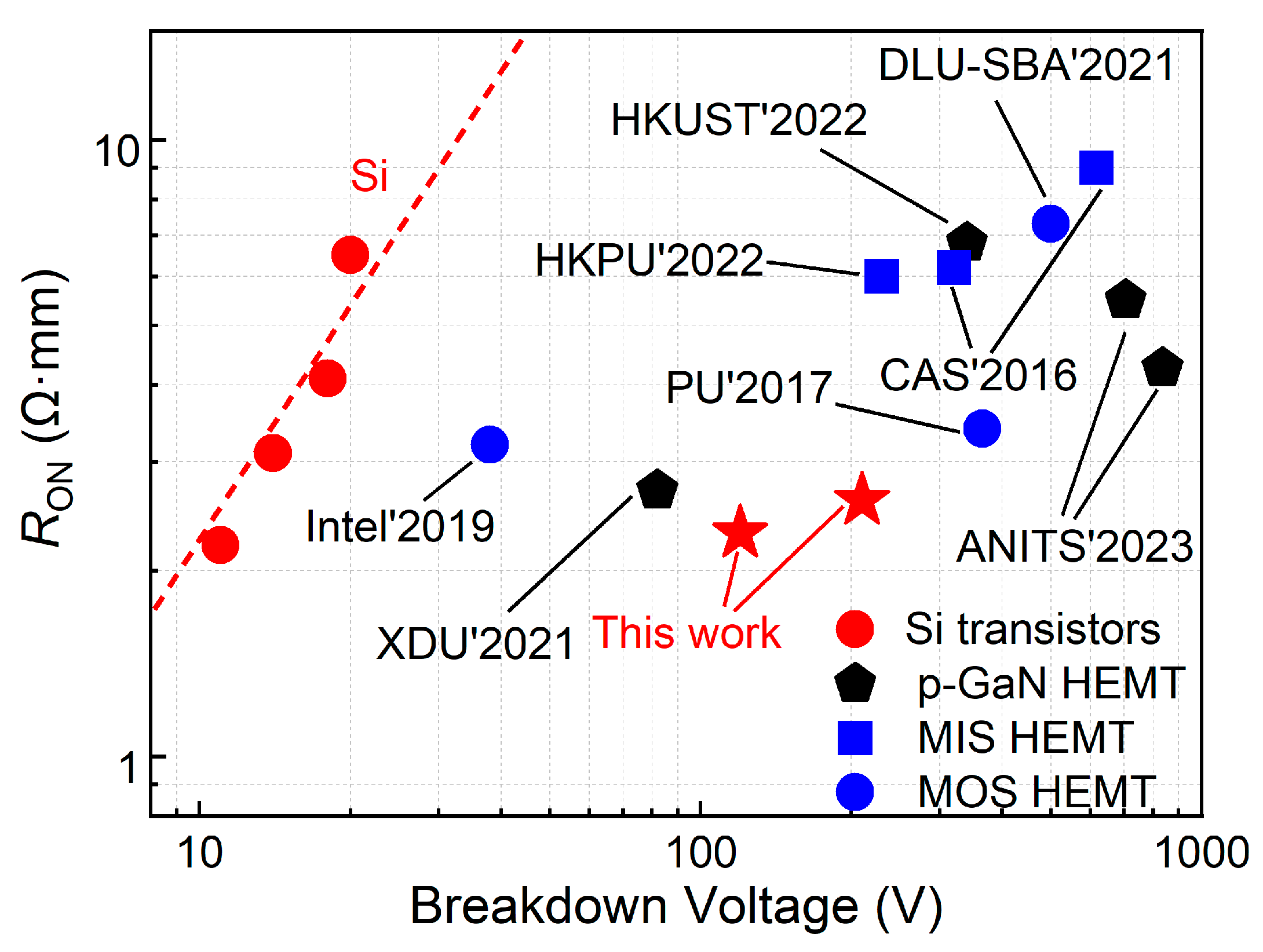

3. Results

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Musumeci, S.; Mandrile, F.; Barba, V.; Palma, M. Low-voltage GaN FETs in motor control application; issues and advantages: A review. Energies 2021, 14, 6378. [Google Scholar] [CrossRef]

- Han, T.; Peng, X.; Zhang, W.; Wang, T.; Yang, L.; Zhao, P. Effects of physical parameters of graded AlGaN buffer on DC characteristic and short-channel effects in AlInN/GaN high-electron mobility transistors. Microelectron. J. 2023, 139, 105881. [Google Scholar] [CrossRef]

- Xin, Y.; Chen, W.; Sun, R.; Deng, X.; Li, Z.; Zhang, B. Barrier Lowering-Induced Capacitance Increase of Short-Channel Power p-GaN HEMTs at High Temperature. IEEE Trans. Electron. Devices 2022, 69, 1176–1180. [Google Scholar] [CrossRef]

- Then, H.W.; Koirala, P.; Varghese, L.; Zubair, A.; Bader, S.; Beumer, M.; Vora, H.; Golani, P.; Peck, J.; Hoff, T.; et al. 30nm Channel-Length Enhancement-Mode GaN MOSHEMT Transistors on a 300mm GaN-on-TRSOI Engineered Substrate. In Proceedings of the 2024 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2024; pp. 1–4. [Google Scholar]

- Posthuma, N.; You, S.; Liang, H.; Ronchi, N.; Kang, X.; Wellekens, D.; Saripalli, Y.; Decoutere, S. Impact of Mg out-diffusion and activation on the p-GaN gate HEMT device performance. In Proceedings of the 2016 28th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Prague, Czech Republic, 12–16 June 2016; pp. 95–98. [Google Scholar]

- Kozak, J.P.; Zhang, R.; Porter, M.; Song, Q.; Liu, J.; Wang, B.; Wang, R.; Saito, W.; Zhang, Y. Stability, Reliability, and Robustness of GaN Power Devices: A Review. IEEE Trans. Power Electron. 2023, 38, 8442–8471. [Google Scholar] [CrossRef]

- Tang, S.; Bakeroot, B.; Huang, Z.; Chen, S.; Lin, W.; Lo, T.; Borga, M.; Wellekens, D.; Posthuma, N.; Decoutere, S.; et al. Using gate leakage conduction to understand positive gate bias induced threshold voltage shift in p-GaN gate HEMTs. IEEE Trans. Electron Devices 2023, 70, 449–453. [Google Scholar] [CrossRef]

- Wei, Y.-T.; Chou, H.-C.; Wu, Y.-H.; Yang, F.; Lee, C.-H. Demonstration of Schottky barrier diode integrated in 200 V power p-GaN HEMTs technology with robust stability. IEEE J. Electron Devices Soc. 2016, 4, 37–41. [Google Scholar]

- Huang, Y.-C.; Chen, G.-R.; Chen, K.-M. 200 V enhancement-mode p-GaN HEMTs fabricated on 200 mm GaN-on-SOI with trench isolation for monolithic integration. IEEE J. Electron Devices Soc. 2017, 5, 10–16. [Google Scholar]

- Wong, K.; Hao, R.; Chou, A.; Zou, Y.; Shen, J.; Li, S.; Yang, C.; Zhang, A.; Hu, T.; Chen, F. Comprehensive GaN-on-Si power device platform: Epitaxy, device, reliability and application. Semicond. Sci. Technol. 2021, 36, 064001. [Google Scholar] [CrossRef]

- Ashourloo, M.; Zaman, M.S.; Nasr, M.; Trescases, O. Opportunities for leveraging low-voltage GaN devices in modular multi-level converters for electric-vehicle charging applications. In Proceedings of the 2018 International Power Electronics Conference, Niigata, Japan, 20–24 May 2018; pp. 2380–2385. [Google Scholar]

- Shen, J.; Jing, L.; Qiu, J. High-frequency full-bridge 48V DC-5V DC LLC resonant converter with AlGaN/GaN HEMTs. In Proceedings of the 2023 5th International Conference on Electrical Engineering and Control Technologies (CEECT), Chengdu, China, 15–17 December 2023; pp. 338–342. [Google Scholar]

- Wu, S.; Ran, Z.; Tong, Z.; Liu, T.; Lu, Y. A monolithic integrated E-mode GaN 48V-to-1V DC-DC buck converter with PWM control. In Proceedings of the 2023 IEEE International Conference on Integrated Circuits, Technologies and Applications (ICTA), Hefei, China, 27–29 October 2023; pp. 130–131. [Google Scholar]

- EPC2100—Enhancement-Mode GaN Power Transistor Half-Bridge. Available online: https://epc-co.com/epc/products/gan-fets-and-ics/epc2100 (accessed on 23 April 2021).

- Wang, T.; Jiang, L.; Zhang, M.; Jiang, Y. A novel physics-based approach to analyze and model E-mode p-GaN power HEMTs. IEEE Trans. Power Electron. 2019, 34, 1524–1534. [Google Scholar]

- Zhou, Y.; Zhu, J.; Mi, M.; Zhang, M.; Wang, P.; Han, Y.; Wu, S.; Liu, J.; Zhu, Q.; Chen, Y. Analysis of low voltage RF power capability on AlGaN/GaN and InAlN/GaN HEMTs for terminal applications. IEEE J. Electron Devices Soc. 2021, 9, 756–762. [Google Scholar] [CrossRef]

- Zanoni, E.; Santi, C.D.; Gao, Z.; Buffolo, M.; Fornasier, M.; Saro, M.; Pieri, F.D. Microwave and millimeter-wave GaN HEMTs: Impact of epitaxial structure on short-channel effects, electron trapping, and reliability. IEEE Trans. Electron Devices 2024, 71, 1396–1407. [Google Scholar] [CrossRef]

- Hu, Y.; Hernández-Gutiérre, C.; Solís-Cisneros, H.; Santana, G.; Kudriatsev, Y.; Camas-Anzueto, J.; López-López, M. Blue luminescence origin and Mg acceptor saturation in highly doped zinc-blende GaN with Mg. J. Alloys Compd. 2022, 897, 163133. [Google Scholar] [CrossRef]

- Zhang, L.; Zheng, Z.; Yang, S.; Song, W.; He, J.; Chen, K.J. p-GaN gate HEMT with surface reinforcement for enhanced gate reliability. IEEE Electron Device Lett. 2020, 42, 22–25. [Google Scholar] [CrossRef]

- Li, X.; Wang, J.; Zhang, J.; Han, Z.; You, S.; Chen, L.; Wang, L.; Li, Z.; Yang, W.; Chang, J. 1700 V high-performance GaN HEMTs on 6-inch sapphire with 1.5 μm thin buffer. IEEE Electron Device Lett. 2024, 45, 84–87. [Google Scholar] [CrossRef]

- Gupta, S.D.; Joshi, V.; Chaudhuri, R.R.; Shrivastava, M. Part I: Physical insights into dynamic R_ON behavior and a unique time-dependent critical stress voltage in AlGaN/GaN HEMTs. IEEE Trans. Electron Devices 2021, 68, 5720–5727. [Google Scholar] [CrossRef]

- Han, Z.; Li, X.; Ji, J.; Chen, L.; Wang, L.; Cheng, Z.; Yang, W.; You, S.; Li, Z.; Hao, Y. p-GaN gate HEMTs on 6-inch sapphire by CMOS-compatible process: A promising game changer for power electronics. IEEE Electron Device Lett. 2024, 45, 1257–1260. [Google Scholar] [CrossRef]

- Gao, R.; Shi, Y.; He, Z.; Chen, Y.; En, Y.; Huang, Y.; Ji, Z.; Zhang, J.; Zhang, W.; Zheng, X.; et al. A fast extraction method of energy distribution of border traps in AlGaN/GaN MIS-HEMT. IEEE J. Electron Devices Soc. 2020, 8, 905–910. [Google Scholar] [CrossRef]

- Tang, X.; Li, B.; Moghadam, H.A.; Tanner, P.; Han, J.; Dimitrijev, S. Mechanism of threshold voltage shift in p-GaN gate AlGaN/GaN transistors. IEEE Electron Device Lett. 2018, 39, 1145–1148. [Google Scholar] [CrossRef]

- Wang, Y.; Hua, M.; Tang, G.; Lei, J.; Zheng, Z.; Wei, J.; Chen, K. Dynamic OFF-State Current (Dynamic IOFF) in p-GaN Gate HEMTs With an Ohmic Gate Contact. IEEE Electron Device Lett. 2018, 39, 1366–1369. [Google Scholar] [CrossRef]

- Wang, Y.; Lyu, G.; Wei, J.; Zheng, Z.; He, J.; Lei, J.; Chen, K.J. Characterization of static and dynamic behavior of 1200 V normally off GaN/SiC cascode devices. IEEE Trans. Ind. Electron. 2019, 67, 10284–10294. [Google Scholar] [CrossRef]

- Song, J.; Wang, M.; Wei, J.; Fan, Z.; Zhang, J.; Yang, H.; Wang, P.; Xie, B.; Li, C.; Yuan, L. Effect of source electrostatic interaction on the off-state leakage current of p-GaN gate HEMTs. IEEE Electron Device Lett. 2024, 45, 1728–1731. [Google Scholar] [CrossRef]

- He, J.; Wang, Q.; Zhou, G.; Li, W.; Jiang, Y.; Qiao, Z.; Tang, C.; Li, G.; Yu, H. Normally-OFF AlGaN/GaN MIS-HEMTs With Low RON and Vth Hysteresis by Functioning In-situ SiNx in Regrowth Process. IEEE Electron Device Lett. 2022, 43, 529–532. [Google Scholar] [CrossRef]

- Liao, H.; Zheng, Z.; Chen, T.; Zhang, L.; Cheng, Y.; Feng, S.; Ng, Y.; Chen, L.; Yuan, L.; Chen, K. Normally-OFF p-GaN Gate Double-Channel HEMT With Suppressed Hot-Electron-Induced Dynamic ON-Resistance Degradation. IEEE Electron Device Lett. 2022, 43, 1424–1427. [Google Scholar] [CrossRef]

- Zhou, G.; Zeng, F.; Jiang, Y.; Wang, Q.; Jiang, L.; Xia, G.; Yu, H. Determination of the Gate Breakdown Mechanisms in p-GaN Gate HEMTs by Multiple-Gate-Sweep Measurements. IEEE Trans. Electron Devices 2021, 68, 1518–1523. [Google Scholar] [CrossRef]

- Revathy, A.; Vijaya Kumar, J.; Murugapandiyan, P.; Wasim, M.; Nirmala Devi, K.; Ramkumar, N. Design and analysis of normally-off GaN-HEMT using β-Ga2O3 buffer for low-loss power converter applications. Micro Nanostructures 2023, 182, 207643. [Google Scholar] [CrossRef]

- Then, H.W.; Dasgupta, S.; Radosavljevic, M.; Agababov, P.; Ban, I.; Bristol, R.; Chandhok, M.; Chouksey, S.; Holybee, B.; Huang, C.Y.; et al. 3D heterogeneous integration of high performance high-K metal gate GaN NMOS and Si PMOS transistors on 300 mm high-resistivity Si substrate for energy-efficient and compact power delivery, RF (5G and beyond) and SoC applications. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 17.3.1–17.3.4. [Google Scholar]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhai, L.; Li, X.; Ji, J.; Yu, L.; Chen, L.; Chen, Y.; Xia, H.; Han, Z.; Wang, J.; Jiang, X.; et al. Optimization of Low-Voltage p-GaN Gate HEMTs for High-Efficiency Secondary Power Conversion. Micromachines 2025, 16, 556. https://doi.org/10.3390/mi16050556

Zhai L, Li X, Ji J, Yu L, Chen L, Chen Y, Xia H, Han Z, Wang J, Jiang X, et al. Optimization of Low-Voltage p-GaN Gate HEMTs for High-Efficiency Secondary Power Conversion. Micromachines. 2025; 16(5):556. https://doi.org/10.3390/mi16050556

Chicago/Turabian StyleZhai, Lili, Xiangdong Li, Jian Ji, Lu Yu, Liang Chen, Yaoming Chen, Haonan Xia, Zhanfei Han, Junbo Wang, Xi Jiang, and et al. 2025. "Optimization of Low-Voltage p-GaN Gate HEMTs for High-Efficiency Secondary Power Conversion" Micromachines 16, no. 5: 556. https://doi.org/10.3390/mi16050556

APA StyleZhai, L., Li, X., Ji, J., Yu, L., Chen, L., Chen, Y., Xia, H., Han, Z., Wang, J., Jiang, X., Yuan, S., Zhang, T., Hao, Y., & Zhang, J. (2025). Optimization of Low-Voltage p-GaN Gate HEMTs for High-Efficiency Secondary Power Conversion. Micromachines, 16(5), 556. https://doi.org/10.3390/mi16050556