Abstract

A Q-enhanced notch filter for interference-rejection LNAs is proposed in this brief. The active capacitance is introduced into the notch filter to improve the quality factor by the negative resistance effect. The designed notch filter achieves excellent performance with a narrow attenuation bandwidth from 5.75 GHz to 5.95 GHz, which can be applied to suppress interference from the IEEE 802.11a. To validate the feasibility of the proposed trap filter in both GaAs process technology and principle, a 3–15 GHz ultra-wideband low-noise amplifier was designed and fabricated using a 0.15-micron gallium arsenide pseudomorphs field-effect transistor process. The frequency-dependent feedback loops are employed between gate and drain stages for wideband input matching and gain flatness. The notch filter is inserted between two stages of the LNA. The measurement results show that the interference-rejection LNA achieves a maximum gain of 24.5 dB and a minimum noise figure of 1.8 dB in the operating band. The notch filter has a maximum interference-rejection ratio of 35.2 dB at 5.8 GHz with almost no effect on the desired gain of the LNA. The LNA has a power consumption of 168 mW, including the notch filter with a size of 1.93 × 0.72 mm2.

1. Introduction

UWB systems, which are announced by the Federal Communications Commission in the 3.1–10.6 GHz [1], have been widely used in modern wireless communications due to low power level, high data-rate transmission (up to 480 Mb/s), and UWB standards for short-range connectivity [2,3]. However, the power spectral density of UWB signals is limited to −41.3 dBm/MHz, which makes it particularly susceptible to interference from some high-power narrowband systems in the band [4,5]. For instance, ranging from 5.7 GHz to 5.85 GHz, the interference sources from the wireless local area network (WLAN) IEEE 802.11a [6] are more than 60 dB higher than the received UWB signal power, resulting in desensitization of the received link [7]. Therefore, to prevent received UWB signals from such detrimental effects, the frequencies of narrowband systems need to be avoided [8].

The interference rejection can be effectively achieved by inserting an off-chip notch filter in front of the LNA, but it will occupy an additional area. Although the integration of notch filters in LNAs can overcome this problem, the low-quality factors (Qs) of on-chip spiral inductors are the major obstacle to achieving high-performance notch filters [9].

There have been many studies reported on the interference-rejection LNA (IR-LNA) in the past decade [10,11,12,13,14,15,16,17]. In [10,11,12], passive LC notch filters are introduced into the LNAs to reject out-of-band interference. However, these filters are inappropriate for UWB LNAs since the lower Qs of notch filters will worsen the in-band gain. A tunable on-chip synthesized notch filter is designed in [13] based on a balanced amplifier idea. The filter has a sharp notch and an excellent interference-rejection ratio (IRR). Moreover, utilizing the negative resistance effect of transistors, the LNA integrated with a high Q notch filter is realized in [14], which achieves the in-band interference rejection at 5.2 GHz with a slight deterioration in the desired gain. In [15], the passive inductor in the conventional dual resonant notch filter is replaced by active circuits; simultaneously achieving the out-of-band interference rejection of LNA at both high and low frequencies is achieved. The active third-order notch filter is designed in [16], which provides an additional pole to compensate for the desired band gain. In [17], the feedback technique is applied to the active notch filter to enhance the Q and decrease the power consumption. These active notch filters both utilize the negative resistance effect of the transistors to enhance the Q, thus avoiding deterioration of the desired gain.

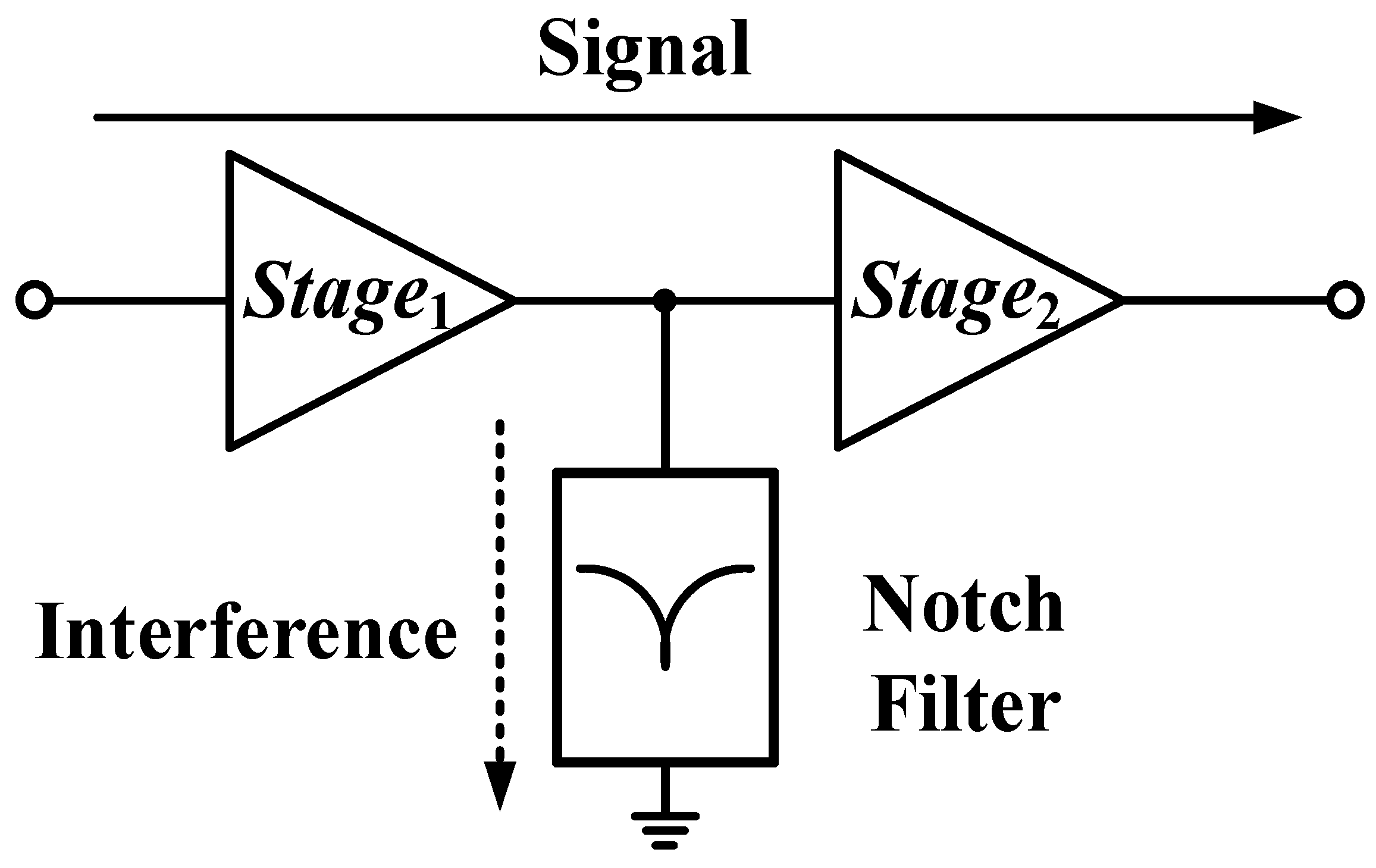

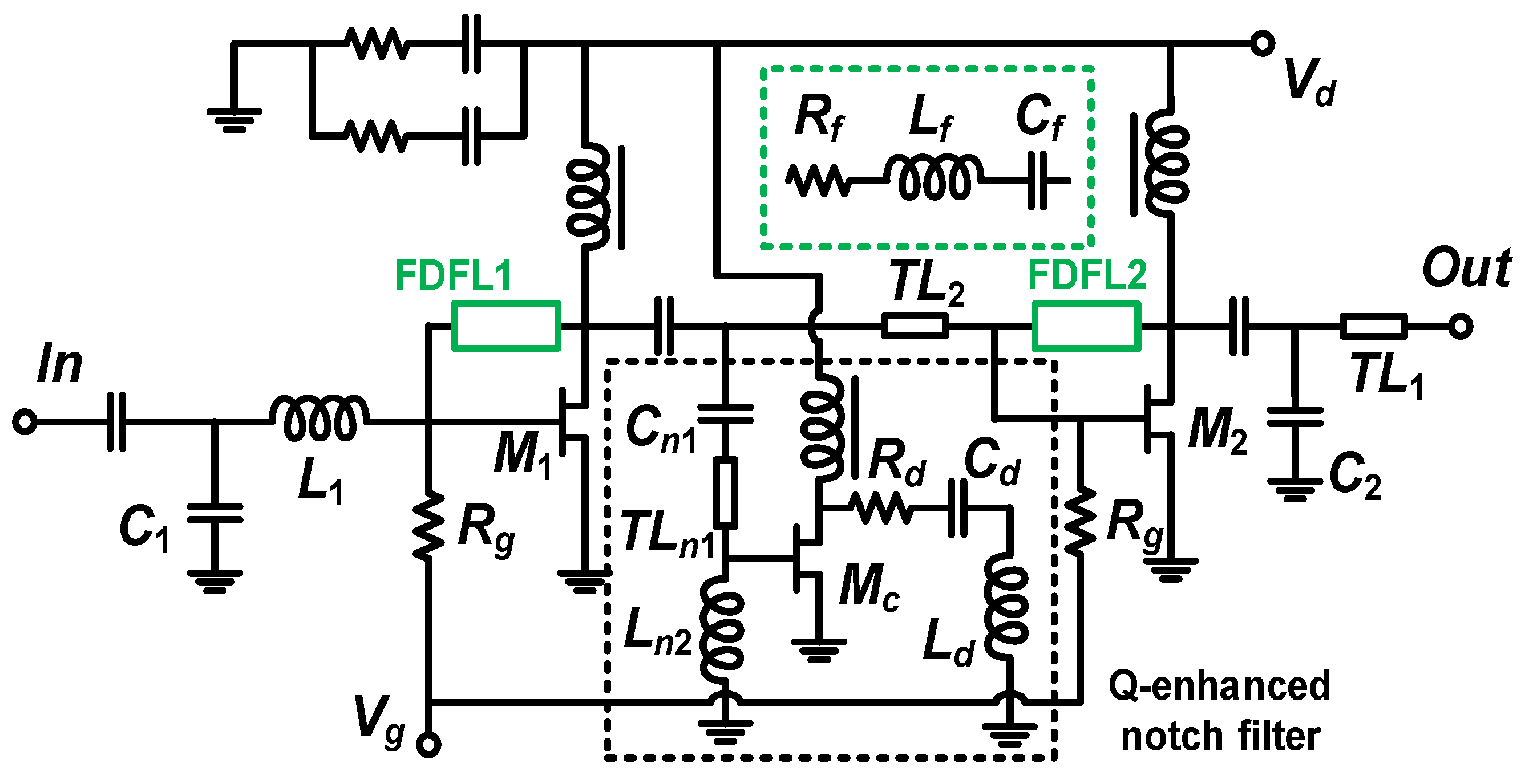

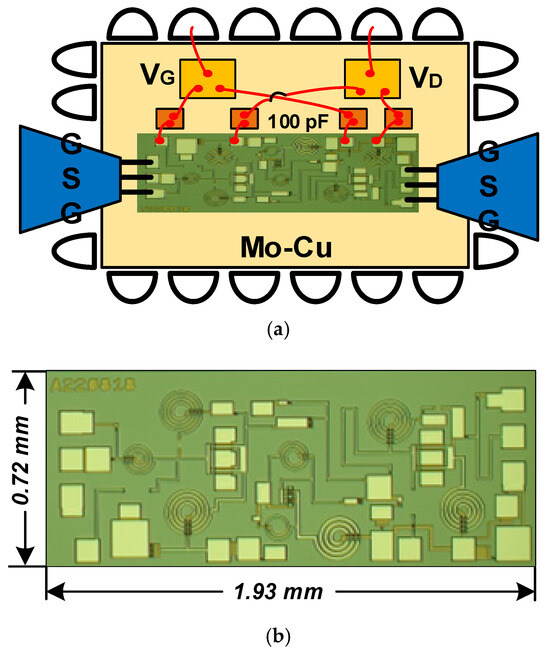

In this brief, an IR-LNA integrated with an on-chip notch filter is designed and fabricated in a 0.15-μm GaAs process, as shown in Figure 1. Thereinto, the active capacitance is introduced into the notch filter to enhance the Q through the negative resistance effect. The designed active notch filter exhibits an IRR of 35.2 dB at 5.8 GHz with little deterioration of the desired gain. This excellent performance makes this notch filter suitable for IR-LNA designs.

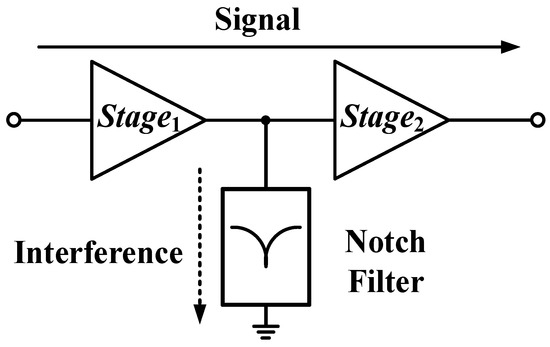

Figure 1.

The topology diagram of the IR-LNA with Q-enhanced notch filters.

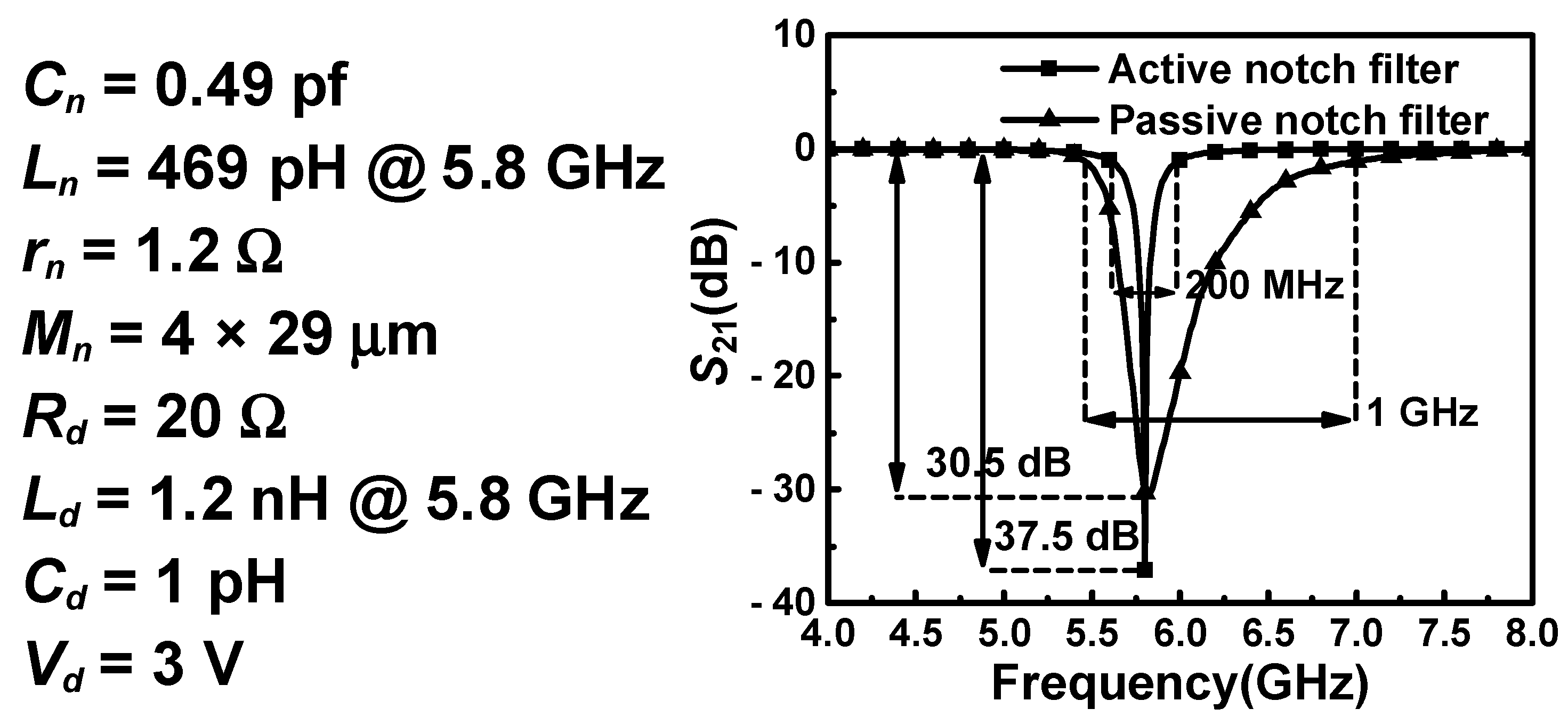

2. Design of the Q-Enhanced Notch Filter

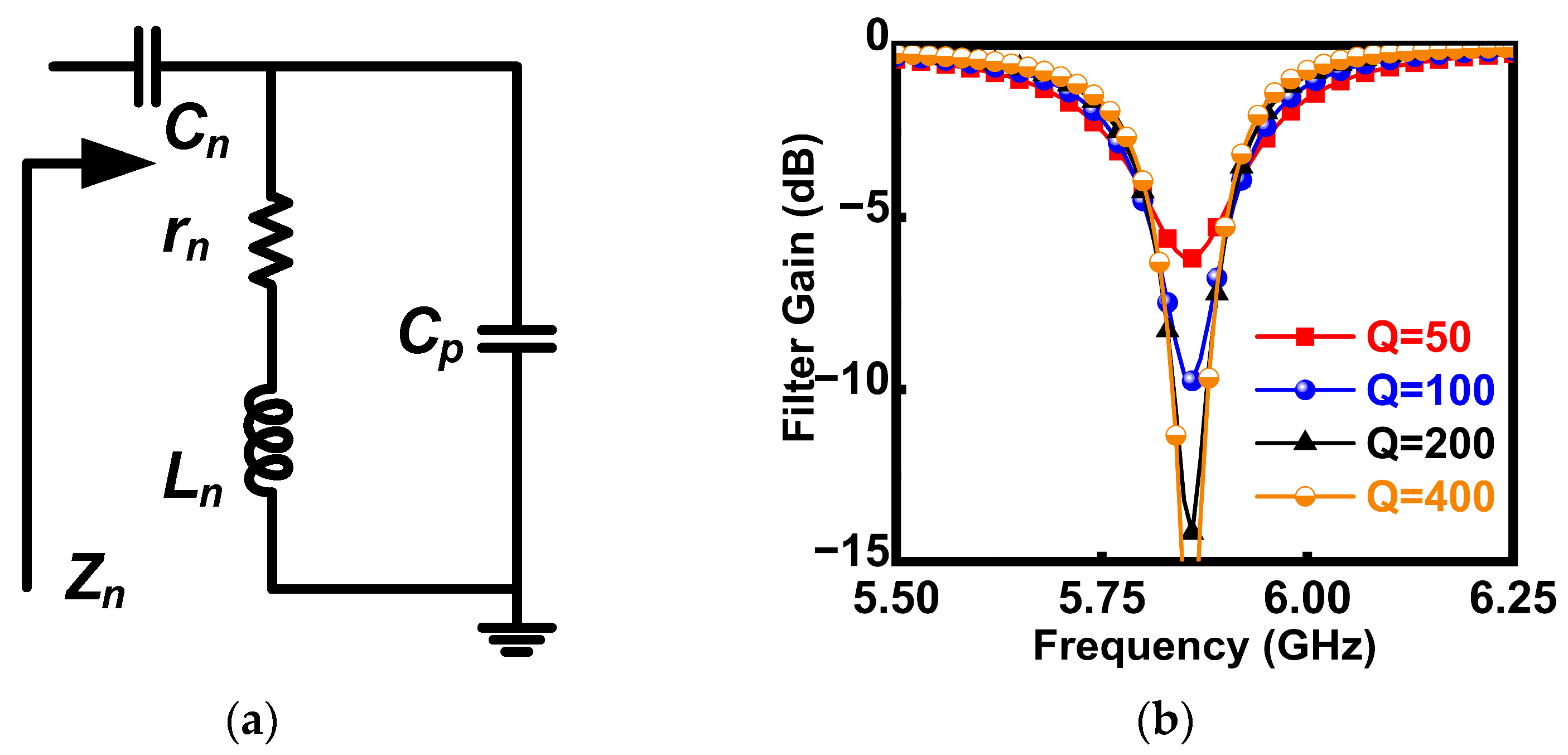

The notch filter is designed with reference to the third-order LC passive resonator in [18], as shown in Figure 2. When ignoring the passive loss rn of Ln, the input impedance of the resonator is given by

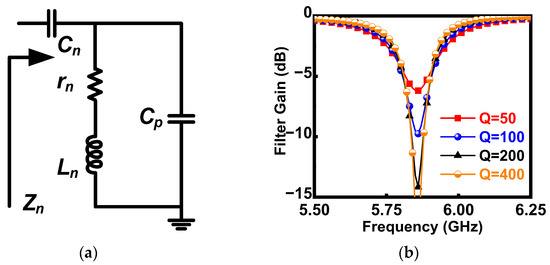

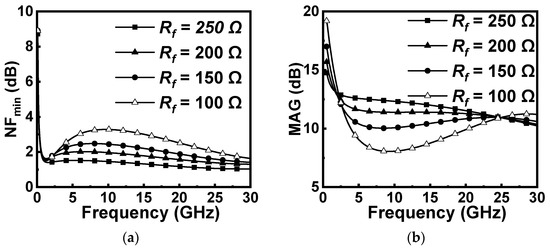

Figure 2.

(a) The schematic of the third-order LC resonator. (b) The simulated results of the third-order notch filter at different Q of Ln.

Ln, Cn, and Cp constitute the components of a third-order LC passive notch filter, while Rn represents the parasitic resistance of the inductor Ln. From (1), a pole fp and a zero fn can be, respectively, obtained as

Zn shows low impedance at fp to realize the interference rejection. In addition, the parallel resonance introduced by Cp makes Zn present high impedance at fp, which contributes to avoiding the deterioration of the desired gain. The notch depth is closely dependent on the Qs (Q = ωLn/rn) of passive components, on-chip spiral inductors especially [17]. Figure 2b shows the simulated results of notch performance at different Q of Ln, which indicates that the Ln with low Q will make the notch filter ineffective. However, the Q factor of inductors used in GaAs processes ranges between 20 and 40, which complicates the design of on-chip notch filters. Therefore, it is necessary to compensate for the loss of passive inductors when designing on-chip notch filters, and this can be achieved by utilizing the negative resistance effect of transistors [14,15,16,17].

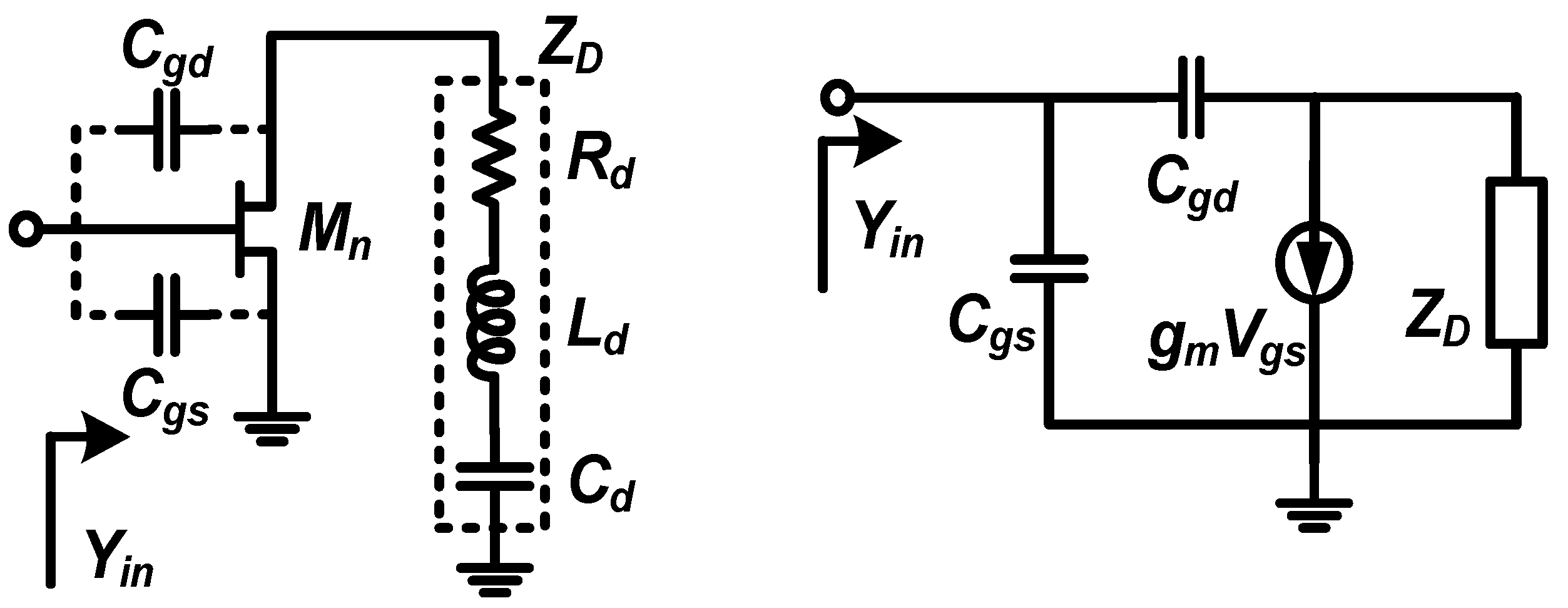

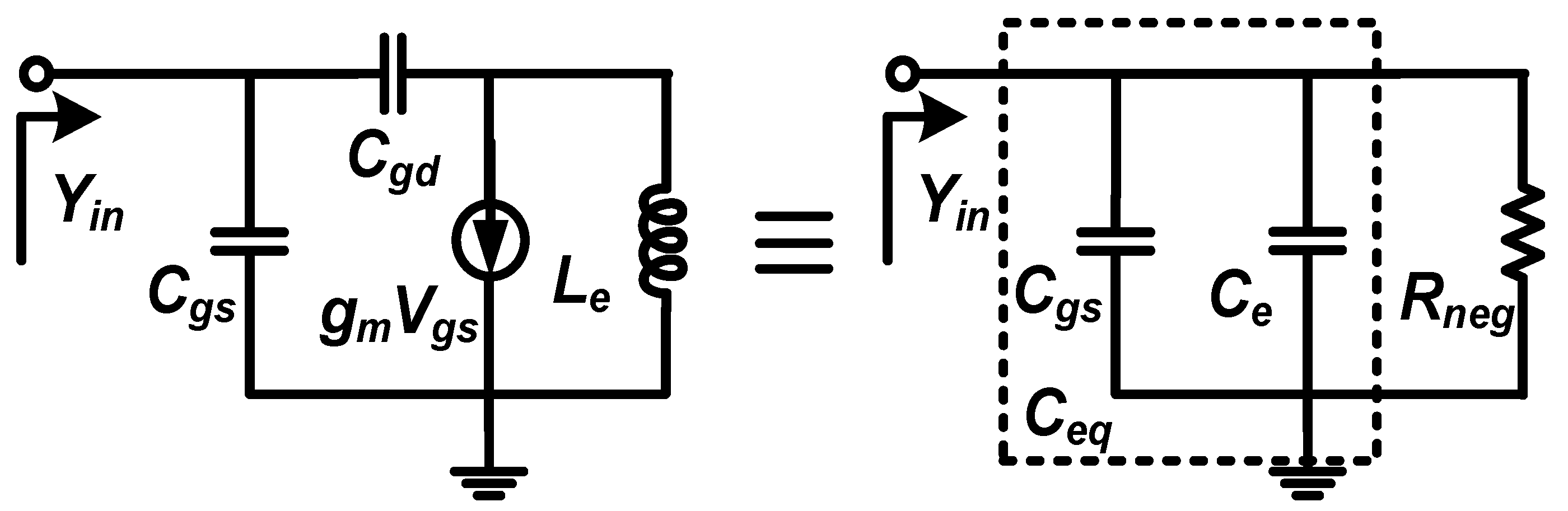

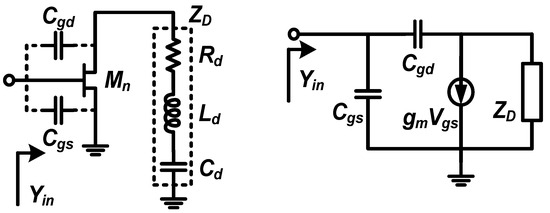

The active capacitance referenced in [19], which consists of a transistor and a series RLC circuit, is designed to provide the necessary negative resistance of the notch filter. The schematic of it is shown in Figure 3. In this circuit, the input admittance can be derived as follows:

where the parameters are

Figure 3.

The schematic of the active capacitance and its equivalent circuit.

From (2), the precondition of negative resistance can be obtained by setting I < 0, which can be derived as

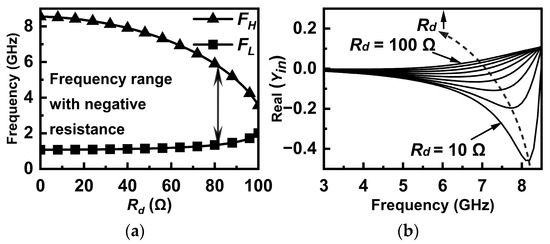

To ensure Δd > 0, Rd is limited to

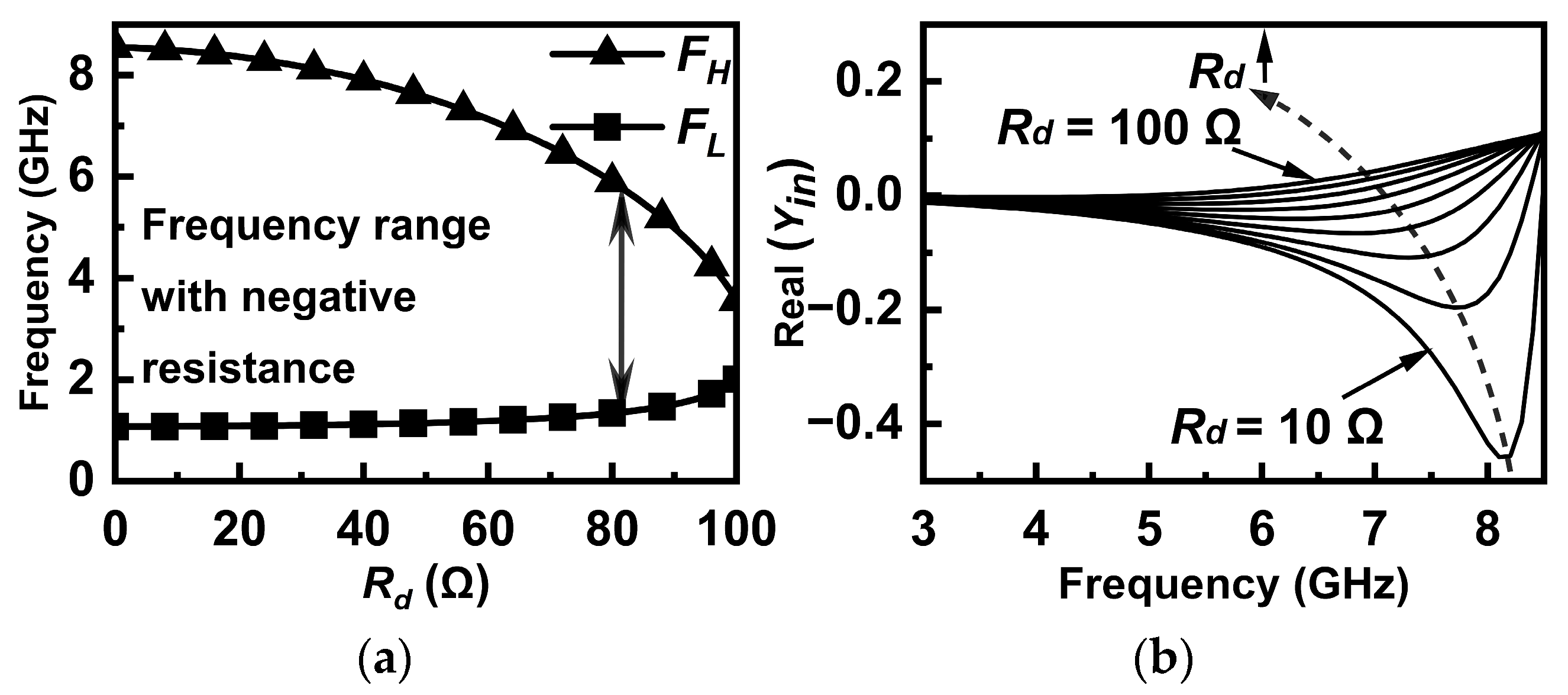

According to (4), the maximum value of Rd is dominated by the size and bias of Mn. Figure 4a and Figure 4b, respectively, shows the simulated results of the negative resistance bandwidth and values at different Rd. It can be seen that a larger Rd not only makes the negative resistance bandwidth narrow but also results in the degeneration of the negative resistance effect. Moreover, II > 0 is unconditionally satisfied in the case of (3), which means the active circuit in Figure 3 can be equivalent to a parallel connection of a capacitor Ceq and a negative resistor Rneg. To simplify the analysis, assume ZD = jωLe with the condition that Rd = 0, where Le is the equivalent inductor value of ZD under the condition of (3). The circuit of the active capacitance is shown in Figure 5, where the parameters are

Figure 4.

The simulated results of (a) negative resistance bandwidth and (b) values at different Rd.

Figure 5.

The equivalent circuit of the active capacitance with the conditions of (3) and Rd = 0.

From (5), both increasing Cgd and Cgs make Ceq larger and Rneg less with the precondition that ω2LeCgd < 1. Therefore, we can obtain an initial frequency range of the negative resistance through Ld and Cd. Then the negative resistance bandwidth can be controlled by Rd. The values of negative resistance and reactance based on Ld, Cd, and Rd can be further tuned by setting different biases or sizes of Mn.

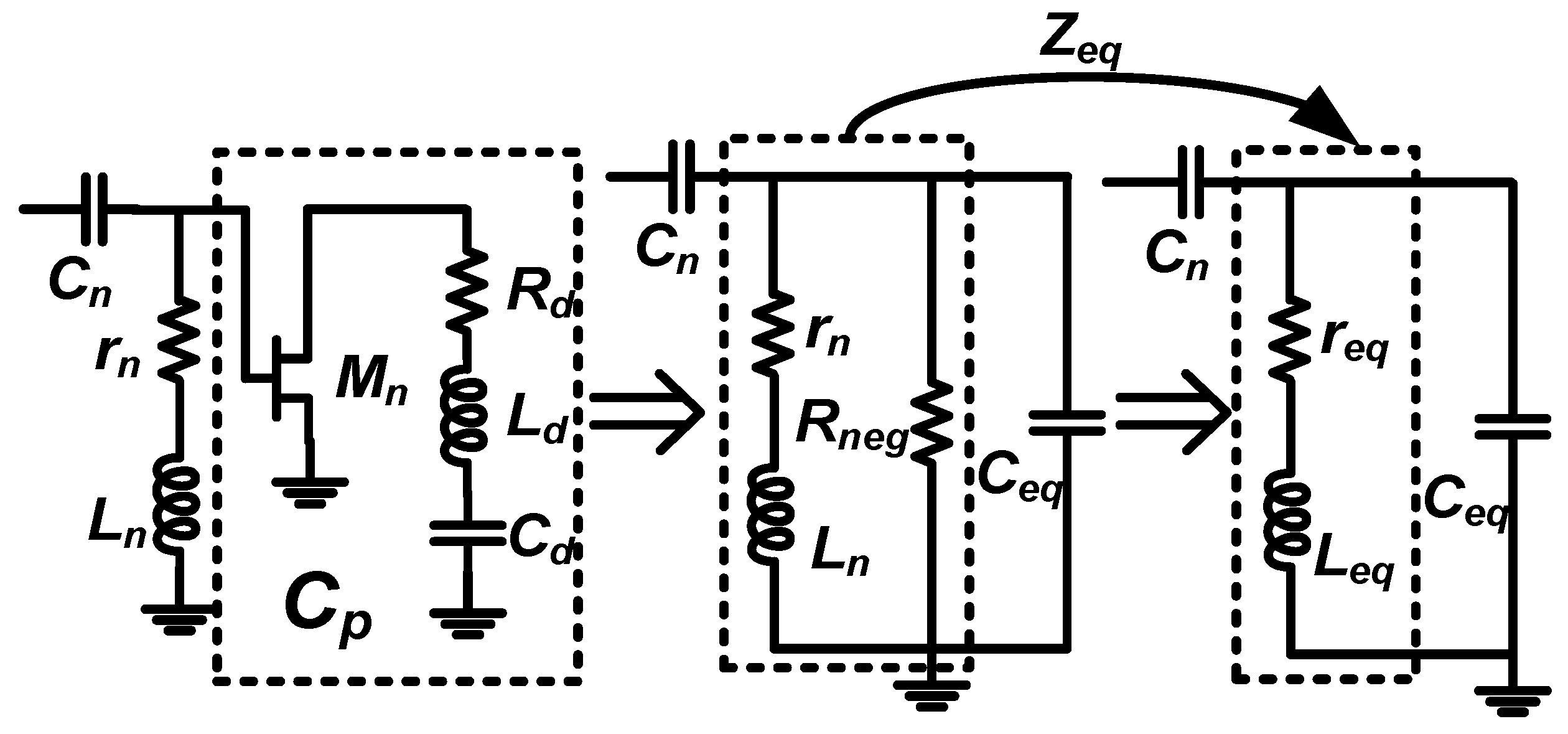

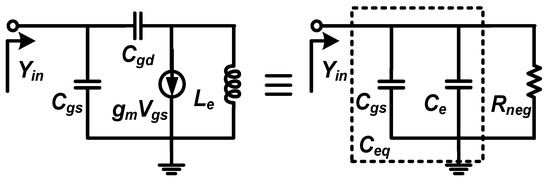

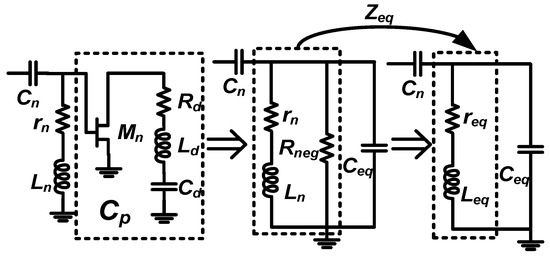

The Cp in Figure 2a is replaced with the designed active capacitance, as shown in Figure 6. The Zeq can be expressed as (6). From (6), we can find that the req = 0 is satisfied under the condition of (7). Therefore, the active capacitance has the potential to improve the Q of the notch filter.

Figure 6.

The schematic of a notch filter with active capacitance.

To verify the above theory, the active notch filter shown in Figure 6 is simulated, and its results are demonstrated in Figure 7. Compared with the passive notch filter, the performance of the active notch filter is significantly improved, which indicates that the active capacitance is helpful to enhance the Q factor of the notch filter.

Figure 7.

Comparison of S21 simulation results for active and passive notch filters and some key parameters of the active notch filter.

3. Design of the Interference-Rejection Broadband LNA

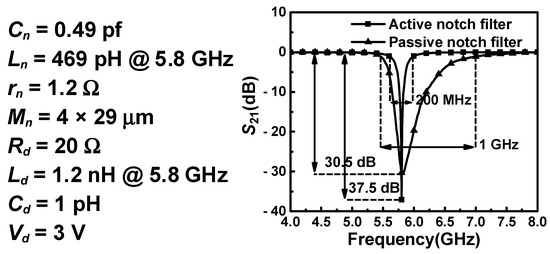

For verifying the feasibility of the designed Q-enhanced notch filter, we designed an LNA for UWB systems using the PL15-12 InGaAs pHEMT(WIN, Taiwan, China) process, as shown in Figure 8. The broadband LNAs of UWB systems are larger than three octaves, and it is difficult to realize such a wide bandwidth with a conventional common-source structure, so it is necessary to introduce some bandwidth-enhancing techniques to realize a broadband design.

Figure 8.

The schematic of the 3–15 GHz interference-rejection LNA with a Q-enhanced notch filter and frequency-dependent feedback loop (FDFL).

The gain roll-off of transistors is one of the most important limiting factors in the broadband design. There are usually two ways to improve transistor gain roll-off: one is to reduce the gain in the low-frequency band through a feedback network to achieve gain flattening over a wide bandwidth range, and the other is to compensate for the high-frequency gain to achieve broadband gain flattening. One of the simplest and most effective methods is to adjust the broadband gain by introducing a negative feedback network [20]. Therefore, a frequency-dependent feedback loop (FDFL) is introduced into the design to achieve gain flattening over a wide bandwidth. In addition, the FDFL network can be equated to a lossy matching network, which helps to realize broadband impedance matching. At the same time, the stable operation of the circuit can be guaranteed due to the introduction of the lossy network.

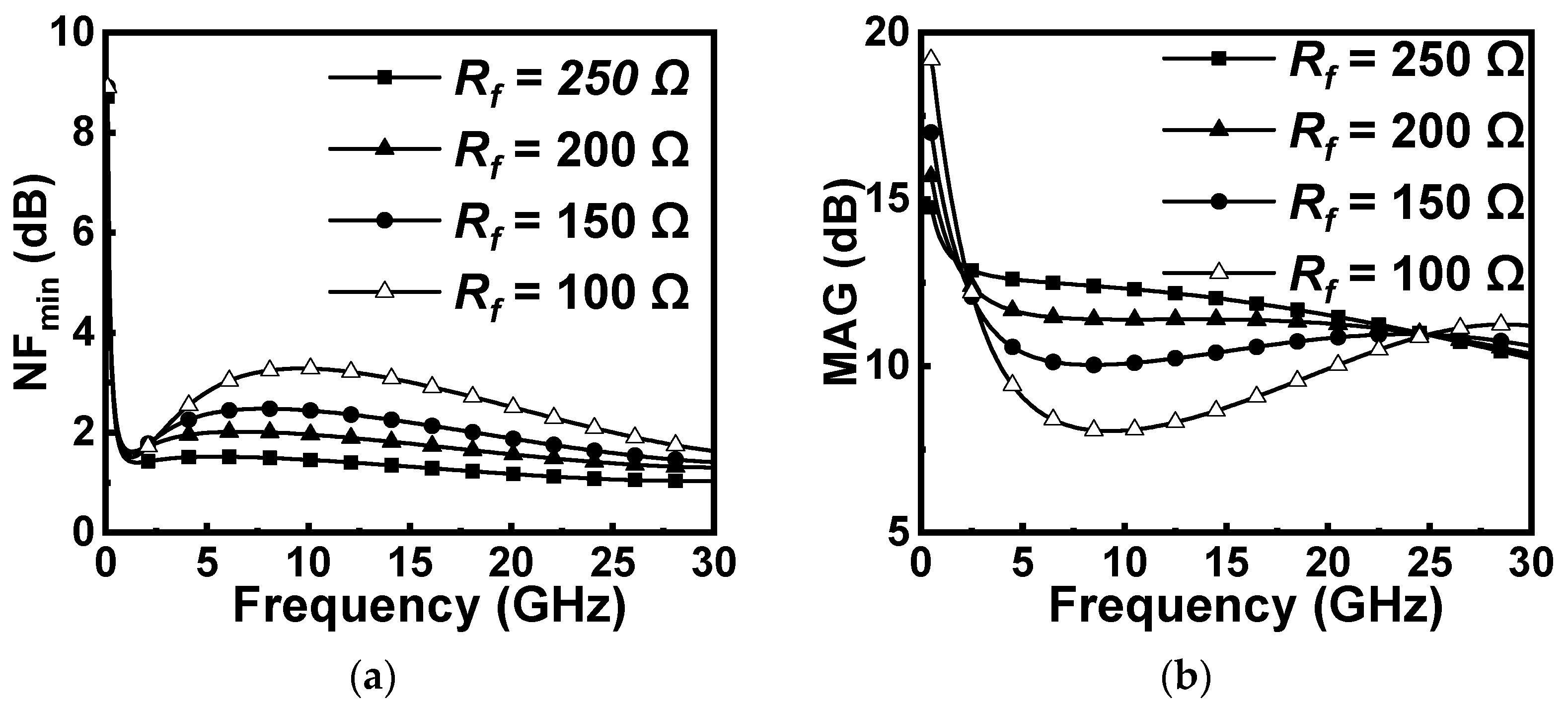

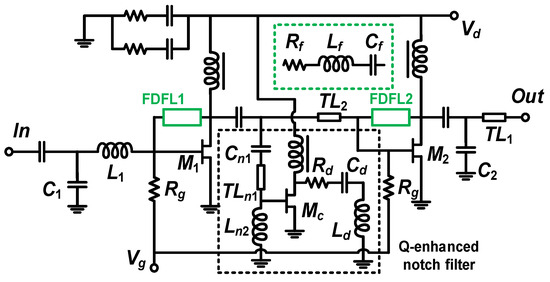

For cascaded LNA design, both the first and second stages are designed to achieve low noise with acceptable power gain. To take a proper value of the Rf, we simulated the effect of different Rf values on maximum available gain (MAG) and noise figure (NF), as shown in Figure 9. In this design, the introduction of FDFL inevitably leads to an increase in NF. To obtain a small NF for the designed broadband LNA, it is necessary to maximize the value of the feedback resistor in the first-stage FDFL network while ensuring stable operation of the amplifier [20]. Therefore, Rf in the first stage of the FDFL is selected to be 340 Ω. Also, when the Rf in the first FDFL is selected, the flatness of the overall gain can be adjusted by adjusting the Rf in the second FDFL. Finally, an overall optimization is carried out for optimum circuit performance. Table 1 lists some of the optimized parameters of the key components.

Figure 9.

The effect of different Rf values on (a) NF and (b) MAG in the FDFL.

Table 1.

Key Component Parameters of the Q-Enhanced LNA.

4. Measurement Results

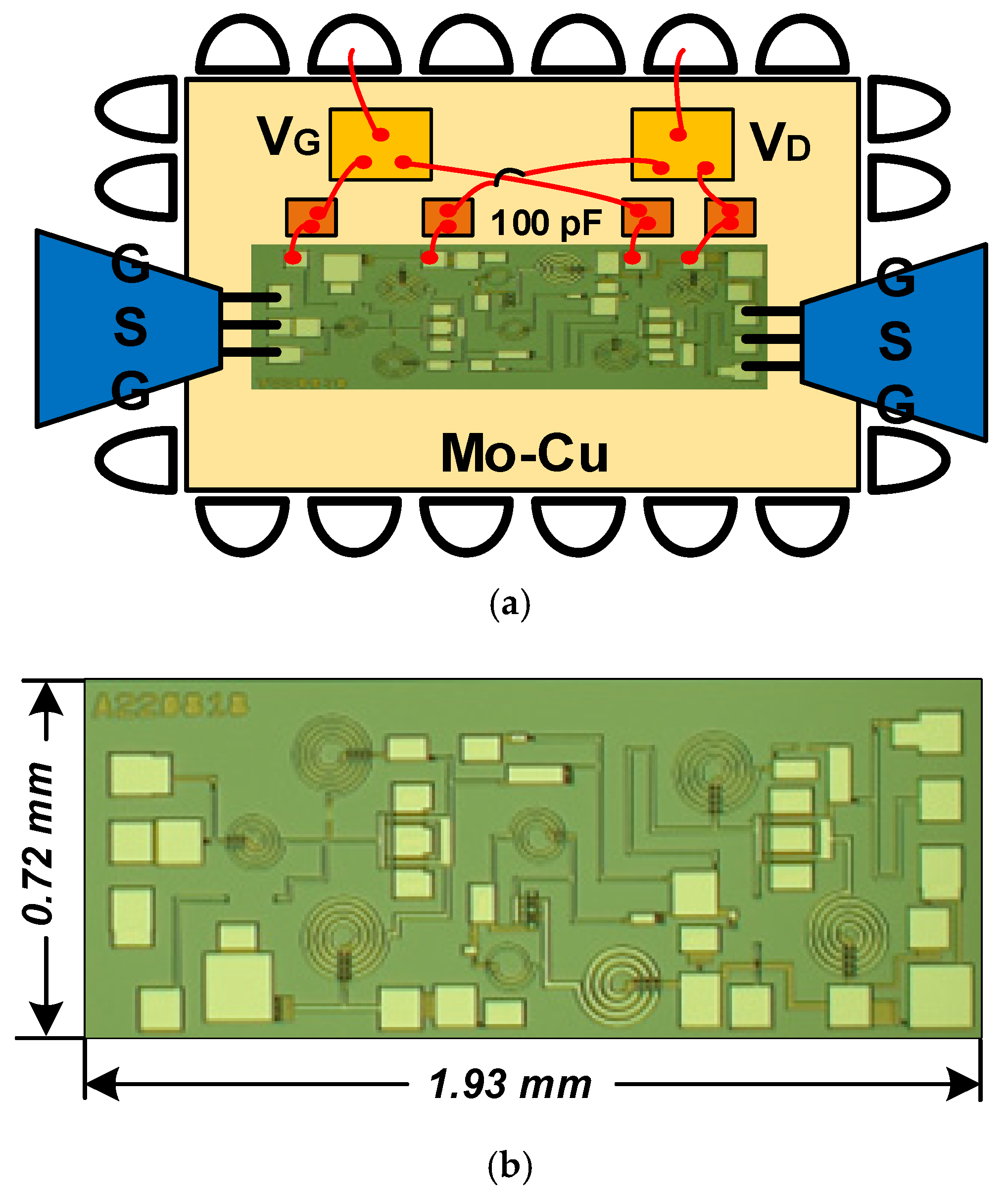

This design was fabricated using WIN’s 0.15 µm GaAs pHEMT process(WIN, Taiwan, China). A schematic of the QFN-packaged chip used for testing is shown in Figure 10a, and a micrograph of the chip is shown in Figure 10b, with an area of 1.93 × 0.72 mm2 (including all input/output test pads). The measurement setup includes a probe station (Cascade Summit 11000M), a vector network analyzer (Agilent N5244A), and a noise analyzer (Keysight N8976B). The LNA is biased at VD = 3 V, VG = −0.6 V for a total current of 56 mA.

Figure 10.

The proposed LNA MMIC: (a) schematic of the chip in QFN package for testing and (b) micrograph of the chip.

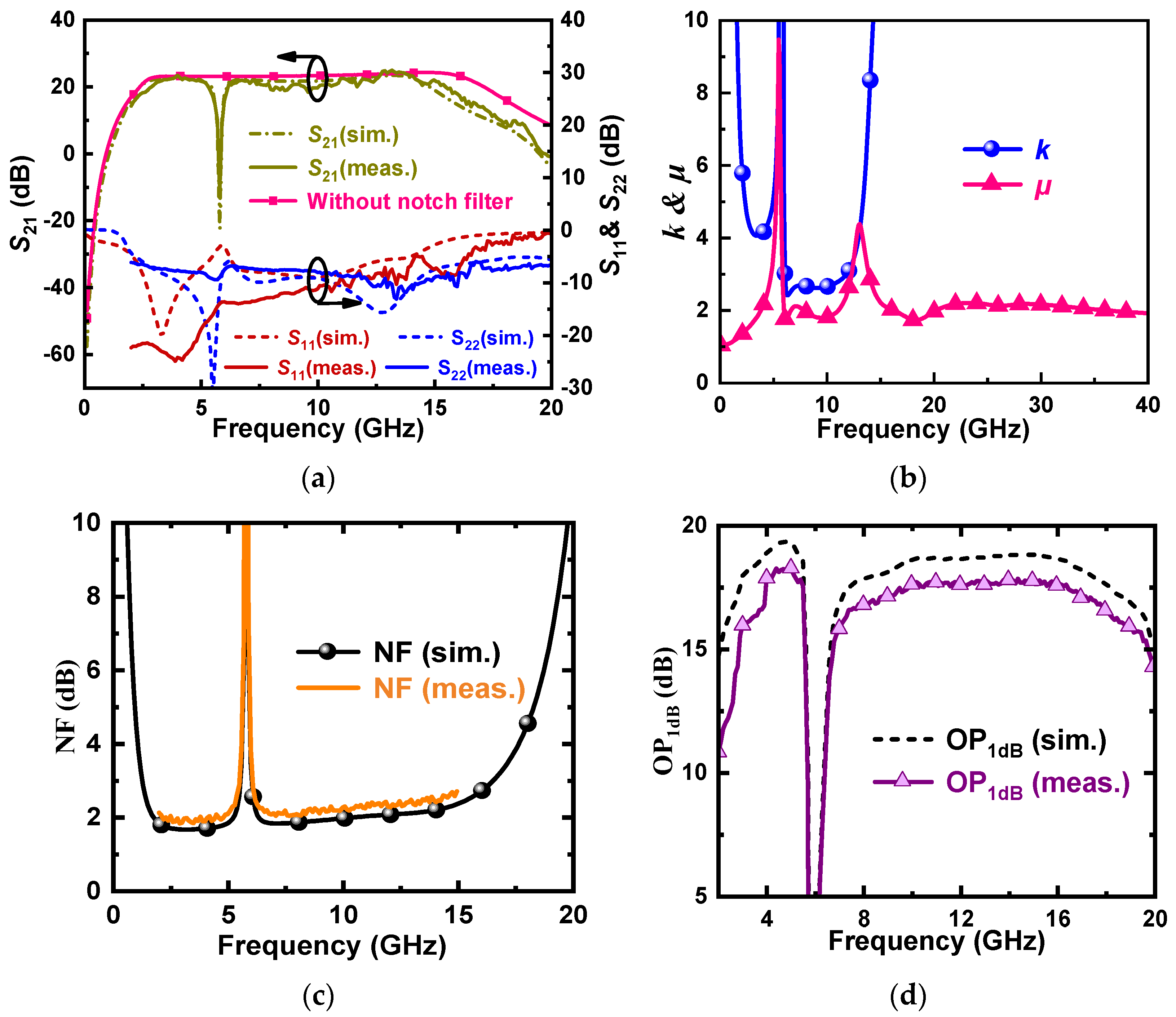

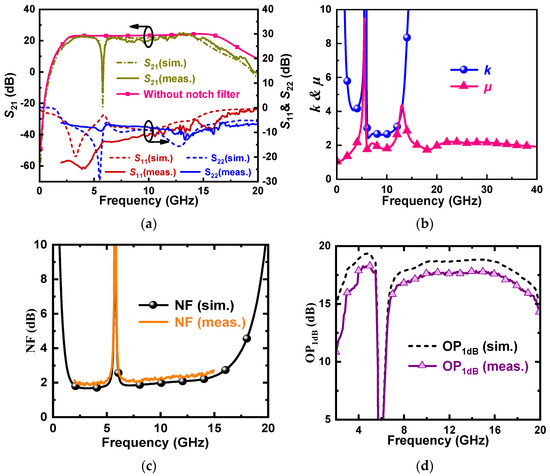

Figure 11a shows the S-parameters of the designed LNA. Compared with the simulation results, the measured S11 and S22 deteriorate slightly but are still less than 6 dB in the range of 3–15 GHz. S21 is about 1 dB lower than the simulated value, with an average value of 20.91 dB. In addition, S21 of the LNA without the Q-enhanced notch filter is given to visualize the interference suppression effect. The comparison shows that the maximum IRR of the designed LNA is 35.2 dB at 5.8 GHz, with 10 dB deterioration compared with the simulation results. However, the actual test results show that the introduction of the Q-enhanced notch filter has less effect on the in-band gain, and the trap frequency is shifted by only 0.05 GHz to the lower frequencies.

Figure 11.

Measured and simulated (a) S-parameters. (b) Rollet k factor and stability factor μ. (c) NF. (d) OP1dB.

Figure 11b shows the simulated stability curves; the coefficients k and μ are both greater than 1 over the passband, implying that the LNA is unconditionally stable.

Figure 11c shows the simulated and the measured NF. The comparison shows that the NF of the measured deteriorates slightly compared to the simulated result, but the overall NF is lower than 2.6 dB, with a minimum value of 1.8 dB. It can also be derived that the introduction of the Q-enhanced notch filter does not have a significant impact on the in-band NF and only deteriorates the noise in a very narrow bandwidth of around 5.8 GHz, which is exactly what we expect.

Figure 11d shows the output 1 dB compression point (OP1dB), which has an average value of 11.82 dBm. Compared with the simulation results, the trend of the OP1dB curve in the 3–15 GHz range is in good agreement, but the overall OP1dB is reduced by about 2 dB.

These measurements validate the feasibility of the Q-enhanced notch filter. Table 2 summarizes the performance of the proposed LNA. Compared with other wideband interference-rejection LNAs, this design has a higher gain and lower noise figure. In addition, the Q-enhanced notch filter of this design minimizes the impact on the in-band gain compared to similar products.

Table 2.

Comparison with Other Interference-Rejection Broadband Low Noise Amplifiers.

5. Conclusions

In this brief, we present a 3–15 GHz interference-rejection low-noise amplifier using a 0.15 µm GaAs pHEMT process. The Q-enhanced notch filter with active capacitance is introduced in the LNA, which realizes a maximum interferer-rejected ratio of 35.2 dB at 5.8 GHz with small deteriorations for in-band gains. In addition, the LNA achieves a maximum gain of 24.5 dB and a minimum noise figure of 1.8 dB in the operating frequency range from 3 to 15 GHz. This demonstrates the suitability of the designed Q-enhanced notch filter with active capacitance for the design of an interference-rejection LNA.

Author Contributions

Conceptualization, J.L., Y.F., and F.M.; data correction, J.L., Y.F., and F.M.; methodology, J.L., Y.F., and F.M.; validation, J.L., Y.F., and F.M.; visualization, J.L., Y.F., and F.M.; writing—original draft, J.L., Y.F., and F.M.; writing—review and editing, J.L., Y.F., and F.M. All authors have read and agreed to the published version of the manuscript.

Funding

This research received no external funding.

Data Availability Statement

The original contributions presented in this study are included in the article. Further inquiries can be directed to the corresponding author.

Conflicts of Interest

The authors declare no conflicts of interest.

References

- Revision of Part 15 of the Commission’s Rules Regarding Ultra-Wideband Transmission Systems; ET Docket No. 98-153, First Report and Order, 17 FCC Rcd 7435, 7441-46; Federal Communications Commission: Washington, DC, USA, 2022.

- Batra, A.; Balakrishnan, J.; Aiello, G.R.; Foerster, J.R.; Dabak, A. Design of a multiband OFDM system for realistic UWB channel environments. IEEE Trans. Microw. Theory Tech. 2004, 52, 2123–2138. [Google Scholar] [CrossRef]

- Lee, G.; Park, J.; Jang, J.; Jung, T.; Kim, T.W. An IR-UWB CMOS transceiver for high-data-rate, low-power, and short-range communication. IEEE J. Solid-State Circuits 2019, 54, 2163–2174. [Google Scholar] [CrossRef]

- Lee, F.S.; Chandrakasan, A.P. A BiCMOS ultra-wideband 3.1–10.6-GHz front-end. IEEE J. Solid-State Circuits 2006, 41, 1784–1791. [Google Scholar] [CrossRef]

- Cusmai, G.; Brandolini, M.; Rossi, P.; Svelto, F. A 0.18-μm C M O S selective receiver front-end for UWB applications. IEEE J. Solid-State Circuits 2006, 41, 1764–1771. [Google Scholar] [CrossRef]

- Medepalli, K.; Gopalakrishnan, P.; Famolari, D.; Kodama, T. Voice capacity of IEEE 802.11b, 802.11a and 802.11g wireless LANs. In Proceedings of the IEEE Global Telecommunications Conference, Dallas, TX, USA, 29 November–3 December 2004; IEEE: New York, NY, USA. [Google Scholar]

- Hedayati, H.; Entesari, K. A 90-nm CMOS UWB impulse radio transmitter with 30-dB in-band notch at IEEE 802.11a system. IEEE Trans. Microw. Theory Tech. 2013, 61, 4220–4232. [Google Scholar] [CrossRef]

- Koirala, N.; Pokharel, R.K.; Galal, A.I.A.; Kanaya, H.; Yoshida, K. Design of a Low Noise Amplifier with integrated notch filter for interference rejection in ultra-wideband systems. In Proceedings of the 2011 China-Japan Joint Microwave Conference, Hangzhou, China, 20–22 April 2011; pp. 1–4. [Google Scholar]

- Zhang, J.; Zhao, D.; You, X. Analysis and Design of a CMOS LNA with Transformer-Based Integrated Notch Filter for Ku-Band Satellite Communications. IEEE Trans. Microw. Theory Tech. 2022, 70, 790–800. [Google Scholar] [CrossRef]

- Gao, L.; Ma, Q.; Rebeiz, G.M. A 20–44-GHz image-rejection receiver with >75-dB image-rejection ratio in 22-nm CMOS FD-SOI for 5G applications. IEEE Trans. Microw. Theory Tech. 2020, 68, 2823–2832. [Google Scholar] [CrossRef]

- Xie, H.; Cheng, Y.J.; Fan, Y. A K-band high interference-rejection GaAs low-noise amplifier using multizero control method for satellite communication. IEEE Microw. Wirel. Compon. Lett. 2020, 30, 1069–1072. [Google Scholar] [CrossRef]

- Lee, J.; Nguyen, C. A K-/Ka-band concurrent dual-band single-ended Input to differential output low-noise amplifier employing a novel transformer feedback dual-band load. IEEE Trans. Circuits Syst. I Reg. Pap. 2018, 65, 2679–2690. [Google Scholar] [CrossRef]

- Mohammadi, L.; Koh, K.-J. Integrated synthetic bandstop filters for blocker rejection at RF and microwave frequency bands. IEEE Trans. Microw. Theory Tech. 2016, 64, 3557–3567. [Google Scholar] [CrossRef]

- Park, B.; Choi, S.; Hong, S. A low-noise amplifier with tunable interference rejection for 3.1- to 10.6-GHz UWB systems. IEEE Microw. Wirel. Compon. Lett. 2010, 20, 40–42. [Google Scholar] [CrossRef]

- Liang, C.-P.; Rao, P.-Z.; Huang, T.-J.; Chung, S.-J. Analysis and design of two low-power ultra-wideband CMOS low-noise amplifiers with out-band rejection. IEEE Trans. Microw. Theory Tech. 2010, 58, 277–286. [Google Scholar] [CrossRef]

- Lin, J.-Y.; Chiou, H.-K. Power-constrained third-order active notch filter applied in IR-LNA for UWB standards. IEEE Trans. Circuits Syst. II Exp. Briefs 2011, 58, 11–15. [Google Scholar] [CrossRef]

- Li, Y.; Li, X.; Huang, Z.; Tan, T.; Chen, D.; Cao, C.; Qi, Z. A Novel Low-Power Notch-Enhanced Active Filter for Ultrawideband Interferer Rejected LNA. IEEE Trans. Microw. Theory Tech. 2021, 69, 1684–1697. [Google Scholar] [CrossRef]

- Nguyen, T.-K.; Oh, N.-J.; Cha, C.-Y.; Oh, Y.-H.; Ihm, G.-J.; Lee, S.-G. Image-rejection CMOS low-noise amplifier design optimization techniques. IEEE Trans. Microw. Theory Tech. 2005, 53, 538–547. [Google Scholar] [CrossRef]

- Chun, Y.-H.; Lee, J.-R.; Yun, S.-W.; Rhee, J.-K. Design of an RF low-noise bandpass filter using active capacitance circuit. IEEE Trans. Microw. Theory Tech. 2005, 53, 687–695. [Google Scholar] [CrossRef]

- Li, J.; Yuan, Y.; Zeng, J.; He, D.; Yu, Z. A Broadband LNA With Multiple Bandwidth Enhancement Techniques. IEEE Microw. Wirel. Technol. Lett. 2023, 33, 551–554. [Google Scholar] [CrossRef]

- Chen, W.-L.; Chang, S.-F.; Huang, G.-W.; Jean, Y.-S.; Yeh, T.-H. A Ku-Band Interference-Rejection CMOS Low-Noise Amplifier Using Current-Reused Stacked Common-Gate Topology. IEEE Microw. Wirel. Compon. Lett. 2007, 17, 718–720. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).