A Si/SiC Heterojunction Double-Trench MOSFET with Improved Conduction Characteristics

Abstract

1. Introduction

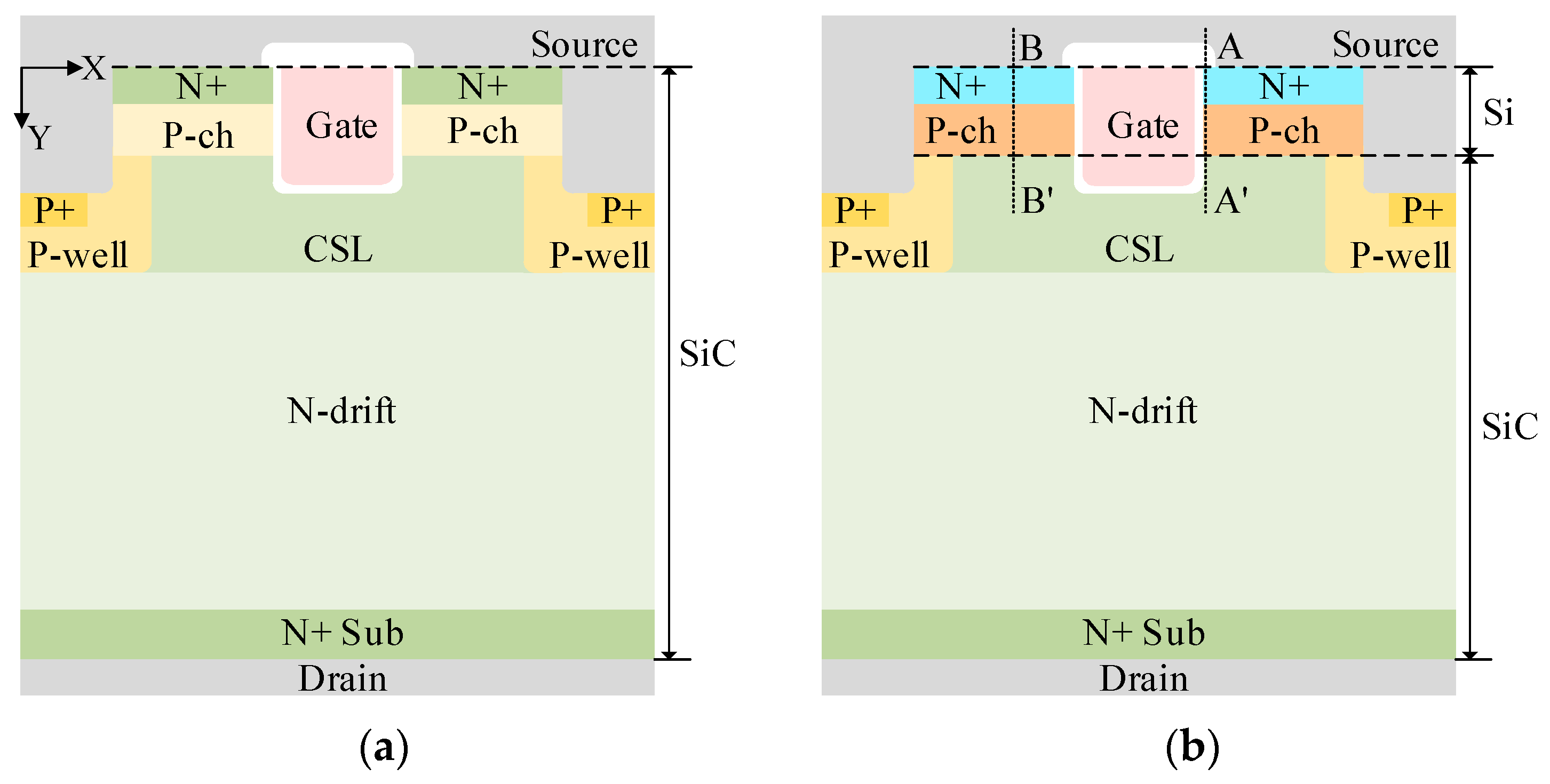

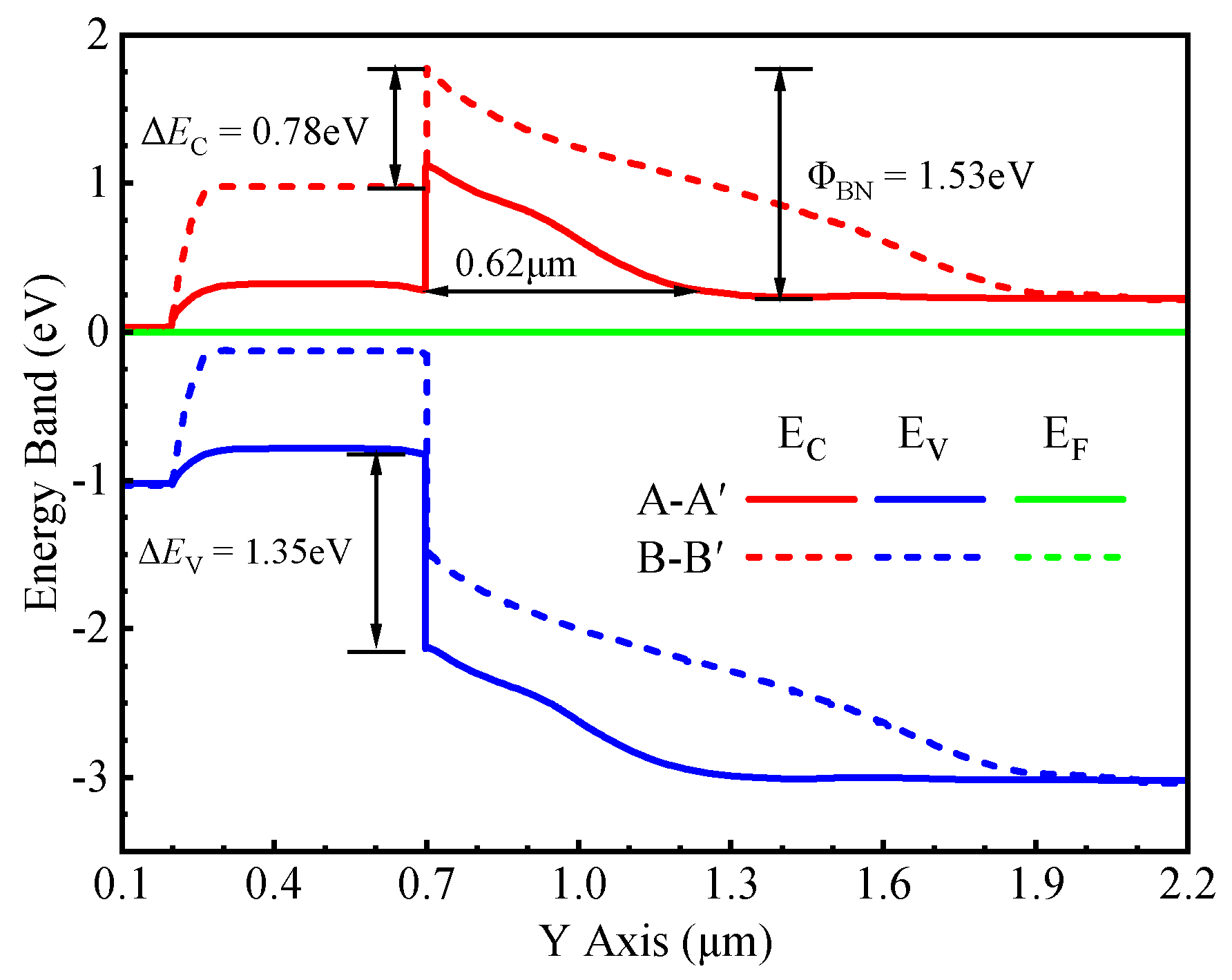

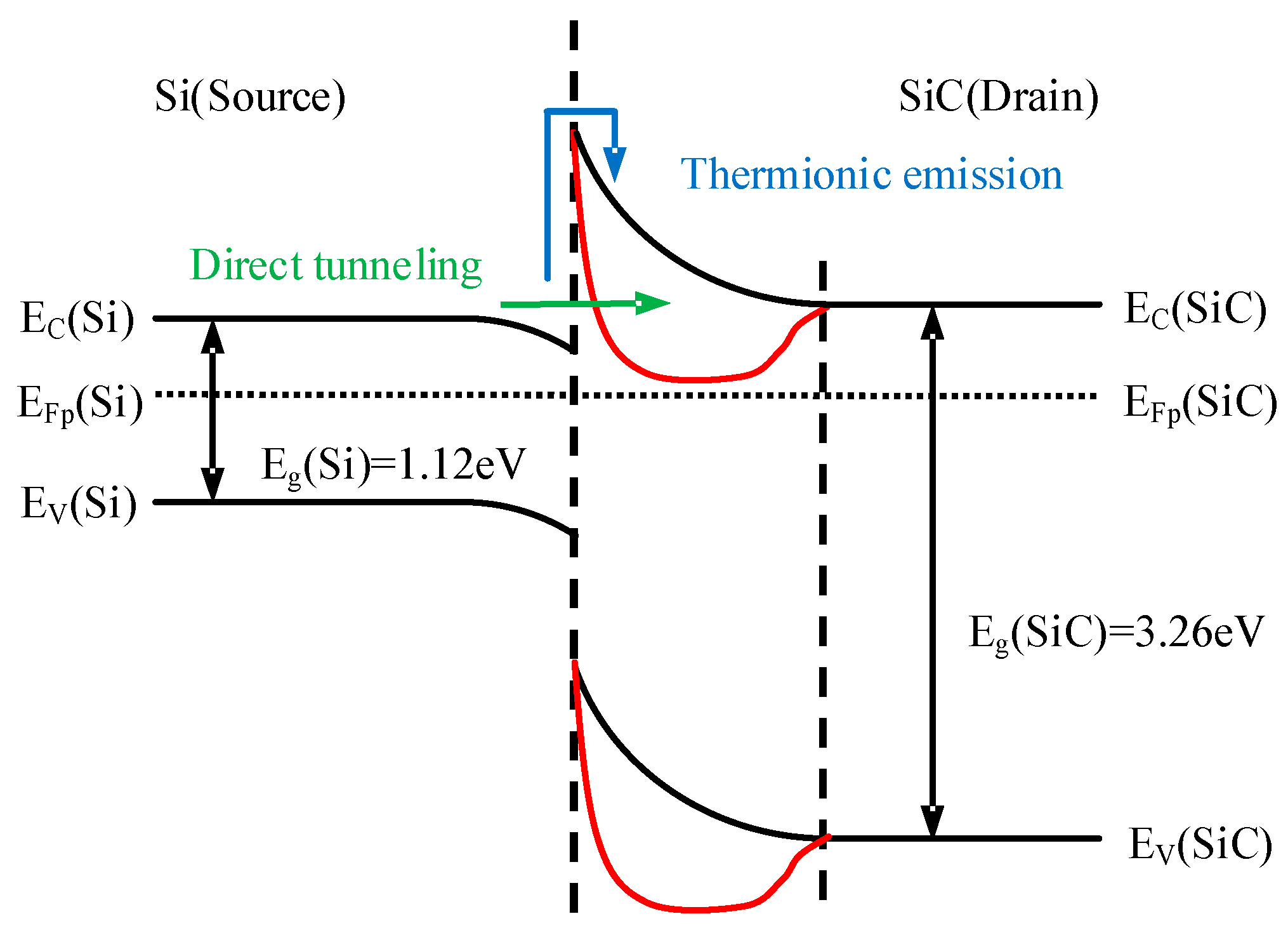

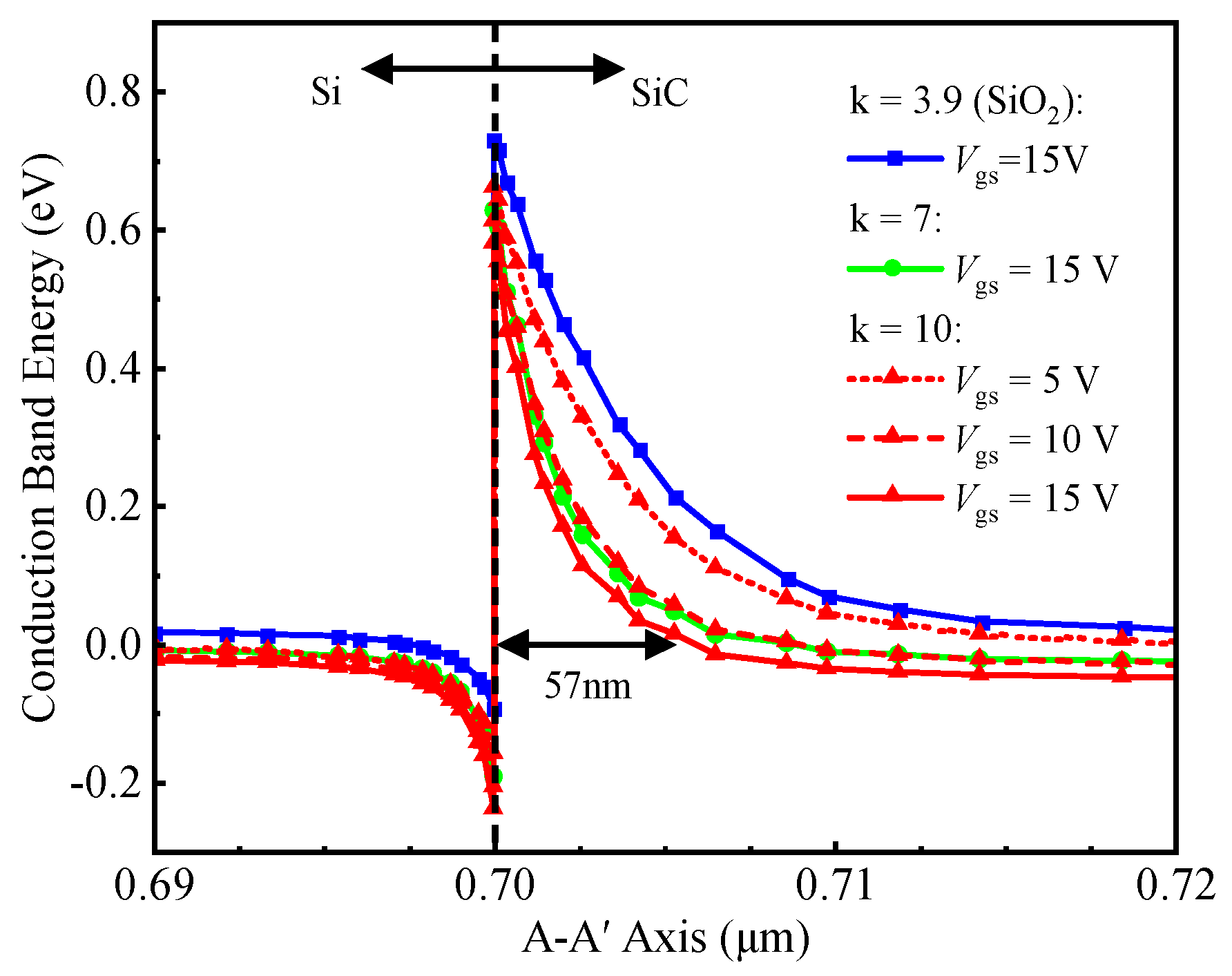

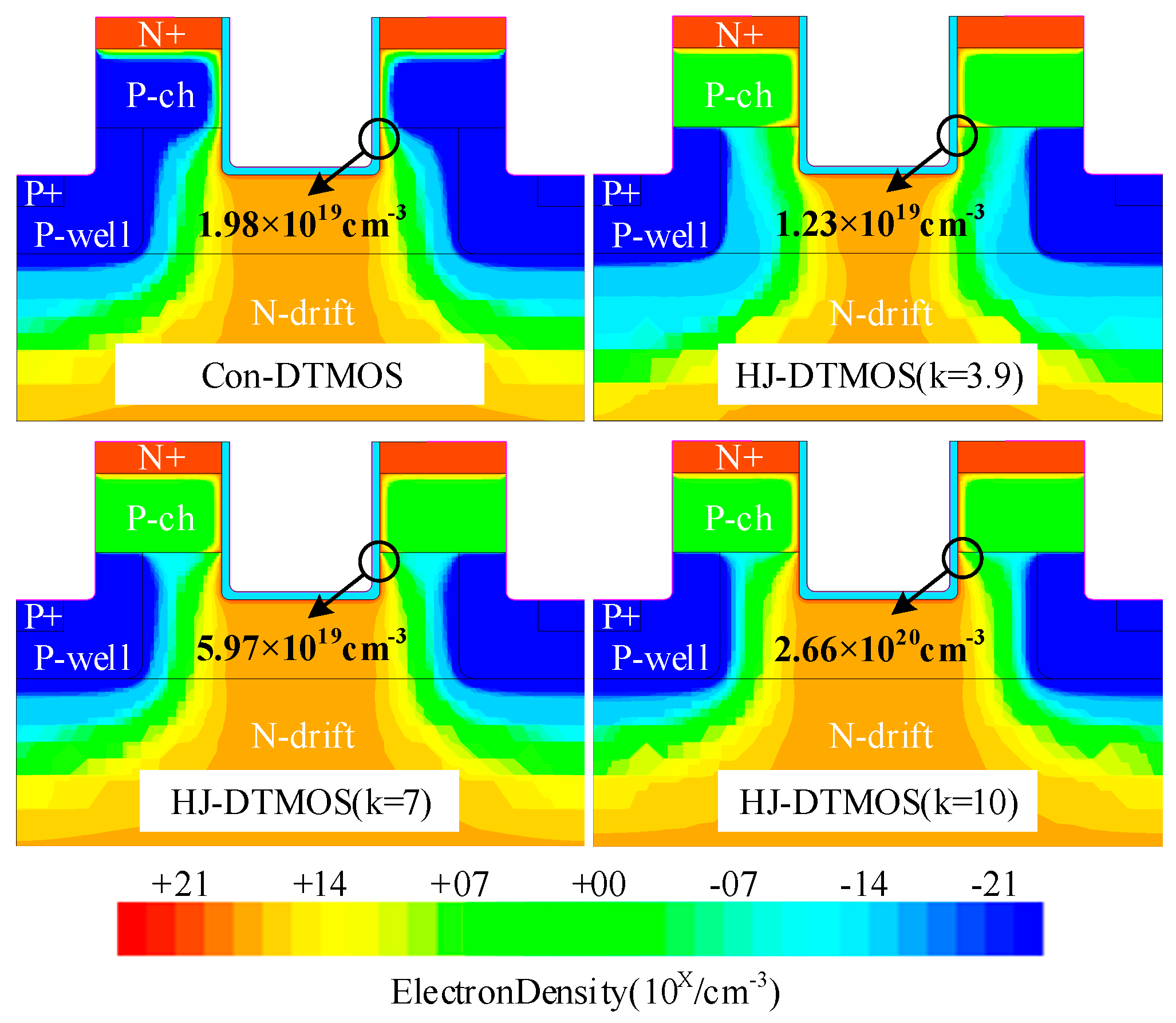

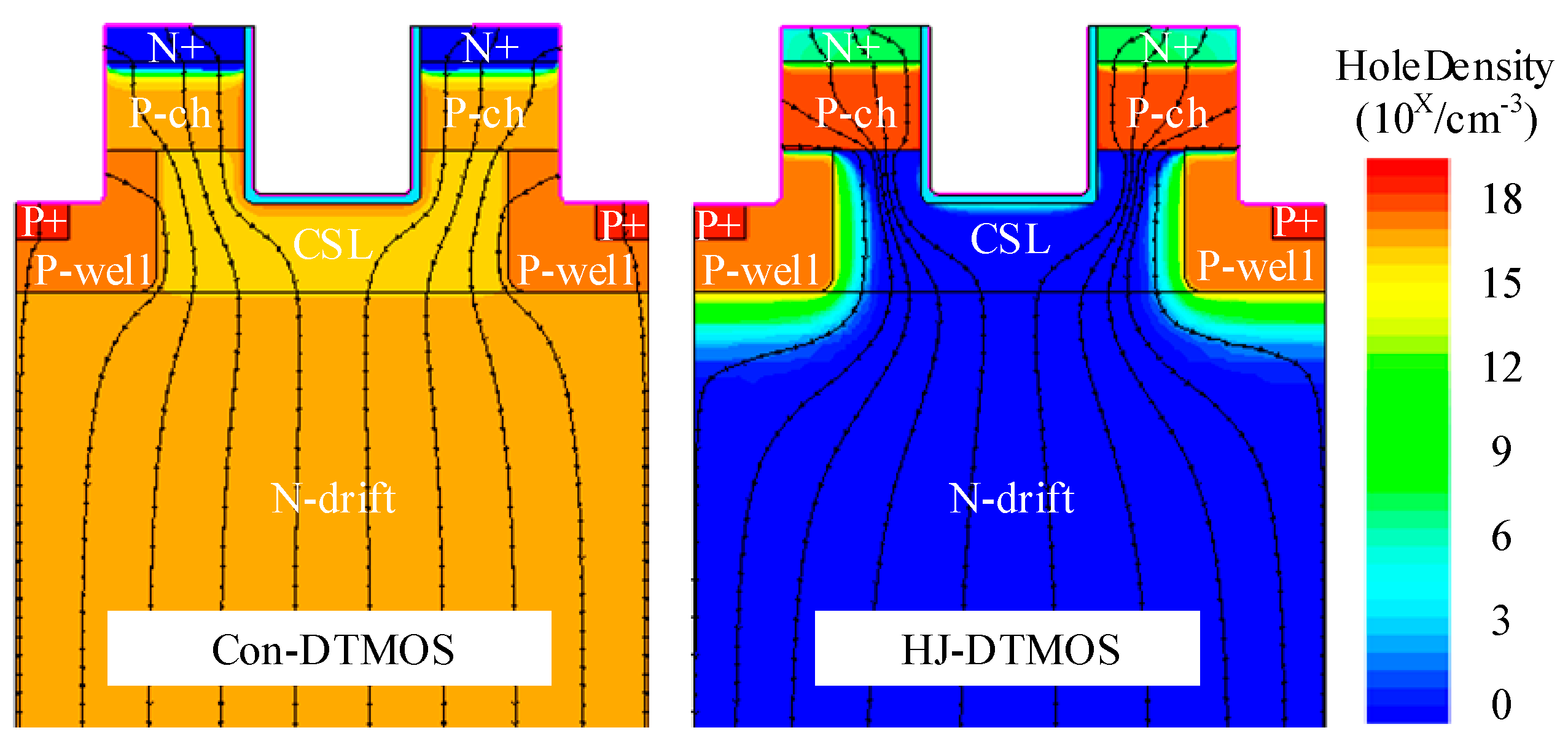

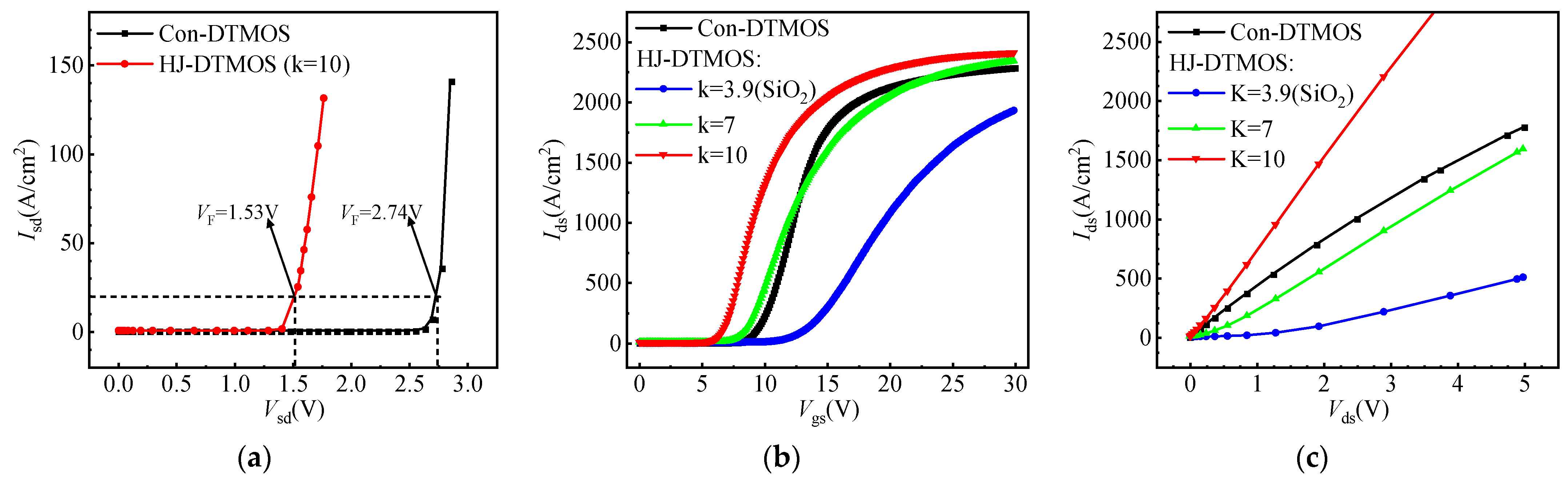

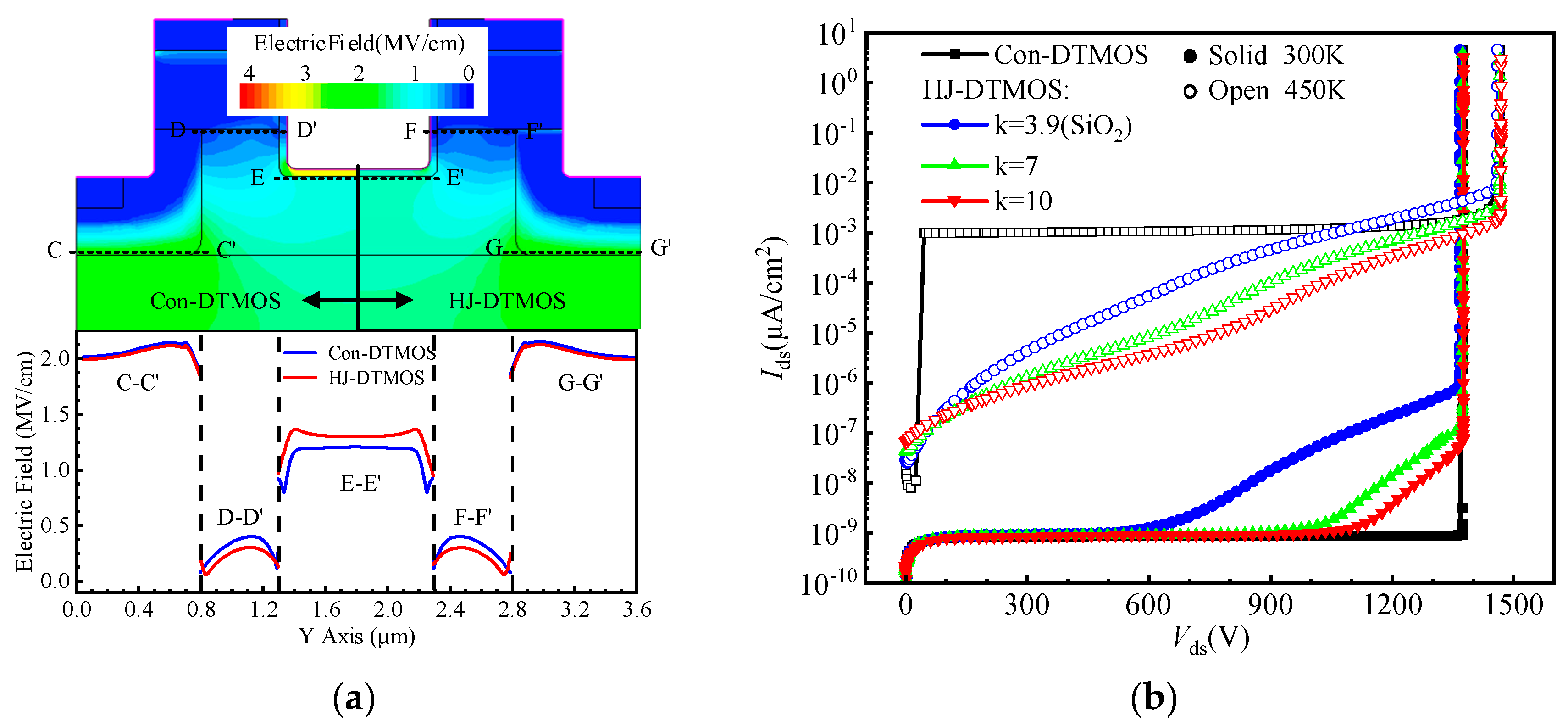

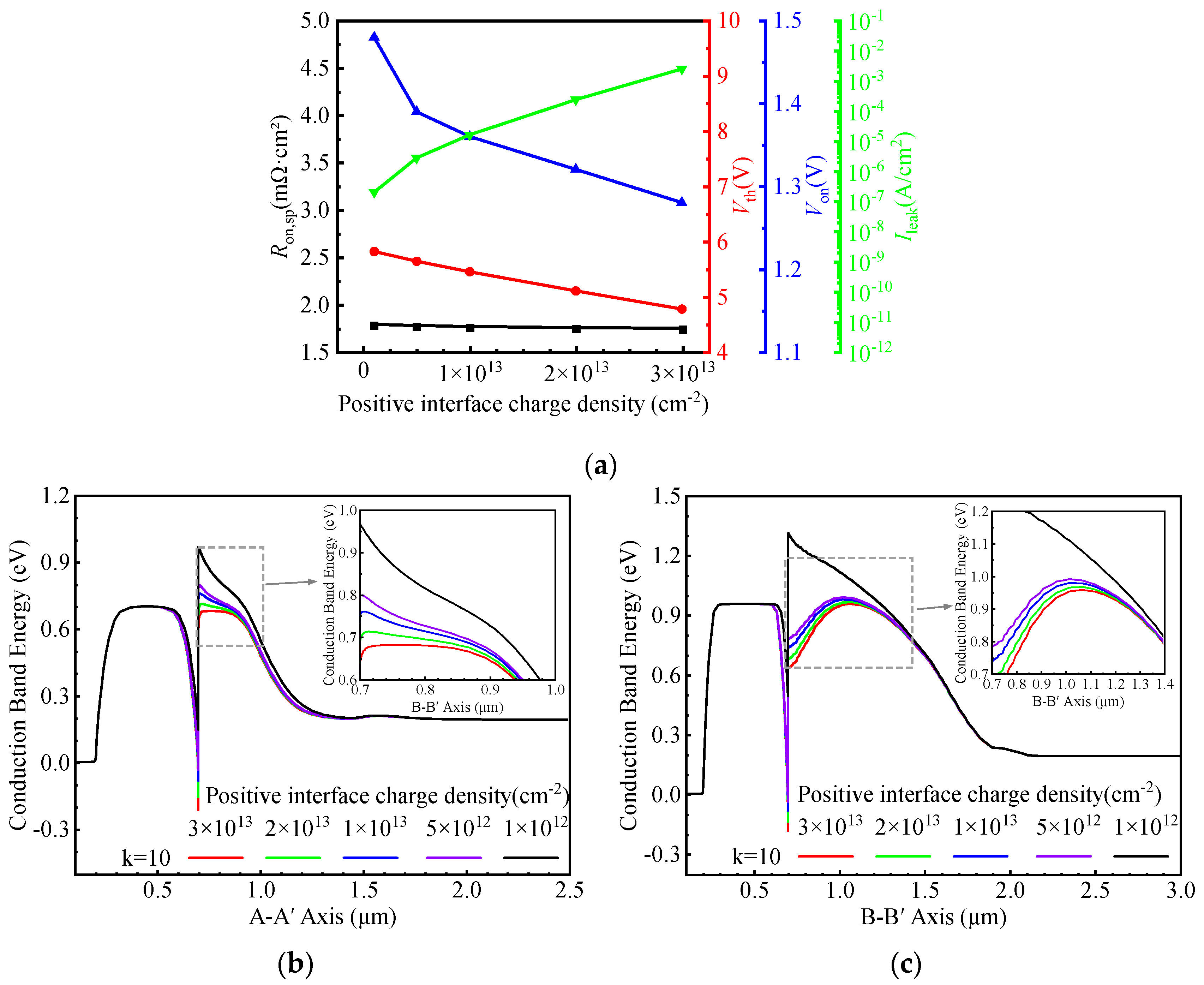

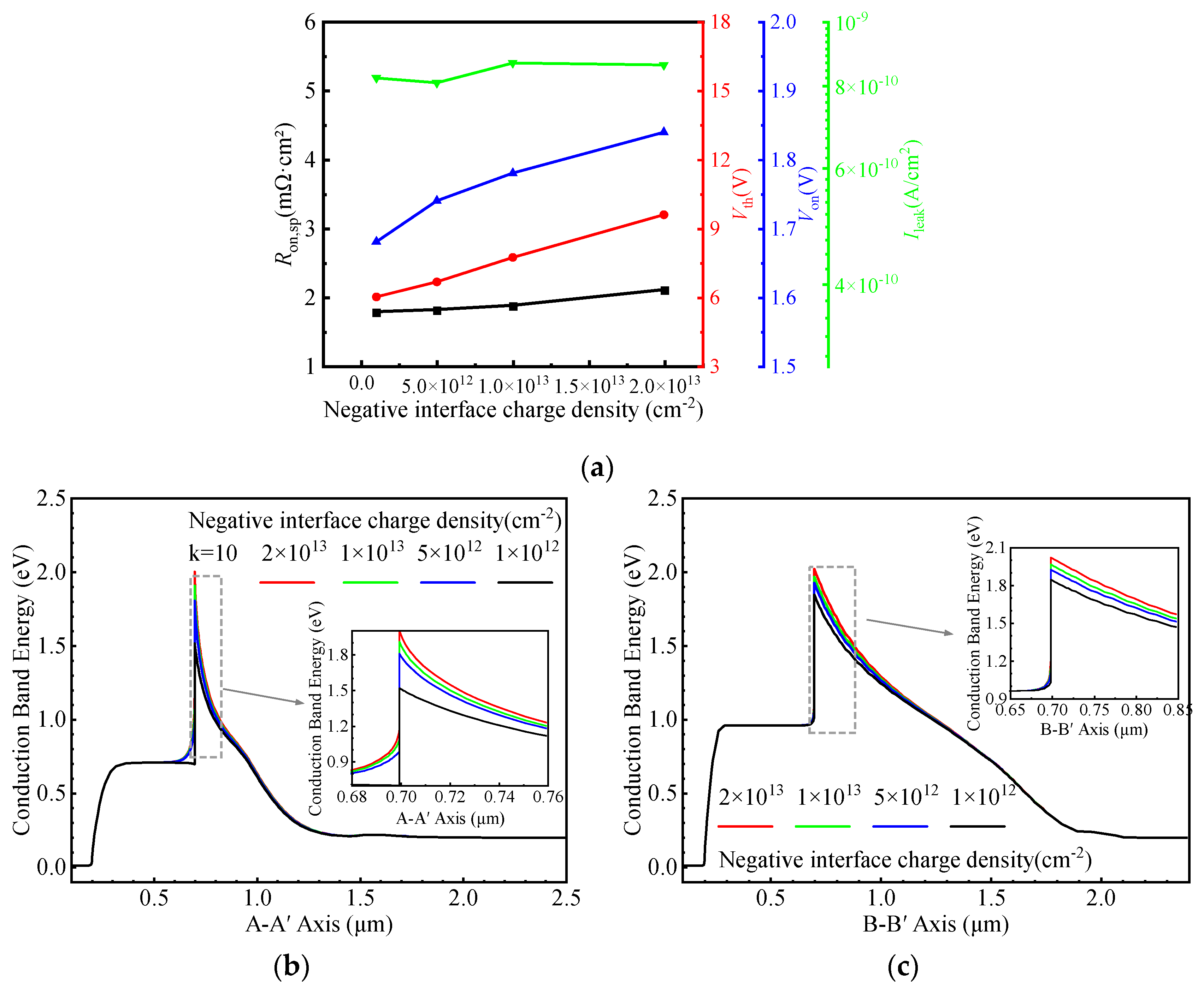

2. Device Structure and Mechanism

3. Simulation Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Abbreviations

| HJ-DTMOS | Si/SiC heterojunction double-trench MOSFET |

| Con-DTMOS | Conventional double-trench MOSFET |

| HJD | Heterojunction diode |

| SBD | Schottky barrier diode |

| JBS | Junction barrier Schottky diode |

| MPS | Merged PiN/Schottky diode |

| MCD | MOS-channel diode |

| DioMOS | Diode-integrated MOSFET |

| CSL | Current spreading layer |

| SAB | Surface activation bonding |

| ALD | Atomic layer deposition |

| SRH | Shockley–Read–Hall recombination |

| ΔEc | Conduction-band offset at Si/SiC heterojunction |

| ΔEv | Valence-band offset at Si/SiC heterojunction |

| ΦBN | Electron barrier height of heterojunction |

| k | Relative permittivity of gate dielectric |

| Ron,sp | Specific on-resistance |

| BV | Breakdown voltage |

| Von | Turn-on voltage |

| Vds | Drain-to-source voltage |

| Ids | Drain-to-source current |

| Isd | Source-to-drain current |

| Vgs | Gate-to-source voltage |

| Vth | Threshold voltage |

| Ileak | Leakage current |

| A–A′, B–B′ | Cut-line labels in figures |

| C–C′, D–D′, E–E′, F–F′, G–G′ | Electric-field profile cut-lines |

References

- She, X.; Huang, A.Q.; Lucía, O.; Ozpineci, B. Review of Silicon Carbide Power Devices and Their Applications. IEEE Trans. Ind. Electron. 2017, 64, 8193–8205. [Google Scholar] [CrossRef]

- Spaziani, L.; Lu, L. Silicon, GaN and SiC: There’s room for all: An application space overview of device considerations. In Proceedings of the 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Chicago, IL, USA, 13–17 May 2018; pp. 8–11. [Google Scholar] [CrossRef]

- Millán, J.; Godignon, P.; Perpiñà, X.; Pérez-Tomás, A.; Rebollo, J. A Survey of Wide Bandgap Power Semiconductor Devices. IEEE Trans. Power Electron. 2014, 29, 2155–2163. [Google Scholar] [CrossRef]

- Karki, U.; González-Santini, N.S.; Peng, F.Z. Effect of Gate-Oxide Degradation on Electrical Parameters of Silicon Carbide MOSFETs. IEEE Trans. Electron Devices 2020, 67, 2544–2552. [Google Scholar] [CrossRef]

- Tachiki, K.; Kimoto, T. Improvement of Both n- and p-Channel Mobilities in 4H-SiC MOSFETs by High-Temperature N2 Annealing. IEEE Trans. Electron Devices 2021, 68, 638–644. [Google Scholar] [CrossRef]

- Zhang, Y.; Yuan, H.; Guo, J.; Yang, H.; Zhou, Y.; Du, F.; Liu, Y.; Liu, K.; Han, C.; Song, Q.; et al. Long-Term Lifetime Evolution Mechanism of 4H-SiC MOSFETs Under Nitric Oxide Annealing. IEEE Trans. Electron Devices 2024, 71, 7682–7688. [Google Scholar] [CrossRef]

- Sharmila, P.; Supraja, G.; Haripriya, D.; Sivamani, C.; Narayana, A.L. Silicon carbide MOSFETs: A critical review of applications, technological advancements, and future perspectives. Micro Nanostruct. 2025, 202, 208126. [Google Scholar] [CrossRef]

- Fiorenza, P.; Giannazzo, F.; Roccaforte, F. Characterization of SiO2/4H-SiC Interfaces in 4H-SiC MOSFETs: A Review. Energies 2019, 12, 2310. [Google Scholar] [CrossRef]

- Modic, A.; Liu, G.; Ahyi, A.C.; Zhou, Y.; Xu, P.; Hamilton, M.C.; Williams, J.R.; Feldman, L.C.; Dhar, S. High channel mobility 4H-SiC MOSFETs by antimony counter-doping. IEEE Electron Device Lett. 2014, 35, 894–896. [Google Scholar] [CrossRef]

- Okamoto, D.; Sometani, M.; Harada, S.; Kosugi, R.; Yonezawa, Y.; Yano, H. Improved Channel Mobility in 4H-SiC MOSFETs by Boron Passivation. IEEE Electron Device Lett. 2014, 35, 1176–1178. [Google Scholar] [CrossRef]

- Chen, L.; Guy, O.J.; Jennings, M.R.; Igic, P.; Wilks, S.P.; Mawby, P.A. Study of a novel Si/SiC hetero-junction MOSFET. Solid-State Electron. 2007, 51, 662–666. [Google Scholar] [CrossRef]

- Duan, B.; Yang, X.; Lv, J.; Yang, Y. Novel SiC/Si Heterojunction Power MOSFET With Breakdown Point Transfer Terminal Technology by TCAD Simulation Study. IEEE Trans. Electron Devices 2018, 65, 3388–3393. [Google Scholar] [CrossRef]

- Chen, H.; Zhang, Y.; Zhou, R.; Wang, Z.; Lu, C.; Li, Z.; Zhang, B. A Novel Low On–State Resistance Si/4H–SiC Heterojunction VDMOS with Electron Tunneling Layer Based on a Discussion of the Hetero–Transfer Mechanism. Crystals 2023, 13, 778. [Google Scholar] [CrossRef]

- Wang, N.; Hu, X.; Xu, Y.; Li, T. A Triple RESURF Si/SiC HeteroJunction LDMOS and Its Analytical Model. Int. J. Numer. Model. Electron. Netw. Devices Fields 2025, 38, e70039. [Google Scholar] [CrossRef]

- Park, S.; Mun, S.; Kim, K.H.; Yang, M.; Chun, Y.T.; Yi, S.N.; Ahn, H.S.; Lee, J.H.; Jang, Y.-S.; Lee, W.J.; et al. Growth of hexagonal-shape Si on a 4H–SiC substrate by mixed-source hydride vapor phase epitaxy. J. Korean Phys. Soc. 2024, 84, 198–207. [Google Scholar] [CrossRef]

- Chan, C.W.; Li, F.; Sanchez, A.; Mawby, P.A.; Gammon, P.M. Comparative Study of RESURF Si/SiC LDMOSFETs for High-Temperature Applications Using TCAD Modeling. IEEE Trans. Electron Devices 2017, 64, 3713–3718. [Google Scholar] [CrossRef]

- Zhang, W.; Zhang, C.; Wu, J.; Yang, F.; An, Y.; Hu, F.; Fan, J. Low temperature hydrophilic SiC wafer level direct bonding for ultrahigh-voltage device applications. Micromachines 2021, 12, 1575. [Google Scholar] [CrossRef] [PubMed]

- Lei, F.; Lu, W.; Liu, F.; Li, B.; Wang, J.; Li, J. Investigation on Wafer Heterogeneous Bonding Process and Performance of CMOS Integrated Circuit on Silicon Carbide Substrate. In Proceedings of the 2024 25th International Conference on Electronic Packaging Technology (ICEPT), Tianjin, China, 7–9 August 2024; pp. 1–5. [Google Scholar] [CrossRef]

- Shigekawa, N.; Liang, J.; Ohno, Y. Heterojunctions fabricated by surface activated bonding–dependence of their nanostructural and electrical characteristics on thermal process. Jpn. J. Appl. Phys. 2022, 61, 120101. [Google Scholar] [CrossRef]

- Liang, J.; Shimizu, S.; Nishida, S.; Shigekawa, N.; Arai, M. 4H-SiC/Si Heterojunction Bipolar Transistors Fabricated by Surface Activated Bonding. ECS Solid State Lett. 2015, 4, Q55. [Google Scholar] [CrossRef]

- Gammon, P.M.; Chan, C.W.; Li, F.; Gity, F.; Trajkovic, T.; Pathirana, V.; Flandre, D.; Kilchytska, V. Development, characterisation and simulation of wafer bonded Si-on-SiC substrates. Mater. Sci. Semicond. Process 2018, 78, 69–74. [Google Scholar] [CrossRef]

- Guo, R.; Xu, B.; Mu, F.; Shiomi, J. Enhancing and mapping thermal boundary conductance across bonded Si-SiC interface. Appl. Surf. Sci. 2025, 682, 161724. [Google Scholar] [CrossRef]

- Huang, S.; Liu, F.; Liu, J.; Mao, R.; Zhang, J.; Liu, Z.; Sun, F.; Wang, Z.; Gao, P. Direct Bonding of 6-in. SiC/Si Wafer with Enhanced Thermal Interface. ACS Appl. Mater. Interfaces 2025, 17, 46409–46416. [Google Scholar] [CrossRef]

- Long, Y.T.; Chen, Y.; Wang, P.K.; Hou, B.; He, H. A Novel Insight Into the Mechanism of Bipolar Degradation in 4H-SiC MOSFET. IEEE Electron Device Lett. 2025, 46, 464–467. [Google Scholar] [CrossRef]

- Palanisamy, S.; Basler, T.; Lutz, J.; Künzel, C.; Wehrhahn-Kilian, L.; Elpelt, R. Investigation of the bipolar degradation of SiC MOSFET body diodes and the influence of current density. In Proceedings of the 2021 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 21–25 March 2021; pp. 1–6. [Google Scholar] [CrossRef]

- Sung, W.; Baliga, B.J. Monolithically Integrated 4H-SiC MOSFET and JBS Diode (JBSFET) Using a Single Ohmic/Schottky Process Scheme. IEEE Electron Device Lett. 2016, 37, 1605–1608. [Google Scholar] [CrossRef]

- Todaka, S.; Matsui, K.; Aiba, R.; Yano, H.; Iwamuro, N.; Baba, M.; Harada, S. Experimental and Numerical Demonstration of Superior RBSOAs in 1.2 kV SiC Trench and SBD-integrated Trench MOSFETs. In Proceedings of the 2021 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Nagoya, Japan, 30 May–3 June 2021; pp. 219–222. [Google Scholar] [CrossRef]

- Yu, Y.R.; Liu, T.; Ma, R.Y.; Cheng, Z.J.; Tao, J.Y.; Guo, J.W.; Wu, H.; Hu, S.D. A Novel Asymmetric Trench SiC MOSFET With an Integrated JFET for Improved Reverse Conduction Performance. IEEE Trans. Electron Devices 2024, 71, 1546–1552. [Google Scholar] [CrossRef]

- Sundaresan, S.; Park, J.; Mulpuri, V.; Singh, R. Performance and Robustness of 6500 V SiC DMOSFETs with Integrated MPS diodes. In Proceedings of the 2021 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Nagoya, Japan, 30 May–3 June 2021; pp. 235–238. [Google Scholar] [CrossRef]

- Uchida, M.; Horikawa, N.; Tanaka, K.; Takahashi, K.; Kiyosawa, T.; Hayashi, M.; Niwayama, M.; Kusumoto, O.; Adachi, K.; Kudou, C.; et al. Novel SiC power MOSFET with integrated unipolar internal inverse MOS-channel diode. In Proceedings of the 2011 International Electron Devices Meeting, Washington, DC, USA, 5–7 December 2011; pp. 26.6.1–26.6.4. [Google Scholar] [CrossRef]

- Zhou, X.; Gong, H.; Jia, Y.; Hu, D.; Wu, Y.; Xia, T.; Pang, H.; Zhao, Y. SiC Planar MOSFETs With Built-In Reverse MOS-Channel Diode for Enhanced Performance. IEEE J. Electron Devices Soc. 2020, 8, 619–625. [Google Scholar] [CrossRef]

- Deng, X.; Xu, X.; Li, X.; Li, X.; Wen, Y.; Chen, W. A Novel SiC MOSFET Embedding Low Barrier Diode With Enhanced Third Quadrant and Switching Performance. IEEE Electron Device Lett. 2020, 41, 1472–1475. [Google Scholar] [CrossRef]

- Liang, S.; Yu, H.; Liu, H.; Wang, Y.; Wang, J. A novel SiC power MOSFET with integrated polySi/SiC heterojunction freewheeling diode. Semicond. Sci. Technol. 2021, 36, 095017. [Google Scholar] [CrossRef]

- Yu, H.; Liang, S.; Liu, H.; Wang, J.; Shen, Z.J. Numerical Study of SiC MOSFET With Integrated n-/n-Type Poly-Si/SiC Heterojunction Freewheeling Diode. IEEE Trans. Electron Devices 2021, 68, 4571–4576. [Google Scholar] [CrossRef]

- Robertson, J.; Wallace, R.M. High-K materials and metal gates for CMOS applications. Mater. Sci. Eng. R Rep. 2015, 88, 1–41. [Google Scholar] [CrossRef]

- Wei, J.; Liu, S.; Tong, J.; Zhang, X.; Sun, W.; Huang, A.Q. Understanding Short-Circuit Failure Mechanism of Double-Trench SiC Power MOSFETs. IEEE Trans. Electron Devices 2020, 67, 5593–5599. [Google Scholar] [CrossRef]

- Lan, Z.; Ou, Y.; Hu, X.; Liu, D. A Novel 4H-SiC Asymmetric MOSFET with Step Trench. Micromachines 2024, 15, 724. [Google Scholar] [CrossRef] [PubMed]

- Yoon, J.; Kim, K. High-performance SiC MOSFET embedded heterojunction diode with electric field protection region. Semicond. Sci. Technol. 2022, 37, 015014. [Google Scholar] [CrossRef]

- Jung, E.S.; Yoo, J.; Choi, T.M.; Lee, H.R.; Lee, C.Y.; Kim, D.H.; Pyo, S.G. Performance variation with pristine and doped high-k materials via atomic layer deposition. Int. J. Appl. Ceram. Technol. 2025, 22, e15001. [Google Scholar] [CrossRef]

| Parameters | HJ-DTMOS | Con-DTMOS |

|---|---|---|

| Cell pitch (μm) | 3.6 | 3.6 |

| Si layer thickness(μm) | 0.7 | - |

| SiC layer thickness(μm) | 12.8 | 13.5 |

| N-drift thickness (μm) | 10 | 10 |

| N-drift doping (cm−3) | 5 × 1015 | 5 × 1015 |

| CSL thickness (μm) | 0.8 | 0.8 |

| CSL doping (cm−3) | 1 × 1016 | 1 × 1016 |

| P-ch thickness (μm) | 0.5 | 0.5 |

| P-ch doping (cm−3) | 2 × 1017 | 2 × 1017 |

| Trench depth (μm) | 1 | 1 |

| Trench width (μm) | 1 | 1 |

| Gate oxide thickness (nm) | 50 | 50 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kang, Y.; Liu, D.; Li, T.; Qiu, Z.; Lu, S.; Hu, X. A Si/SiC Heterojunction Double-Trench MOSFET with Improved Conduction Characteristics. Micromachines 2025, 16, 1335. https://doi.org/10.3390/mi16121335

Kang Y, Liu D, Li T, Qiu Z, Lu S, Hu X. A Si/SiC Heterojunction Double-Trench MOSFET with Improved Conduction Characteristics. Micromachines. 2025; 16(12):1335. https://doi.org/10.3390/mi16121335

Chicago/Turabian StyleKang, Yi, Dong Liu, Tianci Li, Zhaofeng Qiu, Shan Lu, and Xiarong Hu. 2025. "A Si/SiC Heterojunction Double-Trench MOSFET with Improved Conduction Characteristics" Micromachines 16, no. 12: 1335. https://doi.org/10.3390/mi16121335

APA StyleKang, Y., Liu, D., Li, T., Qiu, Z., Lu, S., & Hu, X. (2025). A Si/SiC Heterojunction Double-Trench MOSFET with Improved Conduction Characteristics. Micromachines, 16(12), 1335. https://doi.org/10.3390/mi16121335