Sintering for High Power Optoelectronic Devices

Abstract

1. Introduction

2. Materials and Methods

2.1. Sample Preparation

2.1.1. Materials

2.1.2. Synthesis and Characterization of Cu Particle Free Inks

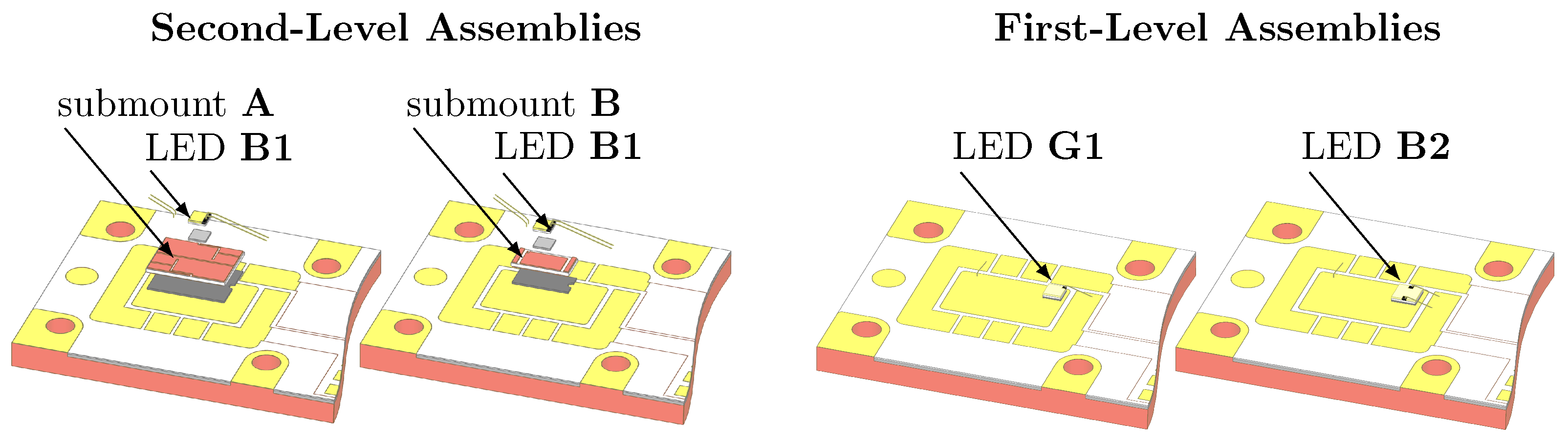

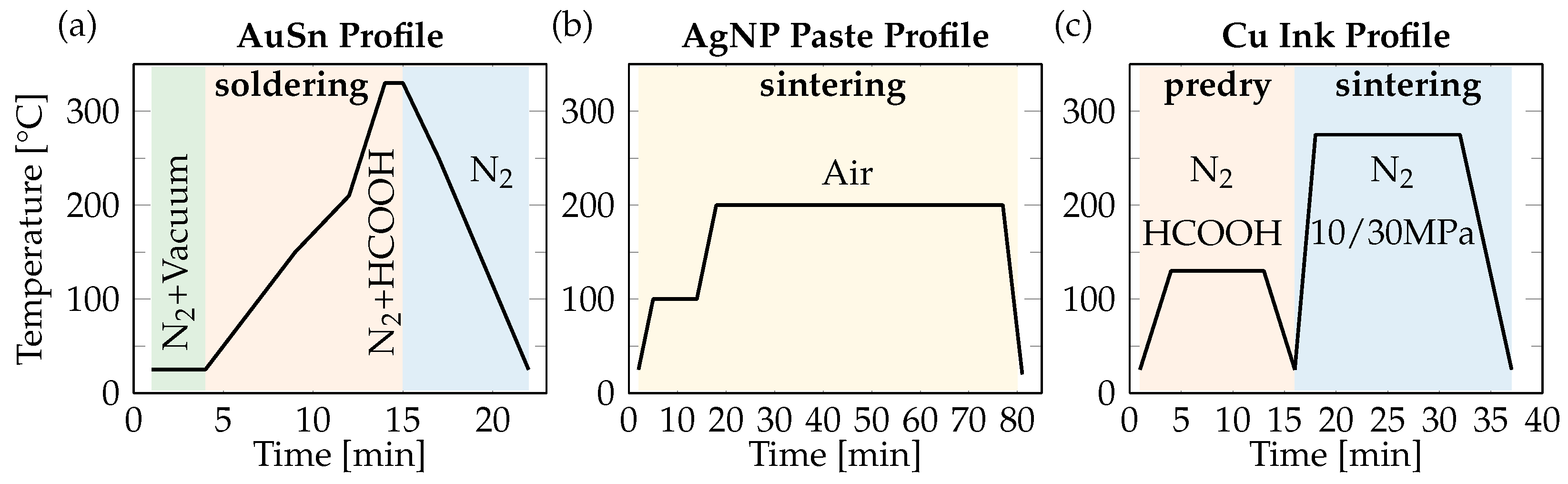

2.1.3. Sample Assembly

2.2. Analysis Methods

2.2.1. Interconnect Quality Analysis Methods

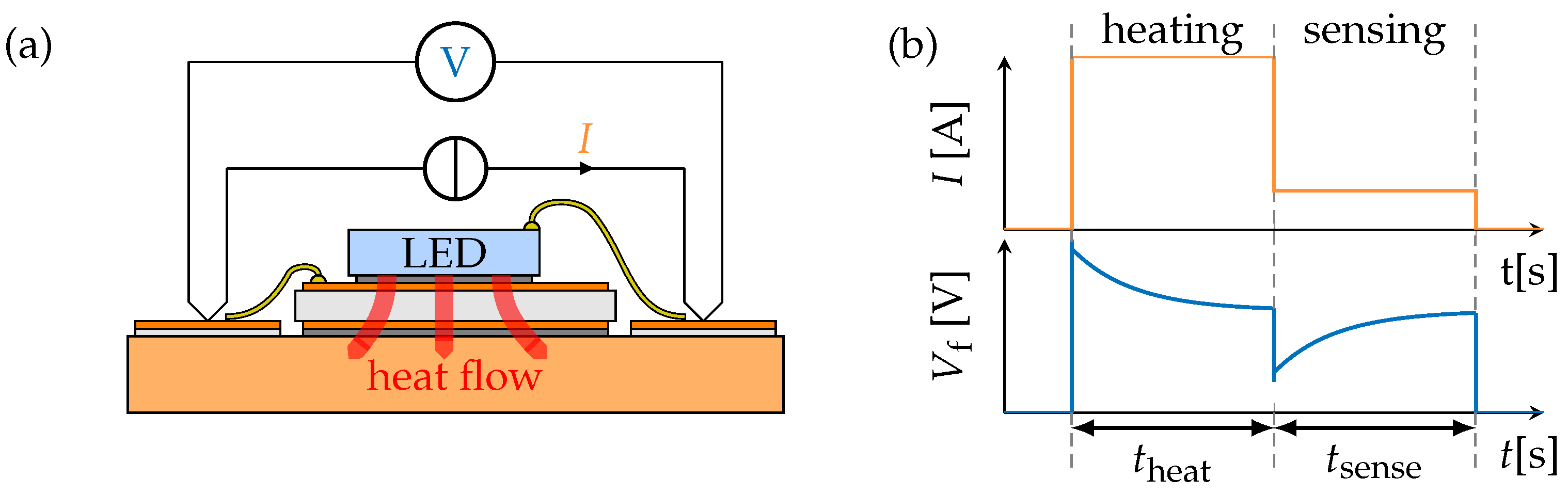

2.2.2. Transient Thermal Analysis

3. Results

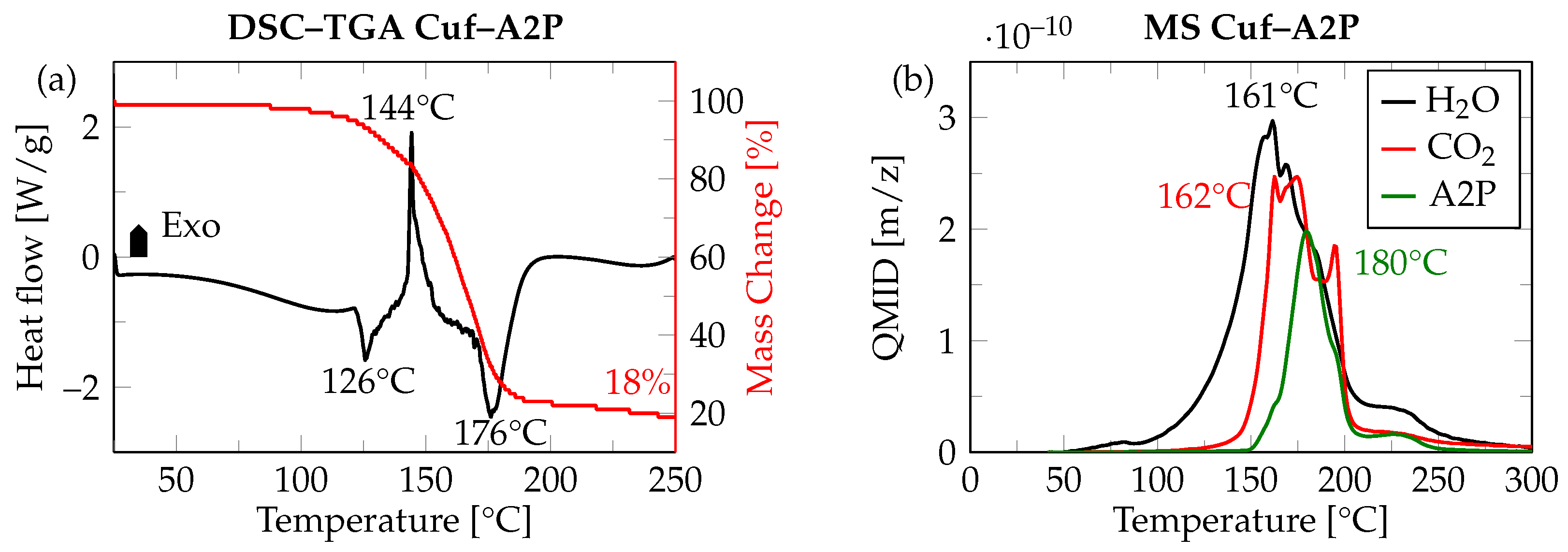

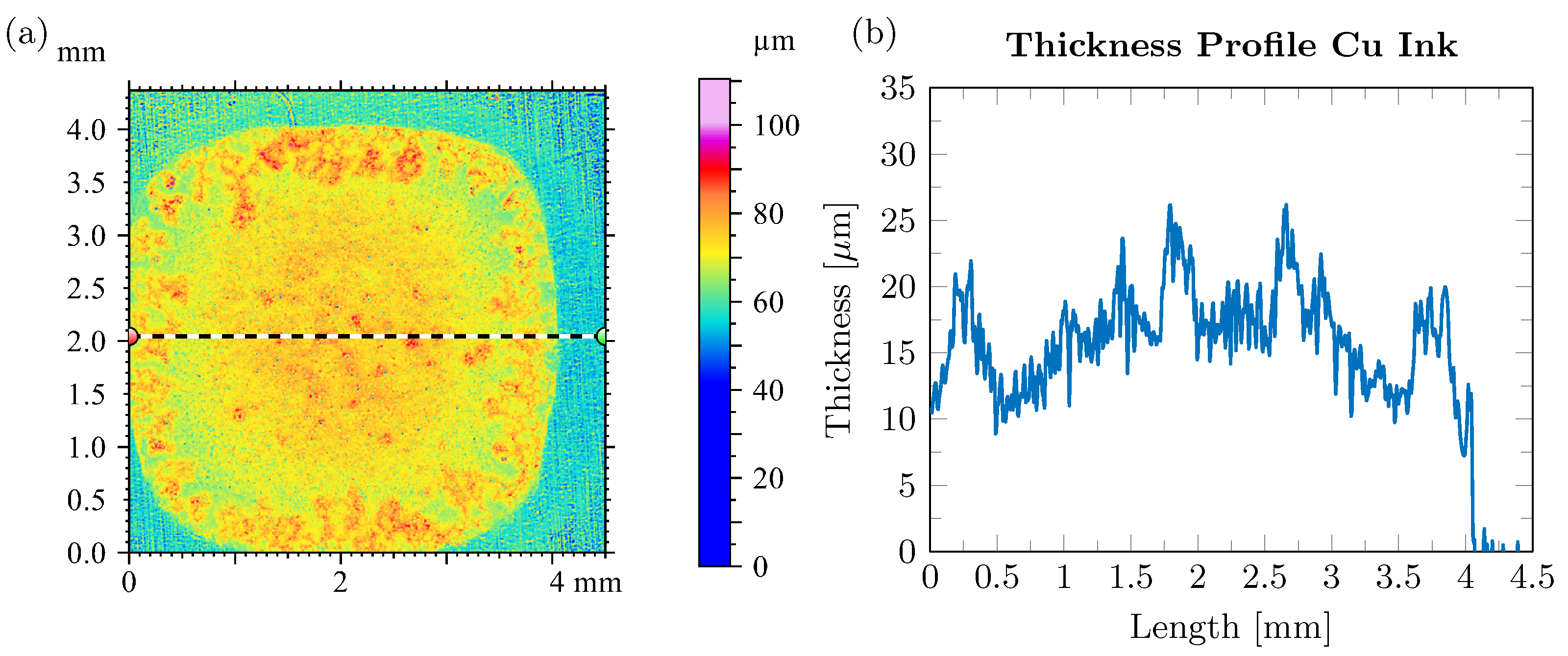

3.1. Realization of Ultra-Thin Sinterable Cu Layer Using Particle Free Cu Ink

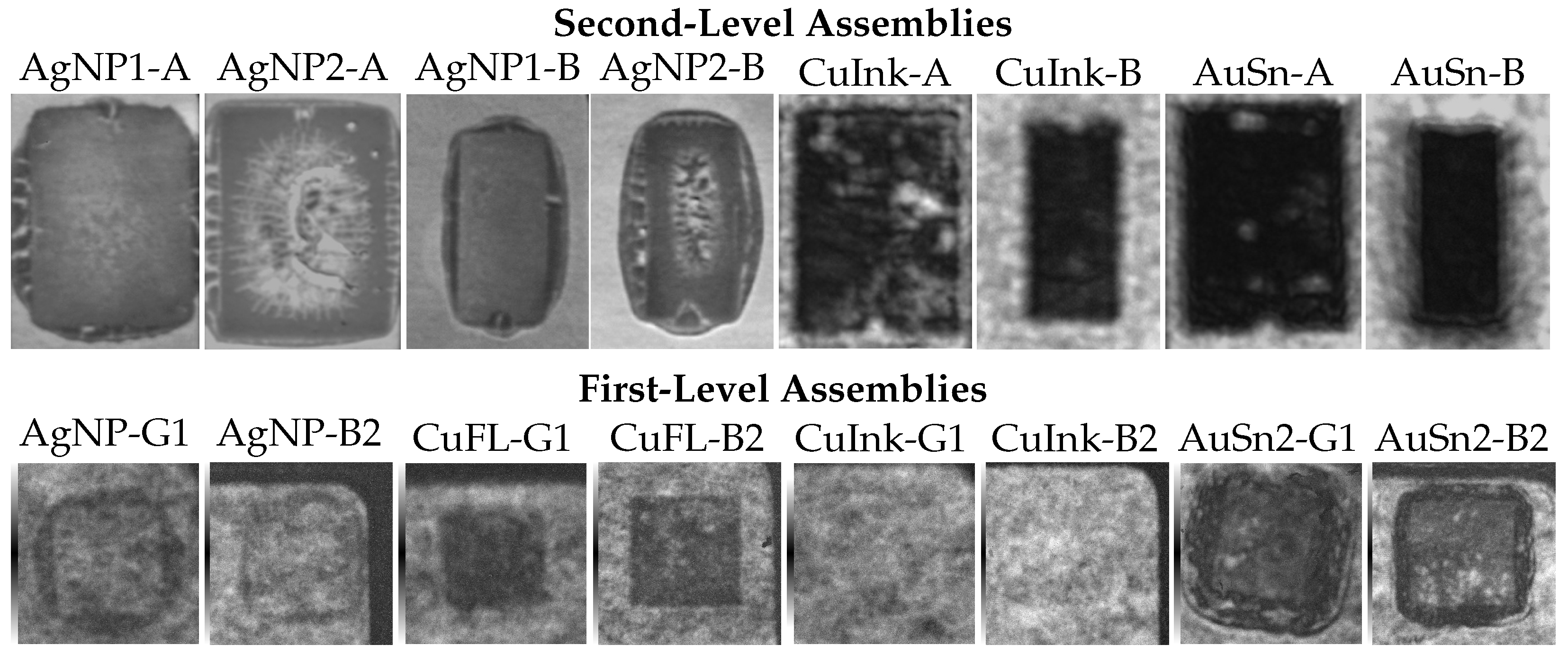

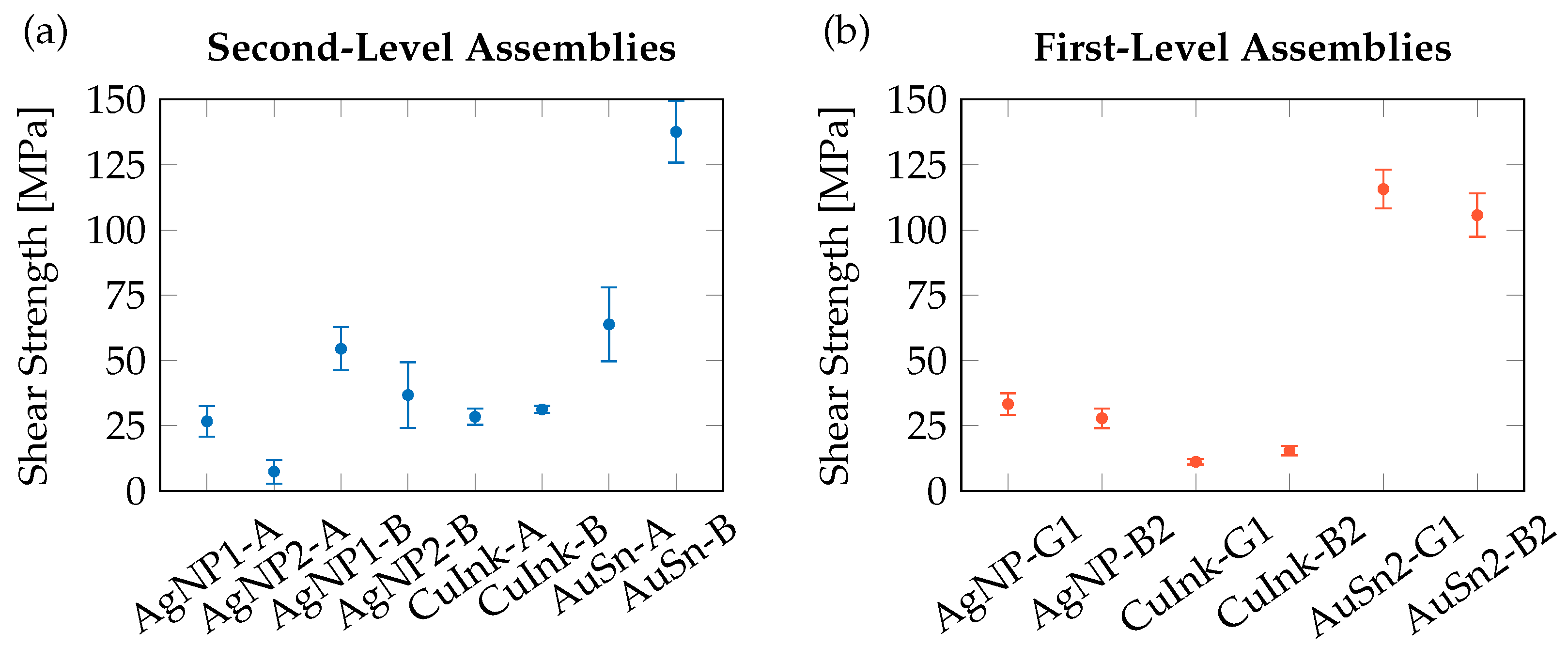

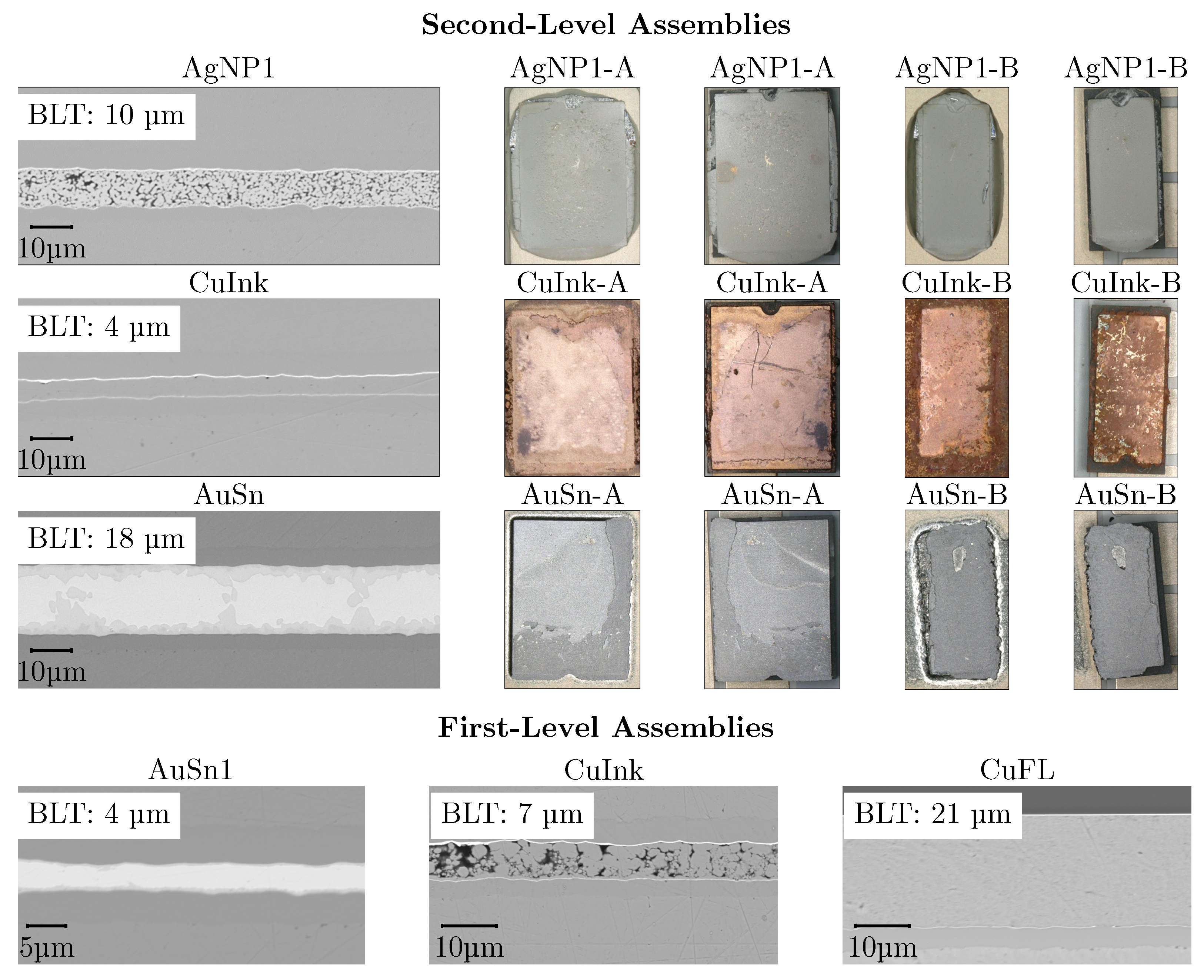

3.2. Analysis of Soldered and Sintered Interconnects

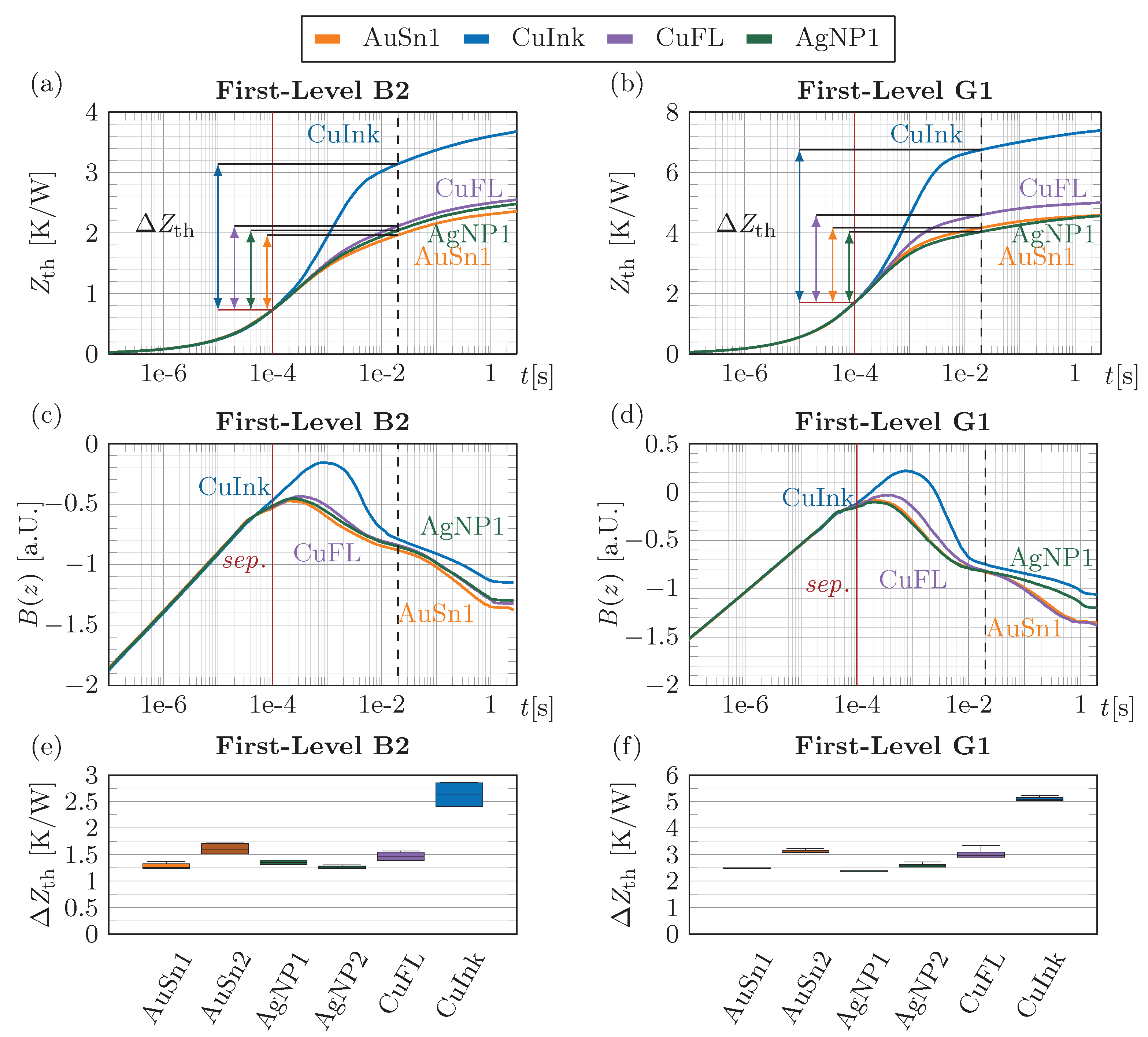

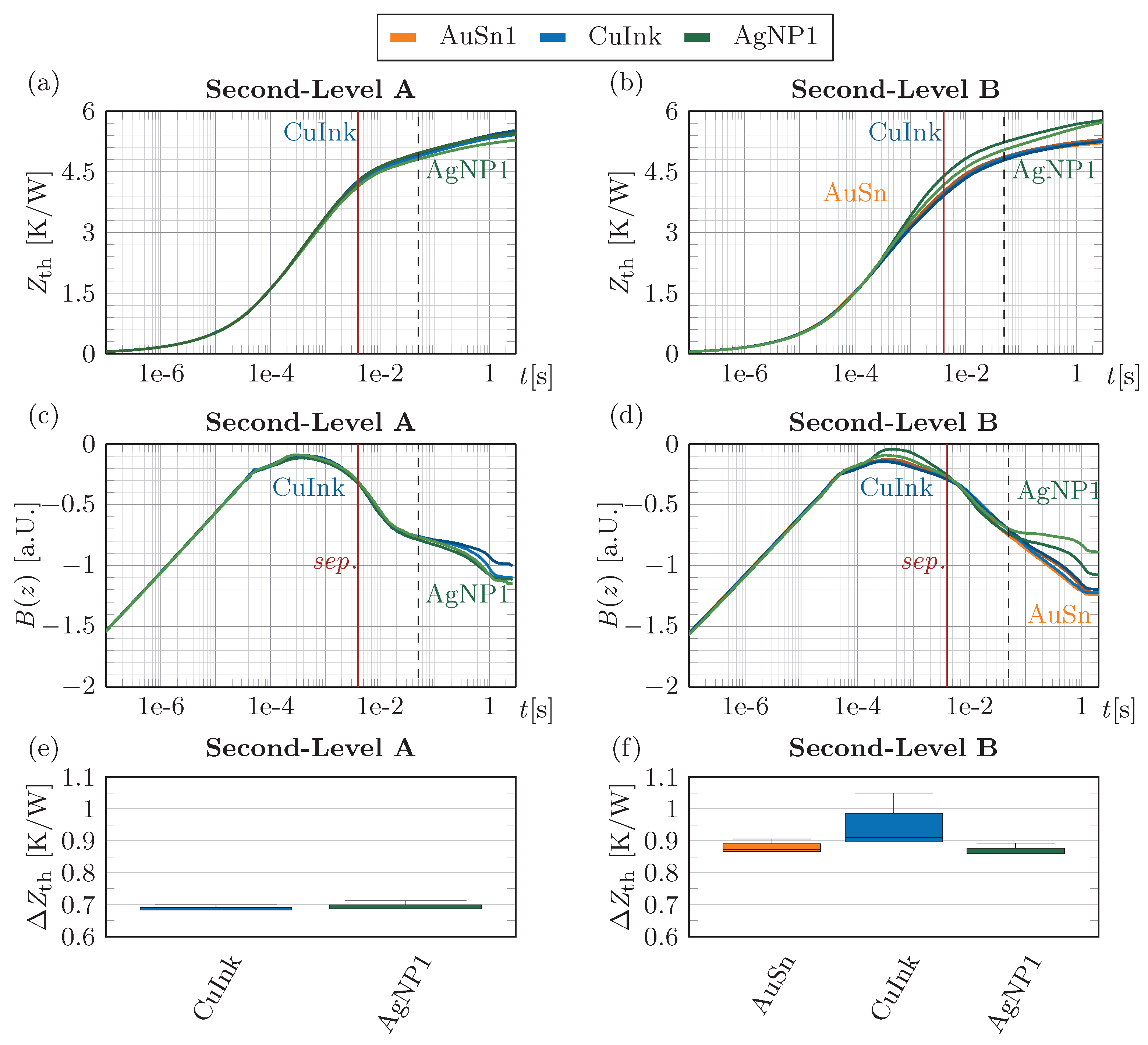

3.3. Transient Thermal Analysis Results

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Zakel, E.; Reichl, H. Flip Chip Assembly Using the Gold, Gold-Tin and Nickel-Gold Metallurgy. In Flip Chip Technologies; Lau, J., Ed.; McGraw-Hill: Columbus, OH, USA, 1995. [Google Scholar]

- Weiss, S.; Bader, V.; Azdasht, G.; Kasulke, P.; Zakel, E.; Reichl, H. Fluxless die bonding of high power laser bars using the AuSn-metallurgy. In Proceedings of the 1997 Proceedings 47th Electronic Components and Technology Conference, San Jose, CA, USA, 18–21 May 1997; pp. 780–787. [Google Scholar] [CrossRef]

- Elger, G.; Hutter, M.; Oppermann, H.; Aschenbrenner, R.; Reichl, H.; Jaeger, E. Development of an assembly process and reliability investigations for flip-chip LEDs using the AuSn soldering. Microsyst. Technol. 2002, 7, 239–243. [Google Scholar] [CrossRef]

- Hanss, A.; Elger, G. Residual free solder process for fluxless solder pastes. In Proceedings of the 2017 21st European Microelectronics and Packaging Conference (EMPC) and Exhibition, Warsaw, Poland, 10–13 September 2017; pp. 1–8. [Google Scholar] [CrossRef]

- Siow, K.S. Are Sintered Silver Joints Ready for Use as Interconnect Material in Microelectronic Packaging? J. Electron. Mater. 2014, 43, 947–961. [Google Scholar] [CrossRef]

- Cui, Z.; Jia, Q.; Zhang, H.; Wang, Y.; Ma, L.; Zou, G.; Guo, F. Review on Shear Strength and Reliability of Nanoparticle Sintered Joints for Power Electronics Packaging. J. Electron. Mater. 2024, 53, 2703–2726. [Google Scholar] [CrossRef]

- Schneider, M.; Leyrer, B.; Herbold, C.; Maikowske, S. High power density LED modules with silver sintering die attach on aluminum nitride substrates. In Proceedings of the 2014 IEEE 64th Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 27–30 May 2014; pp. 203–208. [Google Scholar] [CrossRef]

- Kuramoto, M.; Ogawa, S.; Niwa, M.; Kim, K.S.; Suganuma, K. New Silver Paste for Die-Attaching Ceramic Light-Emitting Diode Packages. IEEE Trans. Compon. Packag. Manuf. Technol. 2011, 1, 653–659. [Google Scholar] [CrossRef]

- Yan, Y.; Chen, X.; Liu, X.; Mei, Y.; Lu, G.Q. Die Bonding of High Power 808 nm Laser Diodes With Nanosilver Paste. J. Electron. Packag. 2012, 134, 041003. [Google Scholar] [CrossRef]

- Yan, Y.; Chen, X.; Liu, X.; Lu, G.Q. Die bonding of single emitter semiconductor laser with nano-scale silver paste. In Proceedings of the 2011 12th International Conference on Electronic Packaging Technology and High Density Packaging, Shanghai, China, 8–11 August 2011; pp. 1–5. [Google Scholar] [CrossRef]

- Zhalefar, P.; Dadoo, A.; Nazerian, M.; Parniabaran, A.; Mahani, A.G.; Akhlaghifar, M.; Abbasi, P.; Zabhi, M.S.; Sabbaghzadeh, J. Study on Effects of Solder Fluxes on Catastrophic Mirror Damages During Laser Diode Packaging. IEEE Trans. Compon. Packag. Manuf. Technol. 2013, 3, 46–51. [Google Scholar] [CrossRef]

- Chew, L.M.; Schmitt, W. High reliable and high bonding strength of silver sintered joints on copper surfaces by pressure sintering under air atmosphere. IMAPSource Proc. 2018, 2018, 434–441. [Google Scholar] [CrossRef]

- Wang, T.; Chen, X.; Lu, G.Q.; Lei, G.Y. Low-Temperature Sintering with Nano-Silver Paste in Die-Attached Interconnection. J. Electron. Mater. 2007, 36, 1333–1340. [Google Scholar] [CrossRef]

- Pittroff, W.; Erbert, G.; Klein, A.; Staske, R.; Sumpf, B.; Traenkle, G. Mounting of laser bars on copper heat sinks using Au/Sn solder and CuW submounts. In Proceedings of the 52nd Electronic Components and Technology Conference 2002. (Cat. No.02CH37345), San Diego, CA, USA, 28–31 May 2002; pp. 276–281. [Google Scholar] [CrossRef]

- Gharaibeh, M.A.; Wilde, J. Applying Anand versus Garofalo creep constitutive models for simulating sintered silver die attachments in power electronics. J. Strain Anal. Eng. Des. 2024, 59, 31–43. [Google Scholar] [CrossRef]

- Bhogaraju, S.K.; Ugolini, F.; Belponer, F.; Greci, A.; Elger, G. Reliability of Copper Sintered Interconnects Under Extreme Thermal Shock Conditions. In Proceedings of the 2023 24th European Microelectronics and Packaging Conference and Exhibition (EMPC), Cambridge, UK, 11–14 September 2023; pp. 1–5. [Google Scholar] [CrossRef]

- Mokhtari, O.; Conti, F.; Saccon, R.; Kandaswamy, S.V.; Elger, G.; Bhogaraju, S.K. Formic acid and formate salts for chemical vapor deposition of copper on glass substrates under atmospheric pressure. New J. Chem. 2021, 45, 20133–20139. [Google Scholar] [CrossRef]

- Saha, R.K.; Aqeel, H.; Elger, G.; Thomas, G.; Schlenk, R. Development of a Low Temperature Sinterable Cu Paste Based on Micro Scale Flakes. In Proceedings of the 2025 IEEE 75th Electronic Components and Technology Conference (ECTC), Dallas, TX, USA, 27–30 May 2025. [Google Scholar] [CrossRef]

- JESD51-51; Implementation of the Electrical Test Method for the Measurement of Real Thermal Resistance and Impedance of Light Emitting Diodes with Exposed Cooling. JEDEC: Arlington, VA, USA, 2012.

- Hanss, A.; Schmid, M.; Elger, G. Transient thermal analysis as measurement method for IC package structural integrity. Chin. Phys. B 2015, 24, 068105. [Google Scholar] [CrossRef]

- Strickland, P.R. The Thermal Equivalent Circuit of a Transistor. IBM J. Res. Dev. 1959, 3, 35–45. [Google Scholar] [CrossRef]

- Hopkins, T.; Tiziani, R. Transient thermal impedance considerations in power semiconductor applications. In Proceedings of the Automotive Power Electronics, Dearborn, MI, USA, 28–29 January 1989; pp. 89–97. [Google Scholar] [CrossRef]

- Mohan, N.; Ahuir-Torres, J.I.; Bhogaraju, S.K.; Webler, R.; Kotadia, H.R.; Erdogan, H.; Elger, G. Decomposition mechanism and morphological evolution of in situ realized Cu nanoparticles in Cu complex inks. New J. Chem. 2024, 48, 6796–6808. [Google Scholar] [CrossRef]

- Mohan, N.; Ahuir-Torres, J.I.; Kotadia, H.; Elger, G. Laser sintering of Cu particle-free inks for high-performance printed electronics. Npj Flex. Electron. 2025, 9, 18. [Google Scholar] [CrossRef]

- Steinberger, F.; Mohan, N.; Rämer, O.; Elger, G. Low Temperature Die-Attach Bonding Using Copper Particle Free Inks. In Proceedings of the 2024 IEEE 10th Electronics System-Integration Technology Conference (ESTC), Berlin, Germany, 11–13 September 2024; pp. 1–7. [Google Scholar] [CrossRef]

- Chen, C.; Sun, M.; Cheng, Z.; Liang, Y. Microstructure Evolution and Shear Strength of the Cu/Au80Sn20/Cu Solder Joints with Multiple Reflow Temperatures. Materials 2022, 15, 780. [Google Scholar] [CrossRef] [PubMed]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Schwan, H.; Mohan, N.; Schmid, M.; Saha, R.K.; Klassen, H.; Müller, K.; Elger, G. Sintering for High Power Optoelectronic Devices. Micromachines 2025, 16, 1164. https://doi.org/10.3390/mi16101164

Schwan H, Mohan N, Schmid M, Saha RK, Klassen H, Müller K, Elger G. Sintering for High Power Optoelectronic Devices. Micromachines. 2025; 16(10):1164. https://doi.org/10.3390/mi16101164

Chicago/Turabian StyleSchwan, Hannes, Nihesh Mohan, Maximilian Schmid, Rocky Kumar Saha, Holger Klassen, Klaus Müller, and Gordon Elger. 2025. "Sintering for High Power Optoelectronic Devices" Micromachines 16, no. 10: 1164. https://doi.org/10.3390/mi16101164

APA StyleSchwan, H., Mohan, N., Schmid, M., Saha, R. K., Klassen, H., Müller, K., & Elger, G. (2025). Sintering for High Power Optoelectronic Devices. Micromachines, 16(10), 1164. https://doi.org/10.3390/mi16101164