Digital Electronic System-on-Chip Design: Methodologies, Tools, Evolution, and Trends

Abstract

1. Introduction

- ○

- Down-up or bottom-up: refers to the traditional way in which electronic systems were designed and built, i.e., starting at the bottom of an imaginary pyramid of building blocks and leading up to a complete system.

- ○

- Informatics: the explosion of data and information brought about by the evolution of memory and communications technologies, including the Internet, has led to a rising demand for increasingly complex electronic systems.

- ○

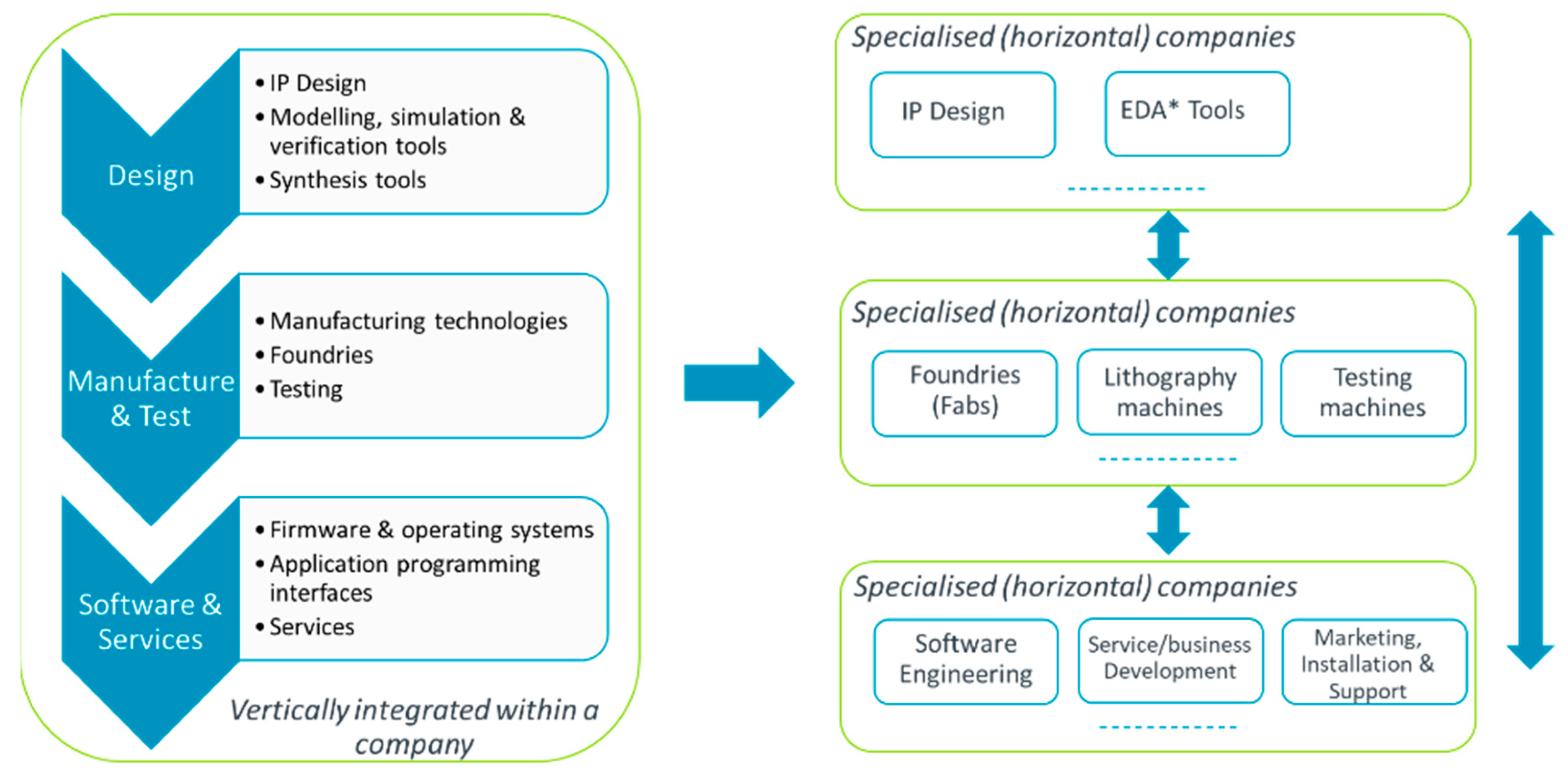

- Globalization: the relentless march of globalization since the 1980s has led to extreme specialization in various parts of supply chains, which in turn led to huge productivity gains leading to further pressures on complexity of use cases and underlying new electronic systems.

- ○

- Integration: the above led to the integration of more functionality into electronic systems, including chips which became system-on-chips over time, with various types of processors to suit multiple needs, e.g., CPUs, GPUs, DSPs; analogue front ends, e.g., for sensors or radio receivers; various memory types; transceivers; and switch fabrics. These are now increasingly built from chiplets integrated together in 2.5D or 3D under a single package.

- ○

- Top-down: the above is driving more top-down design methodologies, making use of higher levels of abstraction in design specification, optimization, verification, validation, and testing.

2. Overview of System-on-Chip Design Methodologies and Tools

2.1. Brief Historical Evolution of Electronic Systems Design Methodologies and Tools

2.2. Electronic Systems—Design Methods and Target Technologies

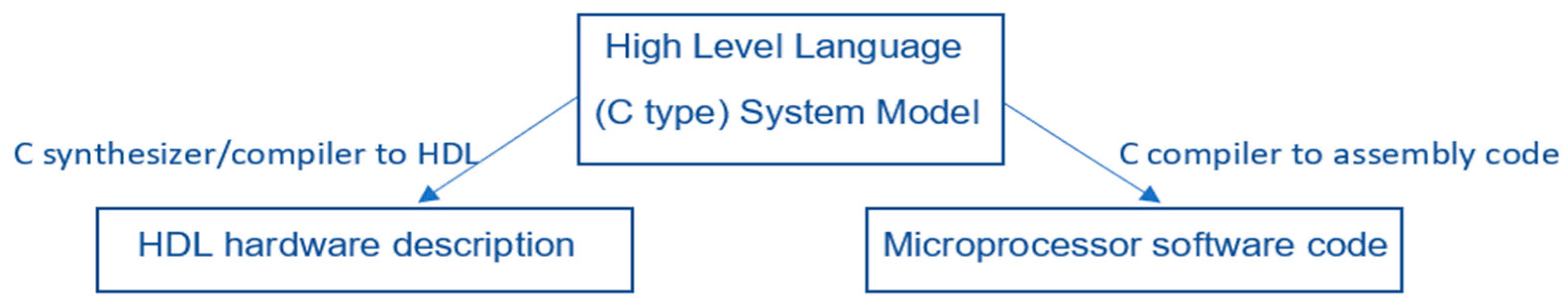

2.2.1. Text-Based High-Level Synthesis (HLS) Design Methods

2.2.2. Schematic-Based/Graphical Electronic System Level (ESL) Design Methods

2.2.3. FPGAs and ASICs

2.3. SoC Design Methodologies and Tools—Users and Enablers of AI

3. Industrial SoC Design

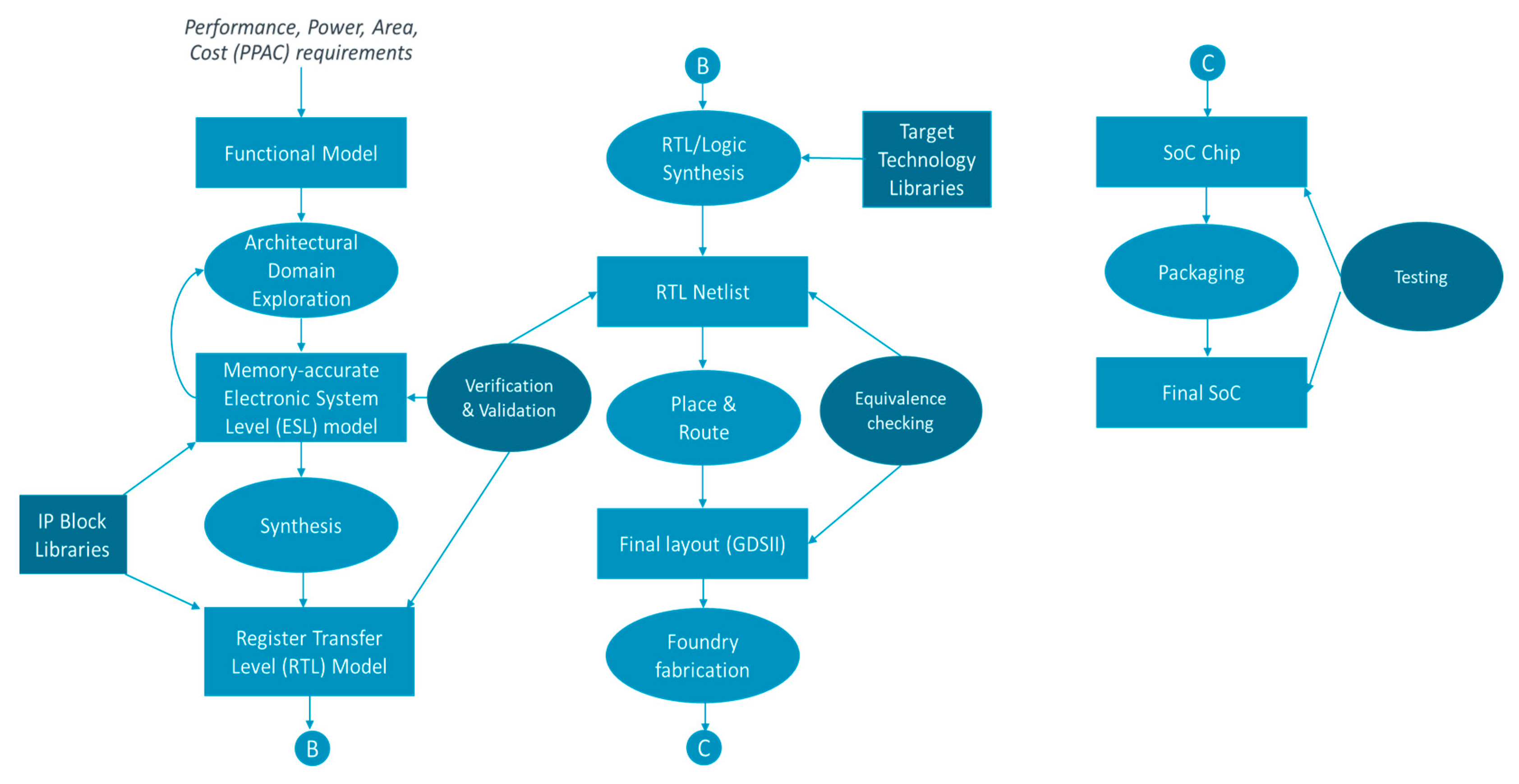

3.1. Fundamentals of SoC Design Flows

- -

- Marketing requirements: a gap is found in market offerings, e.g., an unserved segment of user needs, or opportunity for differentiation on cost or functionality compared to competition.

- -

- Incremental improvements from previous products, e.g., moving to next generation semiconductor node, or leveraging a new memory or interconnect technology.

- -

- New application area requirements, e.g., a new machine learning (ML)/artificial intelligence (AI) paradigm which can benefit from custom acceleration.

- -

- Which processor(s) or core(s) to use? Standard or custom, self-developed or from third party?

- -

- Which co-processors, if any, and which peripherals to use? Standard or custom, self-developed or from third party? Such co-processors include graphic processing units (GPUs), digital signal processors (DSPs), and neural processing units (NPUs).

- -

- Which software stack to use? This includes operating system choice if any, and availability of various software stack layers. This choice is intimately related to the choice of processors/co-processors.

- -

- Which memory types and hierarchy to use? Standard or custom, self-developed or from third party?

- -

- Which type of interconnect to use? Bus architecture or network-on-chip, standard or custom, self-developed or from third party?

- -

- Security of supply including support, e.g., if a third-party supplier of a component fails to deliver, for any reason, is there at least a second source supplier? Geopolitical turmoil is playing an increasingly important role in the choice of suppliers these days as export controls make certain technologies and suppliers impossible to access. In some industries, such as automotive, security of supply and support over a long period of time is a fundamental requirement.

- -

- Logic synthesis: Converting high level ESL models into register-transfer level (RTL) descriptions of logic e.g., processor, glue logic. Verilog [46] or VHDL [47] hardware description languages (HDLs) are generally used to capture RTL. The reuse of pre-designed pre-verified IP blocks is popular for faster time to market and economic efficiency. High-level synthesis (HLS) tools are also sometimes used to generate RTL from high level languages, e.g., C/C++ [48] or Python [49], although this is mostly performed in field programmable gate array (FPGA) designs [50]. Note that the RTL generated in this phase is called behavioral RTL, as it does not depend on any underlying implementation technology yet. The next synthesis phase will take the implementation technology into account.

- -

- Memory synthesis: converting high level memory transaction models into memory blocks with input/output ports, bit width information etc.

- -

- Interconnect synthesis: Interconnect plays a crucial role in meeting PPAC constraints; for example, logic occupancy can be severely impacted if logic cannot access the right data at the right time. This step is about converting the high-level communication needs into the right interconnect architecture, e.g., bus hierarchy or network-on-chip (NoC), with commensurate details. Here again, reuse of pre-designed pre-verified interconnect is popular.

3.2. The Role of the Intellectual Property (IP) Industry

3.3. Brief Comparative Analysis of SoC Design Methodologies and Tools

4. SoC Design Applications: Aerospace and Automotive as Case Study Areas

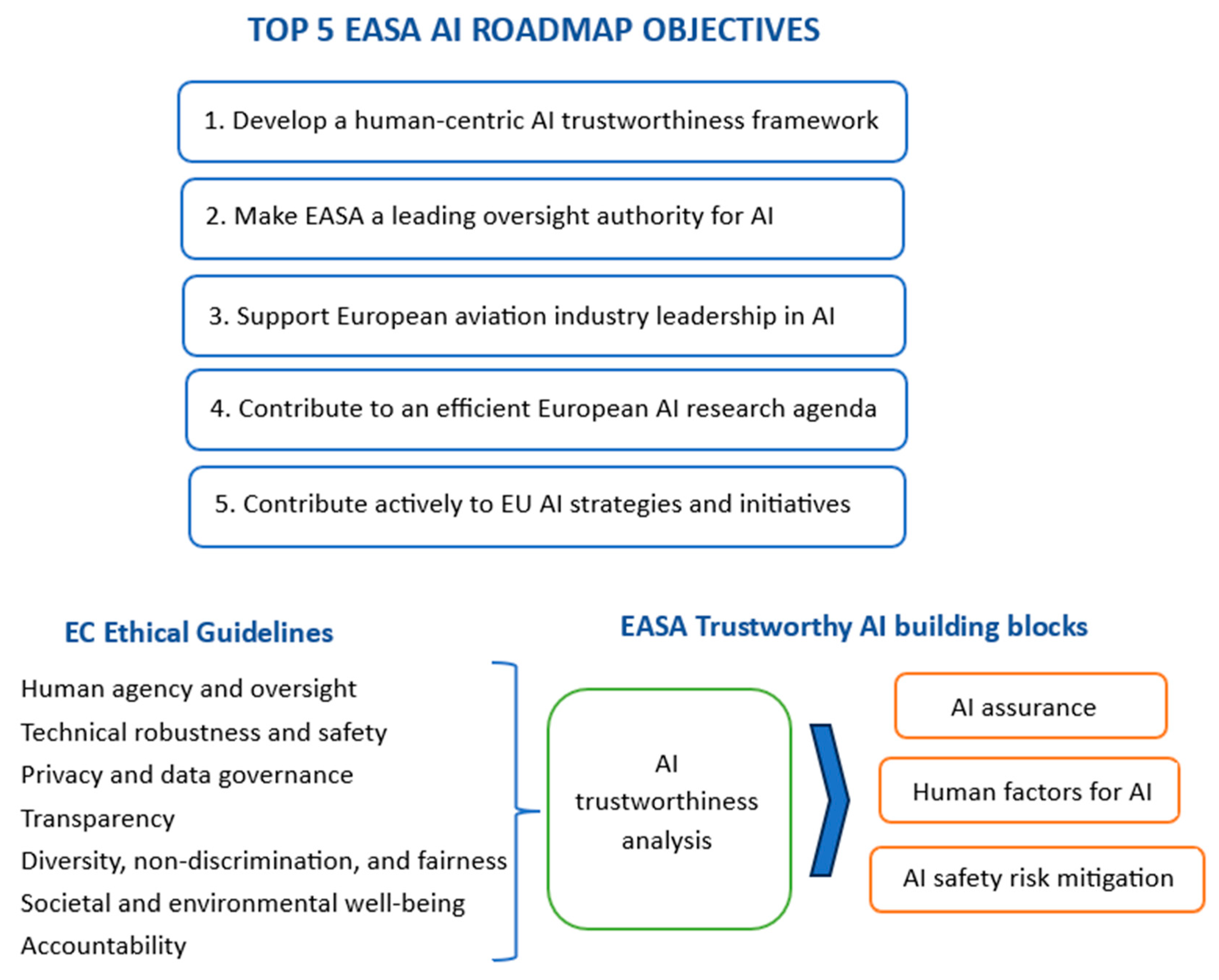

4.1. Aerospace Applications Domain

4.2. Automotive Applications Domain

5. Challenges and Future Trends in SoC Design

5.1. Current Challenges Alongside Technology Enablers

5.2. Emerging Needs: 4.0 Industrial Revolution and Cross-Disciplinary Applications

5.3. Future Trends on Chip Design—Holistic Systems Thinking and AI/ML-Enabled Design

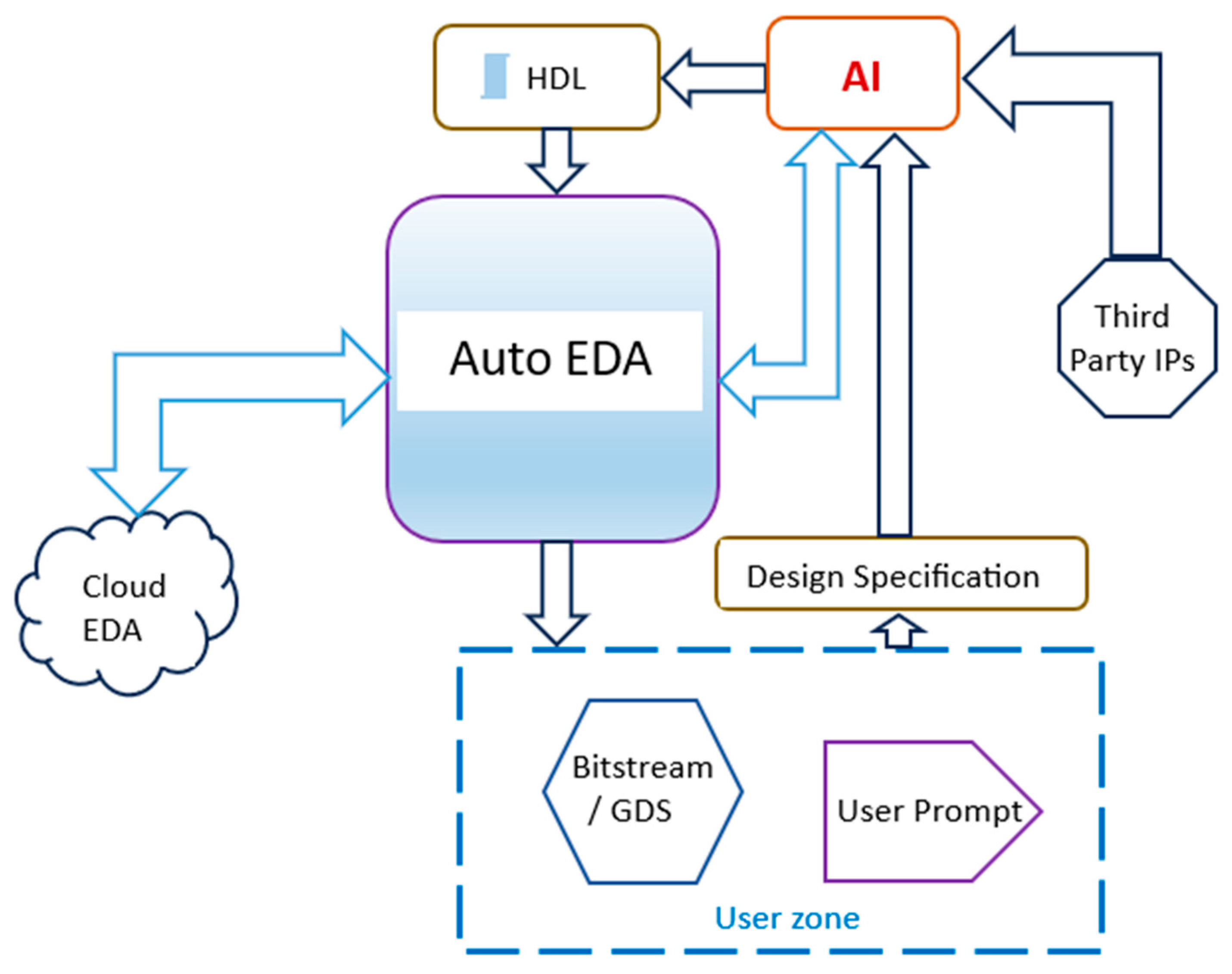

5.4. Generative Design; Prompt Engineering

6. Summary

Funding

Data Availability Statement

Conflicts of Interest

References

- Moore, G.E. Cramming more components onto integrated circuits. Electronics 1965, 38, 114–117. Available online: http://www.computer-architecture.org/textual/Moore-Cramming-More-Components-1965.pdf (accessed on 3 February 2024). [CrossRef]

- Cirstea, M.N. Modelling and Design of Digital Electronic Systems. In Proceedings of the IEEE International Conference on Development and Application Systems (DAS), Suceava, Romania, 19–21 May 2016; pp. 189–194. [Google Scholar]

- Spiliotis, K.; Gonçalves, J.E.; Saelens, D.; Baert, K.; Driesen, J. Electrical system architectures for building-integrated photovoltaics: A comparative analysis using a modelling framework in Modelica. Appl. Energy 2020, 261, 114247. [Google Scholar] [CrossRef]

- Helmns, D.; Blum, D.H.; Dutton, S.M.; Carey, V.P. Development and Validation of a Latent Thermal Energy Storage Model Using Modelica. Energies 2021, 14, 194. [Google Scholar] [CrossRef]

- Mo, Q.; Liu, F. Modeling and optimization for distributed microgrid based on Modelica language. Appl. Energy 2020, 279, 115766. [Google Scholar] [CrossRef]

- Zhang, K.; Feng, Z.; Zhou, H. A fast HDL model for full-custom FPGA verification. In Proceedings of the IEEE 12th International Conference on ASIC (ASICON), Guiyang, China, 25–28 October 2017; pp. 989–992. [Google Scholar]

- Monmasson, E.; Idkhajine, L.; Cirstea, M.N.; Bahri, L.; Tisan, A.; Naouar, W. FPGAs in Industrial Control Applications. IEEE Trans. Ind. Inform. 2011, 7, 224–244. [Google Scholar] [CrossRef]

- Muslim, F.B.; Ma, L.; Roozmeh, M.; Lavagno, L. Efficient FPGA Implementation of OpenCL High-Performance Computing Applications via High-Level Synthesis. IEEE Access 2017, 5, 2747–2762. [Google Scholar] [CrossRef]

- Lattuada, M.; Ferrandi, F. A Design Flow Engine for the Support of Customised Dynamic High Level Synthesis Flows. ACM Trans. Reconfigurable Technol. Syst. (TRETS) 2019, 12, 1–26. Available online: https://trets.acm.org/ (accessed on 7 January 2023). [CrossRef]

- Dossis, M.F. Formal ESL Synthesis for Control-Intensive Applications. Adv. Softw. Eng. 2012, 2012, 156907. [Google Scholar] [CrossRef]

- Cong, J.; Liu, B.; Neuendorffer, S.; Noguera, J.; Vissers, K.; Zhang, Z. High-Level Synthesis for FPGAs: From Prototyping to Deployment. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2011, 30, 473–491. [Google Scholar] [CrossRef]

- Škuta, M.; Macko, D.; Jelemenská, K. Automation of Dynamic Power Management in FPGA-Based Energy-Constrained Systems. IEEE Access 2020, 8, 165894–165903. [Google Scholar] [CrossRef]

- Valdes-Pena, M.D.; Rodriguez-Andina, J.J.; Manic, M. The Internet of Things: The Role of Reconfigurable Platforms. IEEE Ind. Electron. Mag. 2017, 11, 6–19. [Google Scholar] [CrossRef]

- Díaz, E.; Mateos, R.; Bueno, E.J.; Nieto, R. Enabling Parallelized-QEMU for Hardware/Software Co-Simulation Virtual Platforms. Electronics 2021, 10, 759. [Google Scholar] [CrossRef]

- Prasad, B.M.P.; Parane, K.; Talawar, B. FPGA friendly NoC simulation acceleration framework employing the hard blocks. Computing 2021, 103, 1791–1813. [Google Scholar] [CrossRef]

- Prabhu Prasad, B.M.; Parane, K.; Talawar, B. An Efficient FPGA-Based Network-on-Chip Simulation Framework Utilizing the Hard Blocks. Circuits Syst. Signal Process. 2020, 39, 5247–5271. [Google Scholar] [CrossRef]

- Madasamy, P.; Pongiannan, R.K.; Ravichandran, S.; Padmanaban, S.; Chokkalingam, B.; Hossain, E.; Adedayo, Y. A Simple Multilevel Space Vector Modulation Technique and MATLAB System Generator Built FPGA Implementation for Three-Level Neutral-Point Clamped Inverter. Energies 2019, 12, 4332. [Google Scholar] [CrossRef]

- Bonny, T. Chaotic or Hyper-chaotic Oscillator? Numerical Solution, Circuit Design, MATLAB HDL-Coder Implementation, VHDL Code, Security Analysis, and FPGA Realization. Circuits Syst. Signal Process. 2021, 40, 1061–1088. [Google Scholar] [CrossRef]

- Parera-Ruiz, A.; Cirstea, M.N.; Cirstea, S.E.; Dinu, A. Integrated Renewable Energy System Modelling with direct FPGA Controller Prototyping. In Proceedings of the IEEE Industrial Electronics Conference (IECON’09), Porto, Portugal, 3–5 November 2009; pp. 2963–2968. [Google Scholar]

- Lai, C.-K.; Tsao, Y.-T.; Tsai, C.-C. Modeling, Analysis, and Realization of Permanent Magnet Synchronous Motor Current Vector Control by MATLAB/Simulink and FPGA. Machines 2017, 5, 26. [Google Scholar] [CrossRef]

- Michael, T.; Reynolds, S.; Woolford, T. Designing a Generic, Software-Defined Multimode Radar Simulator for FPGAs Using Simulink® HDL Coder and Speedgoat Real-Time Hardware. In Proceedings of the International Conference on Radar (RADAR), Brisbane, QLD, Australia, 27–31 August 2018; pp. 1–4. [Google Scholar] [CrossRef]

- Dhruv, M.; Patel, D.M.; Shah, A.K. FPGA-PLC-based multi-channel position measurement system. ISA Trans. 2021, 115, 234–249. [Google Scholar] [CrossRef]

- Waldbjoern, J.P.; Maghareh, A.; Ou, G.; Dyke, S.J.; Stang, H. Multi-rate Real Time Hybrid Simulation operated on a flexible LabVIEW real-time platform. Eng. Struct. 2021, 239, 112308. [Google Scholar] [CrossRef]

- Sheikh, S.S.; Iqbal, S.; Kazim, M.; Ulasyar, A. Real-Time Simulation of Microgrid and Load Behavior Analysis Using FPGA. In Proceedings of the 2nd International Conference on Computing, Mathematics and Engineering Technologies (iCoMET), Sukkur, Pakistan, 30–31 January 2019; pp. 1–5. [Google Scholar] [CrossRef]

- Gupta, N.; Jain, A.; Vaisla, K.S.; Kumar, A.; Kumar, R. Performance analysis of DSDV and OLSR wireless sensor network routing protocols using FPGA hardware and machine learning. Multimed. Tools Appl. 2021, 80, 22301–22319. [Google Scholar] [CrossRef]

- Tomov, V.; Iliev, I.; Krasteva, V. High resolution FPGA pulse width modulation control of full-bridge DC–DC converters. IET Circuits Devices Syst. 2020, 14, 1110–1116. [Google Scholar] [CrossRef]

- Chaturvedi, D.K. Modeling and Simulation of Systems Using MATLAB® and Simulink®; Taylor & Francis: Abingdon, UK; CRC Press: Boca Raton, FL, USA, 2010. [Google Scholar]

- Iranian, M.E.; Mohseni, M.; Aghili, S.; Parizad, A.; Baghaee, H.R.; Guerrero, J.M. Real-Time FPGA-Based HIL Emulator of Power Electronics Controllers Using NI PXI for DFIG Studies. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 10, 2005–2019. [Google Scholar] [CrossRef]

- Singh, V.K.; Tripathi, R.N.; Hanamoto, T. HIL Co-Simulation of Finite Set-Model Predictive Control Using FPGA for a Three-Phase VSI System. Energies 2018, 11, 909. [Google Scholar] [CrossRef]

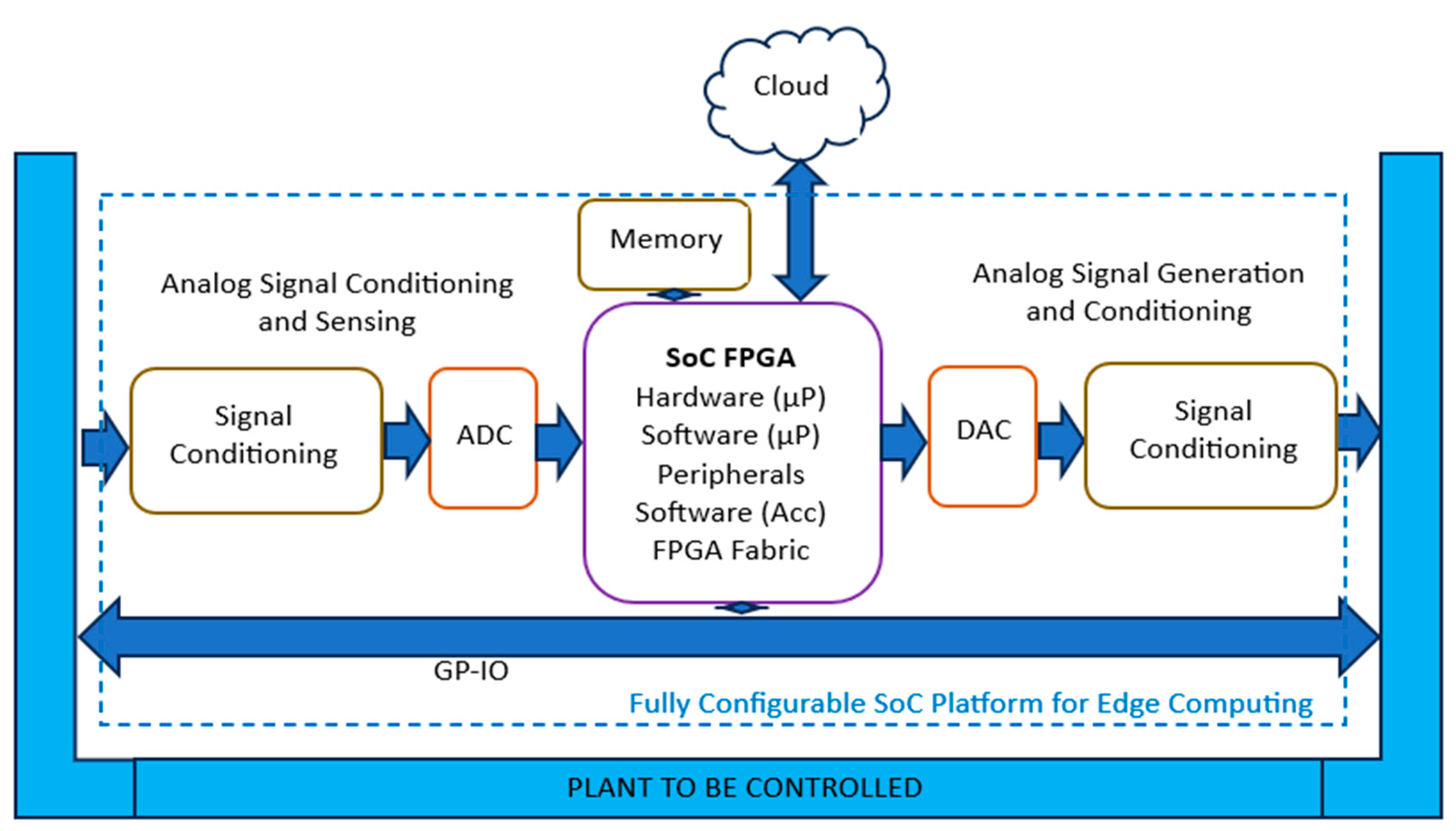

- Monmasson, E.; Hilairet, M.; Spagnuolo, G.; Cirstea, M.N. System-on-Chip FPGA Devices for Complex Electrical Energy Systems Control. IEEE Ind. Electron. Mag. 2022, 16, 53–64. [Google Scholar] [CrossRef]

- OPAL-RT Technologies. Available online: www.opal-rt.com (accessed on 21 May 2021).

- Nathan, S.; Giorlami, M.; Mair, R.; Jans-Singh, M. Creating a Virtual Replica. Ingenia 2021, 87, 16–20. Available online: https://www.ingenia.org.uk/articles/creating-a-virtual-replica/ (accessed on 1 January 2023).

- Synoptix. Digital Twins: How do we integrate and manage risk in security critical environments. Partn. News 2023, 55, 16. [Google Scholar]

- Monmasson, E.; Cirstea, M.N. FPGA Design Methodology for Industrial Control Systems—A Review. IEEE Trans. Ind. Electron. Spec. Issue FPGAs Used Ind. Control Syst. 2007, 54, 1824–1842. [Google Scholar] [CrossRef]

- Molanes, R.F.; Rodriguez-Andina, J.J.; Farina, J. Performance Characterization and Design Guidelines for Efficient Processor–FPGA Communication in Cyclone V FPSoCs. IEEE Trans. Ind. Electron. 2018, 65, 4368–4377. [Google Scholar] [CrossRef]

- Cecati, C.; Ciancetta, F.; Siano, P. A FPGA/fuzzy logic-based multilevel inverter. In Proceedings of the IEEE International Symposium on Industrial Electronics (ISIE), Seoul, Republic of Korea, 5–8 July 2009; pp. 706–711. [Google Scholar]

- Dinu, A.; Cirstea, M.N.; Cirstea, S.E. Direct Neural Networks Hardware Implementation Algorithm. IEEE Trans. Ind. Electron. 2010, 57, 1845–1848. [Google Scholar] [CrossRef]

- Le, Q.N.; Jeon, J.W. Neural-Network-Based Low-Speed-Damping Controller for Stepper Motor with an FPGA. IEEE Trans. Ind. Electron. 2010, 57, 3167–3180. [Google Scholar]

- Youssef, A.; El Telbany, M.; Zekry, A. Reconfigurable generic FPGA implementation of fuzzy logic controller for MPPT of PV systems. Renew. Sustain. Energy Rev. 2018, 82, 1313–1319. [Google Scholar] [CrossRef]

- Gomperts, A.; Ukil, A.; Zurfluh, F. Development and Implementation of Parameterized FPGA-Based General Purpose Neural etworks for Online Applications. IEEE Trans. Ind. Inform. 2011, 7, 78–89. [Google Scholar] [CrossRef]

- Bueno, E.J.; Hernandez, A.; Rodriguez, F.J.; Girón, C.; Mateos, R.; Cobreces, S. A DSP and FPGA-based industrial control with high-speed communication interfaces for grid converters applied to distributed power generation system. IEEE Trans. Ind. Electron. 2009, 56, 654–669. [Google Scholar] [CrossRef]

- Weilkiens, T. Model-Based System Architecture; Wiley: Hoboken, NJ, USA, 2015. [Google Scholar]

- Greaves, D.J. Modern System-on-Chip Design on Arm, Arm Education Media. 2021. Available online: https://www.arm.com/resources/education/books/modern-soc (accessed on 2 June 2023).

- Black, D.C.; Donovan, J. SystemC: From the Ground Up, 2nd ed.; Springer: Berlin/Heidelberg, Germany, 2010. [Google Scholar]

- Spear, C. SystemVerilog for Verification: A Guide to Learning the Testbench Language Features, 3rd ed.; Springer: Berlin/Heidelberg, Germany, 2012. [Google Scholar]

- Vahid, F.; Lysecky, R. Digital Design with RTL Design, Verilog, and VHDL, 2nd ed.; John Wiley & Sons: Hoboken, NJ, USA, 2019. [Google Scholar]

- Chang, K.C. Digital Design and Modeling with VHDL and Synthesis; McGraw-Hill: New York, NY, USA, 2009. [Google Scholar]

- Coussy, P.; Morawiec, A. High-Level Synthesis: From Algorithm to Digital Circuit; Springer: Berlin/Heidelberg, Germany, 2011. [Google Scholar]

- Louise, H.; Crockett, H.; Northcote, D.; Ramsay, C. Exploring Zynq MPSoC with PYNQ and Machine Learning Applications; Strathclyde Academic Media: Glasgow, UK, 2019. [Google Scholar]

- Cirstea, M.N.; Dinu, A.; Khor, J.; McCormick, M. Neural and Fuzzy Logic Control of Drives and Power Systems; Elsevier Science, Newnes: Oxford, UK, 2002. [Google Scholar]

- Synopsis. Design Compiler. Available online: https://www.synopsys.com/implementation-and-signoff/rtl-synthesis-test/dc-ultra.html (accessed on 2 June 2023).

- Cadence. Genus (TM) Synthesis Solution. Available online: https://www.cadence.com/en_US/home/tools/digital-design-and-signoff/synthesis/genus-synthesis-solution.html (accessed on 2 June 2023).

- Siemens EDA. Questa Simulator Tool. Available online: https://eda.sw.siemens.com/en-US/ic/questa/simulation/advanced-simulator/ (accessed on 2 June 2023).

- Synopsis. VCS Functional Verification Solution. Available online: https://www.synopsys.com/verification/simulation/vcs.html (accessed on 2 June 2023).

- Cadence. Incisive (TM). Available online: https://www.cadence.com/en_US/home/training/all-courses/82115.html (accessed on 2 June 2023).

- Siemens EDA. Calibre Design Solutions. Available online: https://eda.sw.siemens.com/en-US/ic/calibre-design/ (accessed on 2 June 2023).

- Synopsis. IC Compiler. Available online: https://www.synopsys.com/implementation-and-signoff/physical-implementation/ic-compiler.html (accessed on 2 June 2023).

- Cadence. Innovus Implementation System. Available online: https://www.cadence.com/en_US/home/tools/digital-design-and-signoff/soc-implementation-and-floorplanning/innovus-implementation-system.html (accessed on 2 June 2023).

- Frumusanu, A. Apple Announces M1 Pro and M1 Max: Gian New ARM SoCs with All-out Performance. AnandTech. 2021. Available online: https://www.anandtech.com/show/17019/apple-announced-m1-pro-m1-max-giant-new-socs-with-allout-performance (accessed on 2 June 2023).

- Available online: https://www.aldec.com/en/products/mil_aero_verification/do-254 (accessed on 10 October 2023).

- Costa, A.; Lusardi, N.; Garzetti, F.; Ronconi, E.; Maffessanti, S.; Danilevski, C.; Lomidze, D.; Turcato, M.; Porro, M.; Geraci, A. A Study of the Latest Updates of the DAQ Firmware for the DSSC Camera at the European XFEL. IEEE Access 2023, 11, 84323–84335. [Google Scholar] [CrossRef]

- Lusardi, N.; Garzetti, F.; Costa, A.; Cautero, M.; Corna, N.; Ronconi, E.; Brajnik, G.; Stebel, L.; Sergo, R.; Cautero, G.; et al. High-Resolution Imager Based on Time-to-Space Conversion. IEEE Trans. Instrum. Meas. 2022, 71, 2004811. [Google Scholar] [CrossRef]

- Lusardi, N.; Garzetti, F.; Costa, A.; Ronconi, E.; Geraci, A. From Multiphase to Novel Single-Phase Multichannel Shift-Clock Fast Counter Time-to-Digital Converter. IEEE Trans. Ind. Electron. 2023, 1–9. Available online: https://ieeexplore.ieee.org/document/10288129 (accessed on 21 January 2024). [CrossRef]

- Huang, H.-C.; Tao, C.-W.; Chuang, C.-C.; Xu, J.-J. FPGA-Based Mechatronic Design and Real-Time Fuzzy Control with Computational Intelligence Optimization for Omni-Mecanum-Wheeled Autonomous Vehicles. Electronics 2019, 8, 1328. [Google Scholar] [CrossRef]

- Vargas-Treviño, M.A.; Lopez-Gomez, J.; Vergara-Limon, S.; Palomino-Merino, A.; Torres-Reyes, R.; Garcia-Ramirez, P. A mechatronic approach for ball screw drive system: Modeling, control, and validation on an FPGA-based architecture. Int. J. Adv. Manuf. Technol. 2019, 104, 2329–2346. [Google Scholar] [CrossRef]

- Shao, X.; Sun, D. Development of a New Robot Controller Architecture with FPGA Based IC Design for Improved High-Speed Performance. IEEE Trans. Ind. Inform. 2007, 3, 312–321. [Google Scholar] [CrossRef]

- Yoshimoto, Y.; Tamukoh, H. FPGA Implementation of a Binarized Dual Stream Convolutional Neural Network for Service Robots. J. Robot. Mechatron. 2021, 33, 386–399. [Google Scholar] [CrossRef]

- Di Paolo Emilio, M. Embedded Systems Design for High-Speed Data Acquisition and Control; Springer: Berlin/Heidelberg, Germany, 2015. [Google Scholar]

- Stanciu, A.; Cirstea, M.N.; Moldoveanu, F. Analysis and Evaluation of PUF-based SoC Designs for Security Applications. IEEE Trans. Ind. Electron. 2016, 63, 5699–5708. [Google Scholar] [CrossRef]

- Vetter, T.; Schulz, M. FPGA to Control Power Electronics. Power Electron. Eur. 2014, 6, 19–21. [Google Scholar]

- Petreus, D.; Daraban, S.; Cirstea, M. Modular Hybrid Energy Concept Employing a Novel Control Structure Based on a Simple Analog System. Adv. Electr. Comput. Eng. 2016, 16, 3–10. [Google Scholar] [CrossRef]

- Rogers, P.; Kavasseri, R.; Smith, S.C. An FPGA-in-the-loop approach for HDL motor controller verification. In Proceedings of the International Conference on ReConFigurable Computing and FPGAs (ReConFig), Cancun, Mexico, 4–6 December 2017; pp. 1–6. [Google Scholar]

- Pan, C. Design of sports course management system based on Internet of Things and FPGA system. Microprocess. Microsyst. 2021, 80, 103357. [Google Scholar] [CrossRef]

- Zhou, Z.; Liu, Y.; Yu, H.; Chen, Q. Logistics supply chain information collaboration based on FPGA and internet of things system. Microprocess. Microsyst. 2021, 80, 103589. [Google Scholar] [CrossRef]

- Huang, X.; Li, X. Agricultural labor market equilibrium based on FPGA platform and IoT communication. Microprocess. Microsyst. 2021, 80, 103332. [Google Scholar] [CrossRef]

- Elnawawy, M.; Farhan, A.; Nabulsi, A.A.; Al-Ali, A.R.; Sagahyroon, A. Role of FPGA in Internet of Things Applications. In Proceedings of the IEEE International Symposium on Signal Processing and Information Technology (ISSPIT), Ajman, United Arab Emirates, 10–12 December 2019; pp. 1–6. [Google Scholar] [CrossRef]

- Urbina, M.; Acosta, T.; Lázaro, J.; Astarloa, A.; Bidarte, U. Smart Sensor: SoC Architecture for the Industrial Internet of Things. IEEE Internet Things J. 2019, 6, 6567–6577. [Google Scholar] [CrossRef]

- Tulpule, B.; Ohme, B.; Larson, M.; Behbahani, A.; Gerety, J.; Steines, A. A System On Chip (SOC) ASIC chipset for Aerospace and Energy Exploration Applications. In Proceedings of the International Conference on High Temperature Electronics (HiTEC), Albuquerque, NM, USA, 1 January 2014; pp. 278–284. [Google Scholar]

- Carter, H.; Chan, A.; Vinegar, C.; Rupert, J. Concerns with using Machine Learning in Airworthiness Applications. In Proceedings of the Vertical Flight Society’s 79th Annual Forum & Technology Display, West Palm Beach, FL, USA, 16–18 May 2023; pp. 1–23. [Google Scholar] [CrossRef]

- European Union Aviation Safety Agency (EASA). Artificial Intelligence Roadmap 2.0-Human-Centric Approach to AI in Aviation. 10 May 2023. Available online: https://www.easa.europa.eu/en/domains/research-innovation/ai (accessed on 10 October 2023).

- Pitcher, G. Growing Number of Ecus Forces New Approach to Cars Electrical Architecture. New Electronics. 25 September 2012. Available online: https://www.newelectronics.co.uk/content/features/growing-number-of-ecus-forces-new-approach-to-cars-electrical-architecture (accessed on 2 June 2023).

- van Djik, L. Future Vehicle Networks and ECUs-Architecture and Technology Considerations. NXP Semiconductor. Available online: https://www.nxp.com/docs/en/white-paper/FVNECUA4WP.pdf (accessed on 2 June 2023).

- Burkacky, J.D.; Doll, G.; Knochenhauer, C. Rethinking Car Software and Electronics Architecture. 14 February 2018. Available online: https://www.mckinsey.com/industries/automotive-and-assembly/our-insights/rethinking-car-software-and-electronics-architecture (accessed on 3 June 2023).

- SAE (Society of Automotive Engineers) Standard J3016: Taxonomy and Definitions for Terms Related to Driving Automation Systems for On-Road Motor Vehicles. 30 April 2021. Available online: https://www.sae.org/standards/content/j3016_202104/ (accessed on 3 June 2023).

- Lieske, T.; Pfundt, B.; Vaas, S.; Reichenbach, M.; Fey, D. System on chip generation for multi-sensor and sensor fusion applications. In Proceedings of the 2017 International Conference on Embedded Computer Systems: Architectures, Modeling, and Simulation (SAMOS), Pythagorion, Greece, 17–20 July 2017; pp. 20–29. [Google Scholar] [CrossRef]

- Kani, A. The New Era of Transportation Is Built on NVIDIA DRIVE Orin. 9 November 2012. Available online: https://blogs.nvidia.com/blog/2021/11/09/new-era-transportation-drive-orin/ (accessed on 3 June 2023).

- Telemaco3P Automotive Family of Telematics and Connectivity Microprocessor. Available online: https://www.st.com/en/automotive-infotainment-and-telematics/sta1385.html (accessed on 3 June 2023).

- Cabrera, J.; Vega, A.; Tobajas, F.; Deniz, V.; Fabelo, H. Design of a reconfigurable Li-Ion Battery Management System (BMS). In Proceedings of the 2014 XI Tecnologias Aplicadas a la Ensenanza de la Electronica (Technologies Applied to Electronics Teaching) (TAEE), Bilbao, Spain, 11–13 June 2014; pp. 1–6. [Google Scholar] [CrossRef]

- Tangemann, C. ISO 26262; Part 11: Systems-on-Chips and the Intellectual Property Conundrum. ISO: Geneva, Switzerland, 13 May 2019. Available online: https://www.automotive-iq.com/autonomous-drive/articles/iso-26262-part-11-systems-on-chips-and-the-intellectual-property-conundrum (accessed on 3 June 2023).

- Munsel, M. How to Handle Complexity in ISO 26262 Compliance Workflow. 30 April 2021. Available online: https://www.perforce.com/blog/mdx/iso-26262-compliance-workflows (accessed on 3 June 2023).

- Schaefer, J.; Christlbauer, H.; Schreiber, A.; Reith, G.; Jonker, M.; Potman, J.; Dannebaum, U.; Eissfeldt, T. Future Automotive Embedded Systems Enabled by Efficient Model-Based Software Development. SAE Technical Paper 2021-01-0129. 2021. Available online: https://www.sae.org/publications/technical-papers/content/2021-01-0129/ (accessed on 3 June 2023).

- Embitel. Model Based Design of Automotive Software. Available online: https://www.embitel.com/model-based-development-mbd-services-for-automotive-applications (accessed on 3 June 2023).

- Mutschler, A. Advanced Packaging for Automotive Chips. Semiconductor Engineering. Deep Insights for the Tech Industry. 2021. Available online: https://semiengineering.com/advanced-packaging-for-automotive-chips/ (accessed on 7 November 2023).

- Watts, M.R.; Poulton, C.; Byrd, M.; Smolka, G. Lidar on a Chip Enters the Fast Lane: Sensors for Self-Driving Cars and Robots will be Tiny, Reliable, and Affordable. IEEE Spectrum. 2023, 60, 38–43. [Google Scholar] [CrossRef]

- Pretz, K. Aart de Geus Transformed IC Design: The Synopsis CEO helped create logical Synthesis. IEEE Spectrum. 2023, 60, 52–53. [Google Scholar]

- Van Schoot, J. The Moore’s Law Machine: The Next Trick to Tinier Transistors is High-Numerical-Aperture EUV Lithography. IEEE Spectrum. 2023, 60, 44–48. [Google Scholar] [CrossRef]

- Edwards, R.T.; Shalan, M.; Kassem, M. Real Silicon Using Open-Source EDA. IEEE Des. Test 2021, 38, 38–44. [Google Scholar] [CrossRef]

- Shalan, M.; Edwards, T. Building OpenLANE: A 130 nm OpenROAD-based Tapeout-Proven Flow: Invited Paper. In Proceedings of the IEEE/ACM International Conference On Computer Aided Design (ICCAD), San Diego, CA, USA, 2–5 November 2020; pp. 1–6. [Google Scholar]

- Lopera, D.S.; Servadei, L.; Kasi, V.P.; Prebeck, S.; Ecker, W. RTL Delay Prediction Using Neural Networks. In Proceedings of the IEEE Nordic Circuits and Systems Conference (NorCAS), Oslo, Norway, 26–27 October 2021; pp. 1–7. [Google Scholar] [CrossRef]

- Colombo, A.W.; Karnouskos, S.; Yu, X.; Kaynak, O.; Luo, R.C.; Shi, Y.; Leitao, P.; Ribeiro, L.; Haase, J. A 70-Year Industrial Electronics Society Evolution through Industrial Revolutions: The Rise and Flourishing of Information and Communication Technologies. IEEE Ind. Electron. Mag. 2021, 15, 115–126. [Google Scholar] [CrossRef]

- Ferguson, H. 3D Printing a Bridge with a Twin. Ingenia 2023, 94, 26–31. [Google Scholar]

- Hunter, A. The future of construction is digital: How digital innovation is proving transformative for NG Bailey. Partn. News 2023, 55, 36–37. [Google Scholar]

- Hayes, C. Right Recipe for Smart: Add a Pinch of AI to the IoT. Eng. Technol. 2020, 15, 66–67. [Google Scholar]

- Lucia, O.; She, J.; Chen, A.C.; Cheng, Z.; Chow, M.Y.; Dunai, L.; Hilairet, M.; Huang, V.; Monmasson, E.; Umetani, K.; et al. Emerging Trends in Industrial Electronics: A Cross-Disciplinary View. IEEE Ind. Electron. Mag. 2021, 15, 127–139. [Google Scholar] [CrossRef]

- Fletcher, M. Rethinking the Future Through Design. Ingenia 2021, 87, 8–9. [Google Scholar]

- Hayes, J. Deep as Chips [AI Chips]. Eng. Technol. 2020, 15, 72–75. [Google Scholar] [CrossRef]

- Agnesina, A.; Mark Ren, M. AutoDMP Optimizes Macro Placement for Chip Design with AI and GPUs. 27 March 2023. Available online: https://developer.nvidia.com/blog/autodmp-optimizes-macro-placement-for-chip-design-with-ai-and-gpus/ (accessed on 4 June 2023).

- Rapid Silicon. RapidGPT—The Evolutionary AI-Based Design Tools for FPGA Designers. 2023. Available online: https://rapidsilicon.com/rapidgpt/ (accessed on 4 June 2023).

- Zunin, V.V.; Romanov, A.I.; Solovyev, R.A. Developing Methods for Combinational Circuit Generation. In Proceedings of the International Russian Automation Conference (RusAutoCon), Sochi, Russia, 4–10 September 2022; pp. 842–846. [Google Scholar] [CrossRef]

- Kumar, A.K.A.; Al-Salamin, S.; Amrouch, H.; Gerstlauer, A. Machine Learning-Based Microarchitecture-Level Power Modeling of CPUs. IEEE Trans. Comput. 2023, 72, 941–956. [Google Scholar] [CrossRef]

- Sengupta, P.; Tyagi, A.; Chen, Y.; Hu, J. How Good Is Your Verilog RTL Code?: A Quick Answer from Machine Learning. In Proceedings of the 41st IEEE/ACM International Conference on Computer-Aided Design (ICCAD), San Diego, CA, USA, 30 October–3 November 2022; pp. 1–9. [Google Scholar] [CrossRef]

- Kaplan, J.; McCandlish, S.; Henighan, T.; Brown, T.B.; Chess, B.; Child, R.; Gray, S.; Radford, A.; Jeffrey Wu, J.; Vasilakos, F.; et al. Scaling Laws for Neural Language Models. arXiv 2020, arXiv:2001.08361. Available online: https://arxiv.org/pdf/2001.08361.pdf (accessed on 4 June 2023).

- Fryer, T. The end of the Engineer? Eng. Technol. 2017, 12, 26–29. [Google Scholar] [CrossRef]

- Aameri, B.A.; Cheong, H.; Beck, J.C. Towards an Ontology for Generative Design of Mechanical Assemblies. Appl. Ontol. 2019, 14, 127–153. [Google Scholar] [CrossRef]

- Dean, L.; Loy, J. Generative Product Design Futures. Des. J. 2020, 23, 331–349. [Google Scholar] [CrossRef]

- Crouch, J.; Palmer, B. Large Language Models: Revolutionising Engineering Design. Partn. News 2023, 55, 28. [Google Scholar]

- Prompt Engineering Institute. What Is Prompt Engineering? Prompt Engineering Guides, News and Resources. 2023. Available online: https://www.promptengineering.org/what-is-prompt-engineering/ (accessed on 3 July 2023).

- Ferguson, M.C. Prompt Engineering; The Future of Language Generation; Michael Ferguson Publisher: Boise, ID, USA, 2023; ISBN 13 979-8215905739. [Google Scholar]

- Rodriguez, J. Google’s Chain of Thought Prompting is One of the Most Exciting Techniques in Generative AI. Towards AI. 2023. Available online: https://pub.towardsai.net/googles-chain-of-thought-prompting-is-one-of-the-most-exciting-techniques-in-generative-ai-782cc62fe602 (accessed on 3 July 2023).

- IEEE. The Impact of Technology in 2023 and Beyond: An IEEE Global Study. IEEE Spectr. 2023, 60, 57. [Google Scholar]

- IEEE. An Ugly Chapter in Chip Design–Study tries to settle a bitter disagreement over Google’s AI tool. IEEE Spectr. 2023, 60, 5–8. [Google Scholar]

| Criteria\Method | Graphical | Text | Mixed | Custom |

|---|---|---|---|---|

| algorithm complexity | ●○○ | ●○○ | ●●○ | ●●● |

| high accuracy | ●○○ | ●●○ | ●●● | ●●● |

| high speed/parallelism | ○○○ | ●○○ | ●●○ | ●●● |

| short development time | ●●● | ●●○ | ●○○ | ○○○ |

| high design flexibility | ●○○ | ●●○ | ●●○ | ●●● |

| ease of learning | ●●● | ●●○ | ●○○ | ○○○ |

| low development cost | ●●● | ●●○ | ●○○ | ○○○ |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Cirstea, M.; Benkrid, K.; Dinu, A.; Ghiriti, R.; Petreus, D. Digital Electronic System-on-Chip Design: Methodologies, Tools, Evolution, and Trends. Micromachines 2024, 15, 247. https://doi.org/10.3390/mi15020247

Cirstea M, Benkrid K, Dinu A, Ghiriti R, Petreus D. Digital Electronic System-on-Chip Design: Methodologies, Tools, Evolution, and Trends. Micromachines. 2024; 15(2):247. https://doi.org/10.3390/mi15020247

Chicago/Turabian StyleCirstea, Marcian, Khaled Benkrid, Andrei Dinu, Romeo Ghiriti, and Dorin Petreus. 2024. "Digital Electronic System-on-Chip Design: Methodologies, Tools, Evolution, and Trends" Micromachines 15, no. 2: 247. https://doi.org/10.3390/mi15020247

APA StyleCirstea, M., Benkrid, K., Dinu, A., Ghiriti, R., & Petreus, D. (2024). Digital Electronic System-on-Chip Design: Methodologies, Tools, Evolution, and Trends. Micromachines, 15(2), 247. https://doi.org/10.3390/mi15020247