Versatility Investigation of Grown Titanium Dioxide Nanoparticles and Their Comparative Charge Storage for Memristor Devices

Abstract

:1. Introduction

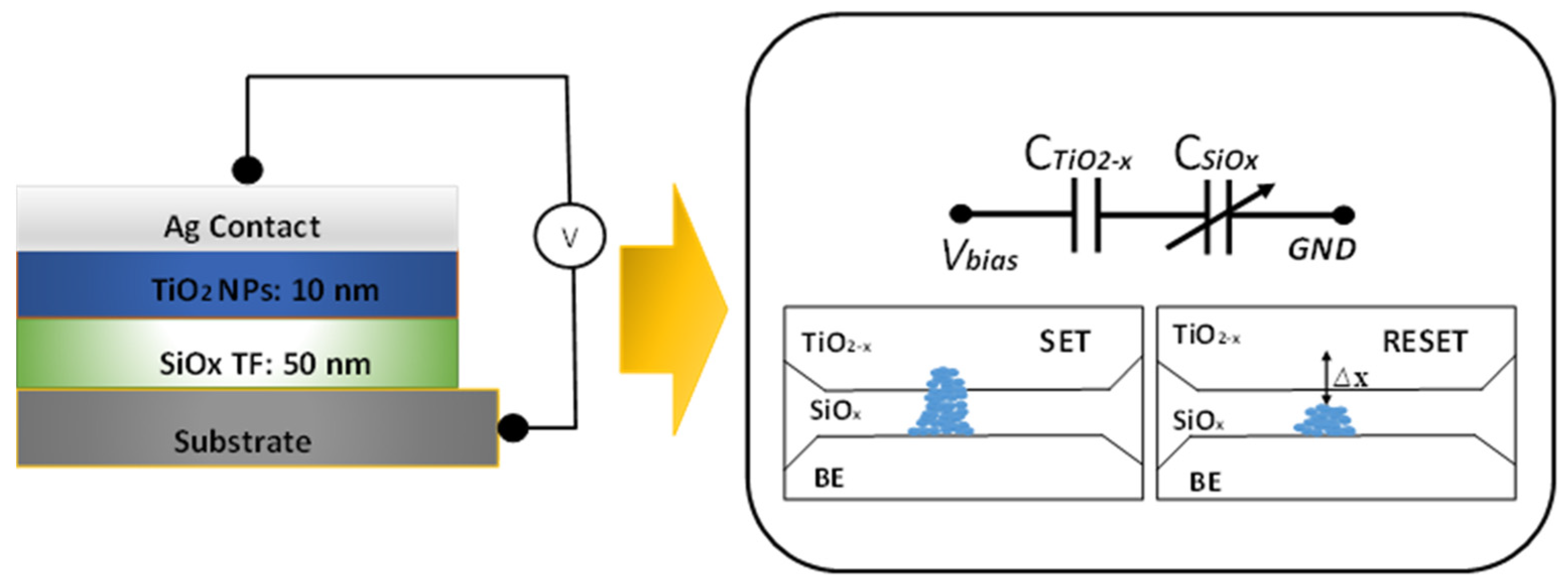

2. Experiment Procedure

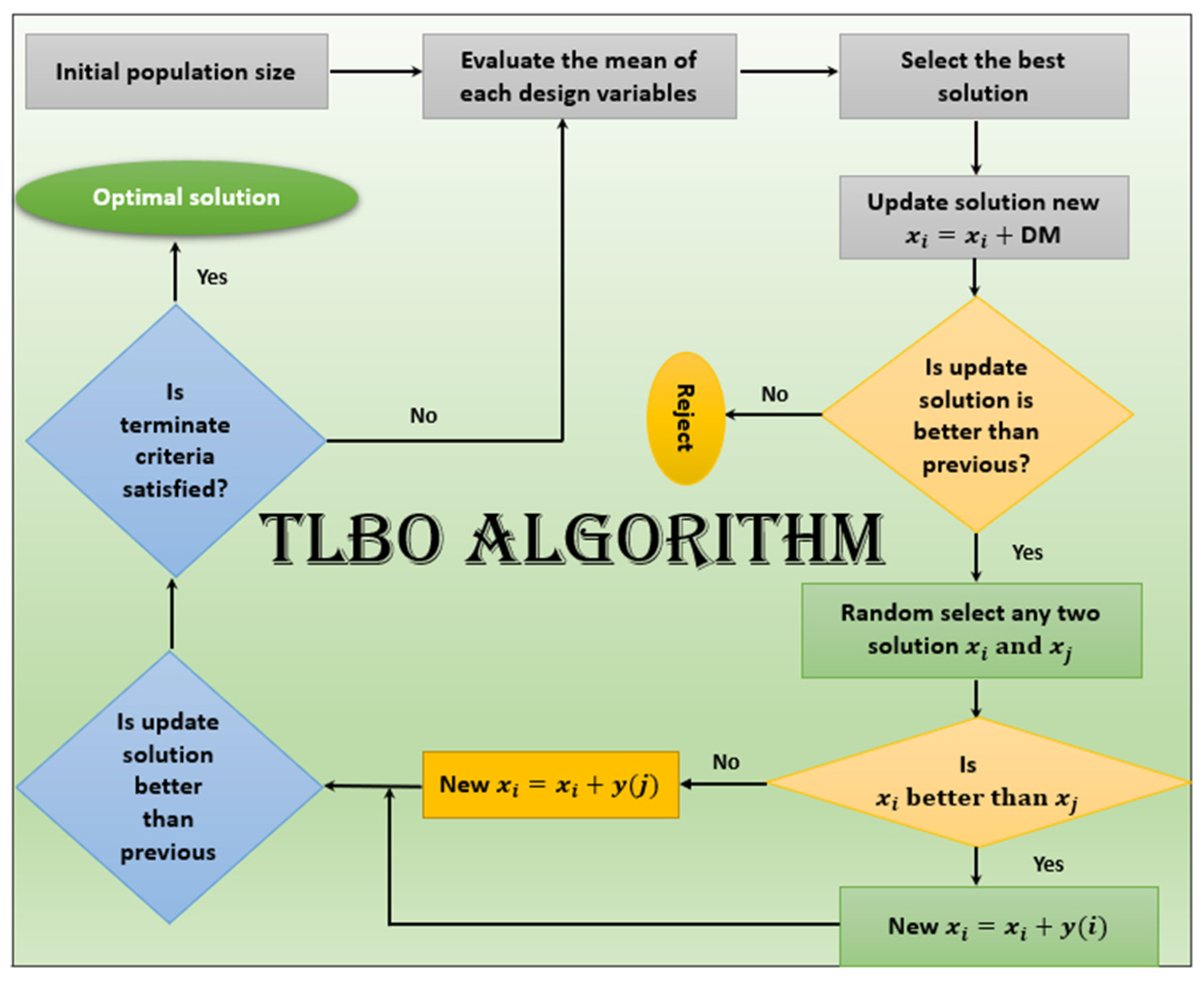

3. Teaching–Learning-Based Optimization (TLBO) Methodology

4. Results and Discussion

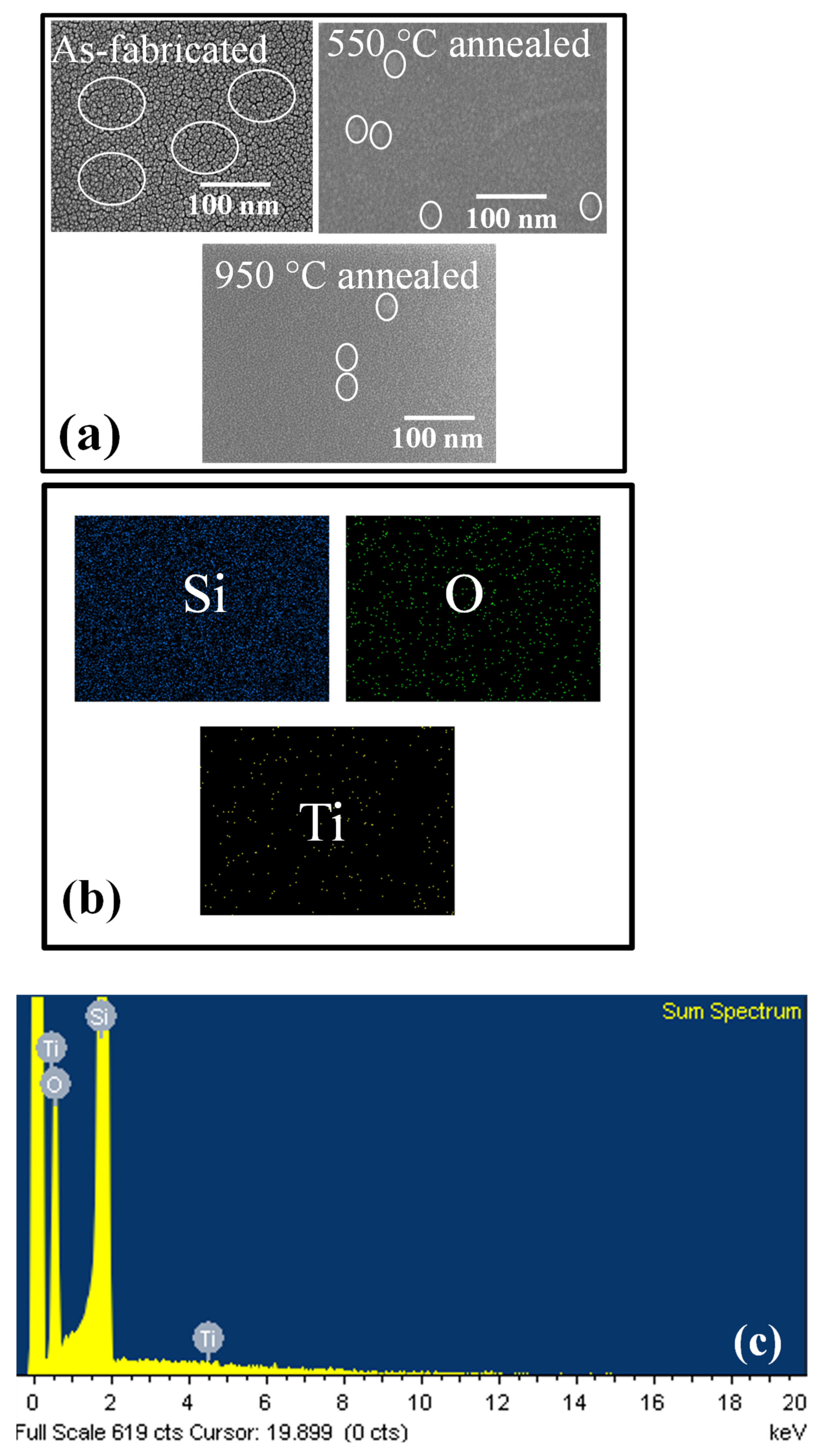

4.1. Structural Topography

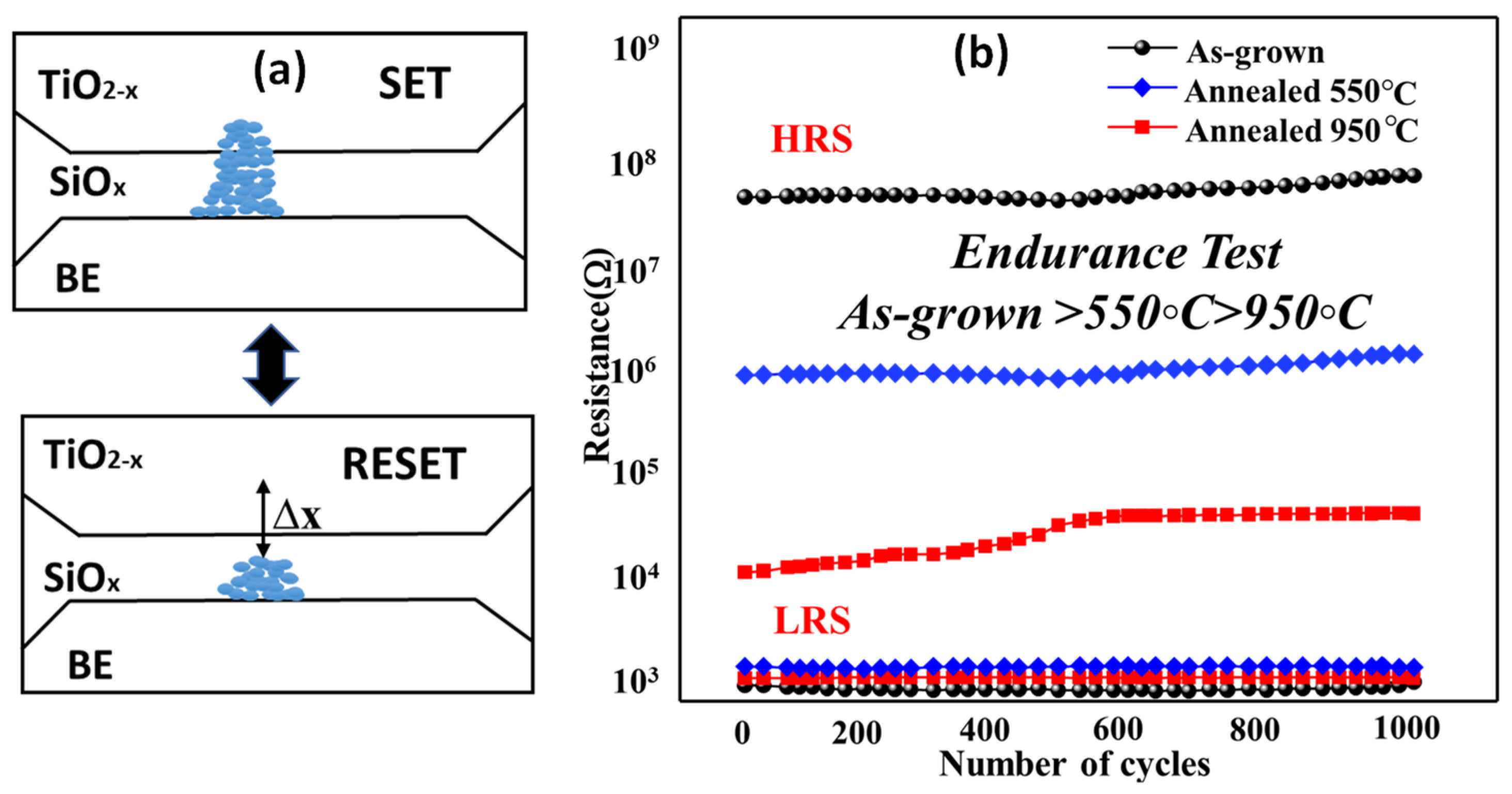

4.2. Endurance of Devices and Their Performance

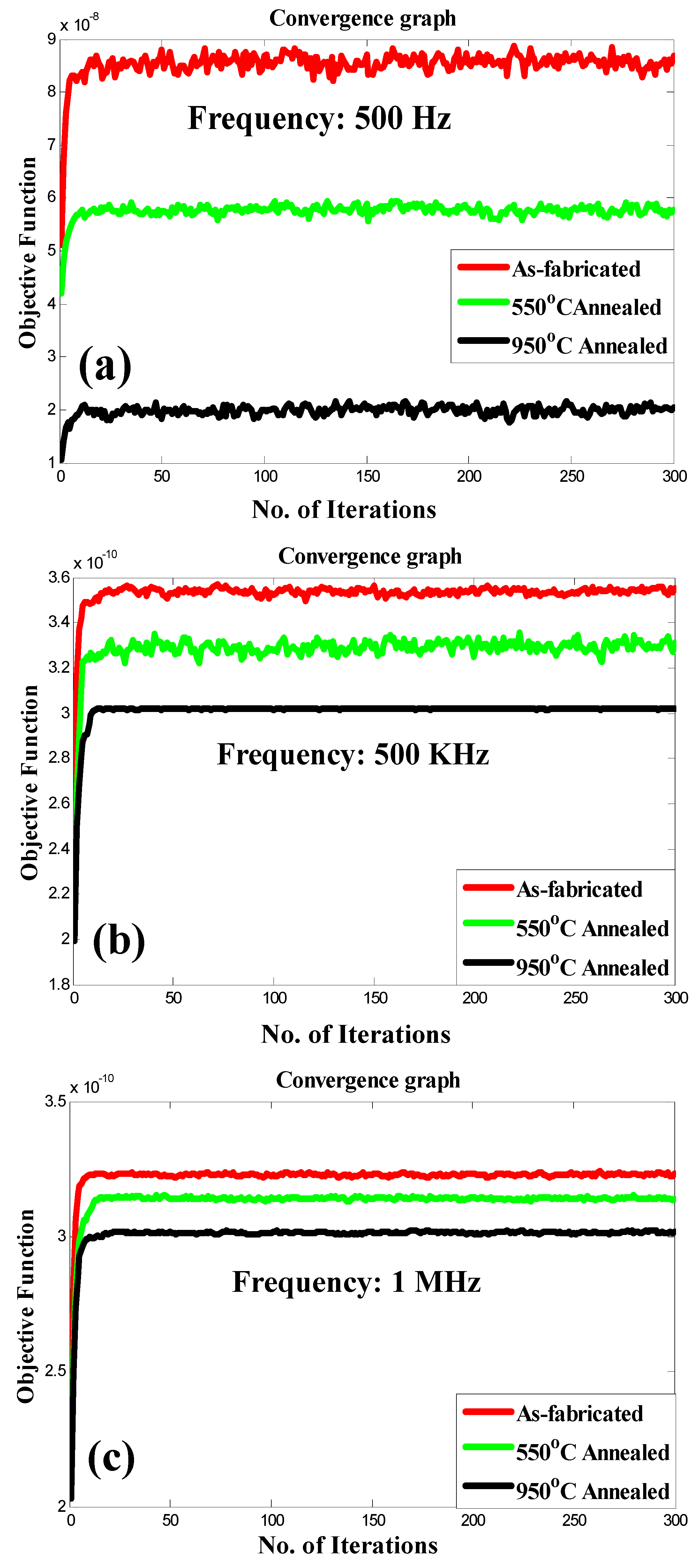

4.3. TLBO

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Smith, J. The Advancement of Miniaturization: A Revolutionary Paradigm in Electronics. J. Electr. Eng. 2022, 36, 78–95. [Google Scholar]

- Johnson, A.B.; Smith, C.D. Versatility of Titanium Dioxide (TiO2) as a Semiconductor: Exploring Anatase, Rutile, and Brookite Crystalline Forms. J. Mater. Sci. 2021, 45, 120–135. [Google Scholar]

- Dima, R.S.; Phuthu, L.; Maluta, N.E.; Kirui, J.K.; Maphanga, R.R. Electronic, Structural, and Optical Properties of Mono-Doped and Co-Doped (210) TiO2 Brookite Surfaces for Application in Dye-Sensitized Solar Cells-A First Principles Study. Materials 2021, 14, 3918. [Google Scholar] [CrossRef] [PubMed]

- Wang, P.; Hu, M.; Wang, H.; Chen, Z.; Feng, Y.; Wang, J.; Ling, W.; Huang, Y. The Evolution of Flexible Electronics: From Nature, beyond Nature, and to Nature. Adv. Sci. 2020, 7, 2001116. [Google Scholar] [CrossRef] [PubMed]

- Chaudhary, V.S.; Kumar, D.; Mishra, G.P.; Sharma, S.; Kumar, S. Plasmonic Biosensor with Gold and Titanium Dioxide Immobilized on Photonic Crystal Fiber for Blood Composition Detection. IEEE Sens. J. 2022, 22, 8474–8481. [Google Scholar] [CrossRef]

- Al-Shidaifat, A.; Chakrabartty, S.; Kumar, S.; Acharjee, S.; Song, H. A Novel Characterization and Performance Measurement of Memristor Devices for Synaptic Emulators in Advanced Neuro-Computing. Micromachines 2020, 11, 89. [Google Scholar] [CrossRef] [PubMed]

- Illarionov, G.A.; Morozova, S.M.; Chrishtop, V.V.; Einarsrud, M.-A.; Morozov, M.I. Memristive TiO2: Synthesis, Technologies, and Applications. Front. Chem. 2020, 8, 724. [Google Scholar] [CrossRef] [PubMed]

- Strukov, D.B.; Snider, G.S.; Stewart, D.R.; Williams, R.S. The Missing Memristor Found. Nature 2008, 453, 80–83. [Google Scholar] [CrossRef] [PubMed]

- Smith, J.; Johnson, A.; Williams, B. Electromigration of Point Defects Inducing Memristivity in Titanium Oxide Systems. J. Mater. Sci. 2018, 45, 789–796. [Google Scholar]

- Gale, E. TiO2-Based Memristors and ReRAM: Materials, Mechanisms and Models (a Review). Semicond. Sci. Technol. 2014, 29, 104004. [Google Scholar] [CrossRef]

- Chakrabartty, S.; Acharjee, S.; Al-Shidaifat, A.; Biswas, M.; Song, H. Gd-Doped HfO2 Memristor Device, Evaluation Robustness by Image Noise Cancellation and Edge Detection Filter for Neuromorphic Computing. IEEE Access 2019, 7, 157922–157932. [Google Scholar] [CrossRef]

- Hur, J.-H. The Origin of the Exceptionally Low Activation Energy of Oxygen Vacancy in Tantalum Pentoxide Based Resistive Memory. Sci. Rep. 2019, 9, 17019. [Google Scholar] [CrossRef] [PubMed]

- Kim, D.; Kim, K.M.; Han, H.; Lee, J.; Ko, D.; Park, K.R.; Jang, K.-B.; Kim, D.; Forrester, J.S.; Lee, S.H.; et al. Ti/TiO2/SiO2 Multilayer Thin Films with Enhanced Spectral Selectivity for Optical Narrow Bandpass Filters. Sci. Rep. 2022, 12, 32. [Google Scholar] [CrossRef] [PubMed]

- Rao, R.V.; Savsani, V.J.; Vakharia, D.P. Teaching–Learning-Based Optimization: A Novel Method for Constrained Mechanical Design Optimization Problems. Comput. Aided Des. 2011, 43, 303–315. [Google Scholar] [CrossRef]

- Rao, R.V.; Savsani, V.J.; Vakharia, D.P. Teaching–Learning-Based Optimization: An Optimization Method for Continuous Non-Linear Large Scale Problems. Inf. Sci. 2012, 183, 1–15. [Google Scholar] [CrossRef]

- Amiri, B. Application of Teaching-Learning-Based Optimization Algorithm on Cluster Analysis. J. Basic Appl. Sci. Res. 2012, 2, 11795–11802. [Google Scholar]

- Lee, C.; Inpyo, K.; Hyunjung, S.; Sanghyo, K.; Jinhan, C. Nonvolatile Memory Properties of Pt Nanoparticle-Embedded TiO2 Nanocomposite Multilayers via Electrostatic Layer-by-Layer Assembly. Nanotechnology 2010, 21, 185704. [Google Scholar] [CrossRef] [PubMed]

- Kargan, N.H.; Aliahmad, M.; Azizi, S. Detecting Ultra-Violet Radiation by Using Titanium Dioxide Nanoparticles. Soft Nanosci. Lett. 2012, 02, 29–33. [Google Scholar] [CrossRef]

- Gupta, S.M.; Tripathi, M. A Review of TiO2 Nanoparticles. Chin. Sci. Bull. 2011, 56, 1639–1657. [Google Scholar] [CrossRef]

- Kerr, P.F. The occurrence of andalusite and related minerals at White Mountain, California. Econ. Geol. 1932, 27, 614–643. [Google Scholar] [CrossRef]

- Deng, L.; Wang, D.; Zhang, Z.; Tang, P.; Li, G.; Pei, J. Energy Consumption Analysis for Various Memristive Networks under Different Learning Strategies. Phys. Lett. A 2016, 380, 903–909. [Google Scholar] [CrossRef]

| Frequency | vmin (V) | vmax (V) | Cmin (pF) | Cmax (pF) | |

|---|---|---|---|---|---|

| As Fabricated | 1 MHz | −10 | 10 | 6.3 | 6.52067 |

| 500 kHz | −10 | 10 | 6.6614 | 7.2518 | |

| 500 Hz | −10 | 10 | 1230 | 1880 | |

| 550 °C Annealed | 1 MHz | −10 | 10 | 6.145 | 6.33665 |

| 500 kHz | −10 | 10 | 5.6721 | 6.899 | |

| 500 Hz | −10 | 10 | 890.26 | 1260.13 | |

| 950 °C Annealed | 1 MHz | −10 | 10 | 5.9256 | 6.0734 |

| 500 kHz | −10 | 10 | 5.992 | 6.0545 | |

| 500 Hz | −10 | 10 | 112.50 | 490.74 |

| Device | Iteration | Value of Objective Function | c (F) | V (volt) | E (pj) |

|---|---|---|---|---|---|

| Charge storage for 500 Hz | |||||

| As fabricated | 300 | 9.400000 × 10−8 | 1.88 × 10−9 | 10 | 94,000.00 |

| 550 °C | 300 | 6.300670 × 10−8 | 1.26013 × 10−9 | 10 | 63,006.50 |

| 950 °C | 300 | 2.453700 × 10−8 | 4.9074 × 10−10 | −10 | 24,537.00 |

| Charge storage for 500 KHz | |||||

| As fabricated | 300 | 3.625900 × 10−10 | 7.2518 × 10−12 | 10 | 362.59 |

| 550 °C | 300 | 3.449500 × 10−10 | 6.899 × 10−12 | −10 | 344.95 |

| 950 °C | 300 | 3.027250 × 10−10 | 6.0545 × 10−12 | 10 | 302.73 |

| Charge storage for 1 MHz | |||||

| As fabricated | 300 | 3.260335 × 10−10 | 6.52067 × 10−12 | −10 | 326.03 |

| 550 °C | 300 | 3.168324 × 10−10 | 6.33665 × 10−12 | 10 | 316.83 |

| 950 °C | 300 | 3.036700 × 10−10 | 6.0734 × 10−12 | 10 | 303.67 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chakrabartty, S.; Almawgani, A.H.M.; Kumar, S.; Kumar, M.; Acharjee, S.; Al-Shidaifat, A.; Poulose, A.; Alsuwian, T. Versatility Investigation of Grown Titanium Dioxide Nanoparticles and Their Comparative Charge Storage for Memristor Devices. Micromachines 2023, 14, 1616. https://doi.org/10.3390/mi14081616

Chakrabartty S, Almawgani AHM, Kumar S, Kumar M, Acharjee S, Al-Shidaifat A, Poulose A, Alsuwian T. Versatility Investigation of Grown Titanium Dioxide Nanoparticles and Their Comparative Charge Storage for Memristor Devices. Micromachines. 2023; 14(8):1616. https://doi.org/10.3390/mi14081616

Chicago/Turabian StyleChakrabartty, Shubhro, Abdulkarem H. M. Almawgani, Sachin Kumar, Mayank Kumar, Suvojit Acharjee, Alaaddin Al-Shidaifat, Alwin Poulose, and Turki Alsuwian. 2023. "Versatility Investigation of Grown Titanium Dioxide Nanoparticles and Their Comparative Charge Storage for Memristor Devices" Micromachines 14, no. 8: 1616. https://doi.org/10.3390/mi14081616

APA StyleChakrabartty, S., Almawgani, A. H. M., Kumar, S., Kumar, M., Acharjee, S., Al-Shidaifat, A., Poulose, A., & Alsuwian, T. (2023). Versatility Investigation of Grown Titanium Dioxide Nanoparticles and Their Comparative Charge Storage for Memristor Devices. Micromachines, 14(8), 1616. https://doi.org/10.3390/mi14081616