Effect of P-Type GaN Buried Layer on the Temperature of AlGaN/GaN HEMTs

Abstract

1. Introduction

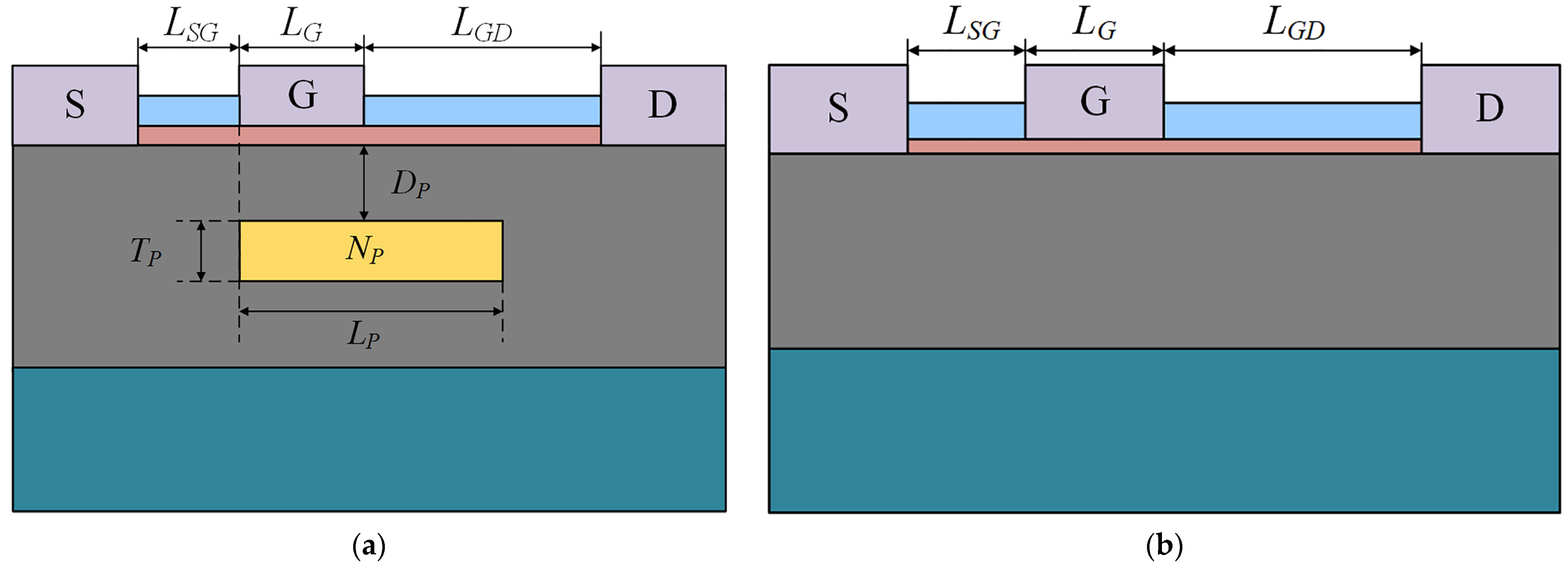

2. Device Structure and Simulation Setup

- (a)

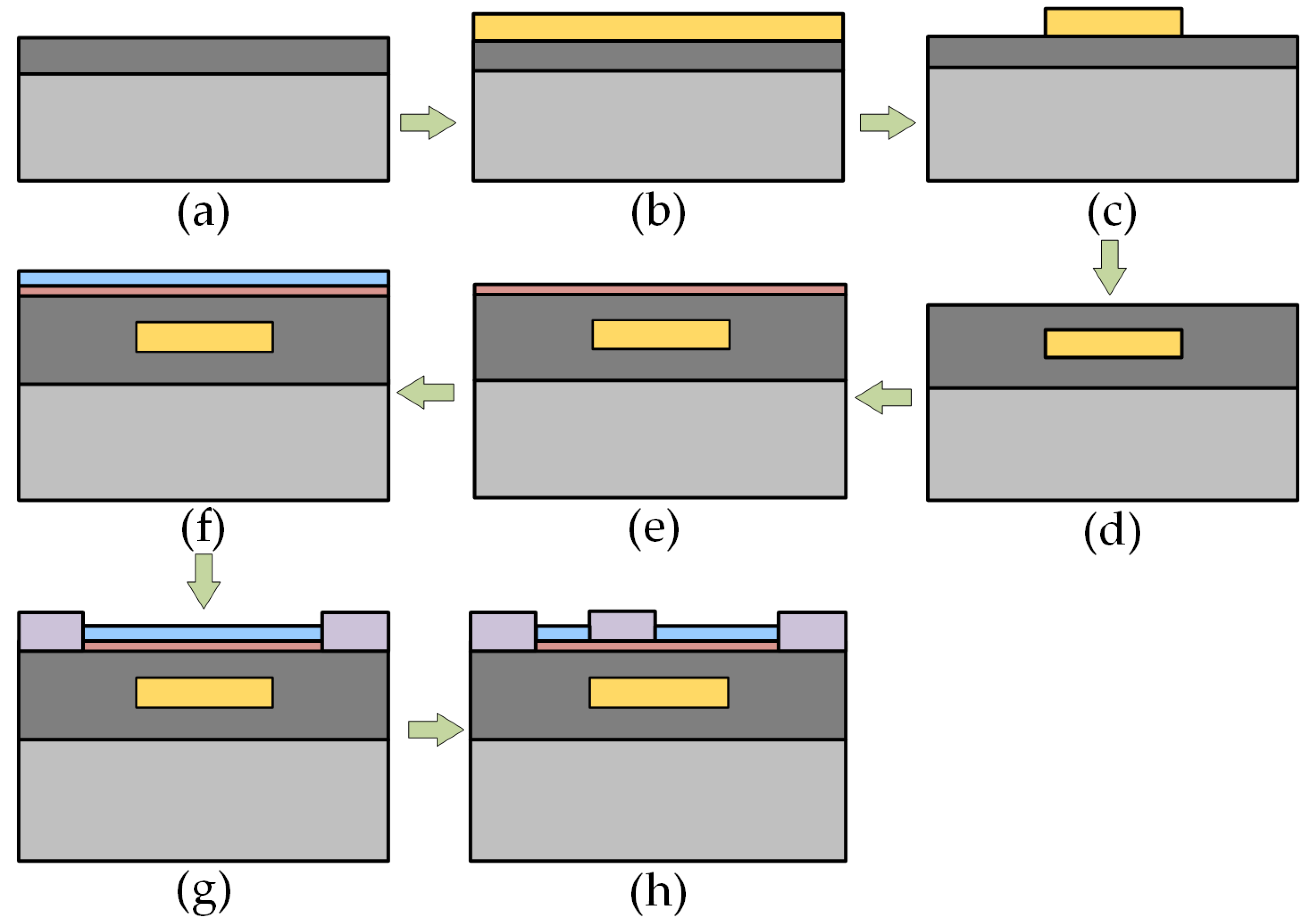

- A portion of GaN buffer layer is grown on sapphire substrate via metal–organic chemical vapor deposition (MOCVD).

- (b)

- The P-type GaN buried layer is grown via MOCVD using Mg as a P-type dopant [21].

- (c)

- Using the inductively coupled plasma (ICP) process, the portions of the P-type GaN buried layer on both ends are etched [21].

- (d)

- The remaining GaN buffer layer is grown via MOCVD.

- (e)

- The AlGaN barrier layer is grown on GaN buffer layer via MOCVD.

- (f)

- Using plasma enhanced chemical vapor deposition (PECVD), a Si3N4 layer is deposited on the AlGaN barrier layer as the passivation layer [20].

- (g)

- The source and drain contact are etched, and then electron beam evaporation is used to deposit Ti/Al/Ni/Au to form the source and drain electrodes, followed by high-temperature annealing.

- (h)

- The gate contact is etched, and then electron beam evaporation is used to deposit Ni/Au, forming the gate electrode.

3. Simulation Results and Discussion

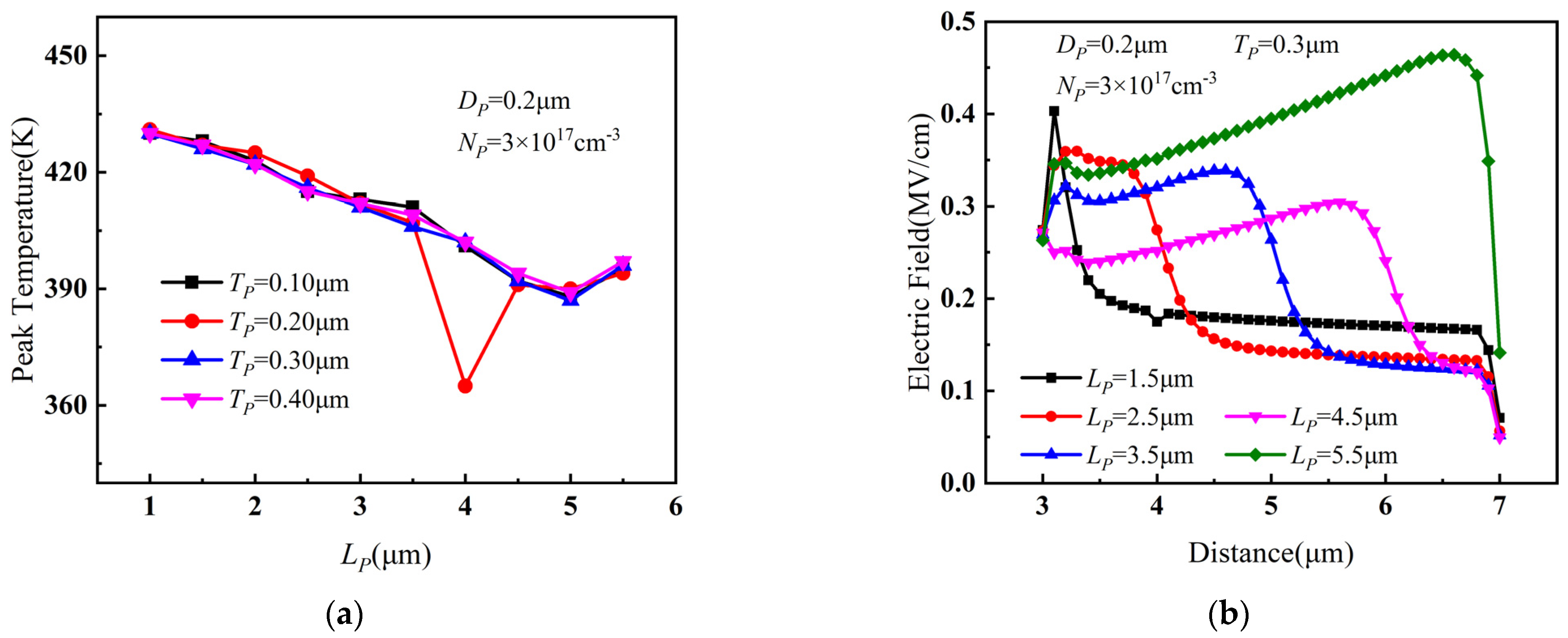

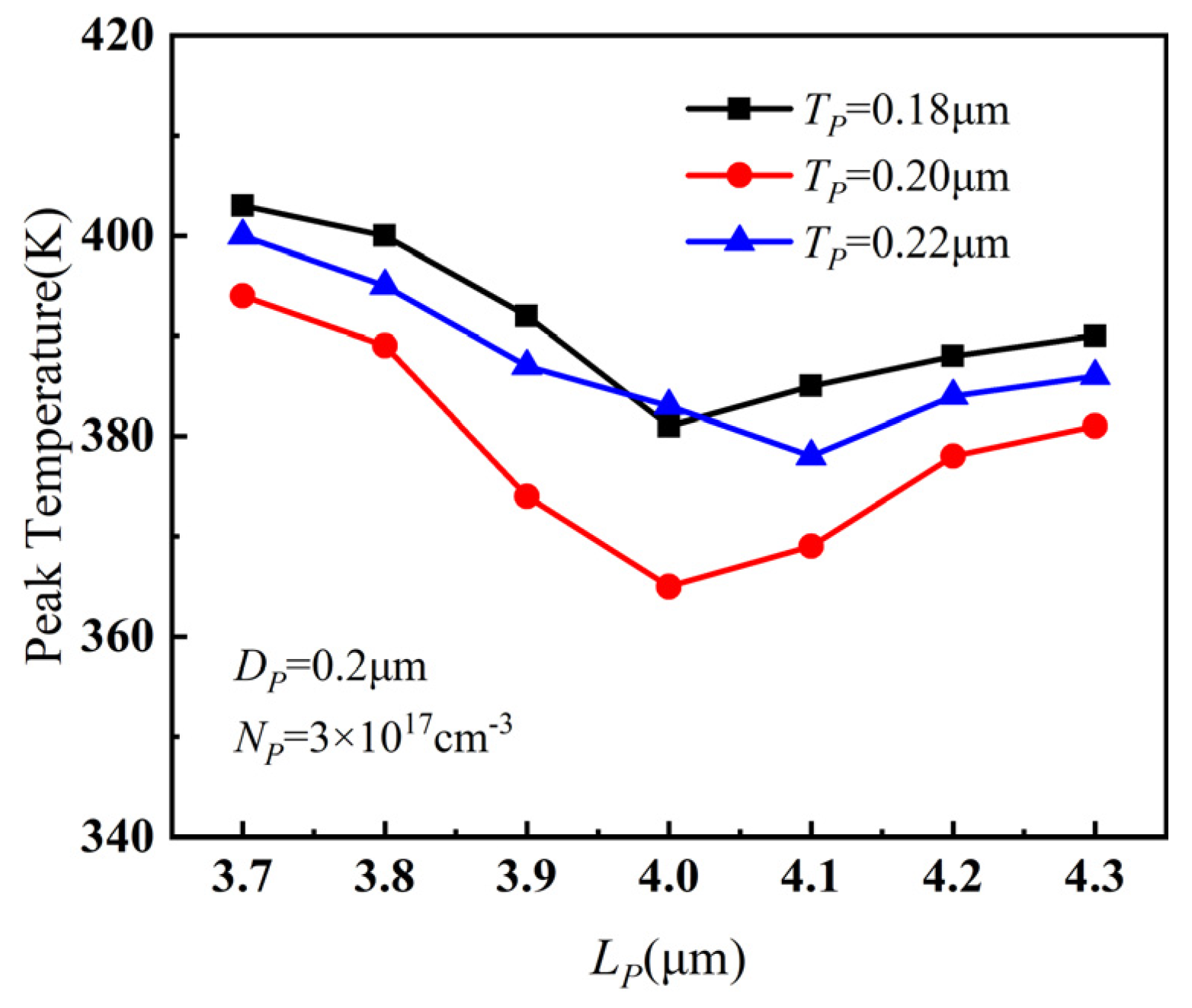

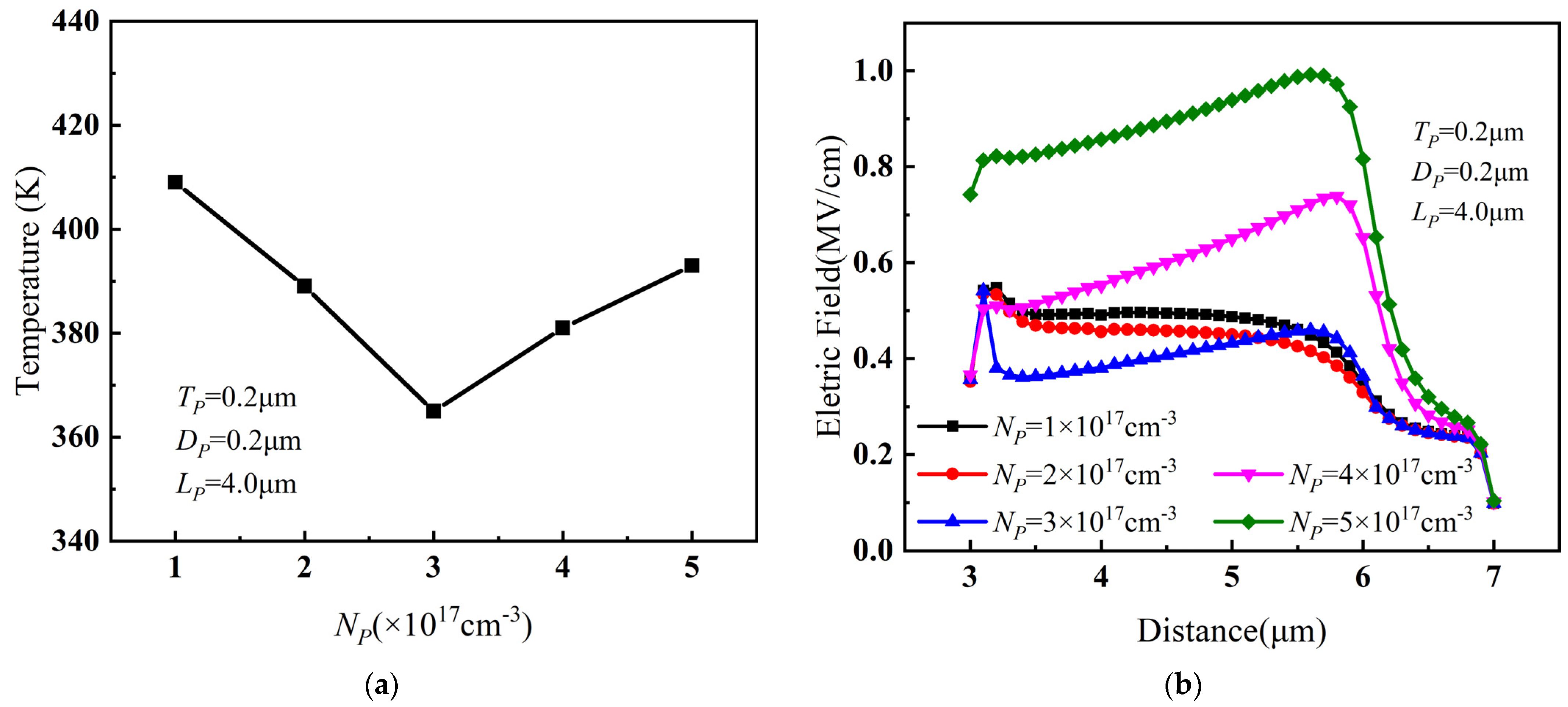

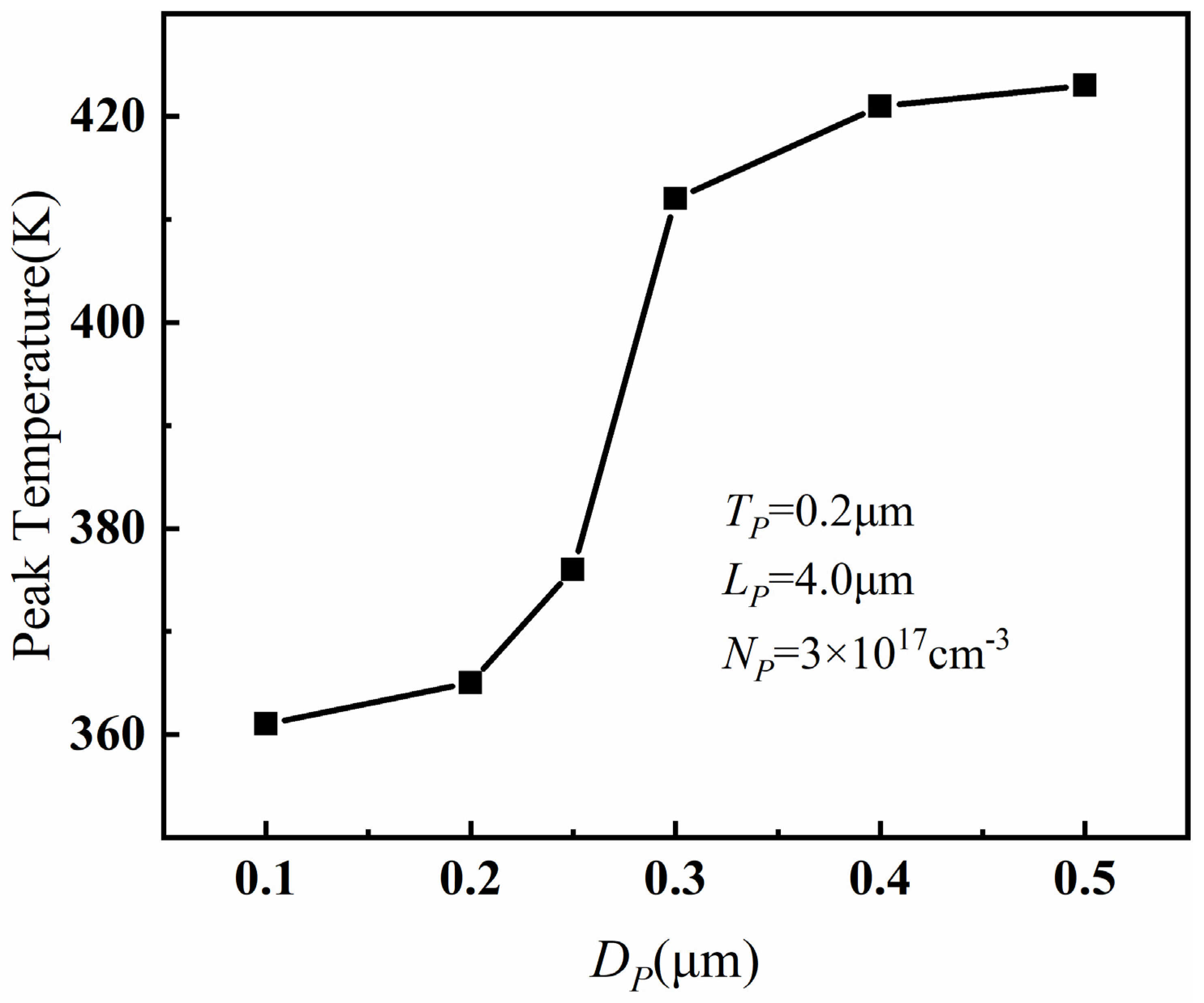

3.1. Optimization Design of PBL Structure Parameters

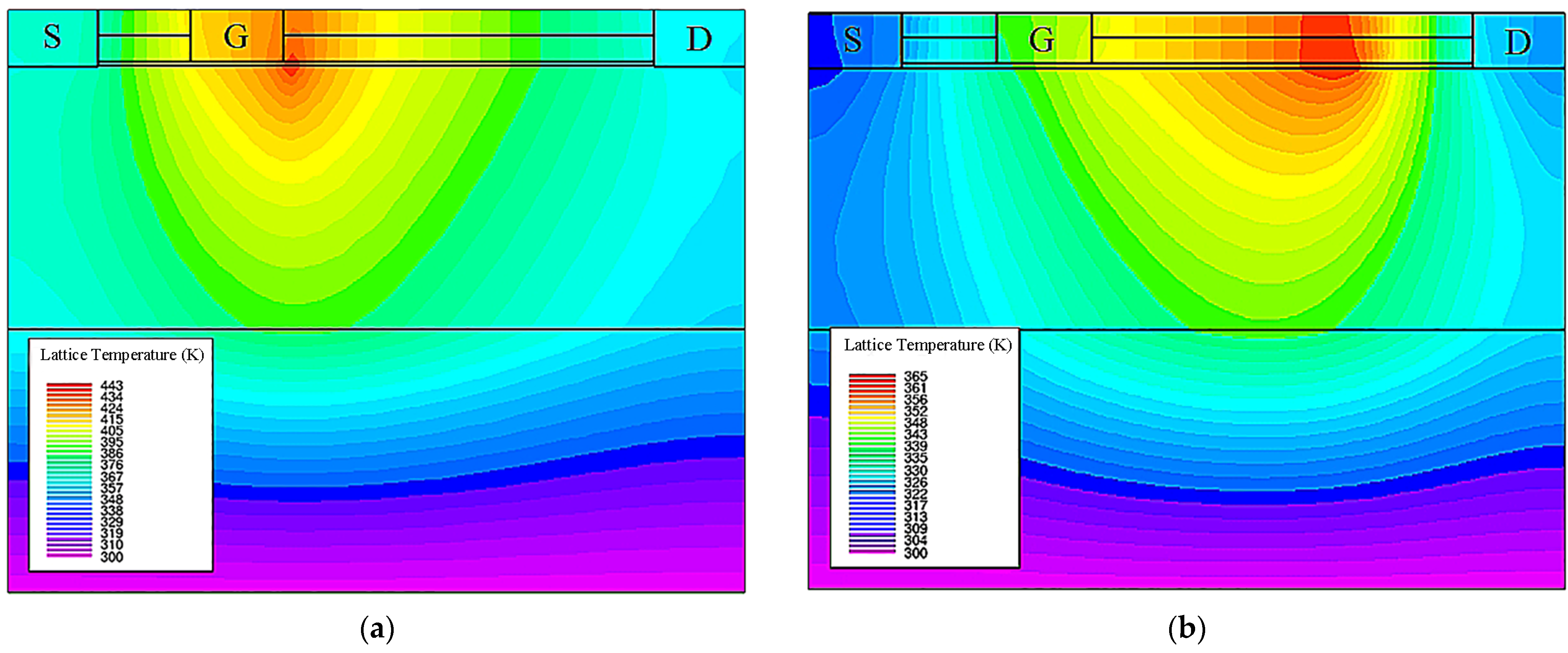

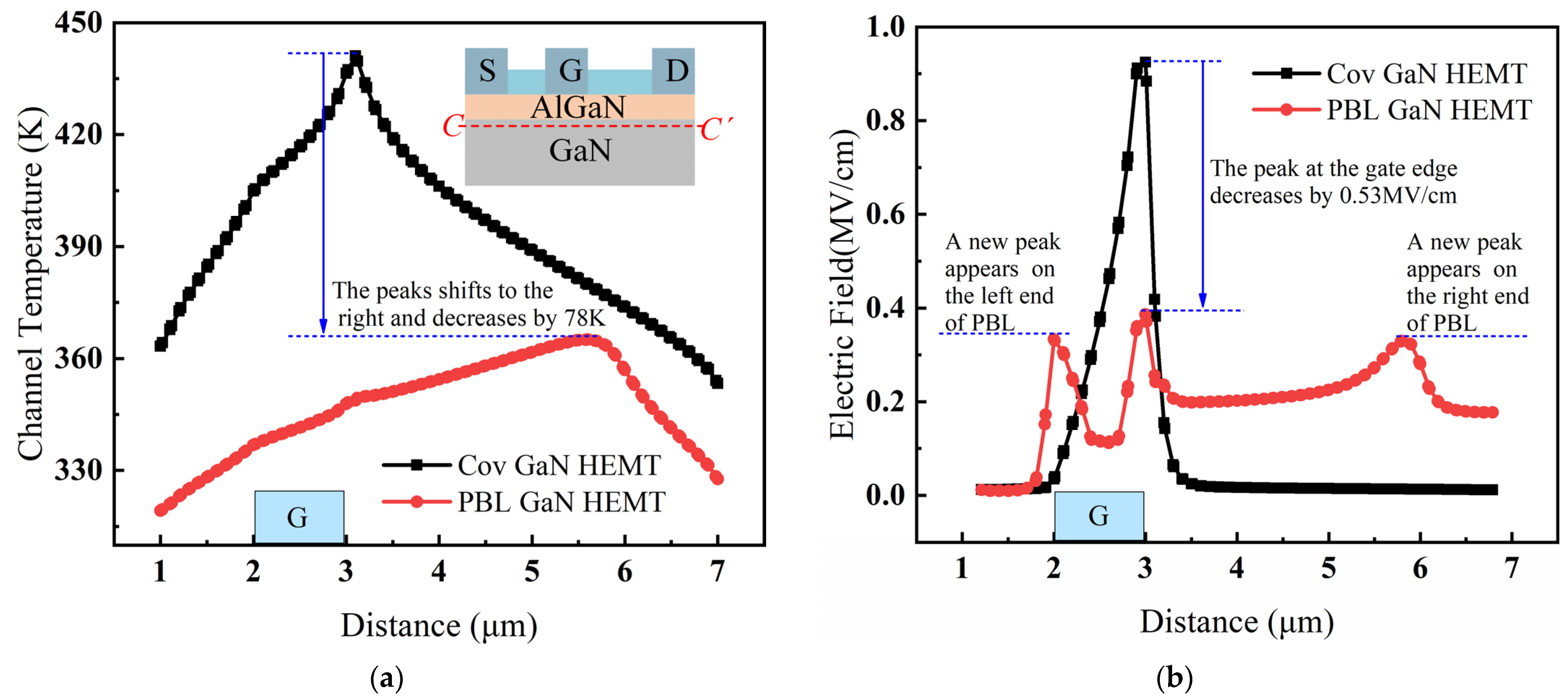

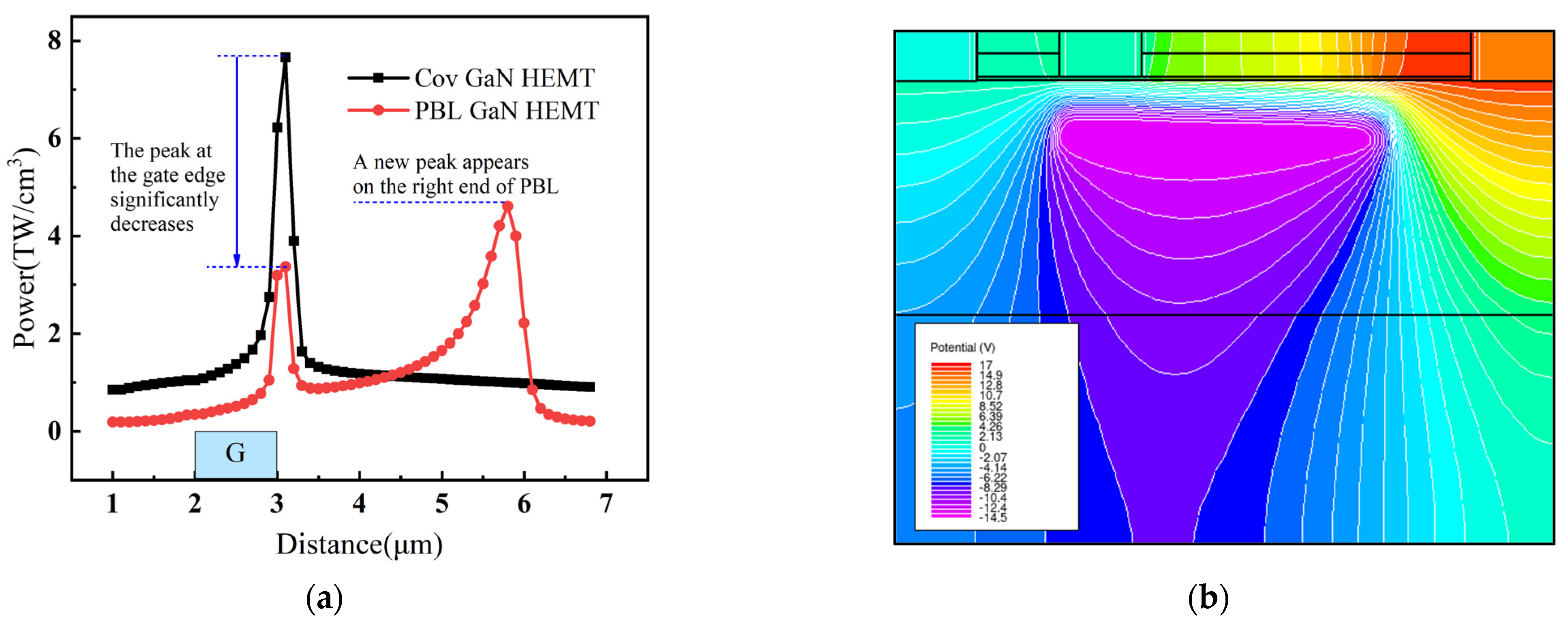

3.2. The Temperature Performance of PBL GaN HEMT

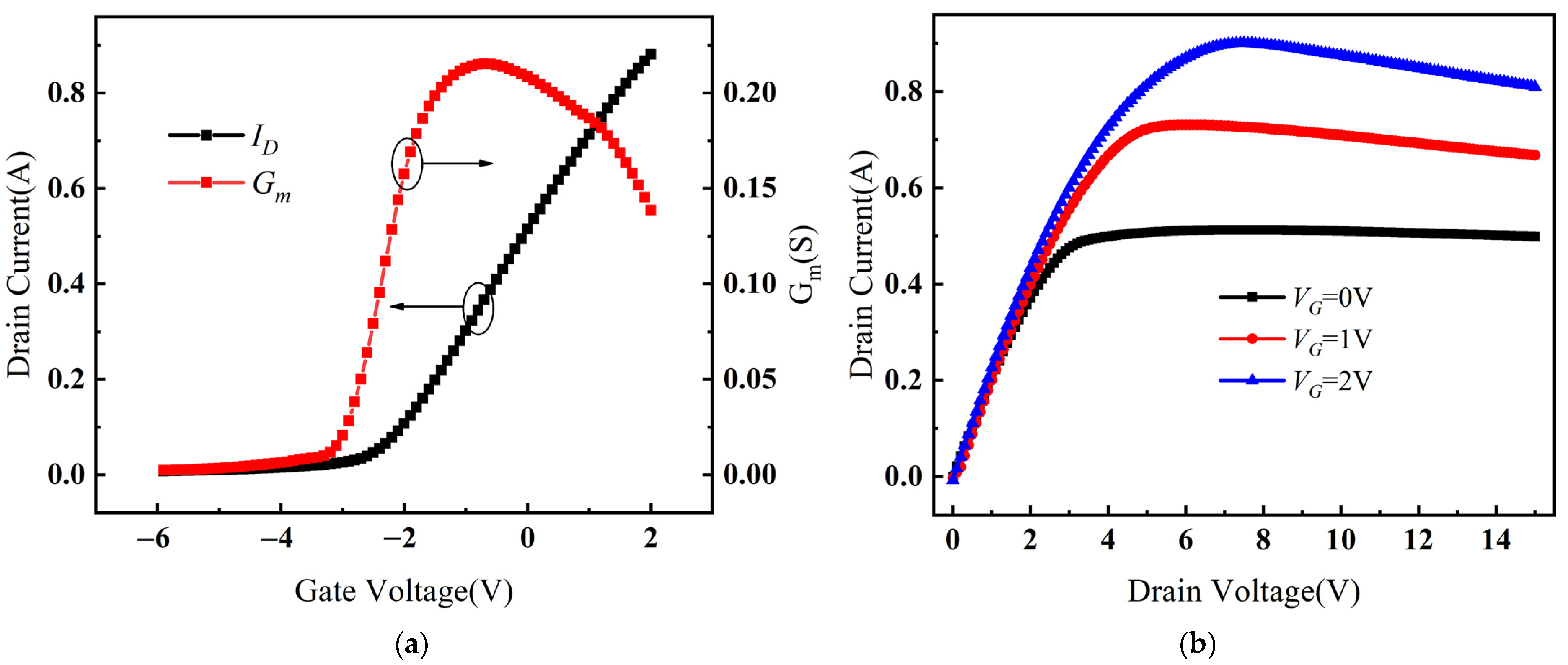

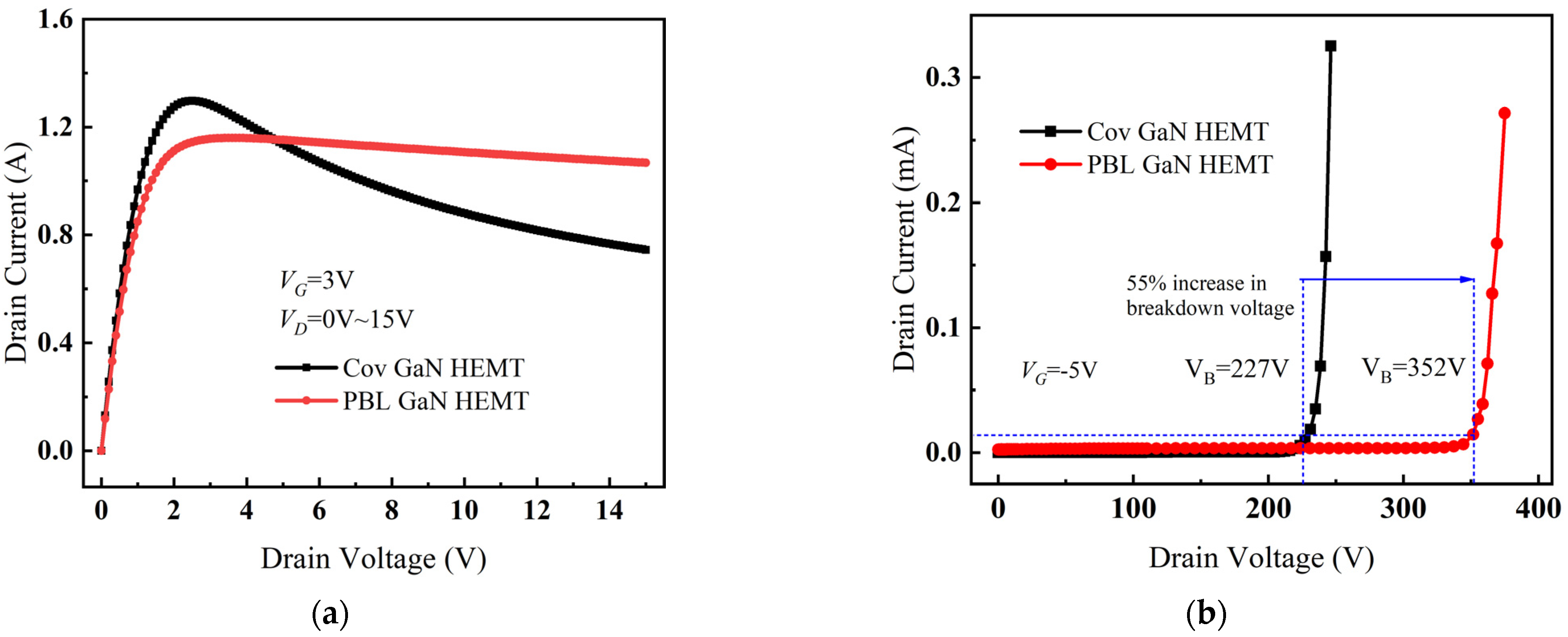

3.3. The Electrical Performance of PBL GaN HEMT

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Zhang, Y.; Huang, S.; Wei, K.; Zhang, S.; Wang, X.; Zheng, Y.; Liu, G.; Chen, X.; Li, Y.; Liu, X. Millimeter-wave AlGaN/GaN HEMTs with 43.6% power-added-efficiency at 40 GHz fabricated by atomic layer etching gate recess. IEEE Elec. Dev. Lett. 2020, 41, 701–704. [Google Scholar] [CrossRef]

- Madhulika; Jain, N.; Kumar, S.; Singh, A.K. Influence of barrier and spacer layer on structural and electrical properties of AlGaN/GaN HEMT. Int. J. Inf. Technol. 2020, 12, 119–124. [Google Scholar] [CrossRef]

- Yang, W.; Li, Y.; Li, Y.; Hu, Z.; Xie, F.; He, C.; Wang, S.; Zhou, B.; He, H.; Khan, W.; et al. Atmospheric neutron single event effect test on Xilinx 28 nm system on chip at CSNS-BL09. Microelectron. Reliab. 2019, 99, 119–124. [Google Scholar] [CrossRef]

- Trew, R.J.; Green, D.S.; Shealy, J.B. AlGaN/GaN HFET reliability. IEEE Microw. Mag. 2019, 10, 116–127. [Google Scholar] [CrossRef]

- Grishakov, K.S.; Elesin, V.F.; Ryzhuk, R.V.; Kargin, N.I.; Minnebaev, S.V. Effect of diamond and graphene heat spreaders on characteristics of AlGaN/GaN HEMT. Phys. Procedia 2015, 72, 460–464. [Google Scholar] [CrossRef]

- Jiang, S.; Lee, K.B.; Guiney, I.; Miaja, P.F.; Zaidi, Z.H.; Qian, H.; Wallis, D.J.; Forsyth, A.J.; Humphreys, C.J.; Houston, P.A. All-GaN-integrated cascode heterojunction field effect transistors. IEEE Trans. Power Electron. 2017, 32, 8743–8750. [Google Scholar] [CrossRef]

- Mu, F.; Xu, B.; Wang, X.; Gao, R.; Huang, S.; Wei, K.; Takeuchi, K.; Chen, X.; Yin, H.; Wang, D.; et al. A novel strategy for GaN-on-diamond device with a high thermal boundary conductance. J. Alloys Compd. 2022, 905, 164076. [Google Scholar] [CrossRef]

- Won, Y.; Cho, J.; Agonafer, D.; Asheghi, M.; Goodson, K.E. Fundamental cooling limits for high power density gallium nitride electronics. IEEE Trans. Compon. Packag. Manuf. Technol. 2015, 5, 737–744. [Google Scholar] [CrossRef]

- Manoi, A.; Pomeroy, J.W.; Killat, N.; Kuball, M. Benchmarking of thermal boundary resistance in AlGaN/GaN HEMTs on SiC substrates: Implications of the nucleation layer microstructure. IEEE Electron Device Lett. 2010, 31, 1395–1397. [Google Scholar] [CrossRef]

- Tao, L.; Theruvakkattil, S.; Shahsavari, R. Interlaced, nanostructured interface with graphene buffer layer reduces thermal boundary resistance in nano/microelectronic systems. ACS Appl. Mater. Interfaces 2017, 9, 989–998. [Google Scholar] [CrossRef]

- Woo, H.; Jo, Y.; Kim, J.; Roh, C.; Lee, J.; Kim, H.; Im, H.; Hahn, C.; Park, J. Effect of heating on electrical transport in AlGaN/GaN Schottky barrier diodes on Si substrate. Curr. Appl. Phys. 2014, 14, S98–S102. [Google Scholar] [CrossRef]

- Shoemaker, D.; Malakoutian, M.; Chatterjee, B.; Song, Y.; Kim, S.; Foley, B.M.; Graham, S.; Nordquist, C.D.; Chowdhury, S.; Choi, S. Diamond-incorporated flip-chip integration for thermal management of GaN and ultra-wide bandgap RF power amplifiers. IEEE Trans. Compon. Packag. Manuf. Technol. 2021, 11, 1177–1186. [Google Scholar] [CrossRef]

- Zhou, Y.; Ramaneti, R.; Anaya, J.; Korneychuk, S.; Derluyn, J.; Sun, H.; Pomeroy, J.; Verbeeck, J.; Haenen, K.; Kuball, M. Thermal characterization of polycrystalline diamond thin film heat spreaders grown on GaN HEMTs. Appl. Phys. Lett. 2017, 111, 287–305. [Google Scholar] [CrossRef]

- Du, J.; Liu, D.; Zhao, Z.; Bai, Z.; Li, L.; Mo, J.; Yu, Q. Design of high breakdown voltage GaN vertical HFETs with p-GaN buried buffer layers for power switching applications. Superlattices Microstruct. 2015, 83, 251–260. [Google Scholar] [CrossRef]

- Luo, X.; Wang, Y.; Hao, Y.; Cao, F.; Yu, C.; Fei, X. TCAD simulation of breakdown-enhanced AlGaN-/GaN-based MISFET with electrode-connected p-i-n diode in buffer layer. IEEE Trans. Electron Devices 2018, 65, 476–482. [Google Scholar] [CrossRef]

- Li, J.; Yin, Y.; Zeng, N.; Liao, F.; Lian, M.; Zhang, X.; Zhang, K.; Zhang, Y.; Li, J. A dual-gate and Γ-type field plate GaN base E-HEMT with high breakdown voltage on simulation investigation. Semicond. Sci. Technol. 2021, 36, 095036. Available online: https://iopscience.iop.org/article/10.1088/1361-6641/ac1963/meta (accessed on 6 June 2023). [CrossRef]

- Pattnaik, G.; Mohapatra, M. Comparison Of DC & RF Characteristics of AlGaN/GaN HEMT Using Different Surface Passivation Materials. In Proceedings of the 2021 IEEE 2nd International Conference on Applied Electromagnetics, Signal Processing, & Communication (AESPC), Bhubaneswar, India, 26–28 November 2021; pp. 1–5. [Google Scholar] [CrossRef]

- Luo, X.; Wang, Y.; Cao, F.; Yu, C.H.; Fei, X. A breakdown enhanced AlGaN/GaN MISFET with source-connected P-buried layer. Superlattices Microstruct. 2017, 112, 517–527. [Google Scholar] [CrossRef]

- Xu, T.; Tang, Z.; Zhou, Z.; Zhou, B. Simulation Optimization of AlGaN/GaN SBD with Field Plate Structures and Recessed Anode. Micromachines 2023, 14, 1121. [Google Scholar] [CrossRef]

- Wang, Y.; Bao, M.; Cao, F.; Tang, J.; Luo, X. Technology computer aided design study of GaN MISFET with double p-buried layers. IEEE Access. 2019, 7, 87574–87581. [Google Scholar] [CrossRef]

- Ji, D.; Laurent, M.A.; Agarwal, A.; Li, W.; Mandal, S.; Keller, S.; Chowdhury, S. Normally OFF trench CAVET with active Mg-doped GaN as current blocking layer. IEEE Trans. Electron Devices 2017, 64, 805–808. Available online: https://ieeexplore.ieee.org/document/7786867 (accessed on 6 June 2023). [CrossRef]

- Ma, M.; Cao, Y.; Lv, H.; Wang, Z.; Zhang, X.; Chen, C.; Wu, L.; Lv, L.; Zheng, X.; Tian, W.; et al. Effect of Acceptor Traps in GaN Buffer Layer on Breakdown Performance of AlGaN/GaN HEMTs. Micromachines 2022, 14, 79. [Google Scholar] [CrossRef] [PubMed]

- Silvaco. ATLAS User’s Manual; Silvaco: Santa Clara, CA, USA, 2019; pp. 330–331. Available online: https://silvaco.com/ (accessed on 3 June 2023).

- Chen, X.; Boumaiza, S.; Wei, L. Self-heating and equivalent channel temperature in short gate length GaN HEMTs. IEEE Trans. Electron Devices 2019, 66, 3748–3755. [Google Scholar] [CrossRef]

- Douglas, E.A.; Ren, F.; Pearton, S.J. Finite-element simulations of the effect of device design on channel temperature for AlGaN/GaN high electron mobility transistors. J. Vac. Sci. Technol. B 2011, 29, 020603. Available online: https://pubs.aip.org/avs/jvb/article-abstract/29/2/020603/623318/Finite-element-simulations-of-the-effect-of-device?redirectedFrom=fulltext (accessed on 3 June 2023). [CrossRef]

- Chen, X.; Boumaiza, S.; Wei, L. Modeling bias dependence of self-heating in GaN HEMTs using two heat sources. IEEE Trans. Electron Devices 2020, 67, 3082–3087. Available online: https://ieeexplore.ieee.org/abstract/document/9130855 (accessed on 9 July 2023). [CrossRef]

- Duan, B.; Yang, L.; Wang, Y.; Yang, Y. Experimental results for AlGaN/GaN HEMTs improving breakdown voltage and output current by electric field modulation. IEEE Trans. Electron Devices 2021, 68, 2240–2245. [Google Scholar] [CrossRef]

| Parameters | Values |

|---|---|

| Gate length (LG) | 1 μm |

| Gate–source spacing (LSG) | 1 μm |

| Gate–drain spacing (LGD) | 4 μm |

| Length of PBL (LP) | 1 to 5.5 μm |

| Thickness of PBL (TP) | 0.1 to 0.4 μm |

| Doping concentration of PBL (NP) | 1 × 1017 to 5 × 1017 cm−3 |

| Distance between PBL and barrier layer (DP) | 0.1 to 0.5 μm |

| Parameters | Values |

|---|---|

| TC.A (sapphire) | −12.56 |

| TC.B (sapphire) | 6.81 × 10−2 |

| TC.C (sapphire) | −7.76 × 10−5 |

| TC.NPOW (GaN) | 1.4 |

| TC.CONST (GaN) | 1.6 |

| TC.CONST (Si3N4) | 0.35 |

| TC.CONST (AlGaN) | 0.19 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lv, H.; Cao, Y.; Ma, M.; Wang, Z.; Zhang, X.; Chen, C.; Wu, L.; Lv, L.; Zheng, X.; Wang, Y.; et al. Effect of P-Type GaN Buried Layer on the Temperature of AlGaN/GaN HEMTs. Micromachines 2023, 14, 1457. https://doi.org/10.3390/mi14071457

Lv H, Cao Y, Ma M, Wang Z, Zhang X, Chen C, Wu L, Lv L, Zheng X, Wang Y, et al. Effect of P-Type GaN Buried Layer on the Temperature of AlGaN/GaN HEMTs. Micromachines. 2023; 14(7):1457. https://doi.org/10.3390/mi14071457

Chicago/Turabian StyleLv, Hanghang, Yanrong Cao, Maodan Ma, Zhiheng Wang, Xinxiang Zhang, Chuan Chen, Linshan Wu, Ling Lv, Xuefeng Zheng, Yongkun Wang, and et al. 2023. "Effect of P-Type GaN Buried Layer on the Temperature of AlGaN/GaN HEMTs" Micromachines 14, no. 7: 1457. https://doi.org/10.3390/mi14071457

APA StyleLv, H., Cao, Y., Ma, M., Wang, Z., Zhang, X., Chen, C., Wu, L., Lv, L., Zheng, X., Wang, Y., Tian, W., & Ma, X. (2023). Effect of P-Type GaN Buried Layer on the Temperature of AlGaN/GaN HEMTs. Micromachines, 14(7), 1457. https://doi.org/10.3390/mi14071457