1. Introduction

Bandgap reference (BGR) circuits are critical modules in most integrated circuit systems and are widely used in analog circuits, digital circuits, and mixed-signal circuits, such as memory circuits, A/D converters, and low dropout linear regulators. BGR circuits provide temperature-independent voltages or currents for the system-on-a-chip (SoC), and their performance determines the quality of the entire SoC. With the development of the CMOS process, the feature size of integrated circuits continues to decrease, and the operation voltage of the electronic system is becoming increasingly lower. Low-voltage and high-precision BGR circuits have received widespread attention.

The output voltage of conventional voltage-mode BGR circuits with first-order temperature compensation is 1.25 V approximately, which can achieve a TC of about a few tens of ppm/℃. In order to achieve more accurate reference voltages, higher-order temperature-compensated techniques are required for BGR circuits. Rincon-Mora et al. [

1] adjusted the reference voltage by optimizing the temperature component with the trimming process and achieved high accuracy of the output voltage. Leung et al. [

2] proposed that the ratio of resistors with the same type and size is independent of temperature, which can be used to reduce temperature drift. Ker et al. [

3] used a subtraction circuit to cancel the convex curve or the concave curve of the output reference current of two BGR circuits. Exponential temperature compensation [

4], quadratic temperature compensation [

5], and third-order compensation [

6] were also used to cancel the high-order terms of the emitter-base voltage V

EB, eliminate the temperature drift, and obtain a reference voltage with a very small TC.

In modern CMOS technology, the operation voltage of CMOS devices is lower than 1.2 V, so a reference voltage should be lower than 1.2 V. Banba et al. [

7] proposed a sub-1V BGR circuit in which the current-mode technique is adopted to scale down the output reference voltage, and a variety of high-precision BGR circuits are developed.

Compared to the first-order temperature compensation in [

7], Malcovati [

8] introduced a high-order temperature compensation, which is based on the theory that the current in the nonlinear compensation bipolar junction transistor (NLCBJT) is temperature-independent. However, high-order temperature residue terms still exist in the NLCBJT currents in this circuit, which require further rejection or elimination.

In this paper, the accuracy of the BGR is further improved on the basis of [

8]. The rest of this paper is organized as follows:

Section 2 describes the operation principle of a conventional current-mode BGR circuit;

Section 3 describes the two proposed solutions for nonlinear compensation BGR circuits;

Section 4 presents the simulation results that verify the accuracy of the proposed high-order terms compensated circuit; and the conclusions are provided in

Section 5.

2. Principle of Conventional Current-Mode BGR Circuits

The low-voltage BGR circuit proposed by Banba et al. [

7] is a current-mode BGR circuit whose output reference current

IREF is realized by the sum of two currents. One is complementary to the absolute temperature

ICTAT, and the other is proportional to the absolute temperature

IPTAT. First, a temperature-independent reference current was generated.

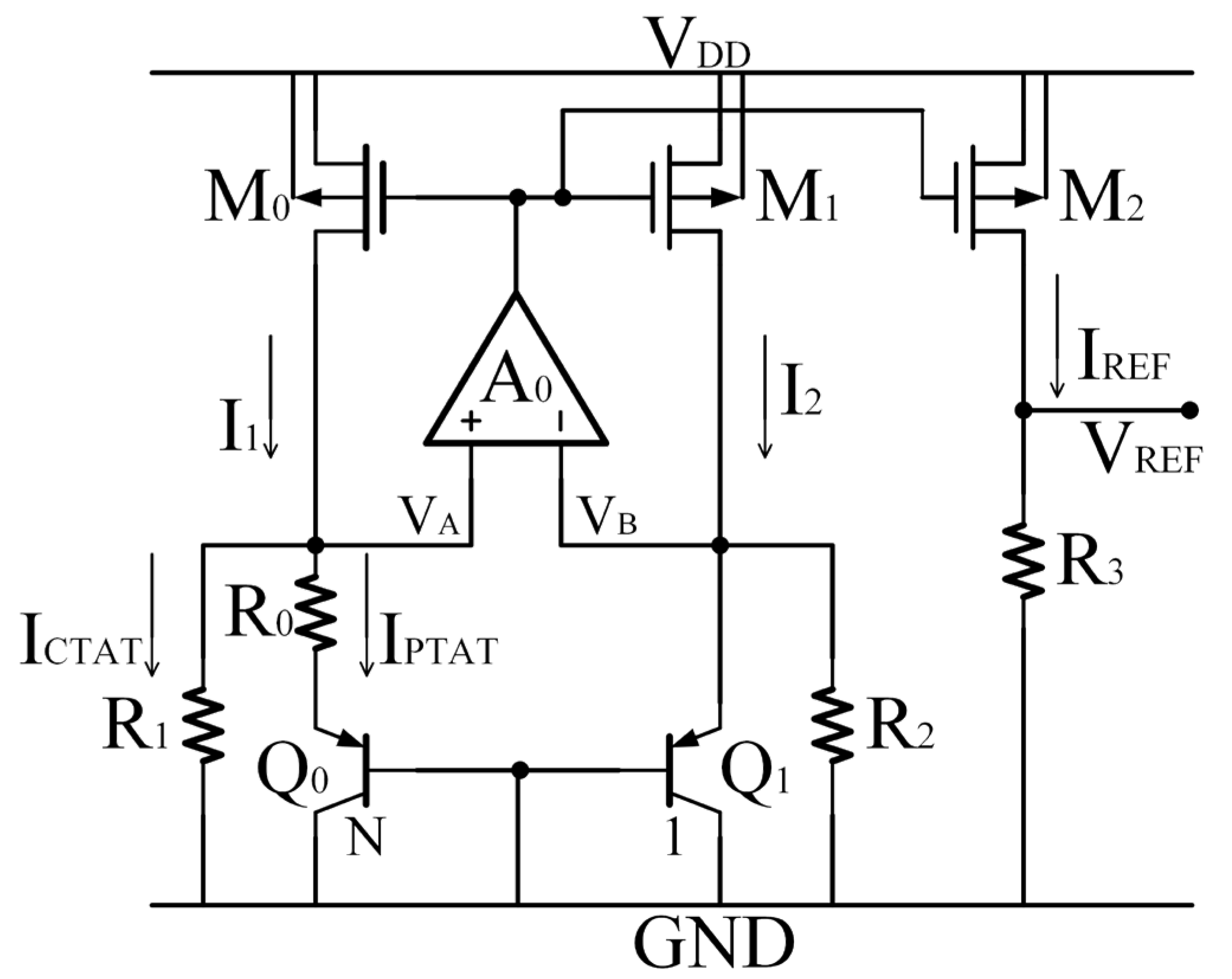

As presented in

Figure 1, due to the effect of negative feedback, the relationship

VA =

VB =

VEB1 and a PTAT current

IPTAT proportional to

VT is achieved. With additional equal resistors

R1 and

R2 (

R1 =

R2 =

R1,2), the BGR circuit achieves a CTAT current

ICTAT proportional to

VEB. The currents

I1 and

I2 are the sum of the currents

IPTAT and

ICTAT, flowing through the current mirror that consists of the transistors M

0, M

1, and M

2 with the same aspect ratio. The currents can be expressed as follows:

Then, a low reference voltage

VREF can be generated and expressed as

However, the current-mode BGR circuit shown in

Figure 1 still belongs to first-order temperature compensation. A large high-order temperature current flows into the emitter of

Q1, which affects the accuracy of

VREF. According to the study by Tsividis et al. [

9], an accurate analysis of the temperature effects on

VEB-

T characteristics can be expressed as

where

VG0(

Tr) is the bandgap voltage of silicon at the reference temperature

Tr, n is a temperature-independent and process-dependent constant around 4, and

δ is a factor of the temperature dependent on the collector current, which is equal to 1 if the current in the BJT is PTAT and becomes 0 when the current is temperature-independent.

VT is the thermal voltage,

k is Boltzmann’s constant, and

q is the electric charge.

In Equation (3), the second item has a first-order TC, whereas the third item is a high-order temperature nonlinear term that should be rejected or eliminated to achieve a high-precision BGR.

On the basis of [

7], Malcovati et al. [

8] presented a high-precision BGR circuit with a low supply voltage, where nonlinear currents were generated to compensate for the high-order errors, as shown in

Figure 2.

The currents flowing into

Q0 and

Q1 are proportional to the absolute temperature so that the parameter

δ in the expression of

VEB is equal to 1. Since the currents flowing into Q

2 are temperature-independent, the parameter

δ is equal to 0 [

8].

The

VEB of

Q0 and

Q1 can be expressed as

The current in M

0 is

which is the current with a low TC after high-order temperature nonlinear compensation. The current is copied by M

2 and injected into a diode connected to NLCBJT

Q2, which is expressed by

Because the nonlinear current I

NL is very small, its TC can be ignored [

8]. Then, a

VEB with

δ = 0 is produced across

Q2, which can be expressed as

Equation (7) is subtracted from (4) and leads to a nonlinear voltage

VNL, which is expressed as

where the first term in the equation is the nonlinear term of temperature, and the second term is the error of the linear term of the

VEB of two BJT

Q1 and

Q2 with the same geometry; however, the emitter currents

IE,Q1 and

IE,Q2 are not equal, so the error of the linear term is not equal to zero. Equation (8) is then corrected.

The values of resistors R

3 and R

4 are equal, and the

INLs generated on them are equal. Then, the current of

IPTAT +

ICTAT −

INL follows M

4 and R

5, as shown in

Figure 3.

The output reference voltage

VREF becomes

where the third term is the nonlinear part, and it can be used to effectively compensate for the nonlinear item of the second term,

VEB,Q0,1. By substituting (4) into (9) and setting n − 1 equal to

, the nonlinear temperature term in

VREF can be eliminated, and a high-precision reference voltage can be achieved.

This BGR circuit achieves an output reference voltage of 0.536 V and obtains a TC of 7.5 ppm/K over a wide temperature range of 80 °C (from 0 °C to 80 °C). Compared to the BGR circuit without the curvature correction technique, the BGR circuit is improved by about three times.

However, in this structure, the expression for the emitter current of

Q2 is actually

where there are excess high-order temperature terms with a certain impact on

IREF. The coefficient of this current can be further reduced, and a more accurate

IREF can be achieved.

3. Proposed High-Precision Current-Mode BGR Circuit

In order to completely eliminate high-order temperature terms in the current flowing through Q2, a novel high-precision compensation BGR structure is proposed in this paper.

On the basis of the conventional curvature-compensated BGR circuit, the transistor M

3 is first added to mirror the current in M

0 flowing into BJT

Q3 and then form a new branch, which can share the nonlinear current flowing into the same BJT, as shown in

Figure 3.

At this time, the current flowing through

Q2 and

Q3 is

The TC of the nonlinear compensation BJT current is reduced, which makes the output reference current more accurate.

In order to further eliminate high-order temperature terms, a BGR circuit with high-order temperature compensation was designed, as shown in

Figure 4.

Let R5 be equal to R3 and R4 (R3 = R4 = R5). Based on the characteristics of the operational amplifier (OPAMP) A1 and A2, two branches, each with a nonlinear current similar to INL, are formed and injected into Q2 and Q3 to offset the excess high-order temperature terms.

The circuit of the OPAMP A

0, A

1, and A

2 is provided in

Figure 5, where the input stage of this circuit mainly consists of a PMOS transistor differential pair M

21 and M

22 and an NMOS transistor differential pair M

23 and M

24 placed in parallel as a rail-to-rail differential input stage, whose range of input common-mode voltage can be from ground to V

DD. The dominant pole of the circuit is located at the output port. The product of the equivalent impedance and capacitance is large, so the position of the pole is close to the DC point. And the non-dominant pole of the circuit is located at the node between the drain of M

32 and the source of M

33, and the other pole is located between the source of M

34 and the drain of M

35. The output impedance and parasitic capacitance of these two nodes are both small so that their poles are far from the dominant pole. So this circuit can be regarded as only one pole approximately and is kept stable through simple compensation.

This formation is theoretically completely independent of temperature.

The design details of the proposed high-precision current-mode BGR and OPAMP circuits A

0, A

1, and A

2 are provided in

Table 1.

With the same power supply voltage, the same component sizes, and the same temperature range from −50 °C to 120 °C, the current

IPTAT +

ICTAT − 3

INL flowing into Q

2 in

Figure 2, the current

IPTAT +

ICTAT − 2

INL flowing into Q

2 or Q

3 in

Figure 3, and the current

IPTAT +

ICTAT −

INL flowing into Q

2 or Q

3 in

Figure 4 simulated in the SMIC 55 nm CMOS process are shown in

Figure 6.

Compared to

Figure 2 and

Figure 3, the current curve in

Figure 4 is the most stable, and the variation is the smallest. In other words, the temperature stability is the best.

The I

REF of the circuit in

Figure 2 varies from the minimum of 4.2049 μA to the maximum of 4.2227 μA with a change of 17.8 nA, the I

REF in

Figure 3 varies from the minimum of 4.1817 μA to the maximum of 4.1926 μA with a change of 10.9 nA, and the I

REF in

Figure 4 varies from the minimum of 4.1539 μA to the maximum of 4.1563 μA with a change of 2.4 nA. It can be seen that the I

REF of the proposed high-precision current-mode BGR circuit is more stable significantly.

4. Simulation Results

The proposed current-mode BGR circuit with a high-order temperature compensation was designed using the SMIC 55 nm CMOS process. The size of the layout of the proposed circuit including dummies turned out to be 300.43 μm × 148.67 μm, which is illustrated in

Figure 8.

- A.

The output reference current

With a supply voltage of 3.3 V, the I

REF of the proposed circuit measured from −50 °C to 120 °C is presented in

Figure 9.

The equation of TC can be expressed as

In the current-mode BGR circuit, the VREF in the above equation should be replaced by IREF, while the rest remains unchanged. IREF over the whole temperature range is about 2.4 nA, varying from 3.6829 μA to 3.6853 μA. So, the typical TC can be calculated as 3.78 ppm/°C.

- B.

Monte Carlo simulation

The Monte Carlo simulation is conducted to assess the circuit stability due to the influence of the process and mismatched variations. Three hundred iterations of the generated I

REF are shown in

Figure 10.

The simulation results show that I

REF varied from 3.6789 μA to 3.6881 μA under the worst-case scenario in

Figure 10a, whose TC is about 7.64 ppm/°C. And it can be calculated that the mean value μ of TC is 4.51 ppm/℃, and the mean square error σ is 0.615 ppm/°C in

Figure 10b.

The Monte Carlo simulation covers over 95% of the process corners and mismatches, which ensures a certain qualification rate for the product. However, the process corners have significant process variations under extreme conditions and require to be trimmed. Under the process corner of ss, there is a maximum deviation of 6 nA from the typical value in this paper. Due to the accuracy requirements of the BGR circuit, trims need to be made. Three-bit trimming is adopted, which means that there are eight trimming states. Three states greater than the typical value are set, and each state can be stepped by 3 nA, so a total of 9 nA can be stepped. Four trimming states below the typical value are set, and each state can be stepped by 3 nA, and a total of 12 nA can be stepped. Because trimming is an engineering implementation process, this paper does not provide detailed circuit implementation steps.

Figure 11 shows the simulation result of the output I

REF versus the temperature of the process corners, including ff, fs, sf, and ss, where the process corners of ss and fs are trimmed in one step to obtain better results, and those of ff and sf are maintained in the set state of tt without any trimming. At the worst process corner ff, the TC is about 7.97 ppm/°C.

- C.

Stability

Figure 12 shows the AC analysis results of the BGR for the gain and phase frequency response of the process corners, including tt, ff, fs, sf, and ss of the proposed circuit.

It can be observed that the phase margin is better than 76.63 degrees, and the gain margin is about 16.64 dB. When the gain is 0 dB, the phase margin is much greater than 60 degrees, which is very stable.

- D.

Transient response

Figure 13 illustrates the start-up process of the proposed circuit with a supply voltage V

DD step from 0 V to 3.3 V at an edge time of 1 ms, and when I

REF flows through a high-precision resistor with a temperature compensation of 160 kΩ, the proposed BGR circuit takes 0.14 ms to reach the normal operating state.

- E.

Comparison between the simulated characteristics of the proposed design and other works

The performance of the proposed BGR circuit is compared to that of other previous BGR circuits [

10,

11,

12,

13,

14], as shown in

Table 2.

It can be observed from

Table 2 that due to more accurate high-order compensation, the TC of the proposed structure is superior to that of previous works over a wider range of temperatures, and there are also certain comprehensive advantages in layout area, current consumption, and PSR.

In order to evaluate the overall performance of the BGR circuits, an evaluation parameter figure-of-merit (

FOM) defined in this paper can be expressed as

Because the layout area is related to the process, for the purpose of a fair comparison, the parameter of the layout area is not used in

FOM, which only uses the temperature range, best

TC, quiescent current, and

PSR. It can be seen from the results that the value of

FOM in this paper is much higher than that in [

11,

15], almost similar to that in [

12,

13], but lower than that in [

10]. However, the

FOM of [

10] is only because of the excellent parameter of

IQ, while the rest of the performance is ordinary. The most important parameter of the BGR circuit is the temperature coefficient, which is best identified in this paper.

- F.

Post-layout simulation

The results of the post-layout simulations are shown in

Table 3.