Performance Degradation in Static Random Access Memory of 10 nm Node FinFET Owing to Displacement Defects

Abstract

1. Introduction

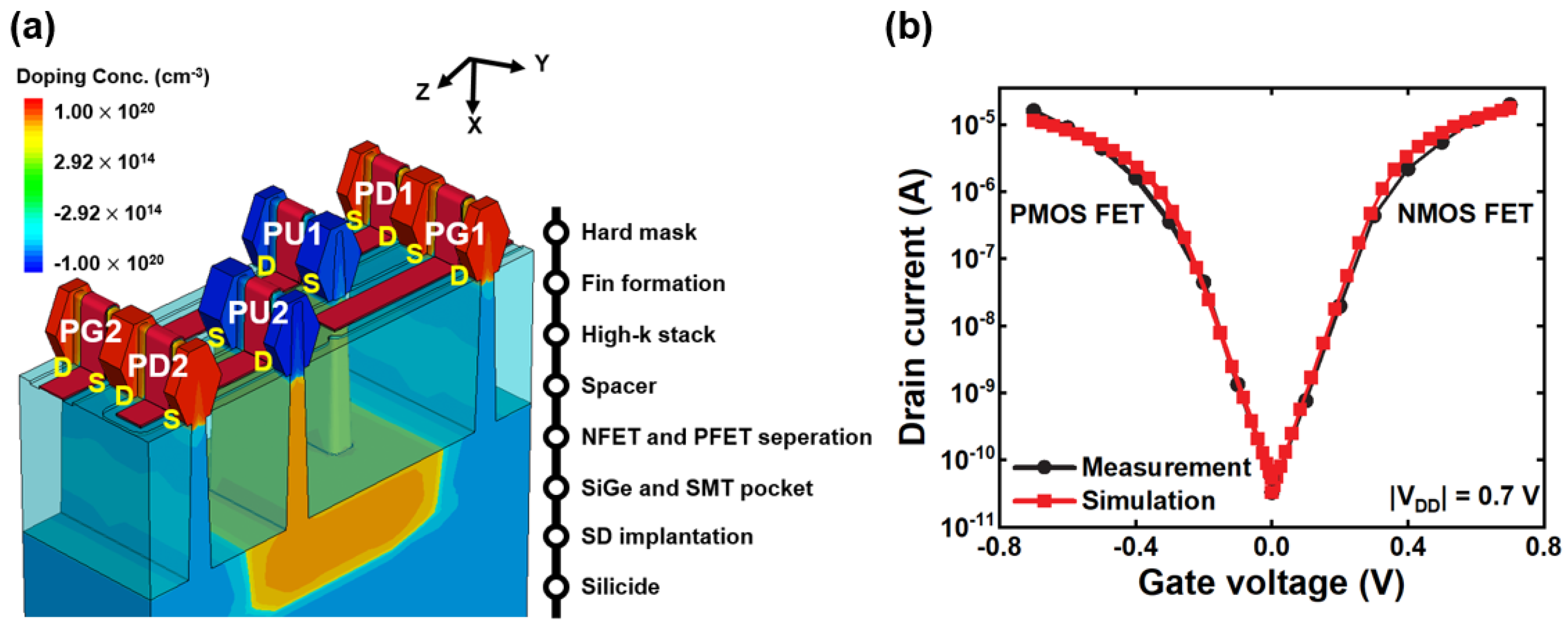

2. Simulation Modeling Methodology

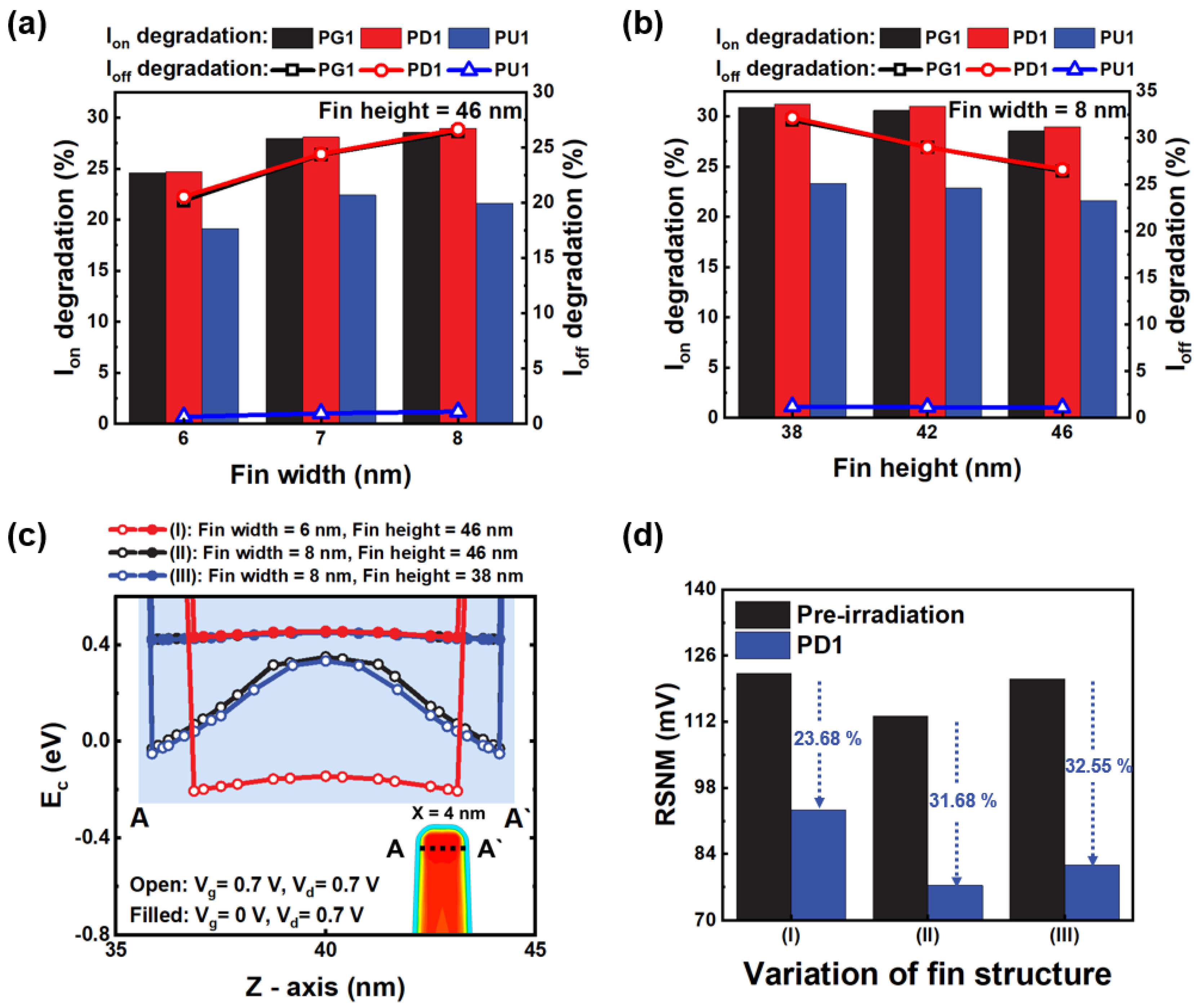

- 8 nm at the top of the fin (fin height = 2 nm);

- 9 nm at the middle of the fin (fin height = 20 nm);

- 11 nm at the bottom of the fin (fin height = 40 nm).

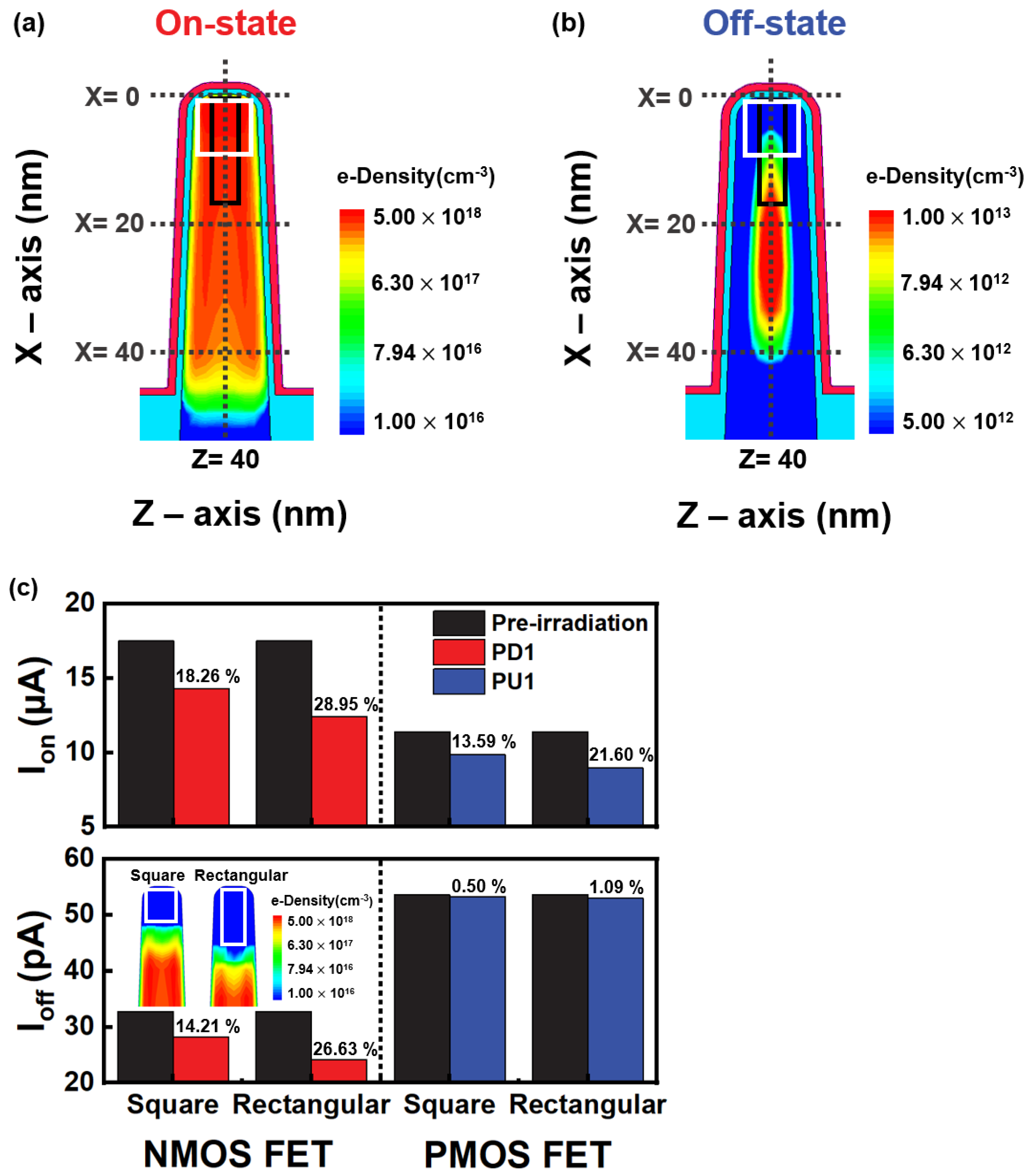

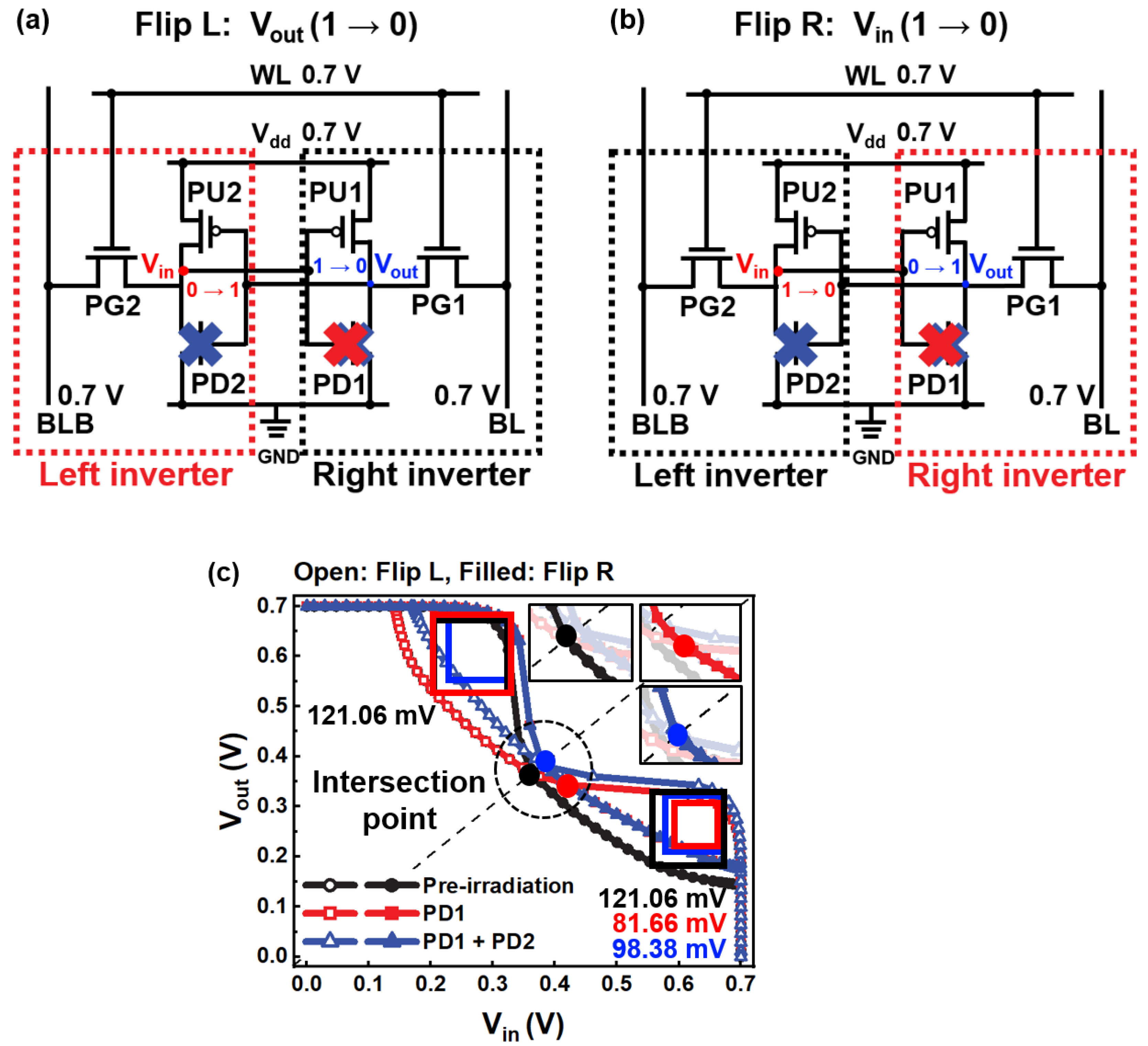

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Madhavi, K.B.; Tripathi, S.L. Electrical Characterization of highly stable 10nm triple-gate FinFET for different contacts and oxide region materials. Silicon 2022, 14, 12281–12291. [Google Scholar] [CrossRef]

- Kumar, T.S.; Tripathi, S.L. Leakage Reduction in 18 nm FinFET based 7T SRAM Cell using Self Controllable Voltage Level Technique. Wirel. Pers. Commun. 2020, 116, 1837–1847. [Google Scholar] [CrossRef]

- Navaneetha, A.; Bikshalu, K. Reliability and Power Analysis of FinFET Based SRAM. Silicon 2021, 14, 5855–5862. [Google Scholar] [CrossRef]

- Kumar, T.S.; Tripathi, S.L. Process evaluation in FinFET based 7T SRAM cell. Analog. Integr. Circuits Signal Process. 2021, 109, 545–551. [Google Scholar] [CrossRef]

- Kawasaki, H.; Okano, K.; Kaneko, A.; Yagishita, A.; Izumida, T.; Kanemura, T.; Kasai, K.; Ishida, T.; Sasaki, T.; Takeyama, Y.; et al. Embedded Bulk FinFET SRAM Cell Technology with Planar FET Peripheral Circuit for hp32 nm Node and Beyond. In Proceedings of the 2006 Symposium on VLSI Technology, Honolulu, HI, USA, 13–15 June 2006; Digest of Technical Papers. pp. 70–71. [Google Scholar] [CrossRef]

- Kim, J.; Lee, J.-S.; Han, J.-W.; Meyyappan, M. Caution: Abnormal Variability Due to Terrestrial Cosmic Rays in Scaled-Down FinFETs. IEEE Trans. Electron Devices 2019, 66, 1887–1891. [Google Scholar] [CrossRef]

- Nidhin, T.S.; Bhattacharyya, A.; Behera, R.; Jayanthi, T.; Velusamy, K. Understanding radiation effects in SRAM-based field programmable gate arrays for implementing instrumentation and control systems of nuclear power plants. Nucl. Eng. Technol. 2017, 49, 1589–1599. [Google Scholar] [CrossRef]

- Hughart, D.R.; Schrimpf, R.D.; Fleetwood, D.M.; Tuttle, B.R.; Pantelides, S.T. Mechanisms of Interface Trap Buildup and Annealing during Elevated Temperature Irradiation. IEEE Trans. Nucl. Sci. 2011, 58, 2930–2936. [Google Scholar] [CrossRef]

- Dodd, P.; Massengill, L. Basic mechanisms and modeling of single-event upset in digital microelectronics. IEEE Trans. Nucl. Sci. 2003, 50, 583–602. [Google Scholar] [CrossRef]

- Srour, J.R.; Palko, J.W. Displacement Damage Effects in Irradiated Semiconductor Devices. IEEE Trans. Nucl. Sci. 2013, 60, 1740–1766. [Google Scholar] [CrossRef]

- Srour, J.; Marshall, C.; Marshall, P. Review of displacement damage effects in silicon devices. IEEE Trans. Nucl. Sci. 2003, 50, 653–670. [Google Scholar] [CrossRef]

- Messenger, G. A summary review of displacement damage from high energy radiation in silicon semiconductors and semiconductor devices. IEEE Trans. Nucl. Sci. 1992, 39, 468–473. [Google Scholar] [CrossRef]

- Han, J.-W.; Meyyappan, M.; Kim, J. Single Event Hard Error due to Terrestrial Radiation. In Proceedings of the 2021 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 21–25 March 2021; pp. 1–6. [Google Scholar] [CrossRef]

- Mohsen, M.Y.; Hassan, M.S.; Aziz, M.; Abdel-Rahman, M.A. Investigating the neutronic, thermal-hydraulic, and solid mechanics analysis for AP-1000 nuclear reactor. Energy Sources Part A Recovery Util. Environ. Eff. 2021, 1–23. [Google Scholar] [CrossRef]

- Ziegler, J.; Lanford, W. The effect of sea level cosmic rays on electronic devices. IEEE ISSCC Dig. Tech. 1980, XXIII, 70–71. [Google Scholar] [CrossRef]

- King, M.P.; Wu, X.; Eller, M.; Samavedam, S.; Shaneyfelt, M.R.; Silva, A.I.; Draper, B.L.; Rice, W.C.; Meisenheimer, T.L.; Felix, J.A.; et al. Analysis of TID Process, Geometry, and Bias Condition Dependence in 14-nm FinFETs and Implications for RF and SRAM Performance. IEEE Trans. Nucl. Sci. 2016, 64, 285–292. [Google Scholar] [CrossRef]

- Ball, D.R.; Alles, M.L.; Schrimpf, R.D.; Cristoloveanu, S. Comparing single event upset sensitivity of bulk vs. SOI based FinFET SRAM cells using TCAD simulations. In Proceedings of the 2010 IEEE International SOI Conference (SOI), San Diego, CA, USA, 11–14 October 2010. [Google Scholar]

- Kauppila, A.V.; Bhuva, B.L.; Kauppila, J.S.; Massengill, L.W.; Holman, W.T. Impact of Process Variations on SRAM Single Event Upsets. IEEE Trans. Nucl. Sci. 2011, 58, 834–839. [Google Scholar] [CrossRef]

- Synopsys Inc. Sentaurus Device User Guide; Version R-2020.09; Synopsys: San Jose, CA, USA, 2020. [Google Scholar]

- Thirunavukkarasu, V.; Jhan, Y.-R.; Liu, Y.-B.; Wu, Y.-C. Performance of Inversion, Accumulation, and Junctionless Mode n-Type and p-Type Bulk Silicon FinFETs with 3-nm Gate Length. IEEE Electron Device Lett. 2015, 36, 645–647. [Google Scholar] [CrossRef]

- Han, J.-W.; Wong, H.Y.; Moon, D.-I.; Braga, N.; Meyyappan, M. Stringer Gate FinFET on Bulk Substrate. IEEE Trans. Electron Devices 2016, 63, 3432–3438. [Google Scholar] [CrossRef]

- Paasch, G.; Übensee, H. A modified local density approximation. Electron density in inversion layers. Phys. Status Solidi 1982, 113, 165–178. [Google Scholar] [CrossRef]

- Guo, D.; Karve, G.; Tsutsui, G.; Lim, K.-Y.; Robison, R.; Hook, T.; Vega, R.; Liu, D.; Bedell, S.; Mochizuki, S.; et al. FINFET technology featuring high mobility SiGe channel for 10nm and beyond. In Proceedings of the 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016; pp. 1–2. [Google Scholar] [CrossRef]

- Tsutsui, G.; Zhou, H.; Greene, A.; Robison, R.; Yang, J.; Li, J.; Prindle, C.; Sporre, J.R.; Miller, E.R.; Liu, D.; et al. SiGe FinFET for practical logic libraries by mitigating local layout effect. In Proceedings of the 2017 Symposium on VLSI Technology, Kyoto, Japan, 5–8 June 2017; pp. T122–T123. [Google Scholar] [CrossRef]

- Cho, J.; Geelhaar, F.; Rana, U.; Vanamurthy, L.; Sporer, R.; Benistant, F. TCAD analysis of SiGe channel FinFET devices. In Proceedings of the 2017 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Kamakura, Japan, 7–9 September 2017; pp. 357–360. [Google Scholar] [CrossRef]

- Auth, C.; Aliyarukunju, A.; Asoro, M.; Bergstrom, D.; Bhagwat, V.; Birdsall, J.; Bisnik, N.; Buehler, M.; Chikarmane, V.; Ding, G.; et al. A 10 nm high performance and low-power CMOS technology featuring 3rd generation FinFET transistors, Self-Aligned Quad Patterning, contact over active gate and cobalt local interconnects. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 29.1.1–29.1.4. [Google Scholar] [CrossRef]

- Kim, K.; Kim, J. Insights into radiation displacement defect in an insulated-gate bipolar transistor. AIP Adv. 2021, 11, 025137. [Google Scholar] [CrossRef]

- Hönniger, F. Radiation Damage in Silicon. Defect Analysis and Detector Properties; Deutsches Elektronen-Synchrotron, DESY: Hamburg, Germany, 2008. [Google Scholar]

- Esposito, M.G.; Manuel, J.E.; Privat, A.; Xiao, T.P.; Garland, D.; Bielejec, E.; Vizkelethy, G.; Dickerson, J.; Brunhaver, J.; Talin, A.A.; et al. Investigating Heavy-Ion Effects on 14-nm Process FinFETs: Displacement Damage Versus Total Ionizing Dose. IEEE Trans. Nucl. Sci. 2021, 68, 724–732. [Google Scholar] [CrossRef]

- Kim, J.; Han, J.-W.; Meyyappan, M. The Impact of a Single Displacement Defect on Tunneling Field-Effect Transistors. IEEE Trans. Electron Devices 2020, 67, 4765–4769. [Google Scholar] [CrossRef]

- Seevinck, E.; List, F.; Lohstroh, J. Static-noise margin analysis of MOS SRAM cells. IEEE J. Solid-State Circuits 1987, 22, 748–754. [Google Scholar] [CrossRef]

| Parameters | Description | Value |

|---|---|---|

| Lg | Gate length | 20 nm |

| Leff | Effective gate length | 20 nm |

| Wfin | Fin width | 8 nm |

| Hfin | Fin height | 46 nm |

| CPP | Contact poly pitch | 54 nm |

| EOT | Equivalent oxide thickness | 1.4 nm |

| Nsd | Doping concentration of the source and drain | 1 × 1020 cm−3 |

| Nch | Doping concentration of the channel | 5 × 1016 cm−3 |

| Transistor | RSNM (mV) | ∆RSNM (%) | WSNM (mV) | ∆WSNM (%) |

|---|---|---|---|---|

| Pre-irradiation | 0.11321 | - | 0.30258 | - |

| PG1 | 0.1414 | −24.90% | 0.30048 | 0.69% |

| PG1 + PG2 | 0.14144 | −24.94% | 0.30063 | 0.64% |

| PD1 | 0.07734 | 31.68% | 0.3015 | 0.36% |

| PD1 + PD2 | 0.09108 | 19.55% | 0.31888 | −5.39% |

| PU1 | 0.11326 | −0.04% | 0.30826 | −1.88% |

| PU1 + PU2 | 0.10607 | 6.31% | 0.30589 | −1.09% |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bang, M.; Ha, J.; Lee, G.; Suh, M.; Kim, J. Performance Degradation in Static Random Access Memory of 10 nm Node FinFET Owing to Displacement Defects. Micromachines 2023, 14, 1090. https://doi.org/10.3390/mi14051090

Bang M, Ha J, Lee G, Suh M, Kim J. Performance Degradation in Static Random Access Memory of 10 nm Node FinFET Owing to Displacement Defects. Micromachines. 2023; 14(5):1090. https://doi.org/10.3390/mi14051090

Chicago/Turabian StyleBang, Minji, Jonghyeon Ha, Gyeongyeop Lee, Minki Suh, and Jungsik Kim. 2023. "Performance Degradation in Static Random Access Memory of 10 nm Node FinFET Owing to Displacement Defects" Micromachines 14, no. 5: 1090. https://doi.org/10.3390/mi14051090

APA StyleBang, M., Ha, J., Lee, G., Suh, M., & Kim, J. (2023). Performance Degradation in Static Random Access Memory of 10 nm Node FinFET Owing to Displacement Defects. Micromachines, 14(5), 1090. https://doi.org/10.3390/mi14051090