Novel SiGe/Si Heterojunction Double-Gate Tunneling FETs with a Heterogate Dielectric for High Performance

Abstract

1. Introduction

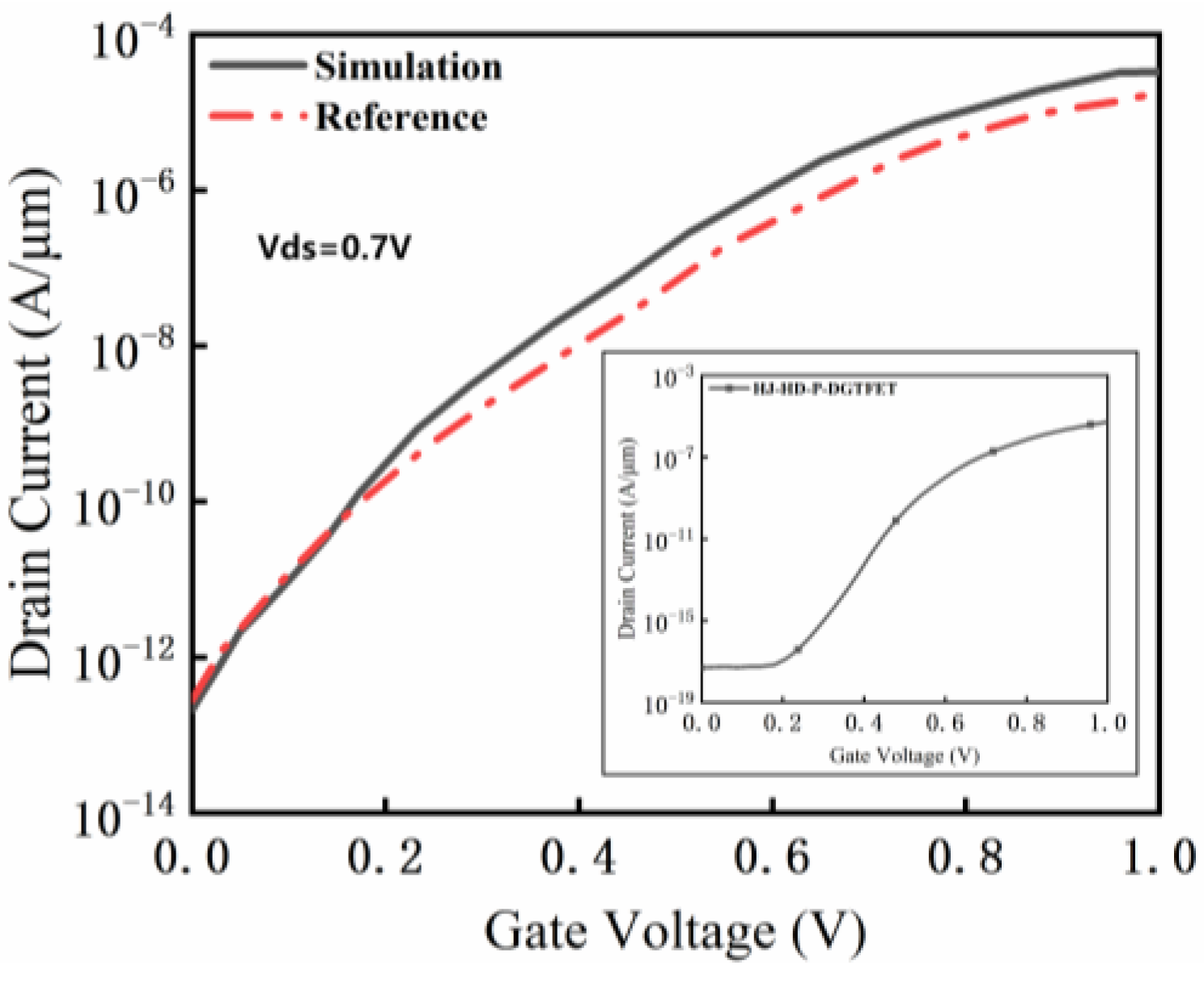

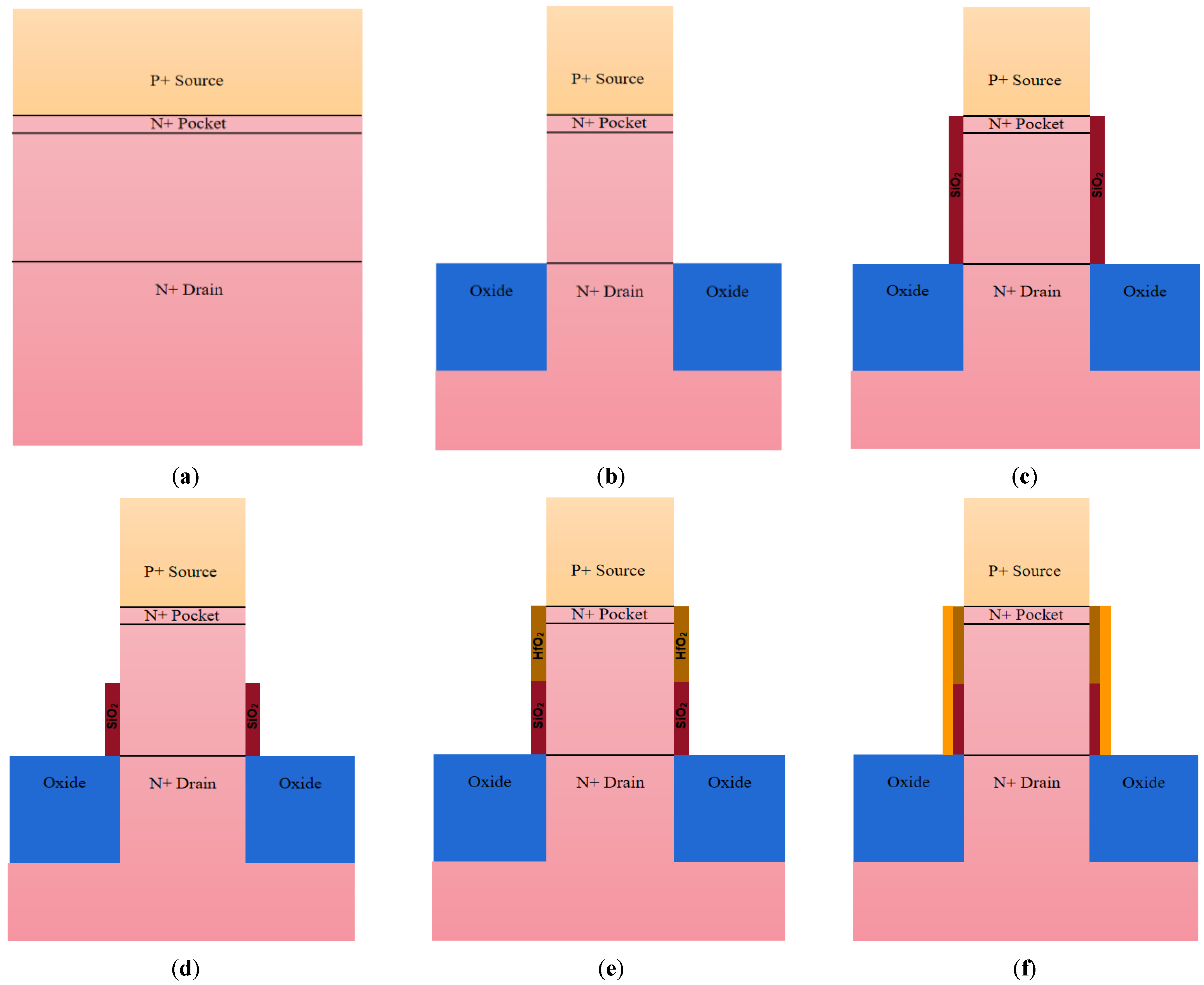

2. Device Architecture, Parameters, and Simulation Methods

3. Results and Discussion

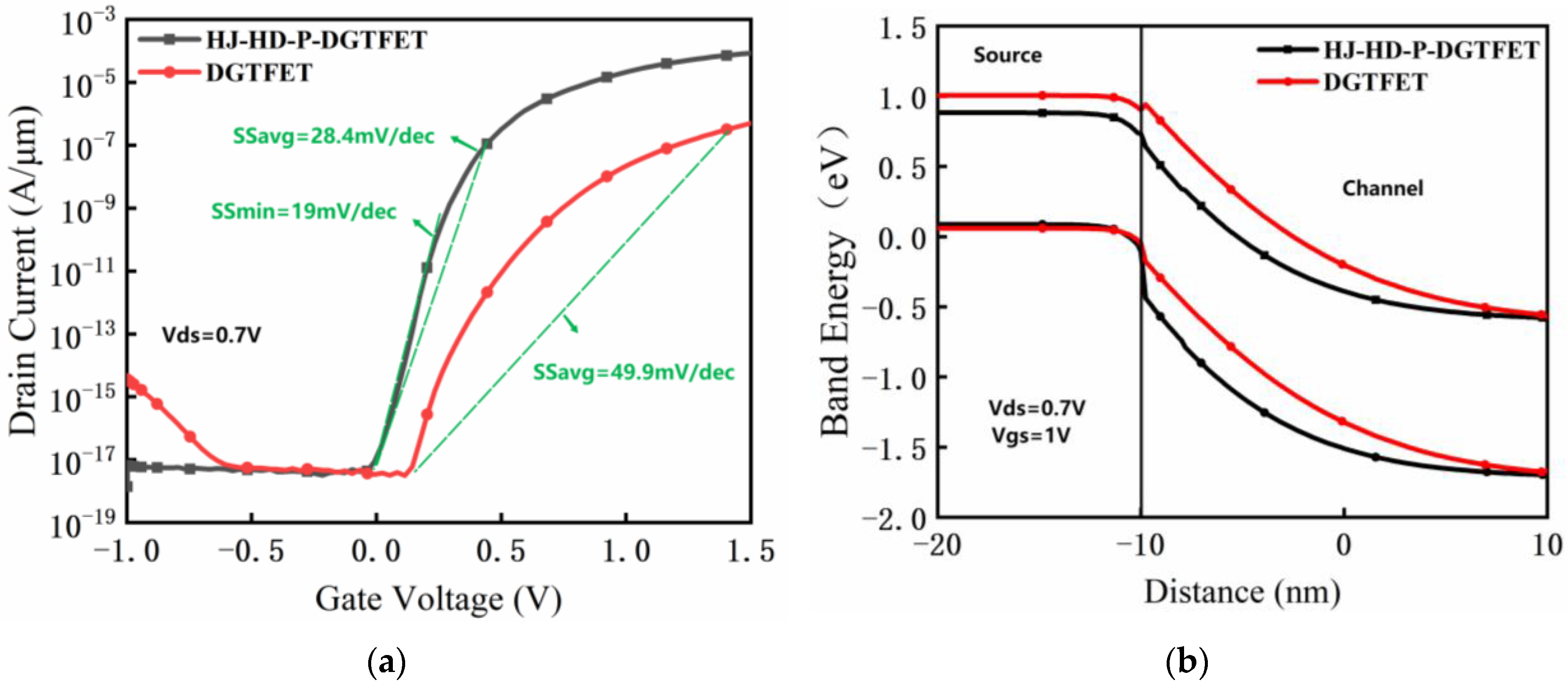

3.1. The Physical Characteristics of Si-DGTFET and HJ-HD-P-DGTFET

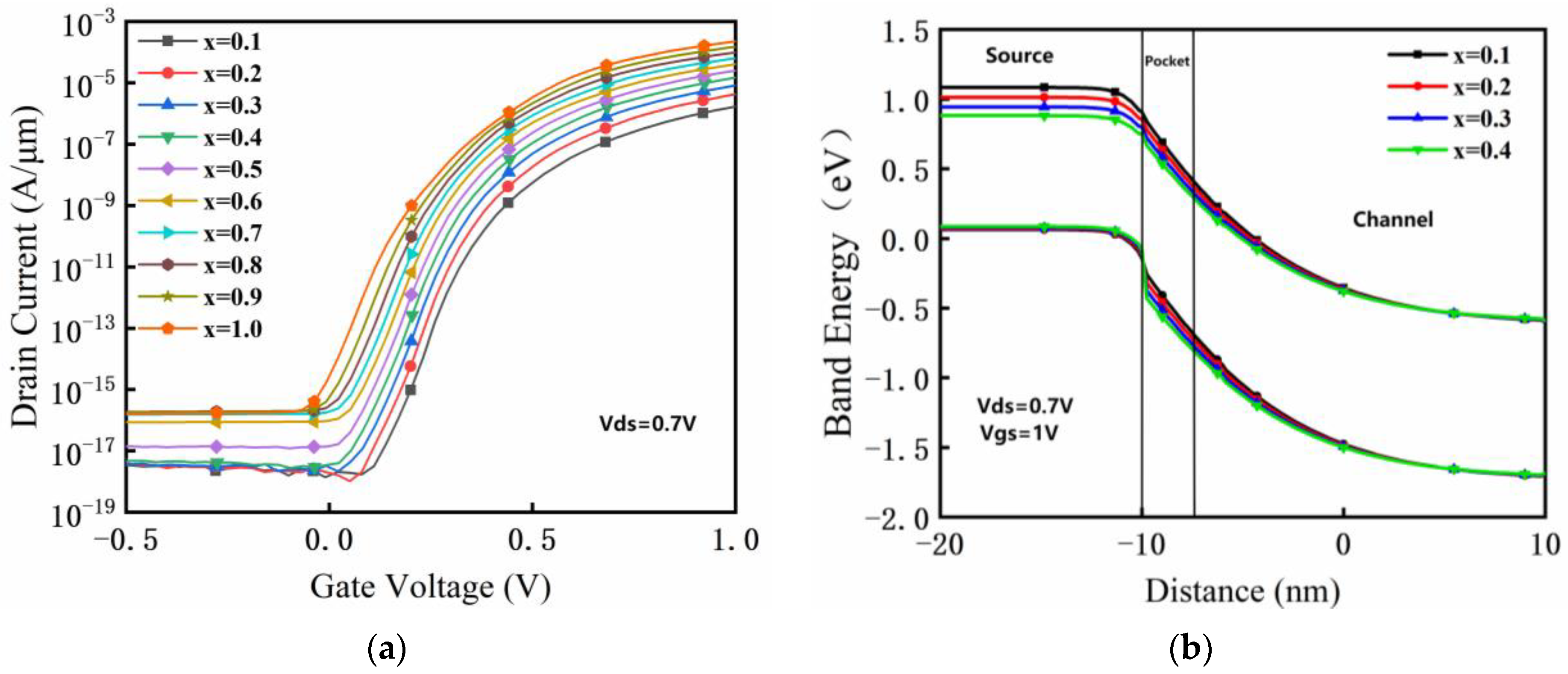

3.2. Si1-xGex/Si Heterojunction

3.3. Gate Heterogeneous Dielectric Structures

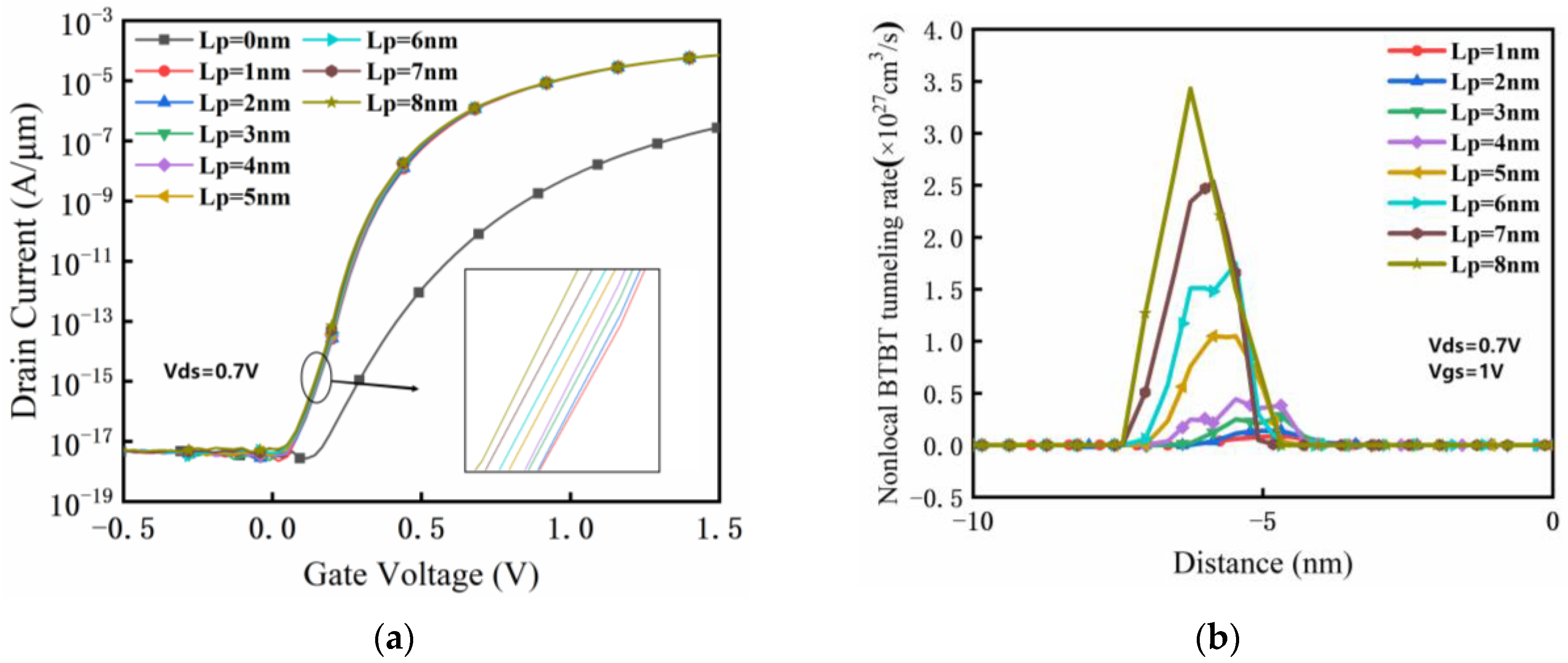

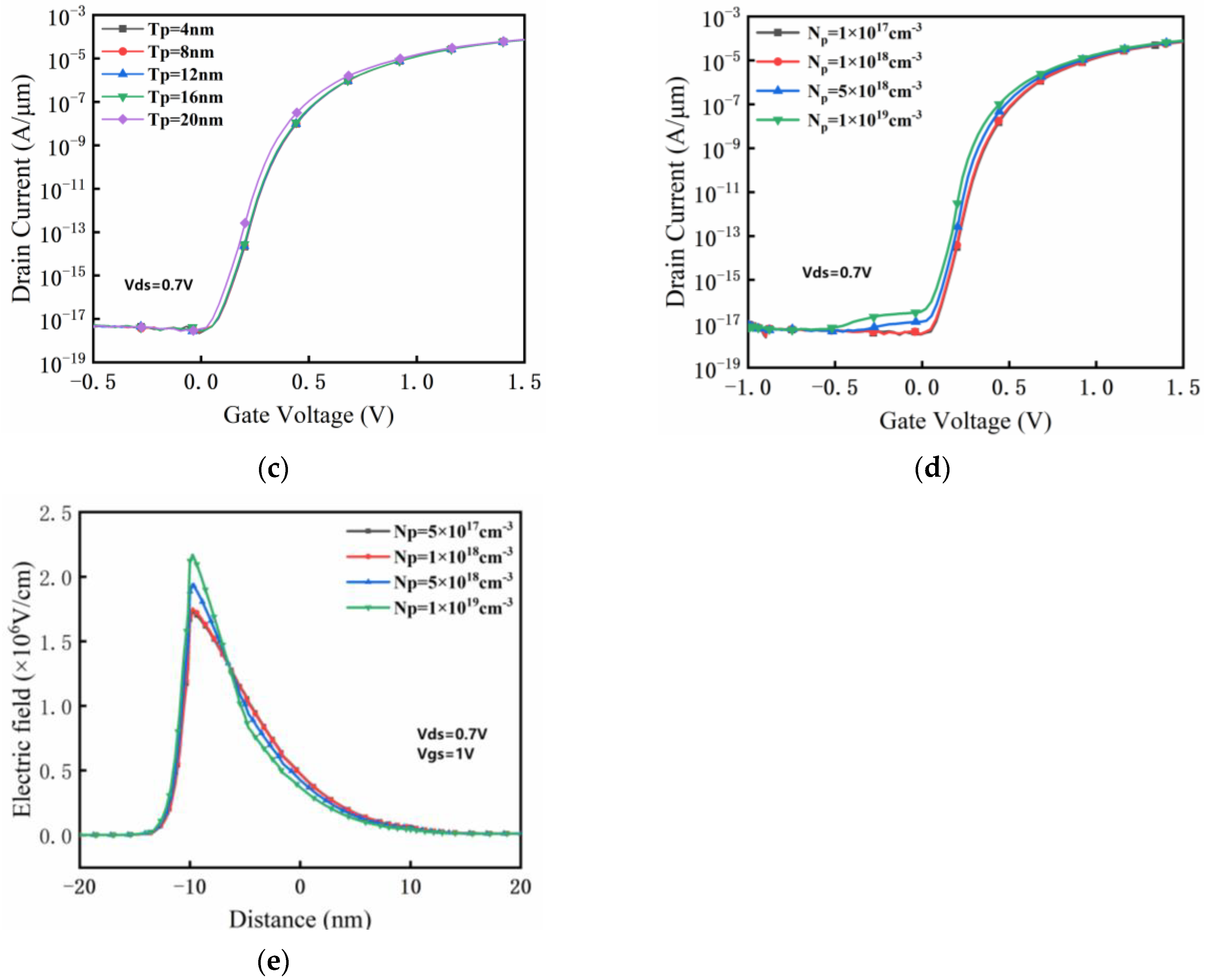

3.4. Auxiliary Tunneling Barrier Layer (Pocket) Optimization Results

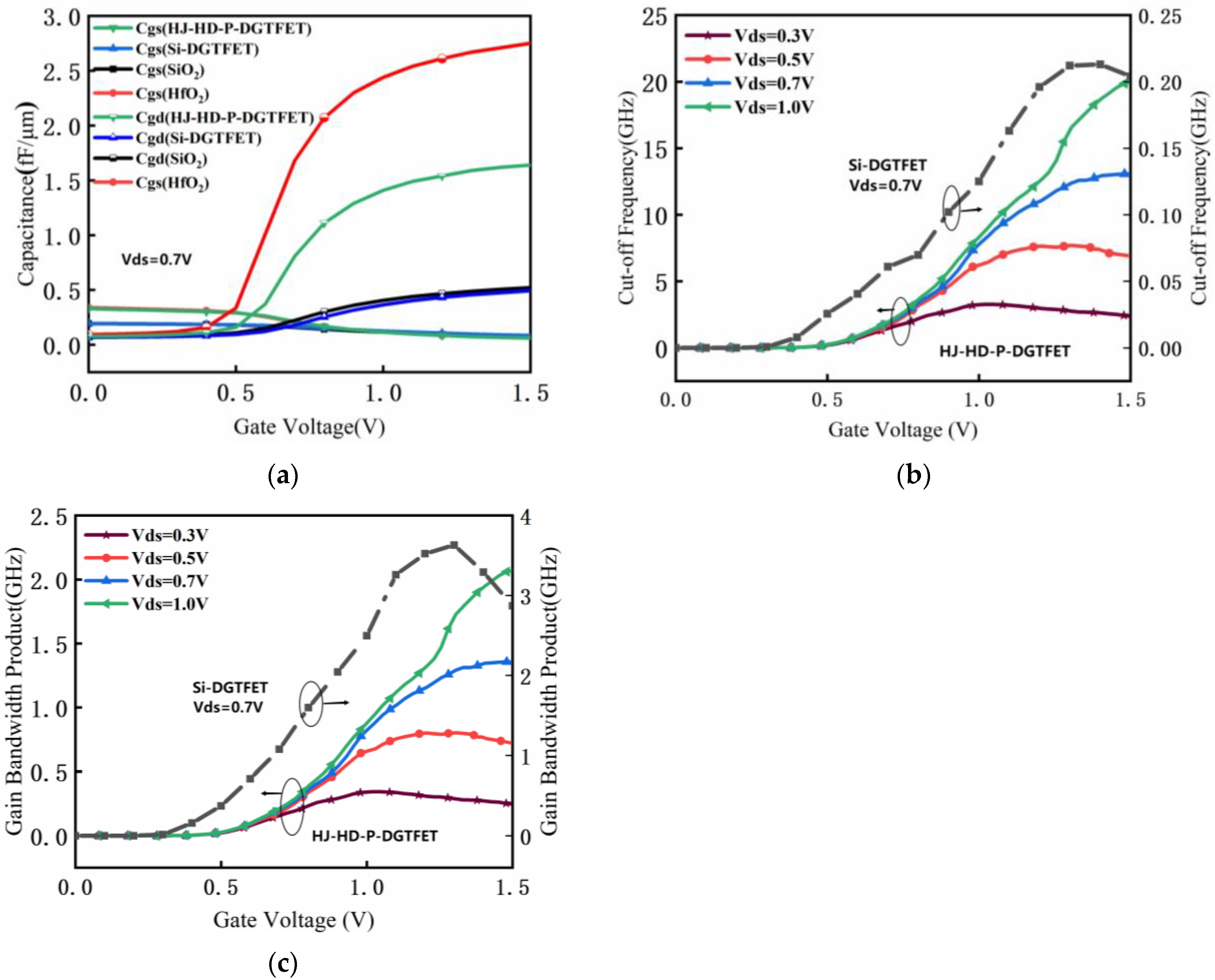

3.5. Comparison of Analog/RF Performance

3.6. Comparison of Different TFETs with HJ-HD-P-DGTFET

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Allam, E.A.; Manku, T.; Ting, M.; Obrecht, M.S. Impact of technology scaling on CMOS RF devices and circuits. In Proceedings of the IEEE Custom Integrated Circuits Conference, Orlando, FL, USA, 21–24 May 2000; pp. 361–364. [Google Scholar]

- Millán, J.; Godignon, P.; Perpiñà, X.; Pérez-Tomás, A.; Rebollo, J. A Survey of Wide Bandgap Power Semiconductor Devices. IEEE Trans. Power Electron. 2013, 29, 2155–2163. [Google Scholar] [CrossRef]

- Nigam, K. Low-K Dielectric Pocket and Workfunction Engineering for DC and Analog/RF Performance Improvement in Dual Material Stack Gate Oxide Double Gate TFET. Silicon 2021, 13, 2347–2356. [Google Scholar]

- Mohapatra, S.K.; Pradhan, K.P.; Sahu, P.K. Effect of channel & gate engineering on Double Gate (DG) MOSFET-A comparative study. In Proceedings of the 2012 International Conference on Emerging Electronics, Mumbai, India, 15–17 December 2012; pp. 1–3. [Google Scholar]

- Song, J.Y.; Choi, W.Y.; Park, J.H.; Lee, J.D.; Park, B.G. Design optimization of gate-all-around (GAA) MOSFETs. IEEE Trans. Nanotechnol. 2006, 5, 186–191. [Google Scholar] [CrossRef]

- Liu, J.S.; Clavel, M.B.; Hudait, M.K. TBAL: Tunnel FET-Based Adiabatic Logic for Energy-Efficient, Ultra-Low Voltage IoT Applications. IEEE J. Electron Devices Soc. 2019, 7, 210–218. [Google Scholar] [CrossRef]

- Choi, W.Y.; Park, B.G.; Lee, J.D.; Liu, T.K. Tunneling Field-Effect Transistors (TFETs) with Subthreshold Swing (SS) Less than 60 mV/dec. IEEE Electron Device Lett. 2007, 28, 743–745. [Google Scholar] [CrossRef]

- Yuan, J.S.; Lin, J.; Alasad, Q.; Taheri, S. Ultra-Low-Power Design and Hardware Security Using Emerging Technologies for Internet of Things. Electronics 2017, 6, 67. [Google Scholar] [CrossRef]

- Chien, N.D.; Shih, C.H. Short channel effects in tunnel field-effect transistors with different configurations of abrupt and graded Si/SiGe heterojunctions. Superlattices Microstruct. 2016, 100, 857–866. [Google Scholar] [CrossRef]

- Martino, M.; Martino, J.A.; Agopian, P.; Vandooren, A.; Rooyackers, R.; Simoen, E.; Claeys, C. Analysis of current mirror circuits designed with line tunnel FET devices at different temperatures. Semicond. Sci. Technol. 2017, 32, 055015. [Google Scholar] [CrossRef]

- Zhang, M.L.; Guo, Y.F.; Zhang, J.; Yao, J.F.; Chen, J. Simulation Study of the Double-Gate Tunnel Field-Effect Transistor with Step Channel Thickness. Nanoscale Res. Lett. 2020, 15, 128. [Google Scholar] [CrossRef]

- Mori, T.; Fukuda, K.; Miyata, N.; Morita, Y.; Migita, S.; Mizubayashi, W.; Masahara, M.; Yasuda, T.; Ota, H. Study of gate leakage current paths in p-channel tunnel field-effect transistor by current separation measurement and device simulation. Jpn. J. Appl. Phys. 2015, 54, 8. [Google Scholar] [CrossRef]

- Dash, S.; Sahoo, G.; Mishra, G.P. Current switching ratio optimization using dual pocket doping engineering. Superlattices Microstruct. 2018, 113, 791–798. [Google Scholar] [CrossRef]

- Ferain, I.; Colinge, C.A.; Colinge, J.P. Multigate transistors as the future of classical metal-oxide-semiconductor field-effect transistors. Nature 2011, 479, 310–316. [Google Scholar] [CrossRef] [PubMed]

- Singh, G.; Amin, S.; Anand, S.; Sarin, R.K. Design of Si0.5Ge0.5 based tunnel field effect transistor and its performance evaluation. Superlattices Microstruct. 2016, 92, 143–156. [Google Scholar] [CrossRef]

- Marjani, S.; Hosseini, S.E. A novel double gate tunnel field effect transistor with 9 mV/dec average subthreshold slope. In Proceedings of the 22nd Iranian Conference on Electrical Engineering (ICEE), Tehran, Iran, 20–22 May 2014; pp. 399–402. [Google Scholar]

- Gopi, C.; Chauhan, S.S. Double-gate Ge, InAs-based tunnel FETs with enhanced ON-current. In Proceedings of the International Conference on Communication and Signal Processing (ICCSP), Melmaruvathur, India, 6–8 April 2016; pp. 639–641. [Google Scholar]

- Duan, X.L.; Zhang, J.C.; Wang, S.L.; Li, Y.; Xu, S.R.; Hao, Y. A High-Performance Gate Engineered InGaN Dopingless Tunnel FET. IEEE Trans. Electron Devices 2018, 65, 1223–1229. [Google Scholar] [CrossRef]

- Bashir, F.; Loan, S.A.; Rafat, M.; Alamoud, A.R.M.; Abbasi, S.A. A high performance gate engineered charge plasma based tunnel field effect transistor. J. Comput. Electron. 2015, 14, 477–485. [Google Scholar] [CrossRef]

- Li, C.; Guo, J.M.; Jiang, H.F.; You, H.L.; Liu, W.F.; Zhuang, Y.Q. A novel gate engineered L-shaped dopingless tunnel field-effect transistor. Appl. Phys. A 2020, 126, 412. [Google Scholar] [CrossRef]

- Vimala, P.; Samuel, T.S.A.; Pandian, M.K. Performance Investigation of Gate Engineered tri-Gate SOI TFETs with Different High-K Dielectric Materials for Low Power Applications. Silicon 2020, 12, 1819–1829. [Google Scholar] [CrossRef]

- Vanlalawmpuia, K.; Bhowmick, B. Optimization of a Hetero-Structure Vertical Tunnel FET for Enhanced Electrical Performance and Effects of Temperature Variation on RF/Linearity Parameters. Silicon 2021, 13, 155–166. [Google Scholar] [CrossRef]

- Choudhury, S.; Niranjan, N.K.; Baishnab, K.L.; Guha, K. Design and simulation of P-TFET for improved I-ON/I-OFF ratio and subthreshold slope using strained Si1-xGex channel heterojunction. Microsyst. Technol. 2020, 26, 1777–1782. [Google Scholar] [CrossRef]

- Ghosh, S.; Venkateswaran, P.; Sarkar, S.K. Analysis of circuit performance of Ge-Si hetero structure TFET based on analytical model. Circuit World 2021, 10. [Google Scholar] [CrossRef]

- Sant, S.; Schenk, A. Band-Offset Engineering for GeSn-SiGeSn Hetero Tunnel FETs and the Role of Strain. IEEE J. Electron Devices Soc. 2015, 3, 164–175. [Google Scholar] [CrossRef]

- Panda, S.; Dash, S. Drain Dielectric Pocket Engineering: Its Impact on the Electrical Performance of a Hetero-Structure Tunnel FET. Silicon 2022, 14, 9305–9317. [Google Scholar] [CrossRef]

- Chang, H.Y.; Adams, B.; Chien, P.Y.; Li, J.P.; Woo, J. Improved Subthreshold and Output Characteristics of Source-Pocket Si Tunnel FET by the Application of Laser Annealing. IEEE Trans. Electron Devices 2013, 60, 92–96. [Google Scholar] [CrossRef]

- Madan, J.; Chaujar, R. Numerical Simulation of N+ Source Pocket PIN-GAA-Tunnel FET: Impact of Interface Trap Charges and Temperature. IEEE Trans. Electron Devices 2017, 64, 1482–1488. [Google Scholar] [CrossRef]

- Beneventi, G.B.; Gnani, E.; Gnudi, A.; Reggiani, S.; Baccarani, G. Optimization of a Pocketed Dual-Metal-Gate TFET by Means of TCAD Simulations Accounting for Quantization-Induced Bandgap Widening. IEEE Trans. Electron Devices 2015, 62, 44–51. [Google Scholar] [CrossRef]

- Kumar, M.J.; Janardhanan, S. Doping-Less Tunnel Field Effect Transistor: Design and Investigation. IEEE Trans. Electron Devices 2013, 60, 3285–3290. [Google Scholar] [CrossRef]

- Vishnoi, R.; Kumar, M.J. Compact Analytical Model of Dual Material Gate Tunneling Field-Effect Transistor Using Interband Tunneling and Channel Transport. IEEE Trans. Electron Devices 2014, 61, 1936–1942. [Google Scholar] [CrossRef]

- Li, W.C.; Woo, C.S. Vertical P-TFET with a P-Type SiGe Pocket. IEEE Trans. Electron Devices 2020, 67, 1480–1484. [Google Scholar] [CrossRef]

- Kumar, N.; Raman, A. Design and Investigation of Charge-Plasma-Based Work Function Engineered Dual-Metal-Heterogeneous Gate Si-Si0.55Ge0.45 GAA-Cylindrical NWTFET for Ambipolar Analysis. IEEE Trans. Electron Devices 2019, 66, 1468–1474. [Google Scholar] [CrossRef]

- Blaeser, S.; Glass, S.; Schulte-Braucks, C.; Narimani, K.; Driesch, N.V.D.; Wirths, S.; Tiedemanm, A.T.; Trellenkamp, S.; Buca, D.; Zhao, Q.T.; et al. Novel SiGe/Si line tunneling TFET with high Ion at low VDD and constant SS. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 608–611. [Google Scholar]

- Boucart, K.; Ionescu, A.M. Double-Gate Tunnel FET with High-k Gate Dielectric. IEEE Trans. Electron Devices 2007, 54, 1725–1733. [Google Scholar] [CrossRef]

- Singh, K.S.; Kumar, S.; Nigam, K. Design and Investigation of Dielectrically Modulated Dual-Material Gate-Oxide-Stack Double-Gate TFET for Label-Free Detection of Biomolecules. IEEE Trans. Electron Devices 2021, 68, 5784–5791. [Google Scholar] [CrossRef]

- Vimala, P.; Kumar, N. Comparative Analysis of Various Parameters of Tri-Gate MOSFET with High-K Spacer. J. Nano Res. 2019, 56, 119–130. [Google Scholar] [CrossRef]

- Narang, R.; Saxena, M.; Gupta, R.S.; Gupta, M. Device and Circuit Level Performance Comparison of Tunnel FET Architectures and Impact of Heterogeneous Gate Dielectric. J. Semicond. Technol. Sci. 2013, 13, 224–236. [Google Scholar] [CrossRef]

- Gandhi, Z.; Chen, N.; Singh, K. Vertical Si-Nanowire n-Type Tunneling FETs with Low Subthreshold Swing (≤50 mV/decade) at Room Temperature. IEEE Electron Device Lett. 2021, 32, 437–439. [Google Scholar] [CrossRef]

- Chang, L.; Choi, Y.K.; Ha, D.; Ranade, P. Extremely scaled silicon nano-CMOS devices. Proc. IEEE 2003, 91, 1860–1873. [Google Scholar] [CrossRef]

- Wu, Y.; Hasegawa, H.; Kakushima, K.; Ohmori, K.; Watanabe, T.; Nishiyama, A.; Sugii, N.; Wakabayashi, H.; Tsutsui, K.; Kataoka, Y.; et al. A novel hetero-junction Tunnel-FET using Semiconducting silicide–Silicon contact and its scalability. Microelectron. Reliab. 2014, 54, 899–904. [Google Scholar] [CrossRef]

- Goyal, P.; Srivastava, G.; Madan, J.; Pandey, R.; Gupta, R.S. Design and Investigation of Mg2Si Source Charge Plasma Based DGTFET for Biomolecule Detection. In Proceedings of the 2022 IEEE International Conference of Electron Devices Society Kolkata Chapter (EDKCON), Kolkata, India, 26–27 November 2022; pp. 474–478. [Google Scholar]

- Goyal, P.; Srivastava, G.; Madan, J.; Pandey, R.; Gupta, R.S. Source Material-Engineered Charge Plasma based Double Gate TFET for Analog/RF Applications. In Proceedings of the 2021 International Conference on Industrial Electronics Research and Applications (ICIERA), New Delhi, India, 22–24 December 2021; pp. 1–4. [Google Scholar]

- Babu, K.M.C.; Goel, E. Analysis of ON Current and Ambipolar Current for Source Pocket Gate-Drain Underlap Double Gate Tunnel Field Effect Transistor. In Proceedings of the 2022 IEEE International Symposium on Smart Electronic Systems (iSES), Warangal, India, 19–21 December 2022; pp. 651–653. [Google Scholar]

- Chen, S.; Wang, S.; Liu, H. A Novel Dopingless Fin-Shaped SiGe Channel TFET with Improved Performance. Nanoscale Res. Lett. 2020, 15, 202. [Google Scholar] [CrossRef]

- Kumar, N.; Amin, S.I.; Anand, S. Design and performance optimization of novel Core–Shell Dopingless GAA-nanotube TFET with Si0.5Ge0.5-based source. IEEE Trans. Electron Devices 2020, 67, 789–795. [Google Scholar]

- Bagga, N.; Kumar, A.; Dasgupta, S. Demonstration of a novel two source region tunnel FET. IEEE Trans. Electron Devices 2017, 64, 5256–5262. [Google Scholar] [CrossRef]

- Sharma, S.; Chaujar, R. High Switching Performance of Novel Heterogeneous Gate Dielectric—Hetero-Material Based Junctionless-TFET. In Microelectronics, Circuits and Systems: Select Proceedings of 7th International Conference on Micro2020; Springer: Singapore, 2021; pp. 3–12. [Google Scholar]

| Parameters | HJ-HD-P-DGTFET | Si-DGTFET |

|---|---|---|

| Source doping (p-type) | 1 × 1020 cm−3 | 1 × 1020 cm−3 |

| Drain doping (n-type) | 1 × 1018 cm−3 | 1 × 1018 cm−3 |

| Channel doping (p-type) | 1 × 1016 cm−3 | 1 × 1016 cm−3 |

| Pocket doping (n-type) | 1 × 1018 cm−3 | – |

| Gate oxide thickness (To) | 2 nm | 2 nm |

| Pocket length (Lp) | 2 nm | – |

| Gate dielectric constant of SiO2 (ε) | 3.9 | 3.9 |

| Gate dielectric constant of HfO2 (ε) | 25 | – |

| Gate work function (Φm) | 4.3 eV | 4.3 eV |

| Device | Ion (A/μm) | Ioff (A/μm) | Ion/Ioff Ratio |

|---|---|---|---|

| CP-DGTFET [41] | 5.8 × 10−7 | 10−15 | 108 |

| SP-GDU-DGTFET [42] | 10−7 | 10−17 | 1010 |

| DF-TFET [43] | 3.8 × 10−6 | 2.7 × 10−17 | 1011 |

| DS-TFET [44] | 1.0 × 10−8 | 1.9 × 10−16 | 107 |

| Mg2Si source CP-DGTFET [45] | 4.6 × 10−3 | 10−16 | 1013 |

| Ge CP-DGTFET [32] | 10−6 | 10−18 | 1012 |

| Si0.8Ge0.2 pocket TFET [34] | 10−6 | 10−13 | 107 |

| SiGe/Si TFET [46] | 6.7 × 10−6 | 2.0 × 10−10 | 104 |

| CS-DL-NT-TFET [47] | 1.7 × 10−5 | 2.0 × 10−17 | 1011 |

| HD-HJLTFET [48] | 4.5 × 10−5 | 1.5 × 10−16 | 1011 |

| This work | 7.8 × 10−5 | 8.2 × 10−18 | 1012 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, Q.; Sun, R.; Miao, R.; Liu, H.; Yang, L.; Qi, Z.; He, W.; Li, J. Novel SiGe/Si Heterojunction Double-Gate Tunneling FETs with a Heterogate Dielectric for High Performance. Micromachines 2023, 14, 784. https://doi.org/10.3390/mi14040784

Chen Q, Sun R, Miao R, Liu H, Yang L, Qi Z, He W, Li J. Novel SiGe/Si Heterojunction Double-Gate Tunneling FETs with a Heterogate Dielectric for High Performance. Micromachines. 2023; 14(4):784. https://doi.org/10.3390/mi14040784

Chicago/Turabian StyleChen, Qing, Rong Sun, Ruixia Miao, Hanxiao Liu, Lulu Yang, Zengwei Qi, Wei He, and Jianwei Li. 2023. "Novel SiGe/Si Heterojunction Double-Gate Tunneling FETs with a Heterogate Dielectric for High Performance" Micromachines 14, no. 4: 784. https://doi.org/10.3390/mi14040784

APA StyleChen, Q., Sun, R., Miao, R., Liu, H., Yang, L., Qi, Z., He, W., & Li, J. (2023). Novel SiGe/Si Heterojunction Double-Gate Tunneling FETs with a Heterogate Dielectric for High Performance. Micromachines, 14(4), 784. https://doi.org/10.3390/mi14040784