Effects of Poly-Si Grain Boundary on Retention Characteristics under Cross-Temperature Conditions in 3-D NAND Flash Memory

Abstract

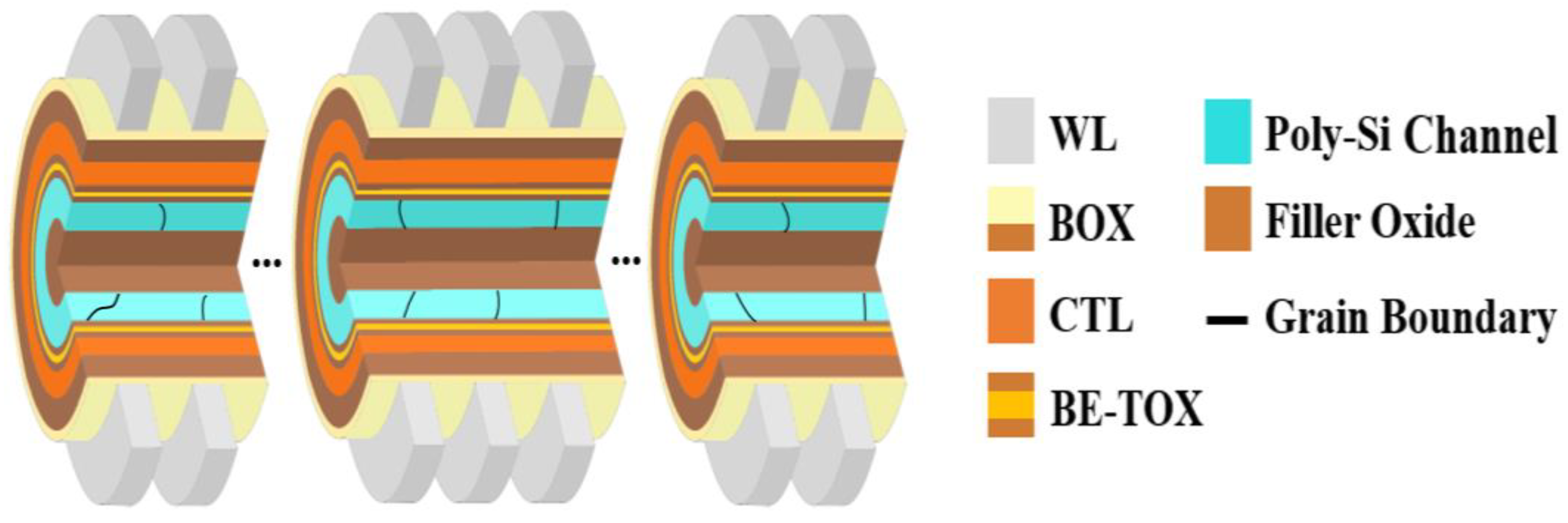

:1. Introduction

2. Results and Discussion

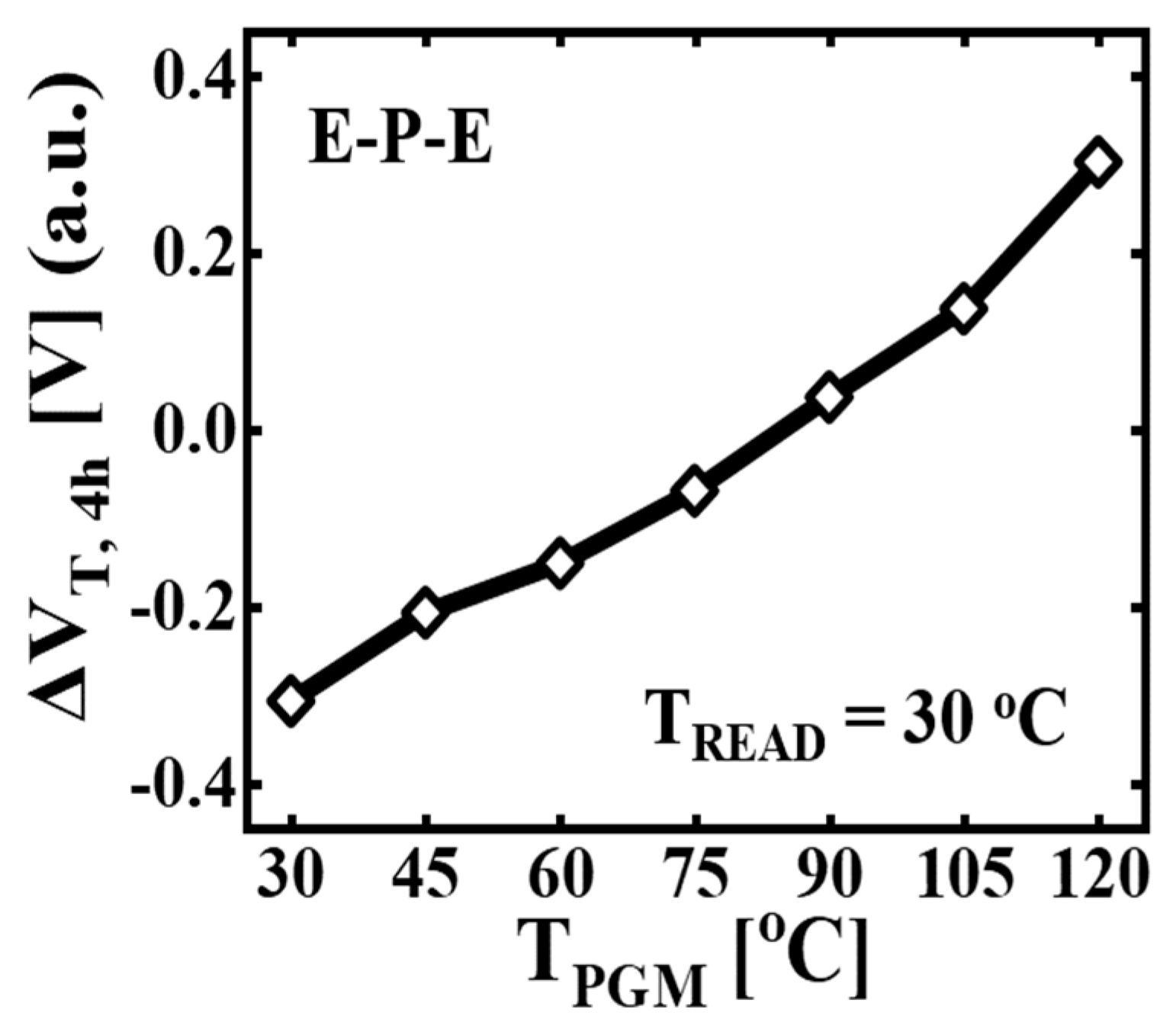

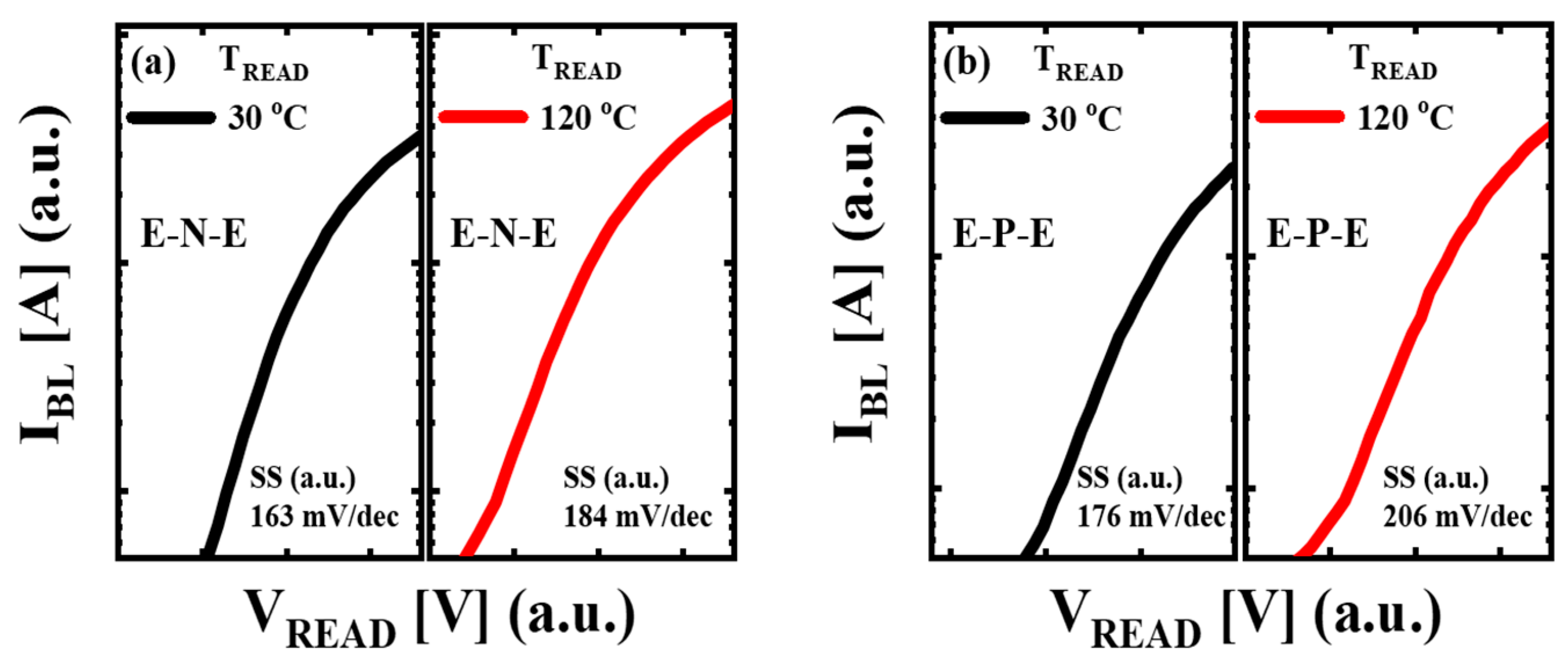

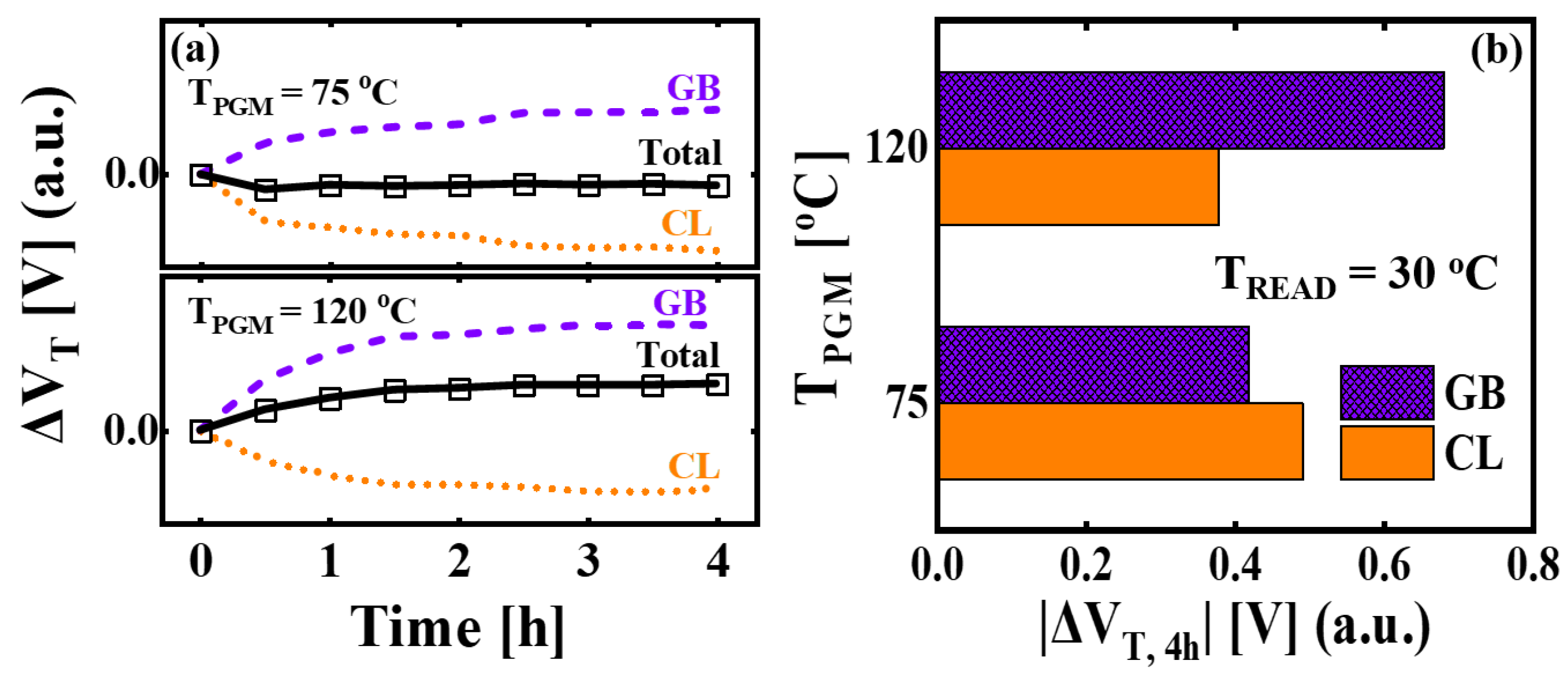

2.1. Cross-Temperature Effects on Retention Characteristics

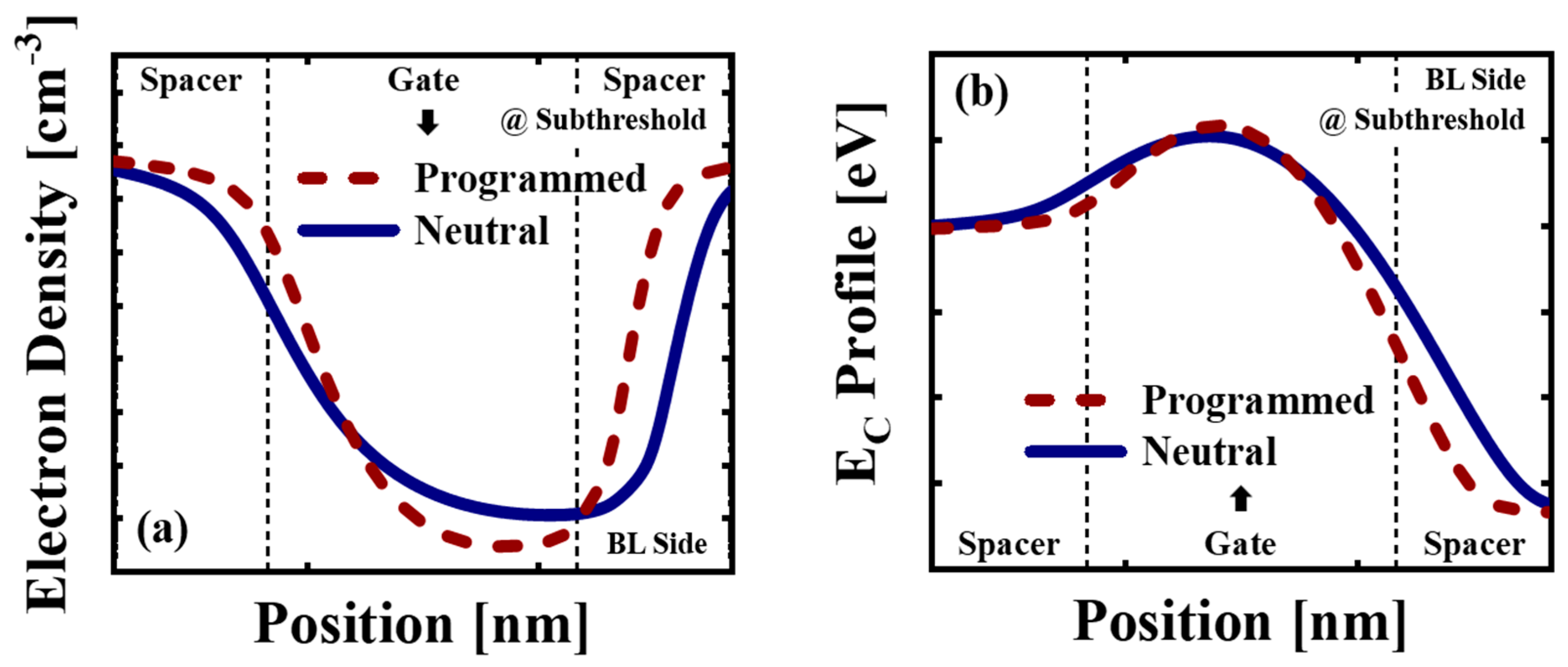

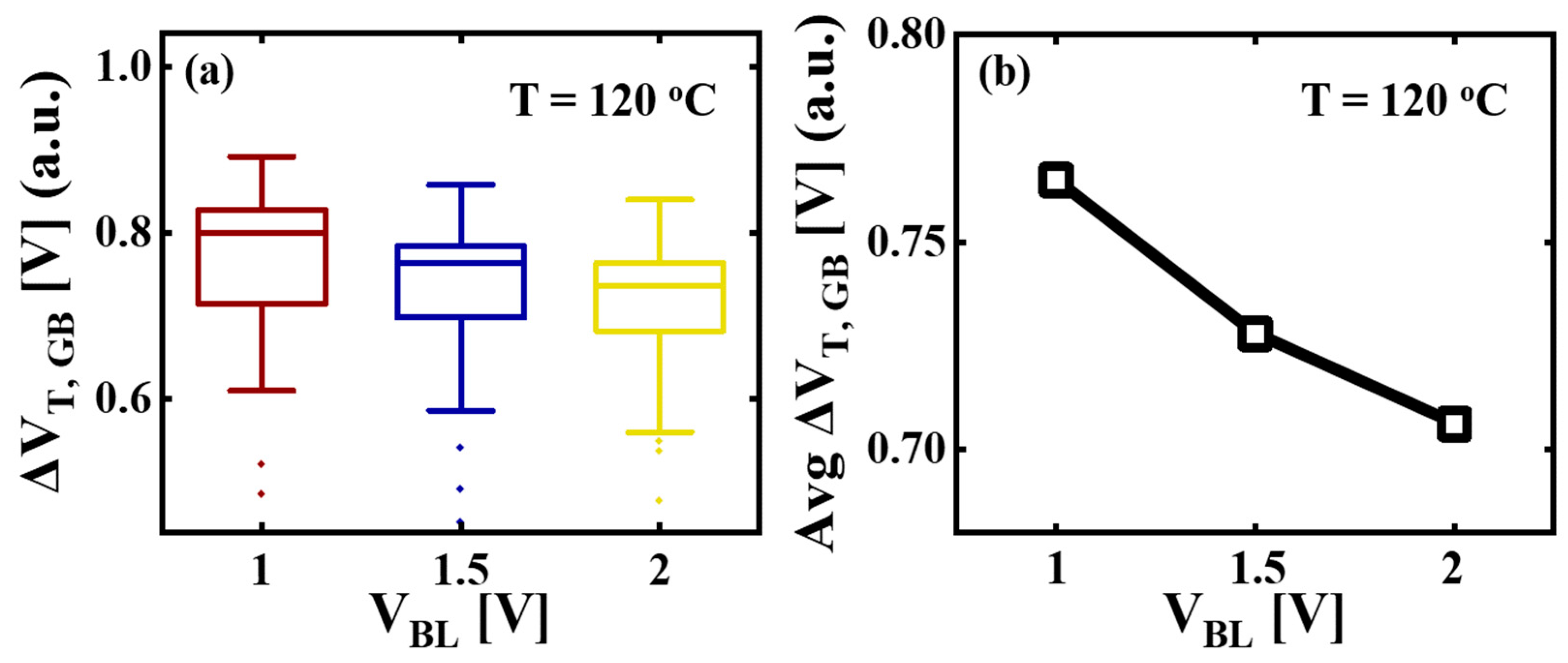

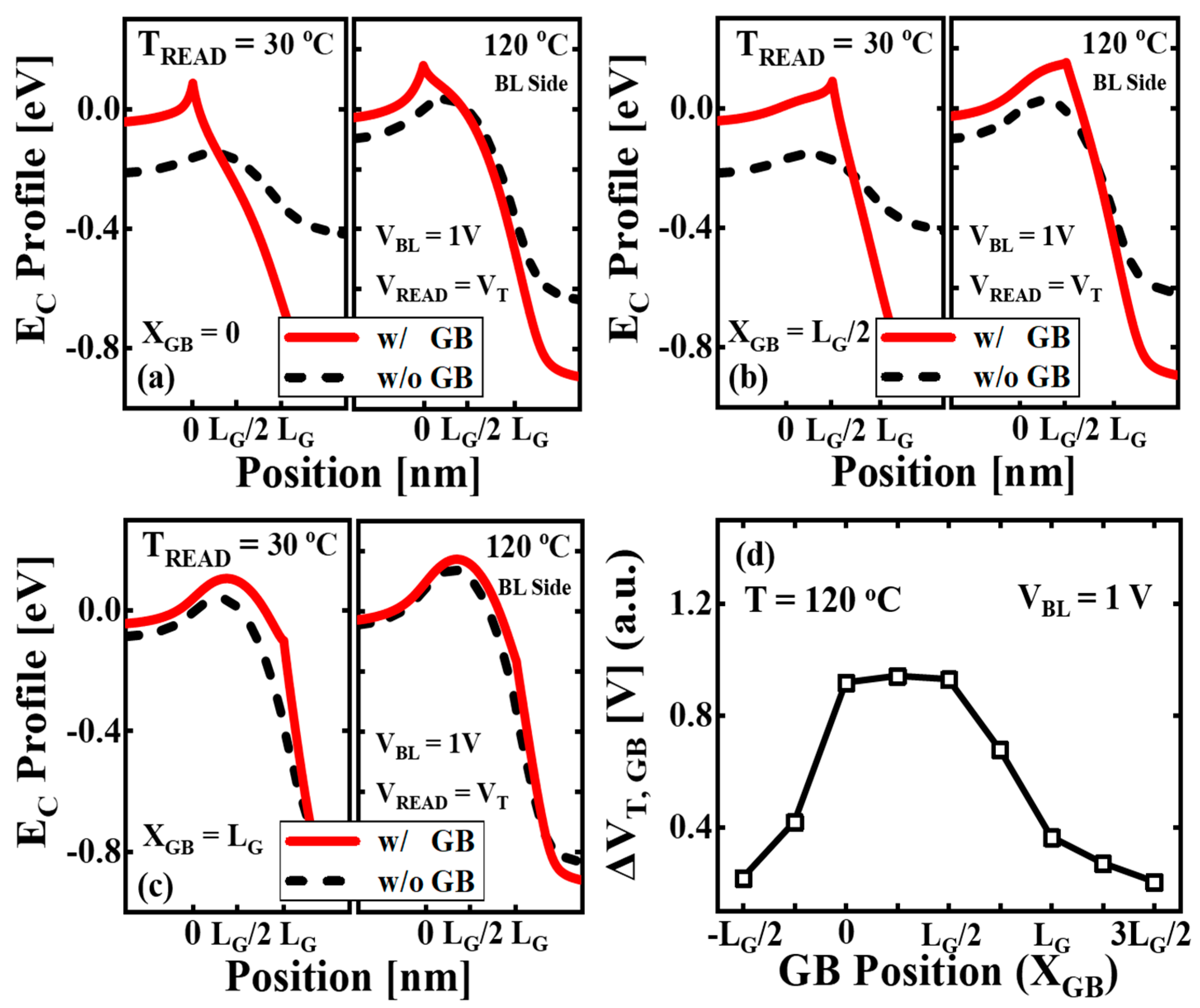

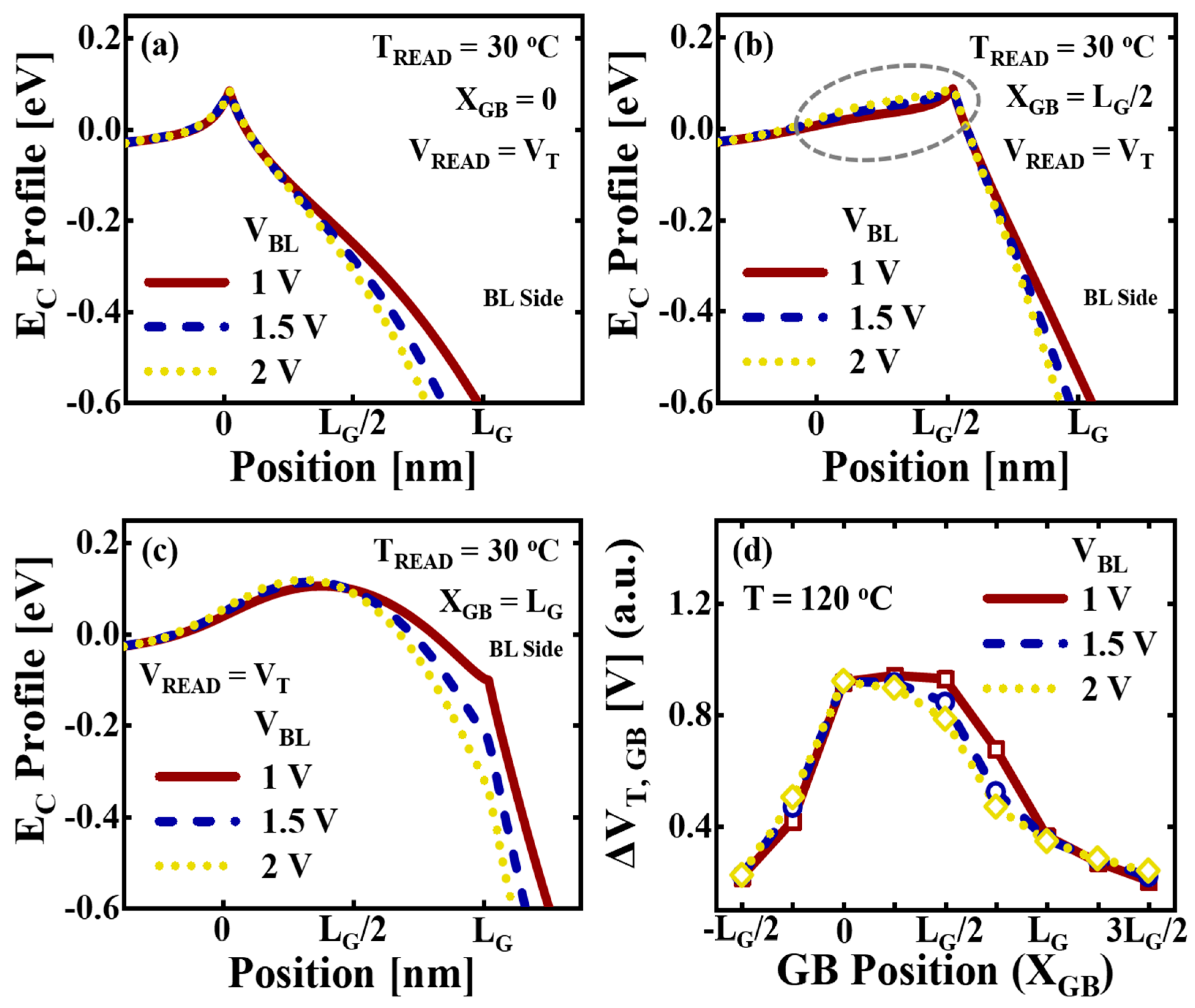

2.2. Threshold Voltage Shift by Poly-Si GB

3. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Goda, A. 3-D NAND Technology Achievements and Future Scaling Perspectives. IEEE Trans. Electron Devices 2020, 67, 1373–1381. [Google Scholar] [CrossRef]

- Parat, K.; Goda, A. Scaling Trends in NAND Flash. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 2.1.1–2.1.4. [Google Scholar]

- Lee, S.; Kim, C.; Kim, M.; Joe, S.-m.; Jang, J.; Kim, S.; Lee, K.; Kim, J.; Park, J.; Lee, H.-J.; et al. A 1Tb 4b/cell 64-stacked-WL 3D NAND Flash Memory with 12MB/s Program Throughput. In Proceedings of the 2018 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 11–15 February 2018; pp. 340–342. [Google Scholar]

- Sanuki, T.; Aiba, Y.; Tanaka, H.; Maeda, T.; Sawa, K.; Kikushima, F.; Miura, M. Cryogenic Operation of 3-D Flash Memory for Storage Performance Improvement and Bit Cost Scaling. IEEE J. Explor. Solid-State Comput. Devices Circuits 2021, 7, 159–167. [Google Scholar] [CrossRef]

- Aiba, Y.; Tanaka, H.; Maeda, T.; Sawa, K.; Kikushima, F.; Miura, M.; Fujisawa, T.; Matsuo, M.; Horii, H.; Mukaida, H.; et al. Bringing in Cryogenics to Storage: Characteristics and Performance Improvement of 3D Flash Memory. In Proceedings of the 2021 IEEE International Memory Workshop (IMW), Dresden, Germany, 16–19 May 2021; pp. 1–4. [Google Scholar]

- Kang, H.-J.; Choi, N.; Joe, S.-M.; Seo, J.-H.; Choi, E.; Park, S.-K.; Park, B.-G.; Lee, J.-H. Comprehensive Analysis of Retention Characteristics in 3-D NAND Flash Memory Cells with Tube-type Poly-Si Channel Structure. In Proceedings of the 2015 Symposium on VLSI Technology (VLSI Technology), Kyoto, Japan, 16–18 June 2015; pp. T182–T183. [Google Scholar]

- Resnati, D.; Mannara, A.; Nicosia, G.; Paolucci, G.M.; Tessariol, P.; Lacaita, A.L.; Spinelli, A.S.; Compagnoni, C.M. Temperature Activation of the String Current and its Variability in 3-D NAND Flash Arrays. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 4.7.1–4.7.4. [Google Scholar]

- Resnati, D.; Goda, A.; Nicosia, G.; Miccoli, C.; Spinelli, A.S.; Compagnoni, C.M. Temperature Effects in NAND Flash Memories: A Comparison between 2-D and 3-D Arrays. IEEE Electron Device Lett. 2017, 38, 461–464. [Google Scholar] [CrossRef]

- Kim, S.; Lee, K.; Woo, C.; Hwang, Y.; Shin, H. Analysis of Failure Mechanisms during the Long-term Retention Operation in 3-D NAND Flash Memories. IEEE Trans. Electron Devices 2020, 67, 5472–5478. [Google Scholar] [CrossRef]

- Park, J.; Yoon, G.; Go, D.; Kim, D.; An, U.; Kim, J.; Kim, J.; Lee, J.-S. Decomposition of Vertical and Lateral Charge Loss in Long-term Retention of 3-D NAND Flash Memory. In Proceedings of the 2023 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 26–30 March 2023; pp. 1–4. [Google Scholar]

- Kim, H.; Ahn, S.-J.; Shin, Y.G.; Lee, K.; Jung, E. Evolution of NAND Flash Memory: From 2D to 3D as a Storage Market Leader. In Proceedings of the 2017 IEEE International Memory Workshop (IMW), Monterey, CA, USA, 14–17 May 2017; pp. 1–4. [Google Scholar]

- Congedo, G.; Arreghini, A.; Liu, L.; Capogreco, E.; Lisoni, J.G.; Huet, K.; Toque-Tresonne, I.; Van Aerde, S.; Toledano-Luque, M.; Tan, C.-L.; et al. Analysis of Performance/Variability Trade-off in Macaroni-type 3-D NAND Memory. In Proceedings of the 2014 IEEE International Memory Workshop (IMW), Taipei, Taiwan, 18–21 May 2014; pp. 1–4. [Google Scholar]

- Lin, W.-L.; Tsai, W.-J.; Cheng, C.C.; Ku, S.H.; Liu, L.; Hwang, S.W.; Lu, T.-C.; Chen, K.-C.; Tseng, T.-Y.; Lu, C.-Y. Grain Boundary Trap-induced Current Transient in a 3-D NAND Flash Cell String. IEEE Trans. Electron Devices 2019, 66, 1734–1740. [Google Scholar] [CrossRef]

- Seto, J.Y. The Electrical Properties of Polycrystalline Silicon Films. J. Appl. Phys. 1975, 46, 5247–5254. [Google Scholar] [CrossRef]

- Baccarani, G.; Ricco, B.; Spadini, G. Transport Properties of Polycrystalline Silicon Films. J. Appl. Phys. 1978, 49, 5565–5570. [Google Scholar] [CrossRef]

- Walker, P.M.; Mizuta, H.; Uno, S.; Furuta, Y.; Hasko, D.G. Improved Off-current and Subthreshold Slope in Aggressively Scaled Poly-Si TFTs with a Single Grain Boundary in the Channel. IEEE Trans. Electron Devices 2004, 51, 212–219. [Google Scholar] [CrossRef]

- Kim, J.; Shin, H. Modeling of Grain Boundary Barrier Height for Undoped Polycrystalline Silicon Channel in Macaroni MOSFETs. IEEE Trans. Electron Devices 2022, 69, 2590–2596. [Google Scholar] [CrossRef]

- Resnati, D.; Mannara, A.; Nicosia, G.; Paolucci, G.M.; Tessariol, P.; Spinelli, A.S.; Lacaita, A.L.; Compagnoni, C.M. Characterization and Modeling of Temperature Effects in 3-D NAND Flash Arrays–Part I: Polysilicon-induced Variability. IEEE Trans. Electron. Devices 2018, 65, 3199–3206. [Google Scholar] [CrossRef]

- Tsuchiya, T.; Miura, T.; Yamai, T.; Kawachi, G.; Matsumura, M. Influences of Grain Boundaries on Temperature Dependence of Device Characteristics and on Hot Carrier Effects in Low-temperature Polycrystalline Silicon Thin Film Transistors containing Large Grains. Jpn. J. Appl. Phys. 2007, 46, 1312–1317. [Google Scholar] [CrossRef]

- Choi, S.; Park, K.; Passerini, M.; Park, H.; Kim, D.; Kim, C.; Park, K.; Kim, J. A Cell Current Compensation Scheme for 3D NAND FLASH Memory. In Proceedings of the 2015 IEEE Asian Solid-State Circuits Conference (A-SSCC), Xiamen, China, 9–11 November 2015; pp. 1–4. [Google Scholar]

- Tanzawa, T.; Tanaka, T.; Tamada, S.; Kishimoto, J.; Yamada, S.; Kawai, K.; Ichikawa, T.; Chiang, P.; Roohparvar, F. A Temperature Compensation Word-line Voltage Generator for Multi-level Cell NAND Flash Memories. In Proceedings of the 2010 European Conference on Solid-State Circuits (ESSCIRC), Seville, Spain, 14–16 September 2010; pp. 106–109. [Google Scholar]

- Zambelli, C.; Crippa, L.; Micheloni, R.; Olivo, P. Cross-temperature Effects of Program and Read Operations in 2D and 3D NAND Flash Memories. In Proceedings of the 2018 International Integrated Reliability Workshop (IIRW), South Lake Tahoe, CA, USA, 7–11 October 2018; pp. 1–4. [Google Scholar]

- Zambelli, C.; Micheloni, R.; Olivo, P. Reliability Challenges in 3D NAND Flash Memories. In Proceedings of the 2019 IEEE International Memory Workshop (IMW), Monterey, CA, USA, 12–15 May 2019; pp. 1–4. [Google Scholar]

- Zhao, C.; Jin, L.; Li, D.; Xu, F.; Zou, X.; Zhang, Y.; Song, Y.; Wei, H.; Chen, Y.; Li, C.; et al. Investigation of Threshold Voltage Distribution Temperature Dependence in 3D NAND Flash. IEEE Electron Device Lett. 2018, 40, 204–207. [Google Scholar] [CrossRef]

- An, U.; Yoon, G.; Go, D.; Park, J.; Kim, D.; Kim, J.; Lee, J.-S. Temperature-induced Instability of Retention Characteristics in 3-D NAND Flash Memory. In Proceedings of the 2023 IEEE Electron Devices Technology & Manufacturing Conference (EDTM), Seoul, Republic of Korea, 7–10 March 2023; pp. 1–3. [Google Scholar]

- Wu, D.; You, H.; Wang, X.; Zhong, S.; Sun, Q. Experimental Investigation of Threshold Voltage Temperature Effect during Cross-temperature Write-read Operations in 3-D NAND Flash. IEEE J. Electron Devices Soc. 2020, 9, 22–26. [Google Scholar] [CrossRef]

- Yoo, H.-N.; Choi, B.; Back, J.-W.; Kang, H.-J.; Kwon, E.; Chung, S.; Bae, J.-H.; Park, B.-G.; Lee, J.-H. Effect of Lateral Charge Diffusion on Retention Characteristics of 3D NAND Flash Cells. IEEE Electron Device Lett. 2021, 42, 1148–1151. [Google Scholar] [CrossRef]

- Sentaurus Device Manual; Synopsys: Mountain View, CA, USA, 2021.

- Park, J.; Yoon, G.; Go, D.; Kim, J.; Lee, J.-S. Extraction of Nitride Trap Profile in 3-D NAND Flash Memory Using Intercell Program Pattern. IEEE Access 2021, 9, 118794–118800. [Google Scholar] [CrossRef]

- Jeong, M.-K.; Joe, S.-M.; Jo, B.-S.; Kang, H.-J.; Bae, J.-H.; Han, K.-R.; Choi, E.; Cho, G.; Park, S.-K.; Park, B.-G.; et al. Characterization of Traps in 3-D Stacked NAND Flash Memory Devices with Tube-type Poly-Si Channel Structure. In Proceedings of the 2012 International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 10–13 December 2012; pp. 9.3.1–9.3.4. [Google Scholar]

- Woo, C.; Lee, M.; Kim, S.; Park, J.; Choi, G.-B.; Seo, M.-s.; Noh, K.H.; Kang, M.; Shin, H. Modeling of Charge Loss Mechanisms during the Short Term Retention Operation in 3-D NAND Flash Memories. In Proceedings of the 2019 Symposium on VLSI Technology (VLSI Technology), Kyoto, Japan, 9–14 June 2019; pp. T214–T215. [Google Scholar]

- Woo, C.; Kim, S.; Shin, H. Cell Pattern Dependency of Charge Failure Mechanisms during Short-term Retention in 3-D NAND Flash Memories. IEEE Electron Device Lett. 2020, 41, 1645–1648. [Google Scholar] [CrossRef]

- Yang, C.-W.; Su, P. Simulation and Investigation of Random Grain-Boundary-Induced Variabilities for Stackable NAND Flash Using 3-D Voronoi Grain Patterns. IEEE Trans. Electron Devices 2014, 61, 1211–1214. [Google Scholar] [CrossRef]

- Nam, K.; Park, C.; Yoon, J.-S.; Yang, G.; Park, M.S.; Baek, R.-H. Channel Thickness and Grain Size Engineering for Improvement of Variability and Performance in 3-D NAND Flash Memory. IEEE Trans. Electron Devices 2022, 69, 3681–3687. [Google Scholar] [CrossRef]

- Oh, H.; Kim, J.; Baek, R.-H.; Lee, J.-S. Threshold Voltage Variation Depending on Single Grain Boundary and Stored Charges in an adjacent cell for vertical silicon-oxide-nitride-oxide-silicon NAND Flash Memory. Jpn. J. Appl. Phys. 2018, 57, 04FE17. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

An, U.; Yoon, G.; Go, D.; Park, J.; Kim, D.; Kim, J.; Lee, J.-S. Effects of Poly-Si Grain Boundary on Retention Characteristics under Cross-Temperature Conditions in 3-D NAND Flash Memory. Micromachines 2023, 14, 2199. https://doi.org/10.3390/mi14122199

An U, Yoon G, Go D, Park J, Kim D, Kim J, Lee J-S. Effects of Poly-Si Grain Boundary on Retention Characteristics under Cross-Temperature Conditions in 3-D NAND Flash Memory. Micromachines. 2023; 14(12):2199. https://doi.org/10.3390/mi14122199

Chicago/Turabian StyleAn, Ukju, Gilsang Yoon, Donghyun Go, Jounghun Park, Donghwi Kim, Jongwoo Kim, and Jeong-Soo Lee. 2023. "Effects of Poly-Si Grain Boundary on Retention Characteristics under Cross-Temperature Conditions in 3-D NAND Flash Memory" Micromachines 14, no. 12: 2199. https://doi.org/10.3390/mi14122199

APA StyleAn, U., Yoon, G., Go, D., Park, J., Kim, D., Kim, J., & Lee, J.-S. (2023). Effects of Poly-Si Grain Boundary on Retention Characteristics under Cross-Temperature Conditions in 3-D NAND Flash Memory. Micromachines, 14(12), 2199. https://doi.org/10.3390/mi14122199