Novel Record Replacement Algorithm and Architecture for QoS Management over Local Area Networks

Abstract

:1. Introduction

2. Related Works

3. Proposed QoS Management Algorithm

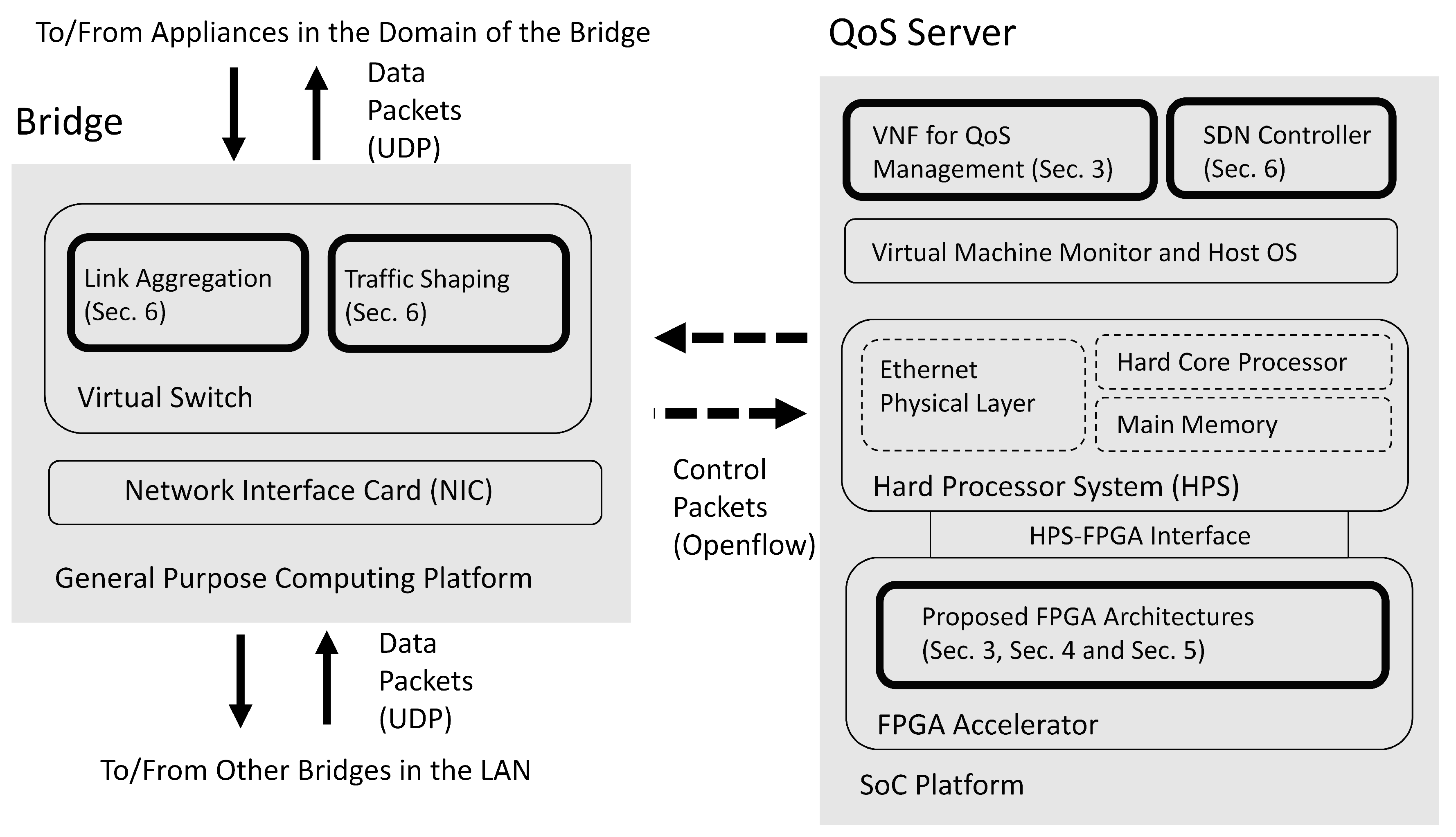

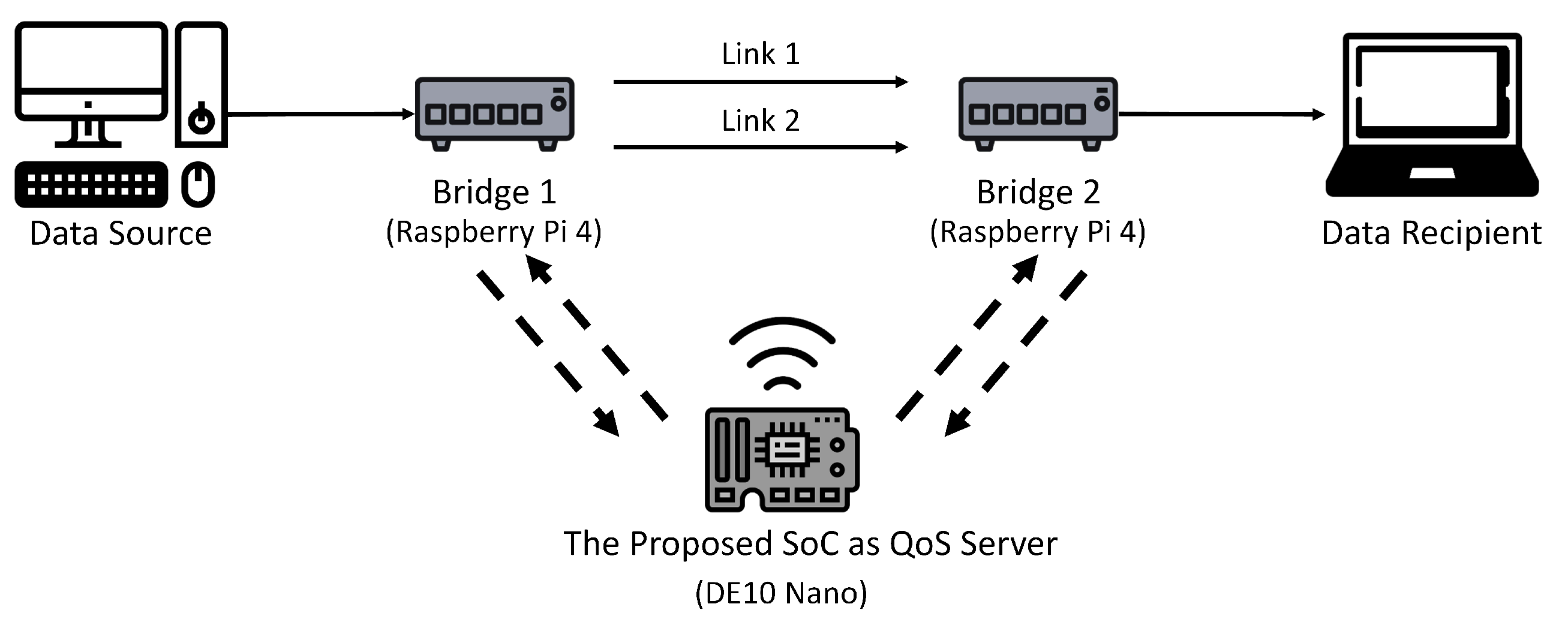

3.1. Infrastructure for QoS Server

3.2. QoS Level

3.3. GRNN-Based Service Quality Prediction

| Algorithm 1 The GRNN-based QoS Management Algorithm |

| Require: Search space . Require: Upper bound of profile size C. Require: Number of service qualities L. Require: The set of threshold for determining service qualities. Require: Initial profile . Require: QoS level specified by T. 1: loop 2: if service required in new time slot then 3: Compute the optimal bandwidth allocation from by (13). 4: Current time slot ← new time slot. 5: Bandwidth allocation of current time slot . 6: Measure the ERAB defined in (4). 7: Compute from ERAB by (6). 8: Profile_Update(, , , p, C, T) 9: Wait till the end of the current time slot. 10: end if 11: end loop |

4. The Proposed Profile Updating Algorithm

4.1. QoS Self-Awareness for Proposed GRNN Algorithm after Appending a New Record

4.1.1. New Positive Response

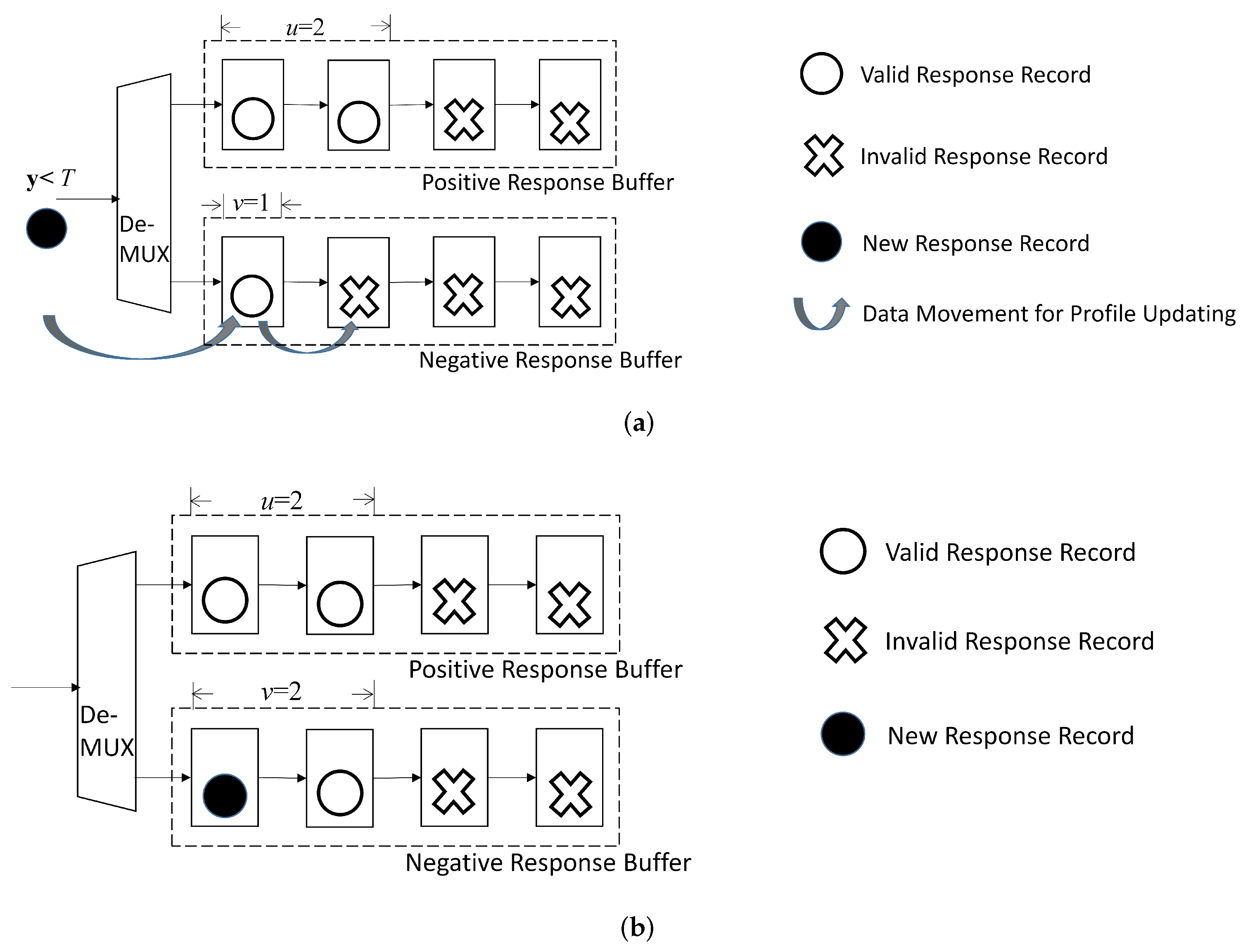

4.1.2. New Negative Response

4.2. QoS Self-Awareness for Proposed GRNN Algorithm after Replacing an Old Record

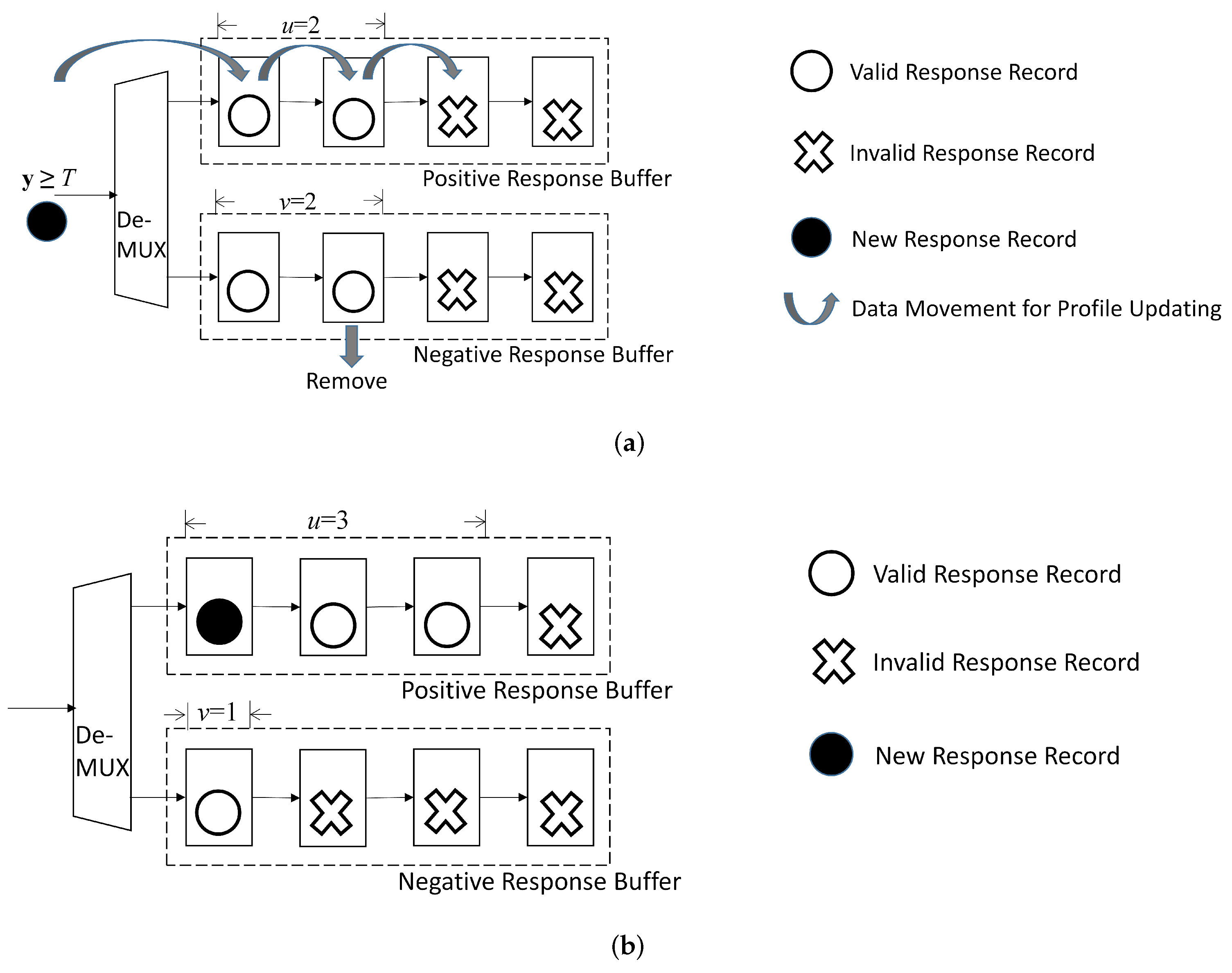

4.2.1. New Positive Response

4.2.2. New Negative Response

4.2.3. Hardware-Friendly Replacement Strategy

| Algorithm 2 The Profile Updating Algorithm |

| 1: procedure Profile_Update(, , , p, C, T) 2: if then 3: . 4: else 5: Determine set by (41). 6: if then 7: . 8: else 9: . 10: end if 11: . 12: end if 13: . 14: return , p. 15: end procedure |

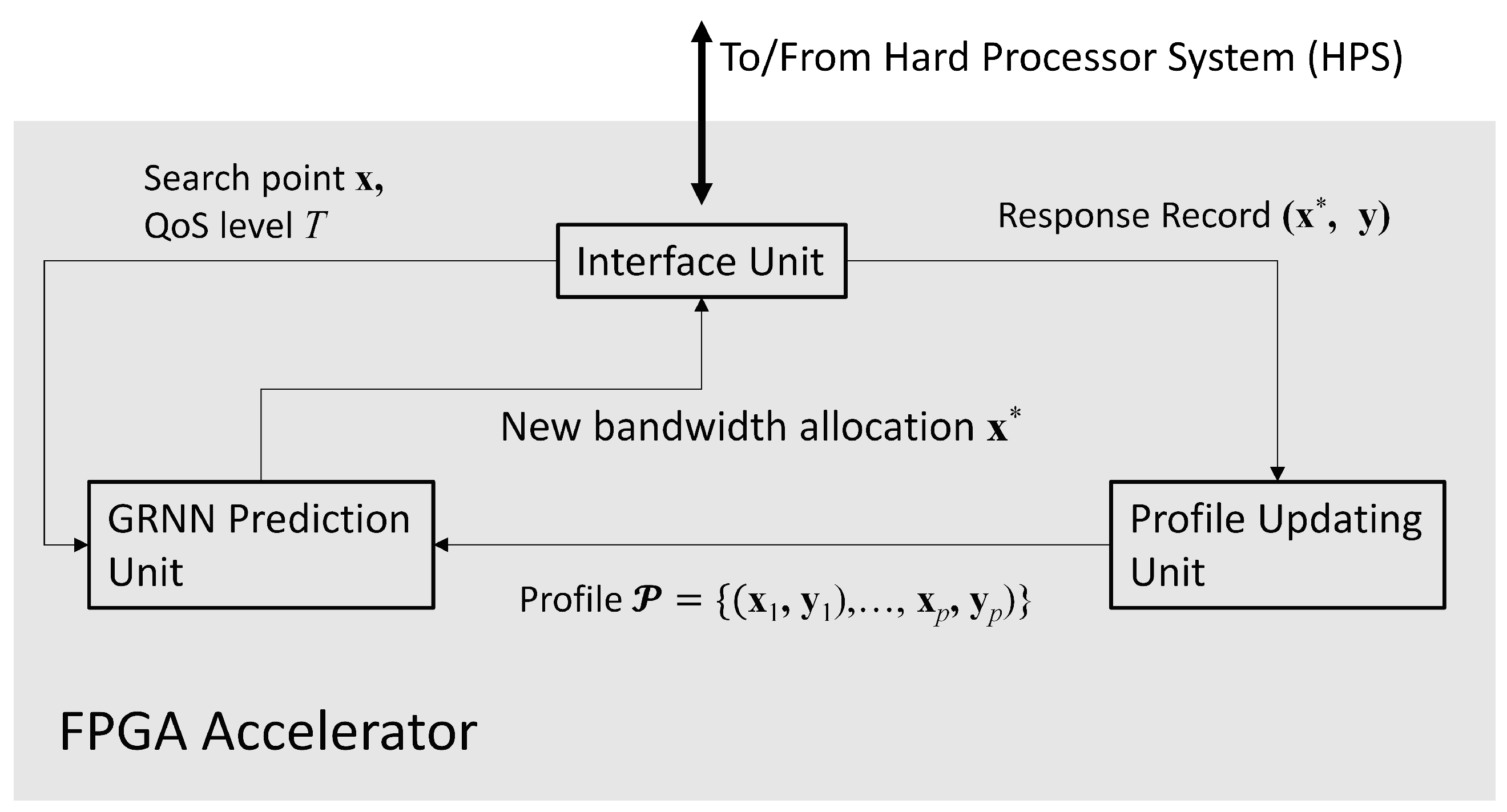

5. Proposed FPGA Accelerator for QoS Management

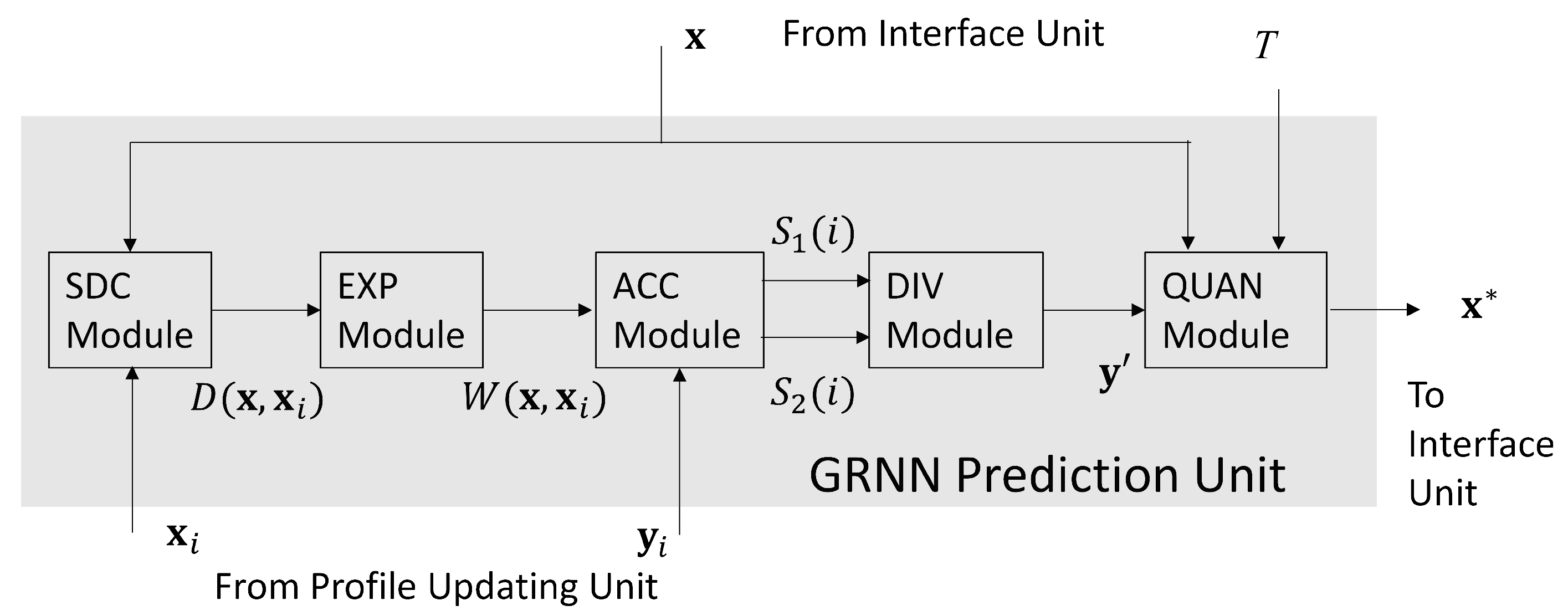

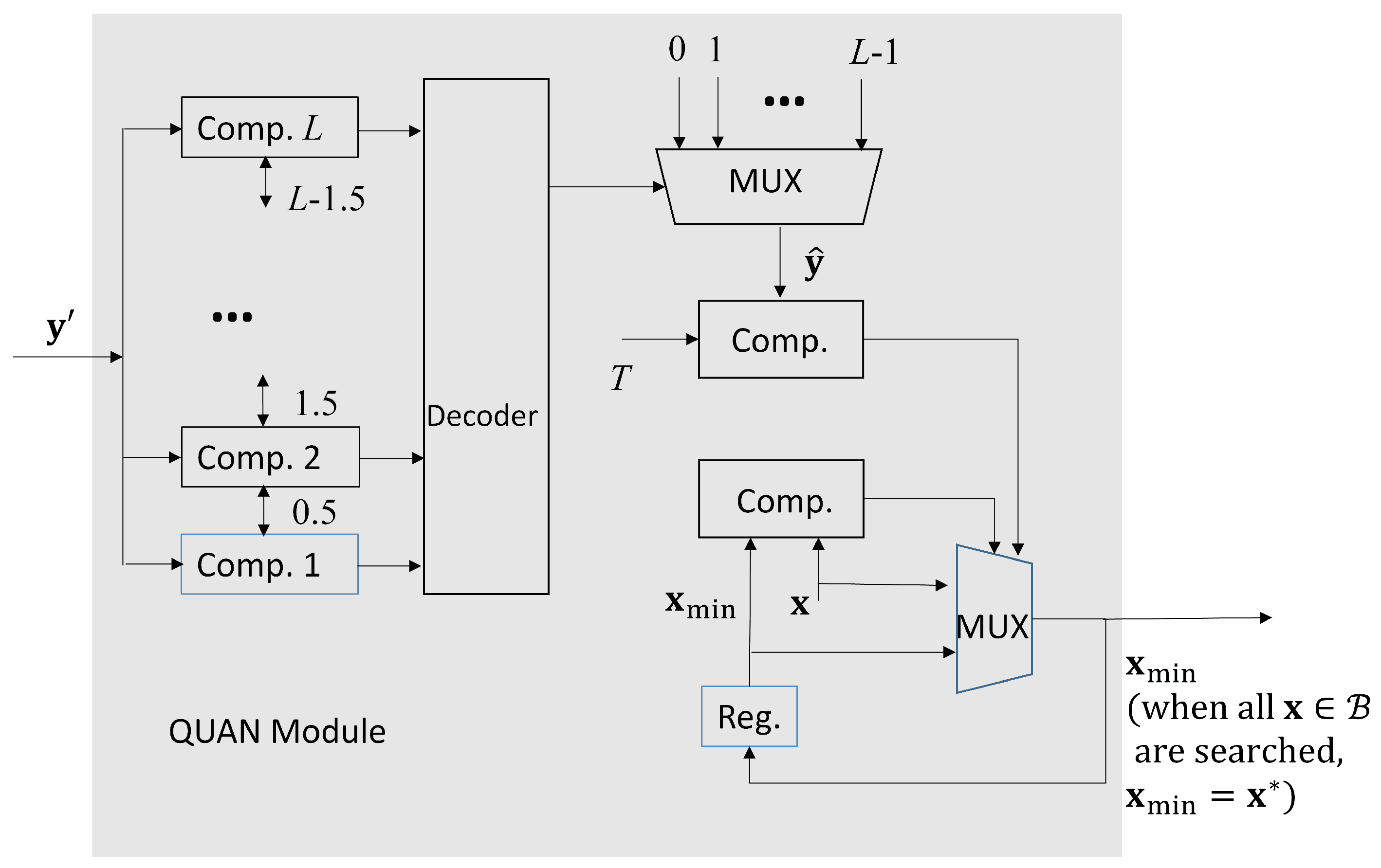

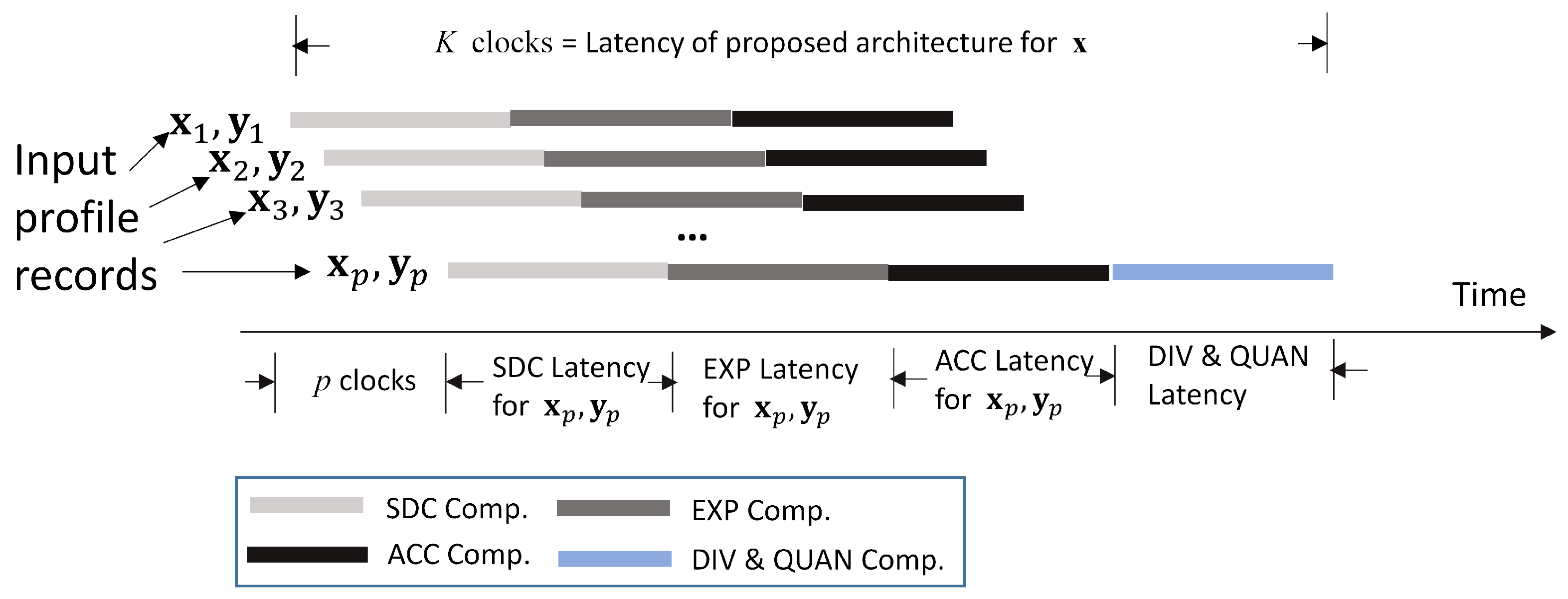

5.1. GRNN Prediction Unit

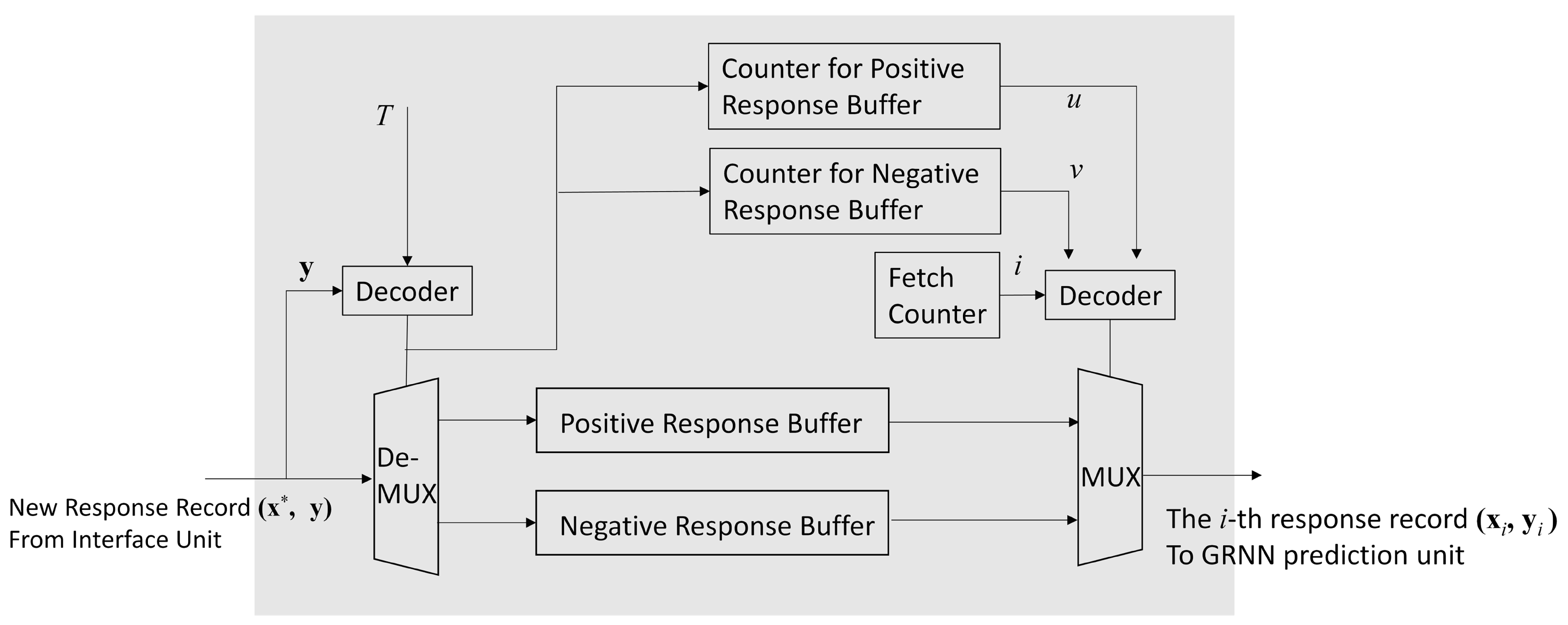

5.2. Profile Updating Unit

5.2.1. Updating Buffers in the Profile Updating Unit for

5.2.2. Updating Buffers in the Profile Updating Unit for

6. Experimental Results

6.1. Experimental Setup

6.2. Hardware Costs and Computation Speed

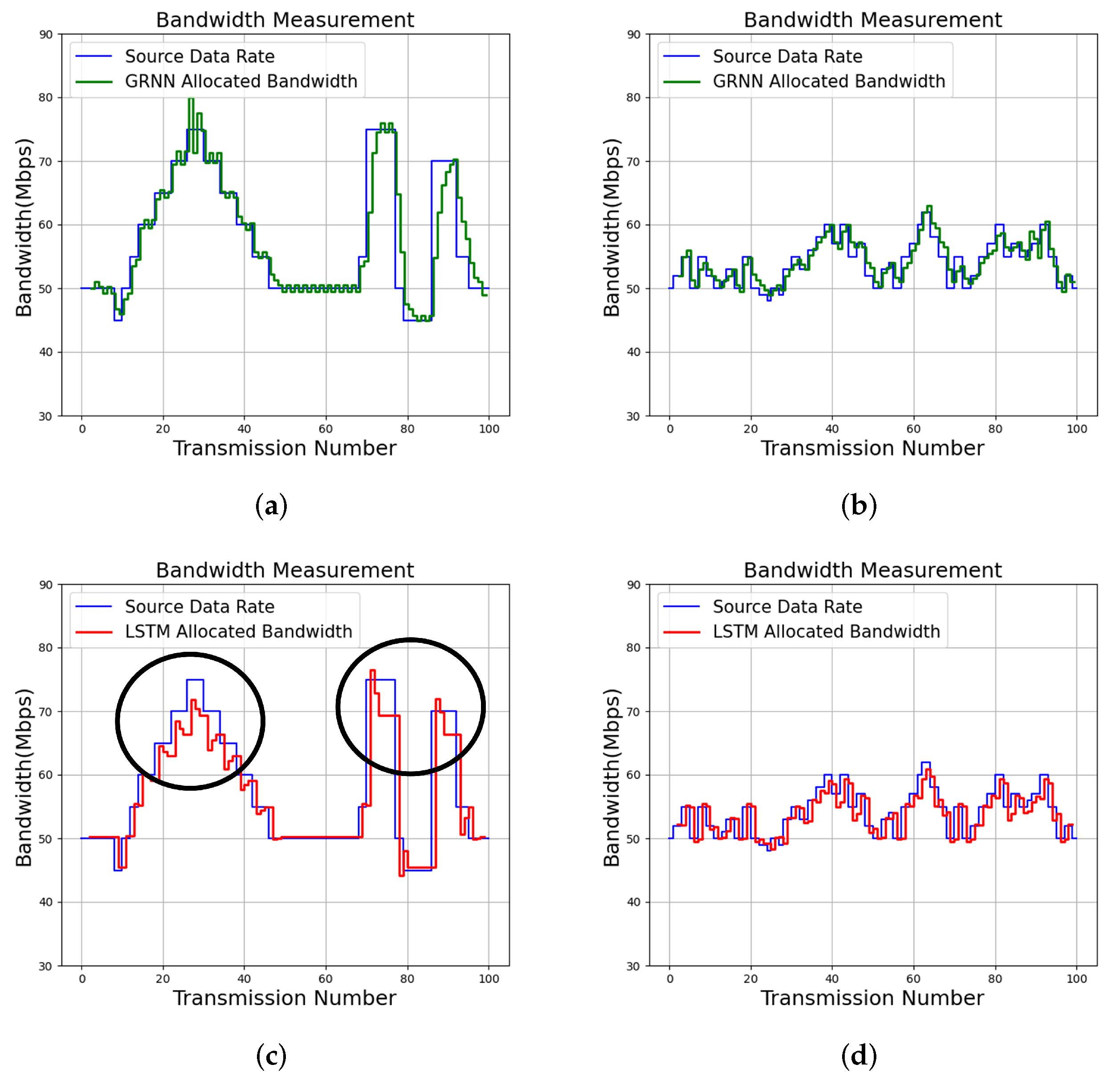

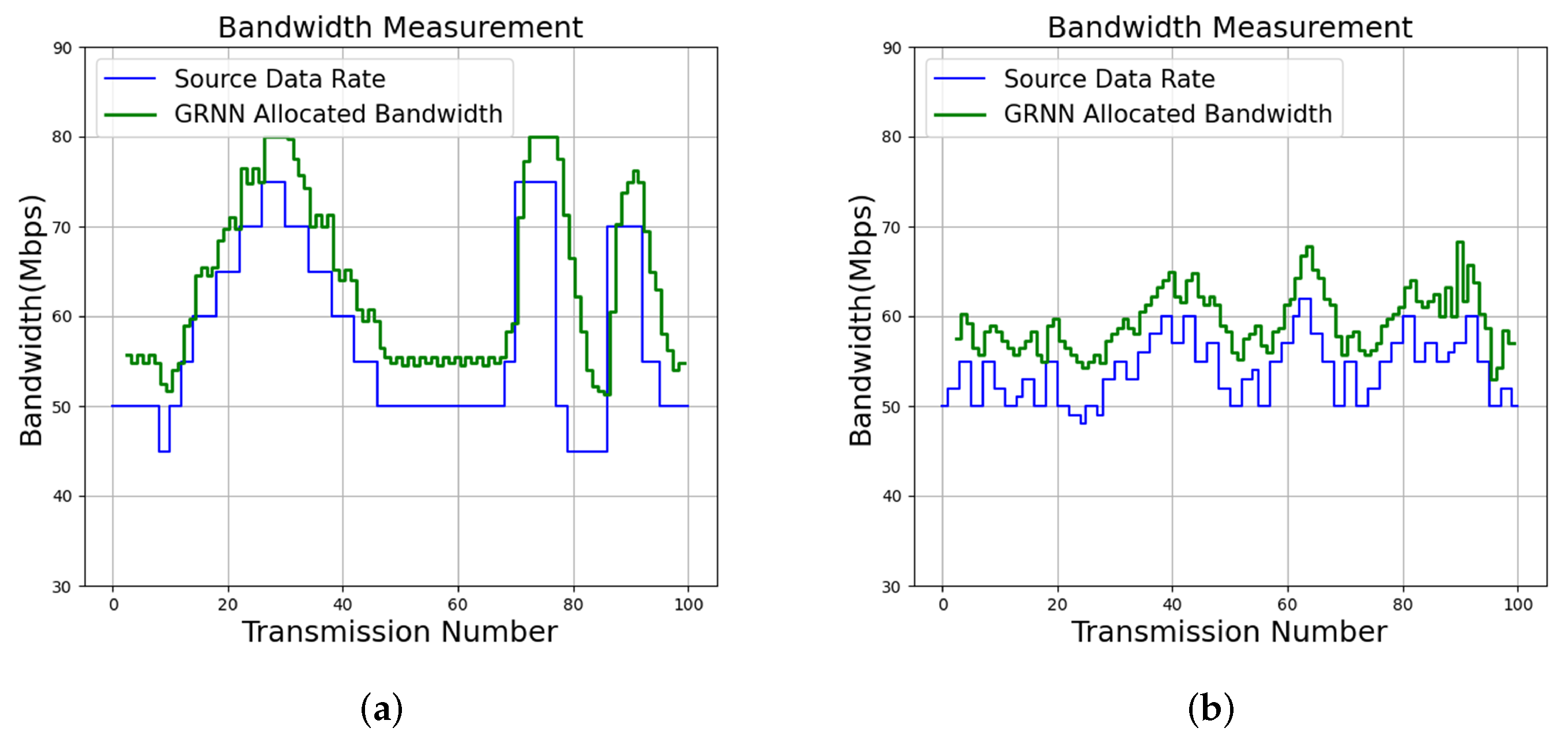

6.3. Bandwidth Allocation, DLR and RAB

7. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

Abbreviations

| ACC | ACCumulation |

| ALM | Adaptive Logic Module |

| ARIMA | Auto-Regressive Integrated Moving Average |

| DIV | Division |

| DLR | Data Loss Rate |

| ERAB | Extended Residual Allocation Bandwidth |

| EXP | Exponent |

| FP | Floating Point |

| FPGA | Field Programmable Gate Array |

| GRNN | General Regression Neural Network |

| HPS | Hard Processor System |

| LAN | Local Area Network |

| LSTM | Long Short Term Memory |

| MLP | Multilayer Perceptron |

| NIC | Network Interface Card |

| NFV | Network Function Virtualization |

| PC | Personal Computer |

| OVS | Open vSwitch |

| QUAN | Quantization |

| QoS | Quality of Service |

| RAB | Residual Allocation Bandwidth |

| RNN | Recurrent Neural Network |

| SDN | Software-defined Networking |

| SIPO | Serial-In Parallel-Out |

| SoC | System on Chip |

| SDC | Squared Distance Computation |

| UDP | User Datagram Protocol |

| VNF | Virtual Network Function |

Appendix A. Frequently Used Symbols

| Step size for the search of optimal bandwidth allocation. | |

| is the set of threshold for determining ERAB intervals . | |

| Set of all possible bandwidth allocations for the service. | |

| Maximum allowed bandwidth at the link j for the service. | |

| C | Upper bound of profile size p. |

| ERAB interval for service quality . | |

| J | Number of search candidates for GRNN prediction. |

| L | Number of service quality levels. |

| n | Number of links in the core network. |

| Set of bandwidth allocations whose service quality prediction is larger or equal to T. | |

| Profile for GRNN prediction. | |

| p | Number of records in the profile . |

| Set of records in that can be replaced without losing QoS self-awareness. | |

| R | Source data rate. |

| T | Lower bound of the service quality. |

| The average latency per search candidate . . | |

| The latency for finding the optimal bandwidth allocation given profile . | |

| The latency for updating profile given new response record . | |

| u | The number of valid response records in the positive response buffer. |

| v | The number of valid response records in the negative response buffer. |

| A bandwidth allocation for the service. | |

| Total bandwidth of the bandwidth allocation . | |

| Result of optimal bandwidth allocation. | |

| is the i-th record in profile , where is the bandwidth allocation of the record. | |

| The bandwidth of the j-th link. | |

| Measured service quality for a bandwidth allocation. | |

| Result of GRNN computation. | |

| Predicted service quality based on a bandwidth allocation . | |

| is the i-th record in profile , where is the measured service quality for . |

References

- Marchese, M. QoS over Heterogeneous Networks; Wiley: New York, NY, USA, 2007. [Google Scholar]

- Barreiros, M.; Lundqvist, P. QoS-Enabled Networks: Tools and Fundations, 2nd ed.; Wiley: New York, NY, USA, 2016. [Google Scholar]

- Goransson, P. Software Defined Networks: A Comprehensive Approach, 2nd ed.; Morgan Kaufmann: Cambridge, MA, USA, 2017. [Google Scholar]

- Wood, T.; Ramakrishnan, K.K.; Hwang, J.; Liu, G.; Zhang, W. Toward a Software-Based Network: Integrating Software Defined Networking and Network Function Virtualization. IEEE Netw. 2015, 29, 36–41. [Google Scholar] [CrossRef]

- Bailey, W.H.; Cotts, B.R.T.; Dopart, P.J. Wireless 5G Radiofrequency Technology—An Overview of Small Cell Exposures, Standards and Science. IEEE Access 2020, 8, 140792–140797. [Google Scholar] [CrossRef]

- Gholampooryazdi, B.; Hammainen, H.; Vijay, S.; Savisalo, A. Scenario planning for 5G light poles in smart cities. In Proceedings of the Conference on Internet of Things Business Models, Users, and Networks, Copenhagen, Denmark, 23–24 November 2017; pp. 1–7. [Google Scholar]

- Wang, Q.; Alcaraz-Calero, J.; Ricart-Sanchez, R.; Weiss, M.B.; Gavras, A.; Nikaein, N.; Vasilakos, X.; Giacomo, B.; Pietro, G.; Roddy, M.; et al. Enable Advanced QoS-Aware Network Sclicing in 5G Networks for Slice-Based Media Use Cases. IEEE Trans. Broadcast. 2019, 65, 444–453. [Google Scholar] [CrossRef] [Green Version]

- Rusti, B.; Stefanescu, H.; Iordache, M.; Ghenta, J.; Brezeanu, C.; Patachia, C. Deploying Smart City components for 5G network slicing. In Proceedings of the 2019 European Conference on Networks and Communications, Valencia, Spain, 18–21 June 2019; pp. 149–154. [Google Scholar]

- Hwang, W.J.; Tai, T.M.; Pan, B.T.; Lou, T.Y.; Jhang, Y.J. An Intelligent QoS Algorithm for Home Networks. IEEE Commun. Lett. 2019, 23, 588–591. [Google Scholar] [CrossRef]

- Specht, D.F. A general regression neural network. IEEE Trans. Neural Netw. 1991, 2, 568–576. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Woods, R.; McAllister, J.; Lightbody, G.; Yi, Y. FPGA-Based Implementation of Signal Processing Systems, 2nd ed.; Wiley: New York, NY, USA, 2017. [Google Scholar]

- Ledin, J. Architecting High-Performance Embedded Systems: Design and Build High-Performance Real-Time Digital Systems Based on FPGAs and Custom Circuits; Packt Publishing: Birmingham, UK, 2021. [Google Scholar]

- Shang, W.C.; Hwang, W.J.; Tai, T.M.; Jhang, Y.J. An FPGA Assisted Intelligent QoS Management System for Local Area Networks. IEEE Syst. J. 2021. accepted. [Google Scholar] [CrossRef]

- Goodfellow, I.; Bengio, Y.; Courville, A. Deep Learning; MIT Press: Cambridge, MA, USA, 2016. [Google Scholar]

- White, G.; Palade, A.; Clarke, S. Forecasting QoS attributes using LSTM networks. In Proceedings of the IEEE International Joint Conference on Neural Networks, Rio de Janeiro, Brazil, 8–13 July 2018. [Google Scholar]

- Jirsik, T.; Trcka, S.; Celeda, P. Quality of Service Forecasting with LSTM Neural Network. In Proceedings of the IFIP/IEEE International Symposium on Integrated Network Management, Arlington, VA, USA, 8–12 April 2019; pp. 251–260. [Google Scholar]

- Ye, Z.; Mistry, S.; Bouguettaya, A.; Dong, H. Long Term QoS-Aware Cloud Service Composition Using Multivariate Time Series Analysis. IEEE Trans. Serv. Comput. 2016, 9, 382–393. [Google Scholar] [CrossRef]

- Shantharama, S.; Thyagaturu, A.S.; Reisslein, M. Hardware accelerated platforms and infrastructures for network functions: A survey of enabling technologies and research studies. IEEE Access 2020, 8, 132021–132085. [Google Scholar] [CrossRef]

- Niemiec, G.S.; Batista, L.M.S.; Schaeffer-Filho, A.E.; Nazar, G.L. A Survey on FPGA Support for the Feasible Execution of Virtualized Network Functions. IEEE Commun. Surv. Tutor. 2020, 22, 504–525. [Google Scholar] [CrossRef]

- Lazaro, J.; Arias, J.; Martin, J.L.; Alegria, I.; Andreu, J.; Jimenez, J. An Implementation of a General Regression Neural Network on FPGA with Direct Matlab Link. In Proceedings of the IEEE International Conference on Industrial Technology, Hammamet, Tunisia, 8–10 December 2004; pp. 1150–1155. [Google Scholar]

- Polat, O.; Yildirim, T. FPGA Implementation of a General Regression Neural Network: An Embedded Pattern Classification System. Digit. Signal Process. 2010, 20, 881–886. [Google Scholar] [CrossRef]

- Krutikov, A.K.; Meltsov, V.Y.; Lapitsky, A.A.; Rostovtsev, V.S. FPGA Implementation of a Prediction Module Based on a Generalized Regression Neural Network. In Proceedings of the IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering, Moscow, Russia, 27–30 January 2020; pp. 147–150. [Google Scholar]

- Patterson, D.A.; Hennessy, J.L. Computer Organization and Design: The Hardware/Software Interface, 5th ed.; Morgan Kaufmann: Waltham, MA, USA, 2014. [Google Scholar]

- OVS: Open vSwitch. Available online: http://openvswitch.org/ (accessed on 25 January 2022).

- iPerf: The Ultimate Speed Test Tool for TCP, UDP and SCTP. Available online: https://iperf.fr/ (accessed on 25 January 2022).

| Service Quality y | ERAB Intervals | Interval Range (Mbps) |

|---|---|---|

| 5 | ||

| 4 | ||

| 3 | ||

| 2 | ||

| 1 | ||

| 0 |

| QoS Level with T | Allowed Service Qualities | Allowed ERAB Intervals |

|---|---|---|

| 5 | 5 | |

| 4 | 4, 5 | |

| 3 | 3, 4, 5 | |

| 2 | 2, 3, 4, 5 | |

| 1 | 1, 2, 3, 4, 5 |

| Unit Name | FP Adder | FP Mult. | FP Acc. | FP Divider | Exponent Operator | FP Comparator | Shift Register |

|---|---|---|---|---|---|---|---|

| GRNN Prediction Unit | 0 | ||||||

| Profile Updating Unit | 0 | 0 | 0 | 0 | 0 | 0 | |

| Overall |

| Profile Size Upper Bound | 30 | 50 | 80 | 150 | 300 | 360 |

|---|---|---|---|---|---|---|

| Number of ALMs | 9444 | 11,366 | 14,385 | 20,955 | 33,109 | 36,462 |

| Number of Registers | 19,105 | 23,521 | 30,372 | 46,185 | 75,091 | 84,008 |

| Block Memory Bits | 8768 | 8768 | 8768 | 8768 | 8768 | 8768 |

| Number of DSP Blocks | 21 | 21 | 21 | 21 | 21 | 21 |

| Hardware Architecture | FPGA Device | Clock Rate | Profile Size | Average Latency |

|---|---|---|---|---|

| Arch. in [13] | Cyclone V 5CSEBA6 | 50 MHz | 54 | 1.22 s |

| Arch. in [20] | Virtex X2V1000 | 50 MHz | 10 | 1.00 s |

| Arch. in [21] | Spartan 3 XC3S2000 | 10 MHz | 55 | 5.60 s |

| Arch. in [22] | Cyclone III EP3C120 | NA | 16 | 0.74 s |

| Proposed | Cyclone V 5CSEBA6 | 50 MHz | 80 | 1.63 s |

| Profile Size | 30 | 50 | 80 | 100 | 200 | 300 | 360 |

|---|---|---|---|---|---|---|---|

| Proposed SoC | 22.09 (ms) | 28.31 (ms) | 34.20 (ms) | 38.56 (ms) | 52.88 (ms) | 64.51 (ms) | 67.89 (ms) |

| Personal Computer | 1169.68 (ms) | 1864.86 (ms) | 3418.17 (ms) | 3500.69 (ms) | 5700.90 (ms) | 7487.50 (ms) | 8030.31 (ms) |

| Speedup | 52.95 | 65.87 | 99.95 | 90.79 | 107.81 | 116.07 | 118.28 |

| Profile Size | 30 | 50 | 80 | 100 | 200 | 300 | 360 |

|---|---|---|---|---|---|---|---|

| Proposed SoC | 0.11 (ms) | 0.12 (ms) | 0.12 (ms) | 0.12 (ms) | 0.12 (ms) | 0.12 (ms) | 0.12 (ms) |

| Personal Computer | 1.73 (ms) | 1.69 (ms) | 1.59 (ms) | 1.54 (ms) | 1.61 (ms) | 1.66 (ms) | 1.64 (ms) |

| Speedup | 15.72 | 14.08 | 13.25 | 12.83 | 13.41 | 13.83 | 13.67 |

| Algorithms | LSTM [16] | Proposed (T = 6) | Proposed (T = 8) | |||

|---|---|---|---|---|---|---|

| ave RAB | ave DLR | ave RAB | ave DLR | ave RAB | ave DLR | |

| Service 1 (Mbps) | 0.82 | 2.28 | 1.08 | 0.88 | 5.35 | 0.02 |

| Service 2 (Mbps) | 1.38 | 1.62 | 1.12 | 0.90 | 5.32 | 0.00 |

| Profile Size Upper Bound | |||||||

|---|---|---|---|---|---|---|---|

| ave RAB | ave DLR | ave RAB | ave DLR | ave RAB | ave DLR | ||

| Service 1 | 1.84 | 1.19 | 1.02 | 1.06 | 1.08 | 0.88 | |

| (Mbps) | 5.73 | 0.09 | 5.63 | 0.02 | 5.35 | 0.02 | |

| Service 2 | 1.30 | 0.68 | 1.28 | 0.88 | 1.12 | 0.90 | |

| (Mbps) | 5.58 | 0.01 | 5.61 | 0.01 | 5.32 | 0.00 | |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Tung, Y.-C.; Law, Y.-W.; Hwang, W.-J.; Tai, T.-M.; Ho, C.-H.; Chen, C.-C. Novel Record Replacement Algorithm and Architecture for QoS Management over Local Area Networks. Micromachines 2022, 13, 594. https://doi.org/10.3390/mi13040594

Tung Y-C, Law Y-W, Hwang W-J, Tai T-M, Ho C-H, Chen C-C. Novel Record Replacement Algorithm and Architecture for QoS Management over Local Area Networks. Micromachines. 2022; 13(4):594. https://doi.org/10.3390/mi13040594

Chicago/Turabian StyleTung, Yi-Chih, Yuk-Wing Law, Wen-Jyi Hwang, Tsung-Ming Tai, Chih-Hsiang Ho, and Cheng-Chang Chen. 2022. "Novel Record Replacement Algorithm and Architecture for QoS Management over Local Area Networks" Micromachines 13, no. 4: 594. https://doi.org/10.3390/mi13040594

APA StyleTung, Y.-C., Law, Y.-W., Hwang, W.-J., Tai, T.-M., Ho, C.-H., & Chen, C.-C. (2022). Novel Record Replacement Algorithm and Architecture for QoS Management over Local Area Networks. Micromachines, 13(4), 594. https://doi.org/10.3390/mi13040594