Multi-Band Power Amplifier Module with Back-Off Efficiency Improvement using Ultra-Compact 3D Vertical Stack Multi-Chip Package for Cellular Handsets

Abstract

1. Introduction

2. Circuit Design

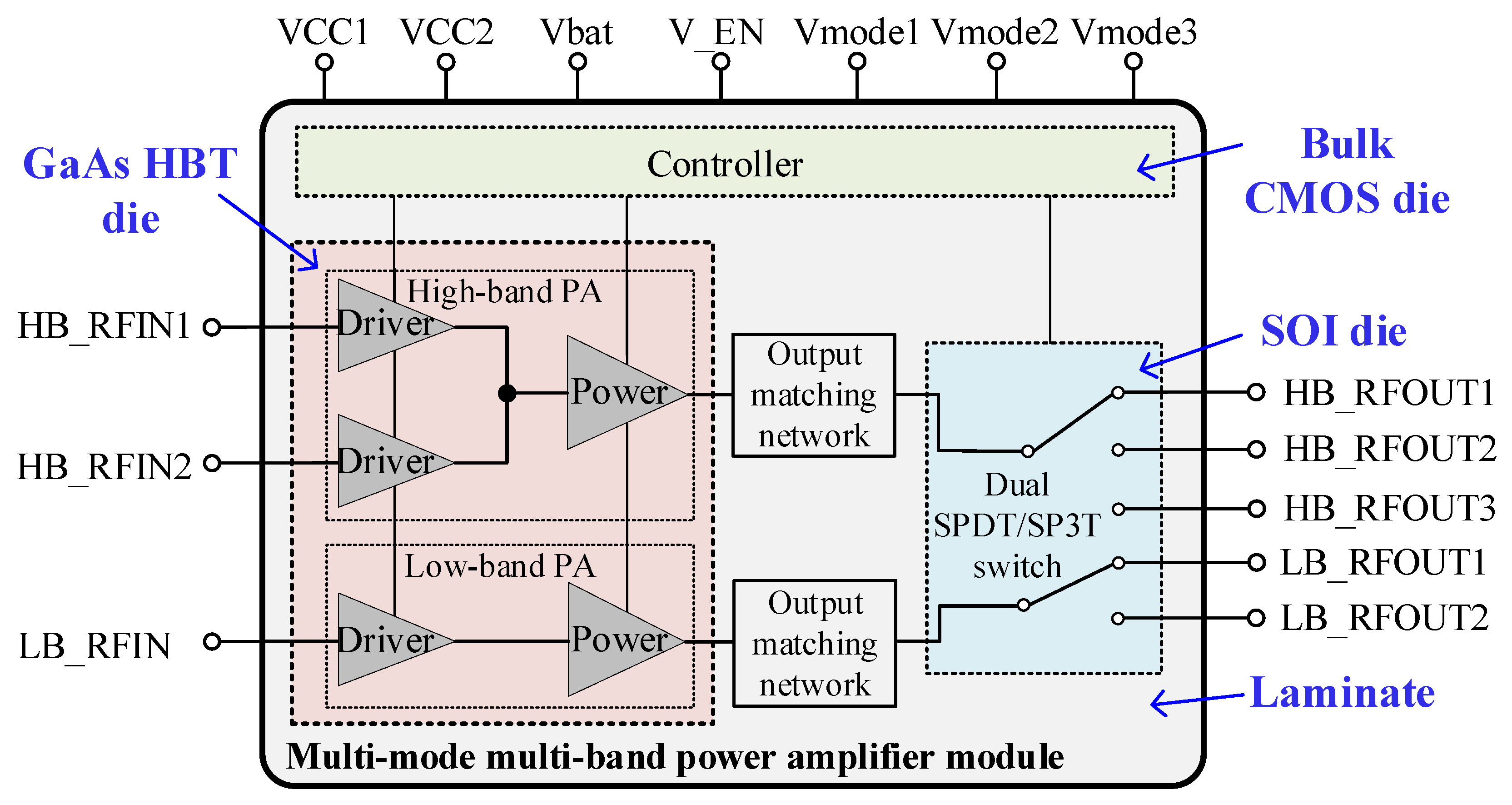

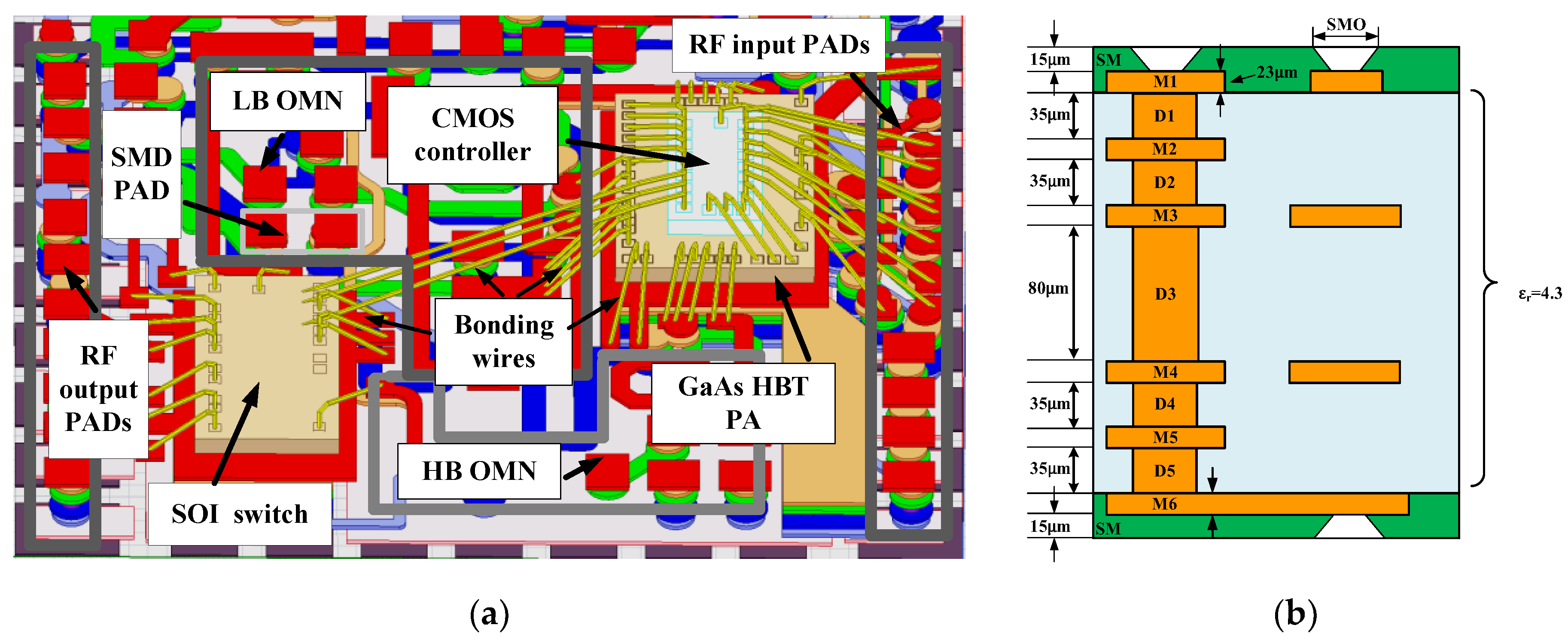

2.1. MMMB PAM Architecture

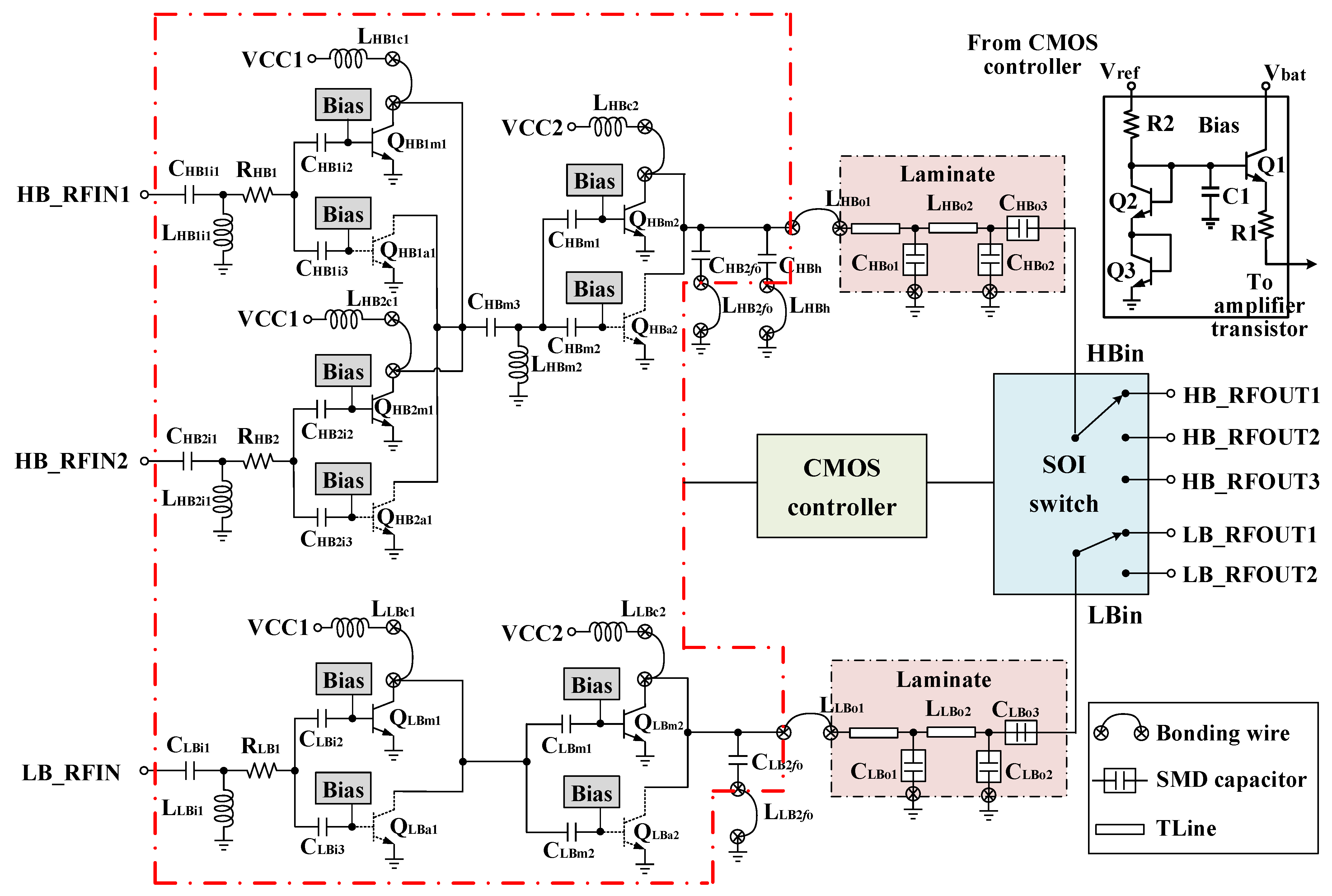

2.2. GaAs HBT PA Design

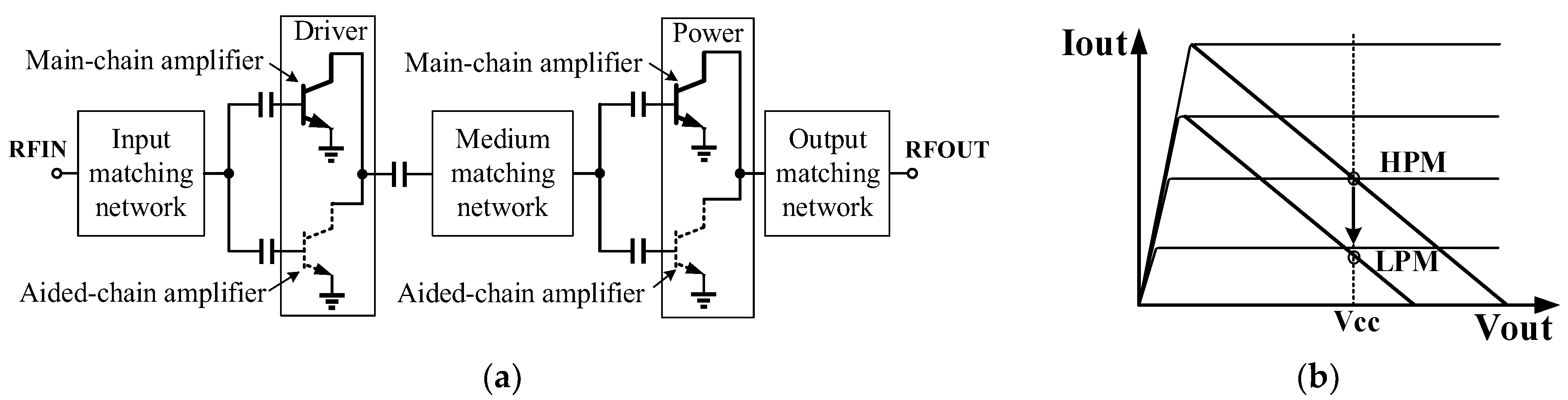

2.2.1. Two-Stage Dual-Chain HBT PA Configuration

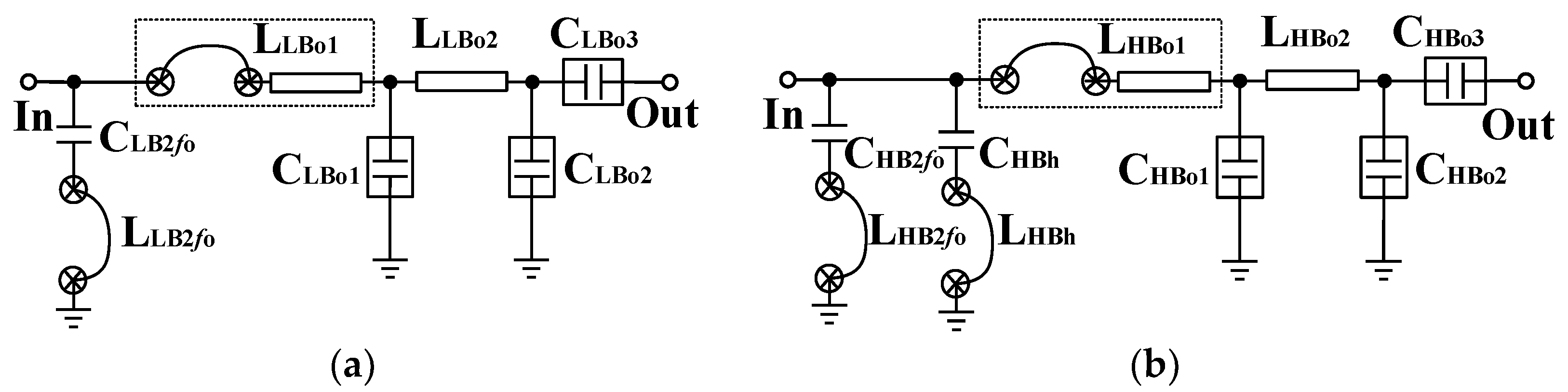

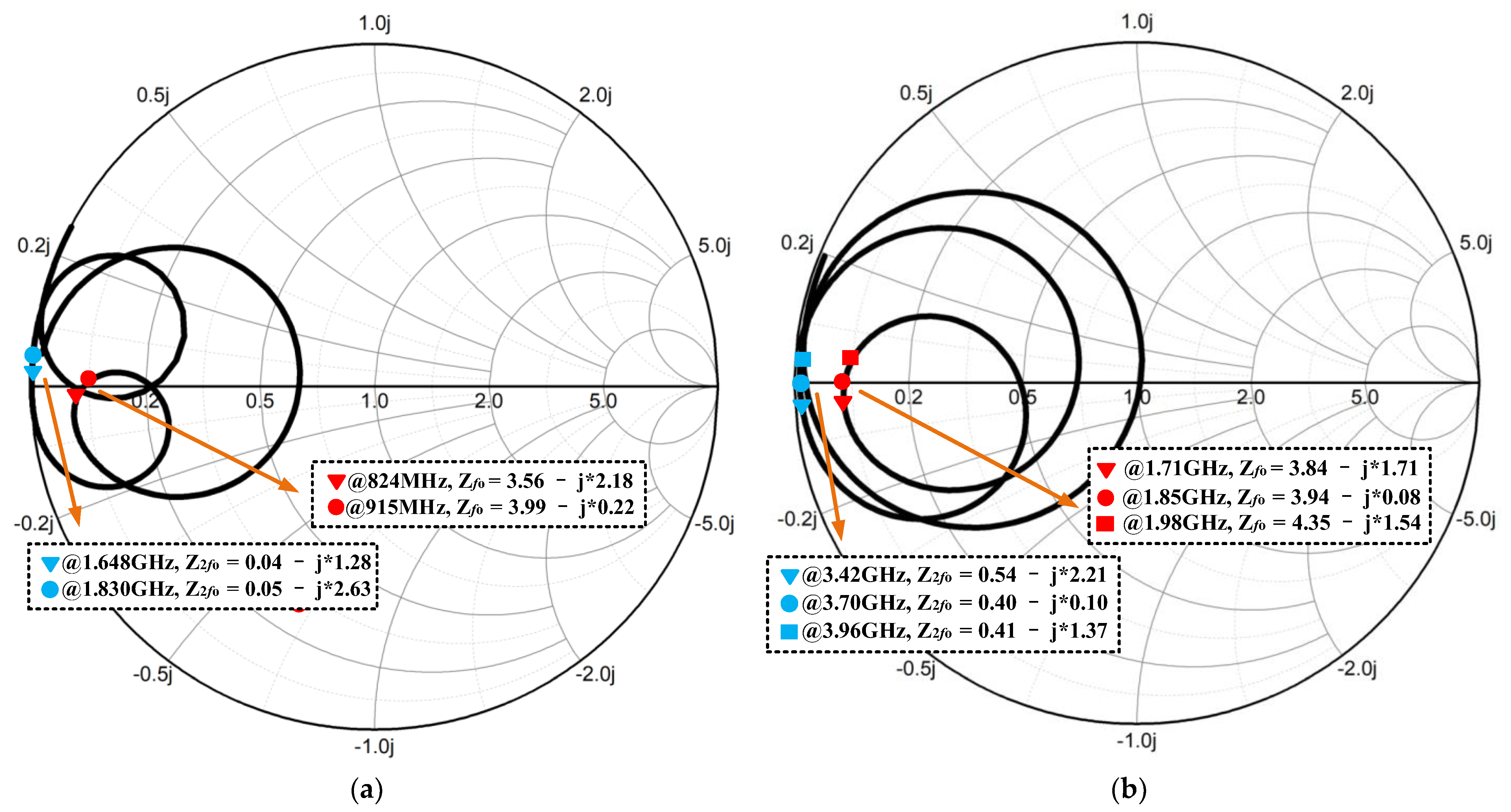

2.2.2. Broadband Output Matching Technique

2.2.3. Detailed Structure of Proposed MMMB PA

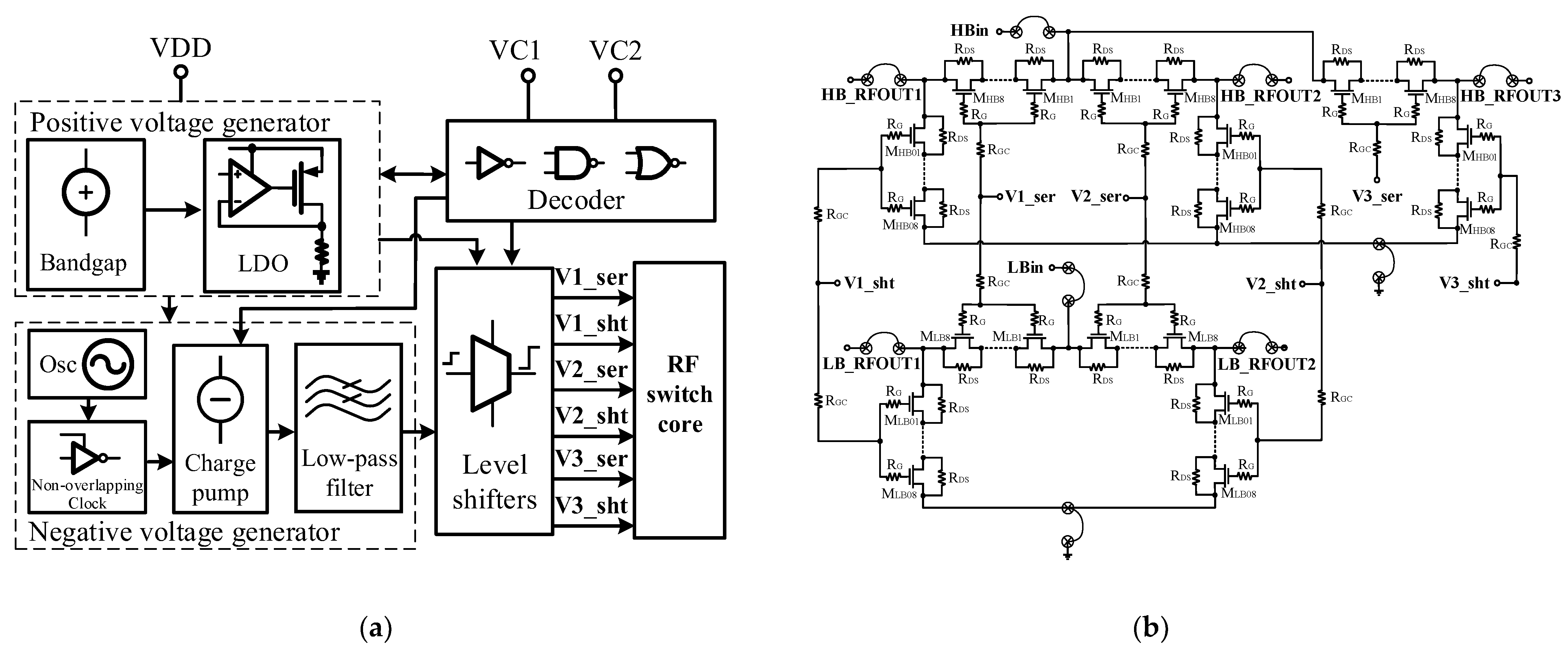

2.3. SOI Switch Design

2.4. Bulk CMOS Controller Design

2.5. Laminate Design

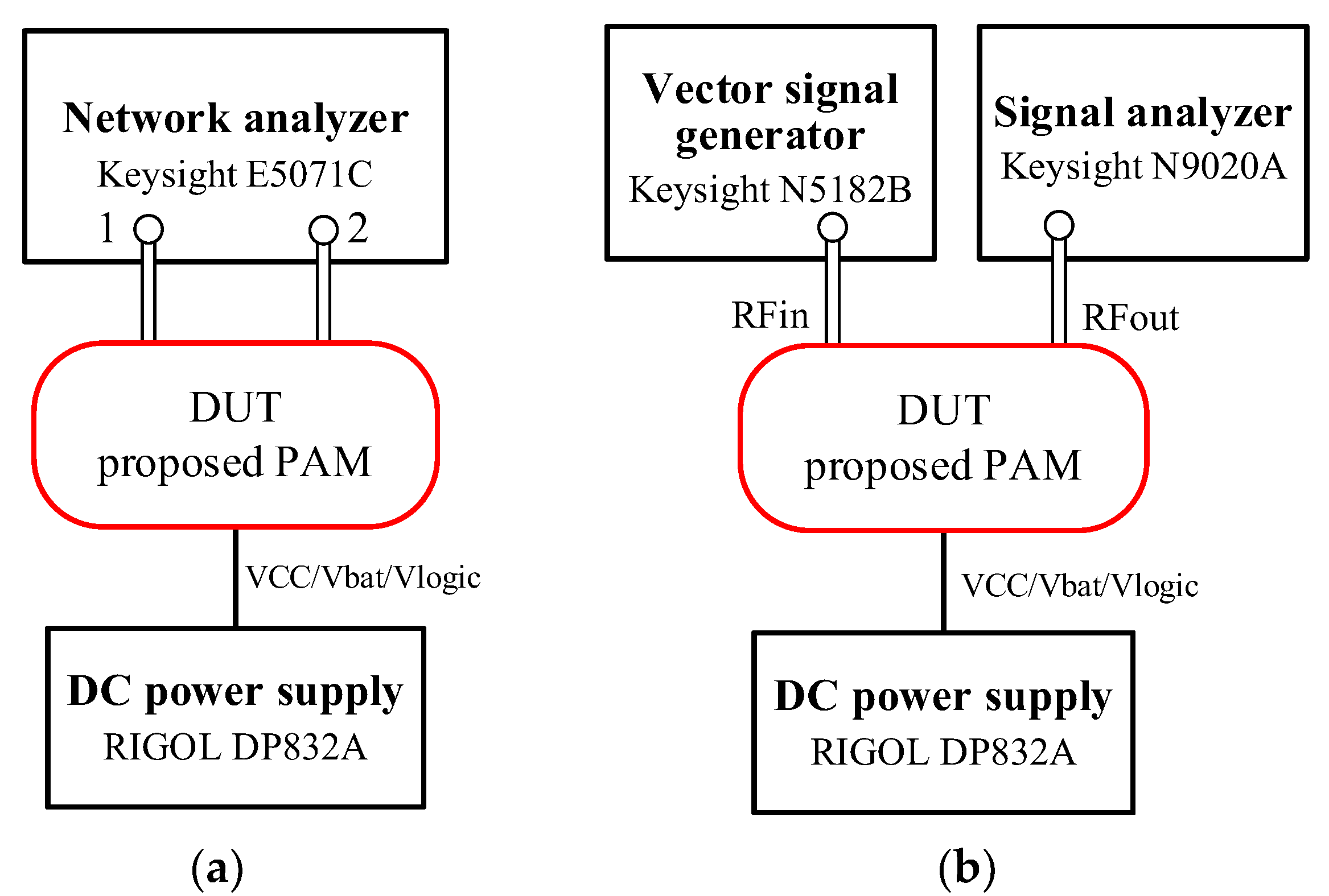

3. Measurement Results and Discussion

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Refai, W.Y.; Davis, W.A. A highly efficient linear multimode multiband Class-J power amplifier utilizing GaAs HBT for handset modules. IEEE Trans. Microw. Theory Tech. 2020, 648, 3519–3531. [Google Scholar]

- Clifton, J.C.; Lawrenson, A.; Motoyama, H.; Kohama, K. Wideband high efficiency multi-band, multi-mode (LTE/WCDMA/GSM) power amplifier for mobile terminals. In Proceedings of the European Microwave Conference, Nuremberg, Germany, 6–8 October 2013. [Google Scholar]

- Choi, K.; Kim, M.; Kim, H.; Jung, S.; Cho, J.; Yoo, S.; Kim, Y.H.; Yoo, H.; Yang, Y. A highly linear two-stage amplifier integrated circuit using InGaP/GaAs HBT. IEEE J. Solid-State Circuits 2010, 45, 2038–2043. [Google Scholar] [CrossRef]

- Balteanu, F. A CMOS high bandwidth envelope tracking and power amplifiers for LTE carrier aggregation. In Proceedings of the IEEE Topical Conference on Power Amplifiers for Wireless and Radio Applications (PAWR), San Diego, CA, USA, 28–30 January 2015. [Google Scholar]

- Oh, H.; Choi, W.; Koo, H.; Shin, J.; Chen, Y.; Jeon, H.; Choi, Y.; Jung, H.; Hwang, J.; Yang, Y. 2.8–3.8 GHz broadband InGaP/GaAs HBT Doherty power amplifier IC for 5G new radio handset. In Proceedings of the IEEE/MTT-S International Microwave Symposium (IMS), Denver, CO, USA, 19–24 June 2022. [Google Scholar]

- Kang, S.; Jeon, M.; Kim, J. Highly efficient 5.15- to 5.85-GHz neutralized HBT power amplifier for LTE applications. IEEE Microw. Wirel. Compon. Lett. 2018, 28, 254–256. [Google Scholar] [CrossRef]

- Ding, X.; Zhang, L. A high-efficiency GaAs MMIC power amplifier for multi-standard system. IEEE Microw. Wirel. Compon. Lett. 2016, 26, 55–57. [Google Scholar] [CrossRef]

- Zhang, Z.; Zhang, G.; Yu, K.; Lin, J.; Liu, Z. A 0.1–2.7GHz SOI SP8T antenna switch adopting body self-adapting bias technique for low-loss high-power applications. Int. J. Circuit Theory Appl. 2017, 46, 827–841. [Google Scholar] [CrossRef]

- Hill, C.; Levy, C.S.; AlShammary, H.; Hamza, A.; Buckwalter, J.F. RF watt-level low-insertion-loss high-bandwidth SOI CMOS switches. IEEE Trans. Microw. Theory Tech. 2018, 66, 5724–5736. [Google Scholar] [CrossRef]

- Gouba, O.A.; Louët, Y. Theoretical analysis of the trade-off between efficiency and linearity of the high power amplifier in OFDM context. In Proceedings of the European Microwave Conference, Poznan, Poland, 18–20 April 2012. [Google Scholar]

- Cheng, N.; Young, J.P. Challenges and requirements of multimode multiband power amplifiers for mobile applications. In Proceedings of the IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), Waikoloa, HI, USA, 16–19 October 2011. [Google Scholar]

- Balteanu, F.; Modi, H.; Khesbak, S.; Drogi, S.; DiCarlo, P. Envelope tracking LTE multimode power amplifier with 44% overall efficiency. In Proceedings of the IEEE Asia Pacific Microwave Conference (APMC), Kuala Lumpur, Malaysia, 13–16 November 2017. [Google Scholar]

- Jin, Q.; Ruan, X.; Ren, X.; Wang, Y.; Leng, Y.; Tse, C.K. Series-parallel form switch-linear hybrid envelope-tracking power supply to achieve high efficiency. IEEE Trans. Ind. Electron. 2017, 64, 244–252. [Google Scholar] [CrossRef]

- Vasić, M.; Garcia, O.; Oliver, J.A.; Alou, P.; Diaz, D.; Cobos, J.A.; Gimeno, A.; Pardo, J.M.; Benavente, C.; Ortega, F.J. Efficient and linear power amplifier based on envelope elimination and restoration. IEEE Trans. Power Electron. 2012, 27, 5–9. [Google Scholar] [CrossRef]

- Imai, S.; Mukai, K.; Tanaka, S.; Okabe, H. Bandwidth optimization of Doherty power amplifier based on source converters for 5G mobile handsets. IEEE Trans. Microw. Theory Tech. 2022, 70, 813–826. [Google Scholar] [CrossRef]

- Jeon, H.; Na, J.; Oh, H.; Yang, Y. Two-stage CMOS/GaAs HBT Doherty power amplifier module for 5G handsets. In Proceedings of the IEEE International Symposium on Radio-Frequency Integration Technology (RFIT), Busan, Korea, 29–31 August 2022. [Google Scholar]

- Deltimple, N.; Leyssenne, L.; Kerhervé, E.; Deval, Y.; Belot, D. Dynamic biasing techniques for RF power amplifier linearity and efficiency improvement. In Proceedings of the IEEE International Conference on Integrated Circuit Design and Technology, Grenoble, France, 2–4 June 2010. [Google Scholar]

- Kang, D.; Kim, D.; Choi, J.; Kim, J.; Cho, Y.; Kim, B. A multimode/multiband power amplifier with a boosted supply modulator. IEEE Trans. Microw. Theory Tech. 2010, 58, 2598–2608. [Google Scholar] [CrossRef]

- Leipold, D.; Allen, W.; Sheehy, P.; Hau, G. A WCDMA 41% power efficiency direct DC coupled hybrid CMOS/GaAs power amplifier with pre-distortion linearization. In Proceedings of the IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Montreal, Canada, 17–19 June 2012. [Google Scholar]

- Kim, K.; Choi, H. High-efficiency high-voltage class F amplifier for high-frequency wireless ultrasound systems. PLoS ONE 2021, 16, e0249034. [Google Scholar]

- Chen, K.; Peroulis, D. Design of broadband highly efficient harmonic-tuned power amplifier using in-band continuous class-F −1 /F mode transferring. IEEE Trans. Microw. Theory Tech. 2012, 60, 4107–4116. [Google Scholar] [CrossRef]

- Alizadeh, A.; Hassanzadehyamchi, S.; Medi, A. Integrated output matching networks for Class–J/J−1 power amplifier. IEEE Trans. Circuits Syst. I Reg. Pap. 2019, 66, 2921–2934. [Google Scholar] [CrossRef]

- Jagadheswaran, U.R.; Ramiah, H.; Mak, P.I.; Martins, R.P. A 2-μm InGaP/GaAs Class-J power amplifier for multi-band LTE achieving 35.8-dB gain, 40.5% to 55.8% PAE and 28-dBm linear output power. IEEE Trans. Microw. Theory Tech. 2016, 64, 200–209. [Google Scholar] [CrossRef]

- Xie, H.; Cheng, Y.; Ding, Y.; Wang, L.; Fan, Y. A C-band high-efficiency power amplifier MMIC with second-harmonic control in 0.25 µm GaN HEMT Technology. IEEE Microw. Wirel. Compon. Lett. 2021, 31, 1303–1306. [Google Scholar] [CrossRef]

- Hookari, M.; Roshani, S.; Roshani, S. High-efficiency balanced power amplifier using miniaturized harmonics suppressed coupler. Int. J. RF Microw. Comput. Aided Eng. 2020, 30, e22252. [Google Scholar] [CrossRef]

- Chung, S.; Ma, R.; Teo, K.H. Design considerations on wideband envelope termination for high efficiency RF power amplifiers. Electron. Lett. 2016, 52, 460–462. [Google Scholar] [CrossRef]

- Kang, S.; Kim, U.; Kim, J. A multi-mode multi-band reconfigurable power amplifier for 2G/3G/4G handset applications. IEEE Microw. Wirel. Compon. Lett. 2015, 25, 49–51. [Google Scholar] [CrossRef]

- Yamamoto, K.; Miyashita, M.; Maki, S.; Takahashi, Y.; Fujii, K.; Fujiwara, S.; Kitabayashi, F.; Suzuki, S.; Shimura, T.; Hieda, M.; et al. A WCDMA multiband power amplifier module with Si-CMOS/GaAs-HBT hybrid power-stage configuration. IEEE Trans. Microw. Theory Tech. 2016, 64, 810–825. [Google Scholar] [CrossRef]

- Lin, J.; Zhang, G.; Zhang, Z.; Zheng, Y.; Li, J.; Ou, L.; Liu, Z. A compact multi-mode multi-band power amplifier with harmonic-suppression matching networks for GSM/TD-SCDMA/LTE terminals. IEICE Electron. Expr. 2016, 13, 1–12. [Google Scholar] [CrossRef][Green Version]

- Kim, U.; Kang, S.; Woo, J.; Kwon, Y.; Kim, J. A multiband reconfigurable power amplifier for UMTS handset applications. IEEE Trans. Microw. Theory Tech. 2012, 60, 2532–2542. [Google Scholar] [CrossRef]

- Sun, X.; Gao, H.; Li, G.; Sun, W. Peripheral adaption power cell network for high efficiency and high linearity power amplifier. IEEE Microw. Wirel. Compon. Lett. 2014, 24, 799–801. [Google Scholar] [CrossRef]

- Serhan, A.; Parat, D.; Reynier, P.; Berro, R.; Mourot, R.; De Ranter, C.; Indirayanti, P.; Borremance, M.; Mercier, E.; Giry, A. A broadband high-efficiency SOI-CMOS PA module for LTE/LTE-A handset applications. In Proceedings of the IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Boston, MA, USA, 2–4 June 2019. [Google Scholar]

- Lee, M.; Kim, S.; Hong, S.; Kim, D. Compact 20-W GaN internally matched power amplifier for 2.5 GHz to 6 GHz jammer systems. Micromachines 2020, 11, 375. [Google Scholar] [CrossRef] [PubMed]

- Hu, L.; Liao, X.; Zhang, F.; Wu, H.; Ma, S.; Lin, Q.; Tang, X. A wideband high-efficiency GaN MMIC power amplifier for sub-6-GHz applications. Micromachines 2022, 13, 793. [Google Scholar] [PubMed]

- Li, J.; Zhang, Z.; Zhang, G. Dual-mode linearity enhanced power amplifier with wideband AM-PM compensation for 5–6-GHz FeLAA applications. Electron. Lett. 2022, 58, 188–190. [Google Scholar] [CrossRef]

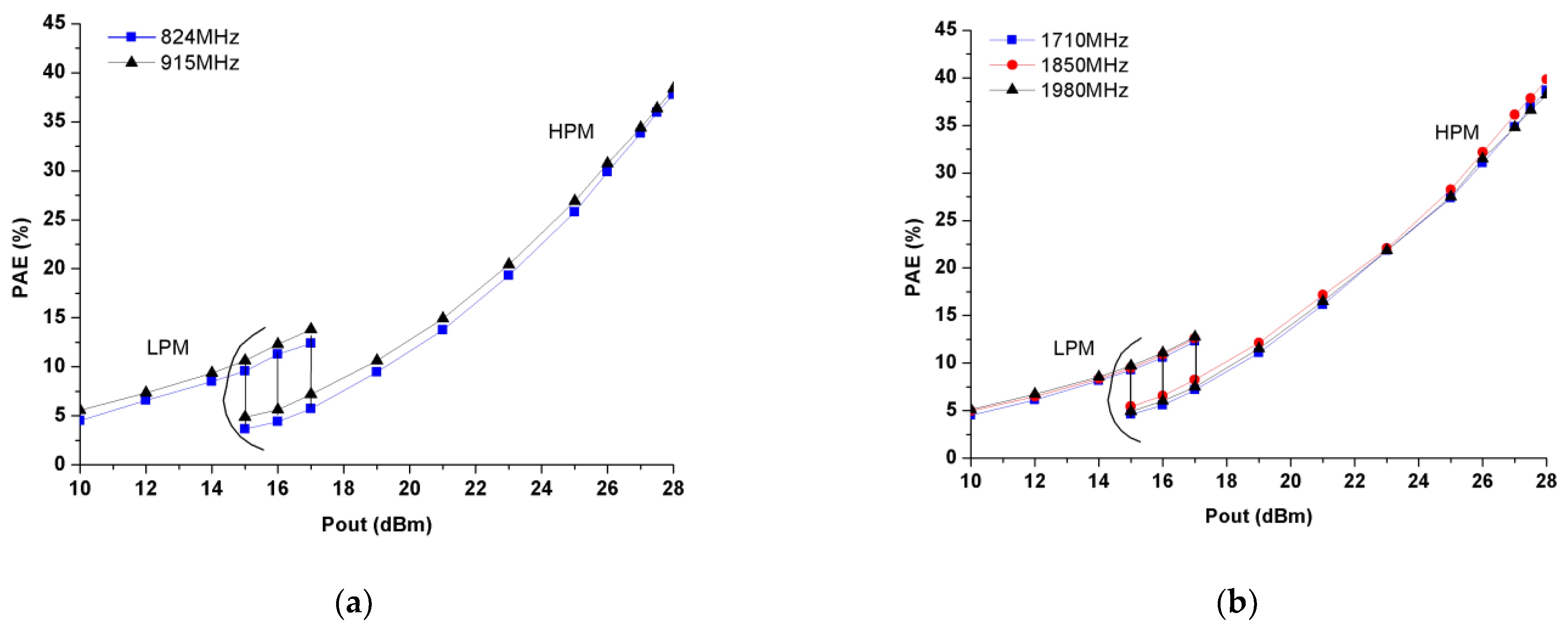

| Band | Freq. (MHz) | Pout (dBm) | Gain (dB) | PAE (%) | OIP3 (dBm) | H2 (dBc) | H3 (dBc) | ACLR-5 1 (dBc) | ACLR-10 2 (dBc) | ACLRE_UTRA 3 (dBc) | ACLRUTRA 4 (dBc) |

|---|---|---|---|---|---|---|---|---|---|---|---|

| LB | 824 | 28 | 27 | 38 | 40.6 | −38.2 | −61 | −39.6 | −52.8 | −34.5 | −35 |

| 17 | 20.4 | 12.4 | 42.7 | −37.2 | −57.4 | −40 | −60.2 | −36.5 | −35.5 | ||

| 915 | 28 | 26.1 | 38.4 | 40.5 | −37.1 | −55.8 | −38.2 | −52 | −34.6 | −34.6 | |

| 17 | 20.9 | 13.8 | 41.8 | −38.8 | −54 | −42.7 | −59.1 | −37 | −35.2 | ||

| HB | 1710 | 28 | 26.4 | 38.7 | 40.5 | −43.3 | −59.2 | −37.5 | −52.3 | −33.5 | −34.4 |

| 17 | 15.9 | 12.3 | 42.2 | −38.7 | −54.5 | −38.3 | −52.2 | −35 | −35 | ||

| 1850 | 28 | 26.7 | 39.9 | 42.8 | −45.6 | −65.4 | −40 | −54.1 | −34.6 | −35.6 | |

| 17 | 17.2 | 12.6 | 43.7 | −42.3 | −51.7 | −40.7 | −54.2 | −36.5 | −36.2 | ||

| 1980 | 28 | 24.3 | 38.2 | 41.4 | −42.2 | −50 | −35.9 | −51.8 | −33.5 | −33.2 | |

| 17 | 17.5 | 12.8 | 41.8 | −39.7 | −51.1 | −36.6 | −54.9 | −34.6 | −34.5 |

| Reference | This Work | [27] | [28] | [29] | [30] | |||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Band | Mode | Freq. (MHz) | 824 | 915 | 824 | 915 | 824 | 915 | 824 | 915 | 824 | 915 | ||||

| LB | HPM | Pout (dBm) | 28 | 28 | 28 | 28 | 28 | 28 | 33 | 33 | 28.2 | 28.2 | ||||

| Gain (dB) | 27 | 26.1 | 28.4 | 28.6 | >26 | >27 | 39.5 | 37 | 28.4 | 28.1 | ||||||

| PAE (%) | 38 | 38.4 | 39 | 40.1 | 40.1–41.1 | >35 | >35 | 43 | 43.2 | |||||||

| LPM | Pout (dBm) | 17 | 17 | 17 | 17 | 16 | 16 | -- | -- | 16 | 16 | |||||

| Gain (dB) | 20.4 | 20.9 | 18.5 | 16.8 | 15 | >17 | -- | -- | >17 | >16 | ||||||

| PAE (%) | 12.4 | 13.8 | 15.8 | 14.8 | >16 | >16 | -- | -- | 14.5 | 14.5 | ||||||

| Freq. (MHz) | 1710 | 1850 | 1980 | 1850 | 1980 | 1710 | 1850 | 1980 | 1710 | 1810 | 1910 | 1710 | 1850 | 1910 | ||

| HB | HPM | Pout (dBm) | 28 | 28 | 28 | 28 | 28 | 28 | 28 | 28 | 30.5 | 30.5 | 30.5 | 27.5 | 28.5 | 28 |

| Gain (dB) | 26.4 | 26.7 | 24.3 | 31.2 | 30.7 | >23.5 | >23.5 | >26 | 35.5 | 35.5 | 35 | 28.2 | 26.6 | 27.8 | ||

| PAE (%) | 38.7 | 39.9 | 38.2 | 34.9 | 35.1 | 40.1–41.1 | >33 | >33 | >33 | 38.5 | 40.7 | 39 | ||||

| LPM | Pout (dBm) | 17 | 17 | 17 | 17.5 | 17.5 | 16 | 16 | 16 | -- | -- | -- | 16 | 16 | 16 | |

| Gain (dB) | 15.9 | 17.2 | 17.5 | 19.1 | 19.1 | >17.5 | >17.5 | >18.5 | -- | -- | -- | >17 | >17 | >17 | ||

| PAE (%) | 12.3 | 12.6 | 12.8 | 15.4 | 15.1 | >24 | >24 | >24 | -- | -- | -- | 14.5 | 14.5 | 14.5 | ||

| Technology | Hybrid CMOS/HBT/SOI | Hybrid CMOS/HBT | HBT | Hybrid CMOS/HBT/SOI | HBT | |||||||||||

| Package | 3D stack MCM | Planar MCM | Planar MCM | Planar MCM | Planar MCM | |||||||||||

| Size (mm2) | 5 × 3.5 | 5 × 5.5 | 5 × 7 | 5 × 5 | 5 × 6 | |||||||||||

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, Z.; Li, J.; Peng, L.; Sun, B. Multi-Band Power Amplifier Module with Back-Off Efficiency Improvement using Ultra-Compact 3D Vertical Stack Multi-Chip Package for Cellular Handsets. Micromachines 2022, 13, 1976. https://doi.org/10.3390/mi13111976

Zhang Z, Li J, Peng L, Sun B. Multi-Band Power Amplifier Module with Back-Off Efficiency Improvement using Ultra-Compact 3D Vertical Stack Multi-Chip Package for Cellular Handsets. Micromachines. 2022; 13(11):1976. https://doi.org/10.3390/mi13111976

Chicago/Turabian StyleZhang, Zhihao, Jing Li, Lin Peng, and Bo Sun. 2022. "Multi-Band Power Amplifier Module with Back-Off Efficiency Improvement using Ultra-Compact 3D Vertical Stack Multi-Chip Package for Cellular Handsets" Micromachines 13, no. 11: 1976. https://doi.org/10.3390/mi13111976

APA StyleZhang, Z., Li, J., Peng, L., & Sun, B. (2022). Multi-Band Power Amplifier Module with Back-Off Efficiency Improvement using Ultra-Compact 3D Vertical Stack Multi-Chip Package for Cellular Handsets. Micromachines, 13(11), 1976. https://doi.org/10.3390/mi13111976