Power Reduction in Punch-Through Current-Based Electro-Thermal Annealing in Gate-All-Around FETs

Abstract

:1. Introduction

2. Materials and Methods

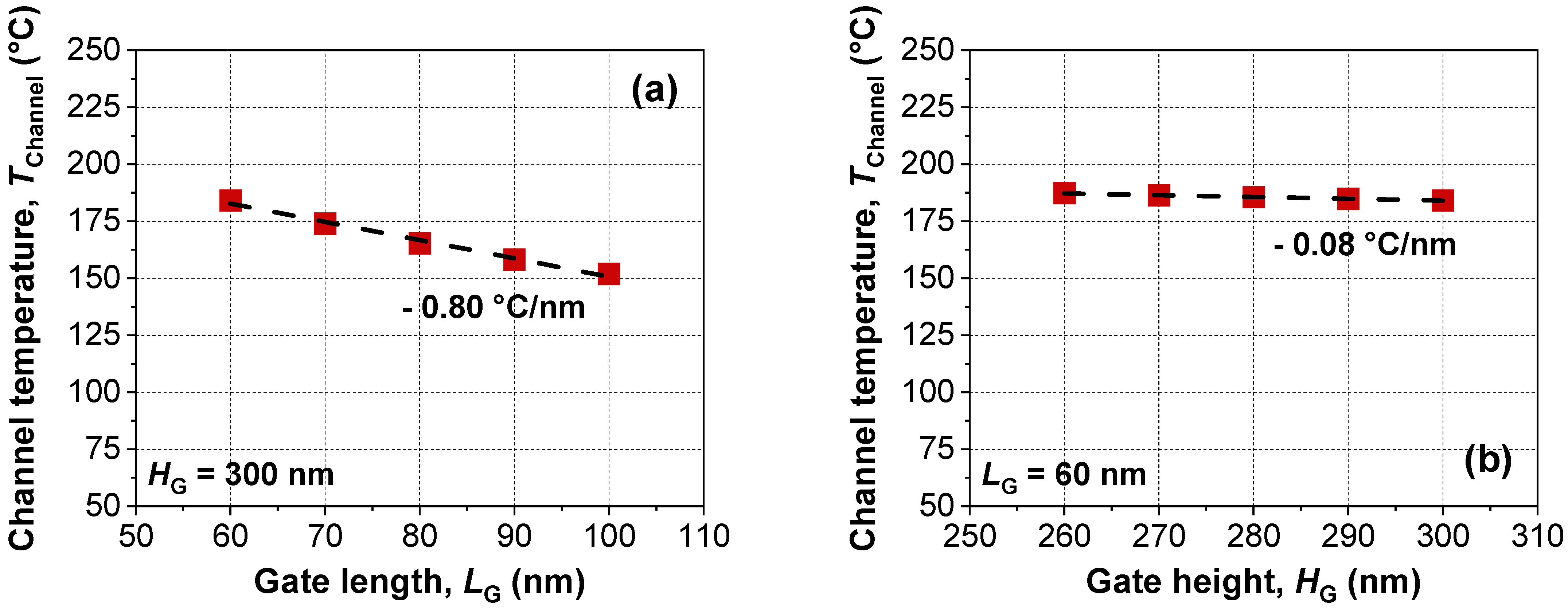

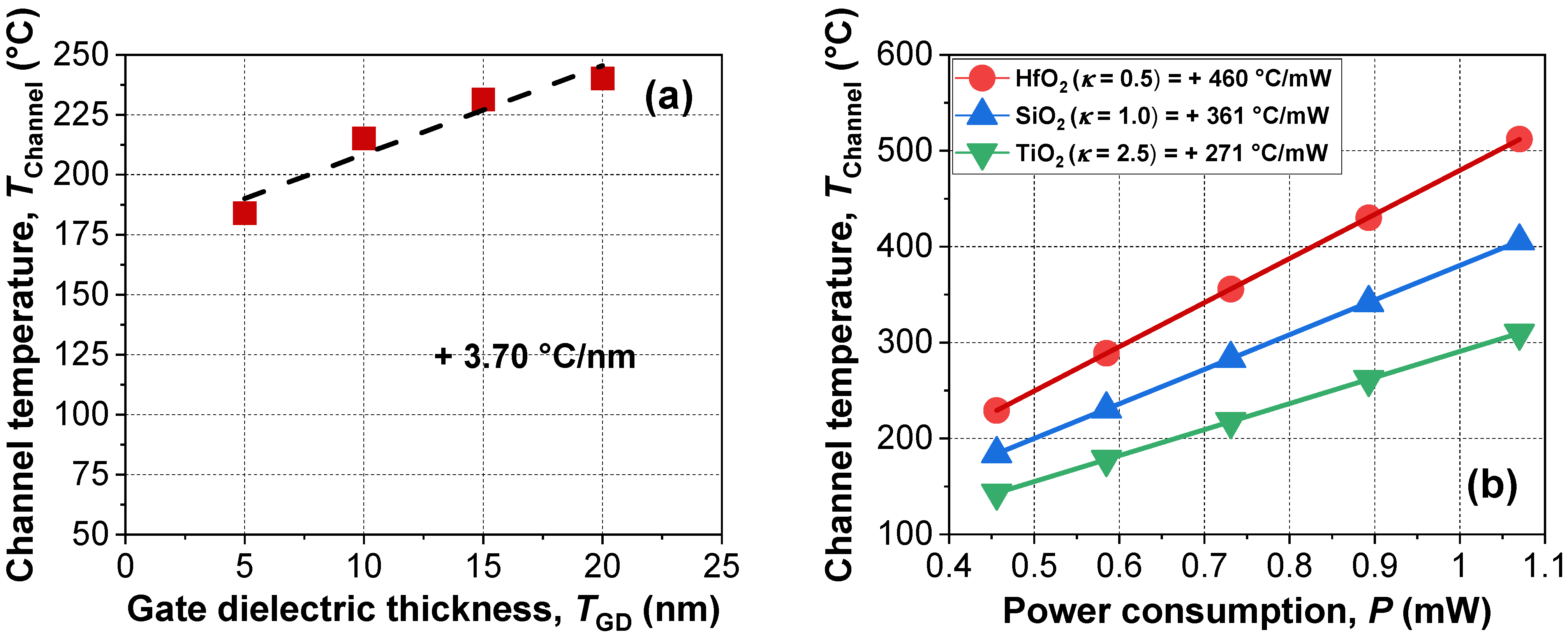

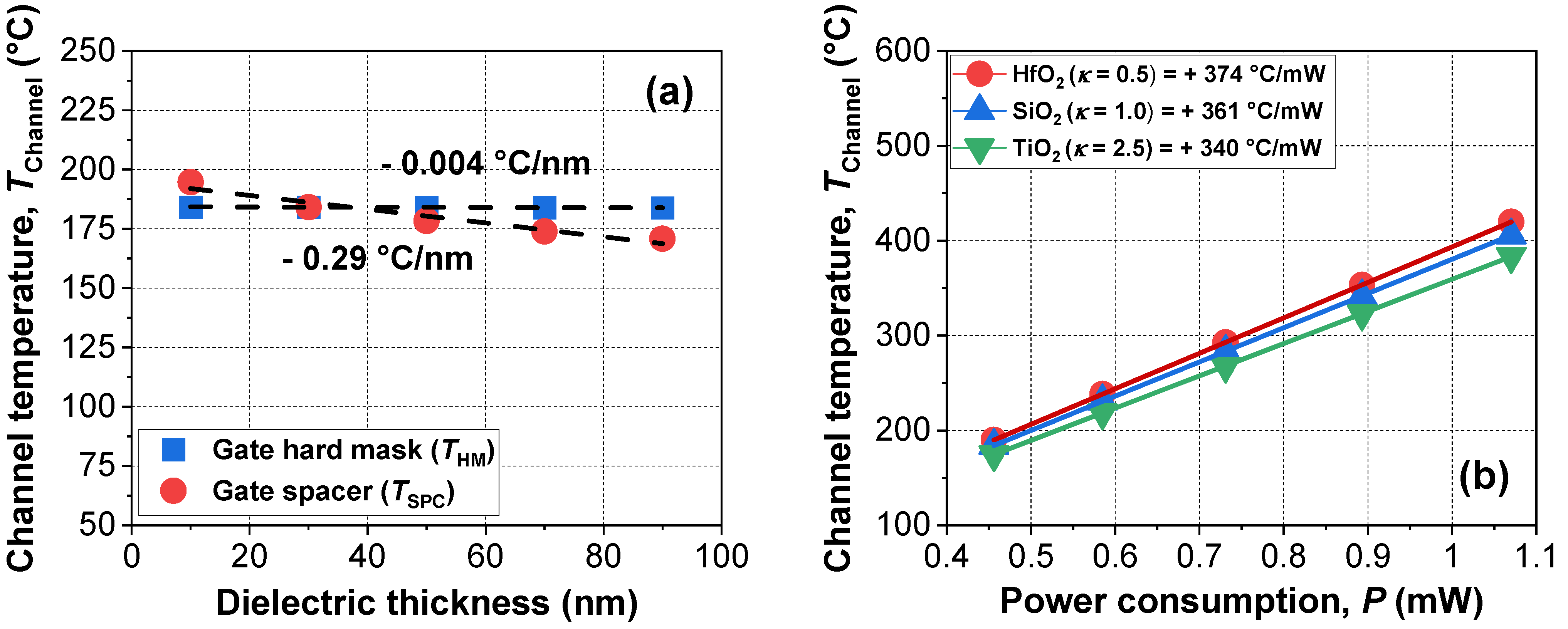

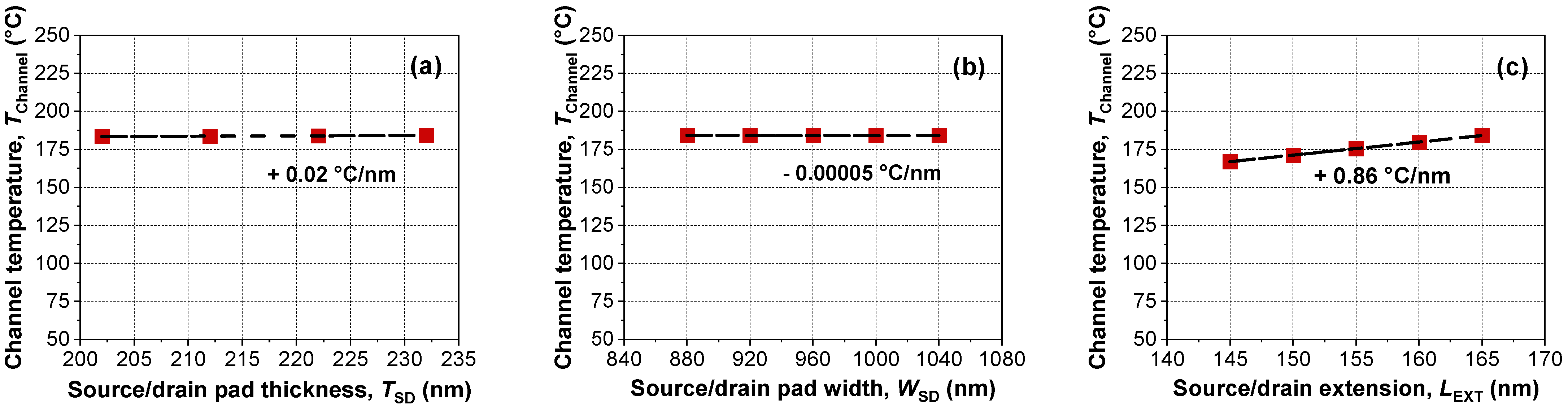

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Moroz, V.; Huang, J.; Arghavani, R. Transistor Design for 5 nm and Beyond: Slowing Down Electrons to Speed Up Transistors. In Proceedings of the 17th International Symposium on Quality Electronic Design (ISQED), Santa Clara, CA, USA, 15–16 March 2016; pp. 278–283. [Google Scholar] [CrossRef]

- Ciou, F.-M.; Lin, J.-H.; Chen, P.-H.; Chang, T.-C.; Chang, K.-C.; Hsu, J.-T.; Lin, Y.-S.; Jin, F.-Y.; Hung, W.-C.; Yeh, C.-H.; et al. Comparison of the Hot Carrier Degradation of N- and P-Type Fin Field-Effect Transistors in 14-nm Technology Nodes. IEEE Electron Device Lett. 2021, 42, 1420–1423. [Google Scholar] [CrossRef]

- Lee, K.; Kaczer, B.; Kruv, A.; Gonzalez, M.; Degraeve, R.; Tyaginov, S.; Grill, A.; Wolf, I.D. Hot-Electron-Induced Punch-Through (HEIP) Effect in p-MOSFET Enhanced by Mechanical Stress. IEEE Electron Device Lett. 2021, 42, 1424–1427. [Google Scholar] [CrossRef]

- Hu, C.; Simon, C.T.; Hsu, F.-C.; Ko, P.-K.; Chan, T.-Y.; Terrill, K.W. Hot-Electron-Induced MOSFET Degradation-Model, Monitor, and Improvement. IEEE J. Solid State Circuit 1985, 20, 295–305. [Google Scholar] [CrossRef]

- Takeda, E.; Suzuki, N. An Empirical Model for Device Degradation Due to Hot-Carrier Injection. IEEE Electron Dev. Lett. 1983, 4, 111–113. [Google Scholar] [CrossRef]

- Onishi, K.; Kang, C.S.; Choi, R.; Cho, H.-J.; Gopalan, S.; Nieh, R.E.; Krishnan, S.A.; Lee, J.C. Improvement of Surface Carrier Mobility of Hfo2 Mosfets By High-Temperature Forming Gas Annealing. IEEE Trans. Electron Devices 2003, 50, 384–390. [Google Scholar] [CrossRef]

- Jo, M.; Chang, M.; Park, H.; Hwang, H. Improvement of Hafnium Oxide/Silicon Oxide Gate Dielectric Stack Quality by High Pressure D2O Post Deposition Annealing. Jpn. J. Appl. Phys. 2007, 46, L531–L533. [Google Scholar] [CrossRef]

- Park, J.-Y.; Moon, D.-I.; Lee, G.-B.; Choi, Y.-K. Curing of Aged Gate Dielectric by the Self-Heating Effect in MOSFETs. IEEE Trans. Electron Devices 2020, 67, 777–788. [Google Scholar] [CrossRef]

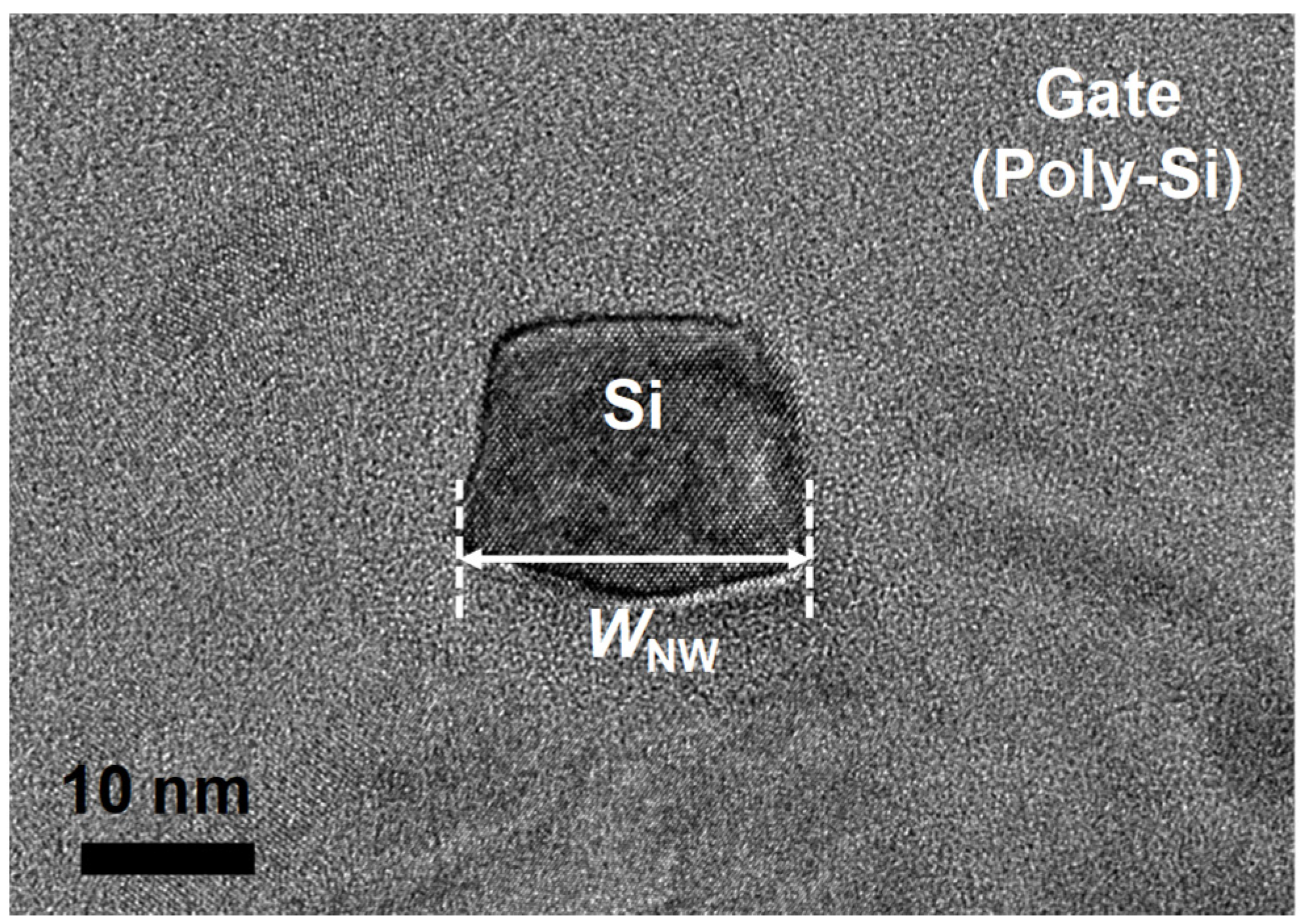

- Moon, D.-I.; Choi, S.-J.; Kim, C.-J.; Kim, J.-Y.; Lee, J.-S.; Oh, J.-S.; Lee, G.-S.; Park, Y.-C.; Hong, D.-W.; Lee, D.-W.; et al. Silicon Nanowire All-Around Gate Mosfets Built on a Bulk Substrate by All Plasma-Etching Routes. IEEE Electron Device Lett. 2011, 32, 452–454. [Google Scholar] [CrossRef]

- Park, J.-Y.; Hur, J.; Choi, Y.-K. Demonstration of a Curable Nanowire FinFET Using Punchthrough Current to Repair Hot-Carrier Damage. IEEE Electron Dev. Lett. 2018, 39, 180–183. [Google Scholar] [CrossRef]

- Lee, G.-B.; Kim, C.-K.; Park, J.-Y.; Bang, T.; Bae, H.; Kim, S.-Y.; Ryu, S.-W.; Choi, Y.-K. A Novel Technique for Curing Hot-Carrier-Induced Damage by Utilizing the Forward Current of the PN-Junction in a MOSFET. IEEE Electron Dev. Lett. 2017, 38, 1012–1014. [Google Scholar] [CrossRef]

- Moon, D.-I.; Park, J.-Y.; Han, J.-W.; Jeon, G.-J.; Kim, J.-Y.; Moon, J.-B.; Seol, M.-L.; Kim, C.-K.; Lee, H.C.; Meyyappan, M.; et al. Sustainable Electronics for Nano-Spacecraft in Deep Space Missions. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 3–7. [Google Scholar] [CrossRef]

- Jeon, C.-H.; Park, J.-Y.; Seol, M.-L.; Moon, D.-I.; Hur, J.; Bae, H.; Jeon, S.-B.; Choi, Y.-K. Joule Heating to Enhance the Performance of a Gate-All-Around Silicon Nanowire Transistor. IEEE Trans. Electron Devices 2016, 63, 2288–2292. [Google Scholar] [CrossRef]

- Pop, E.; Sinha, S.; Goodson, K.E. Heat Generation and Transport in Nanometer-Scale Transistors. Proc. IEEE 2006, 94, 1587–1601. [Google Scholar] [CrossRef]

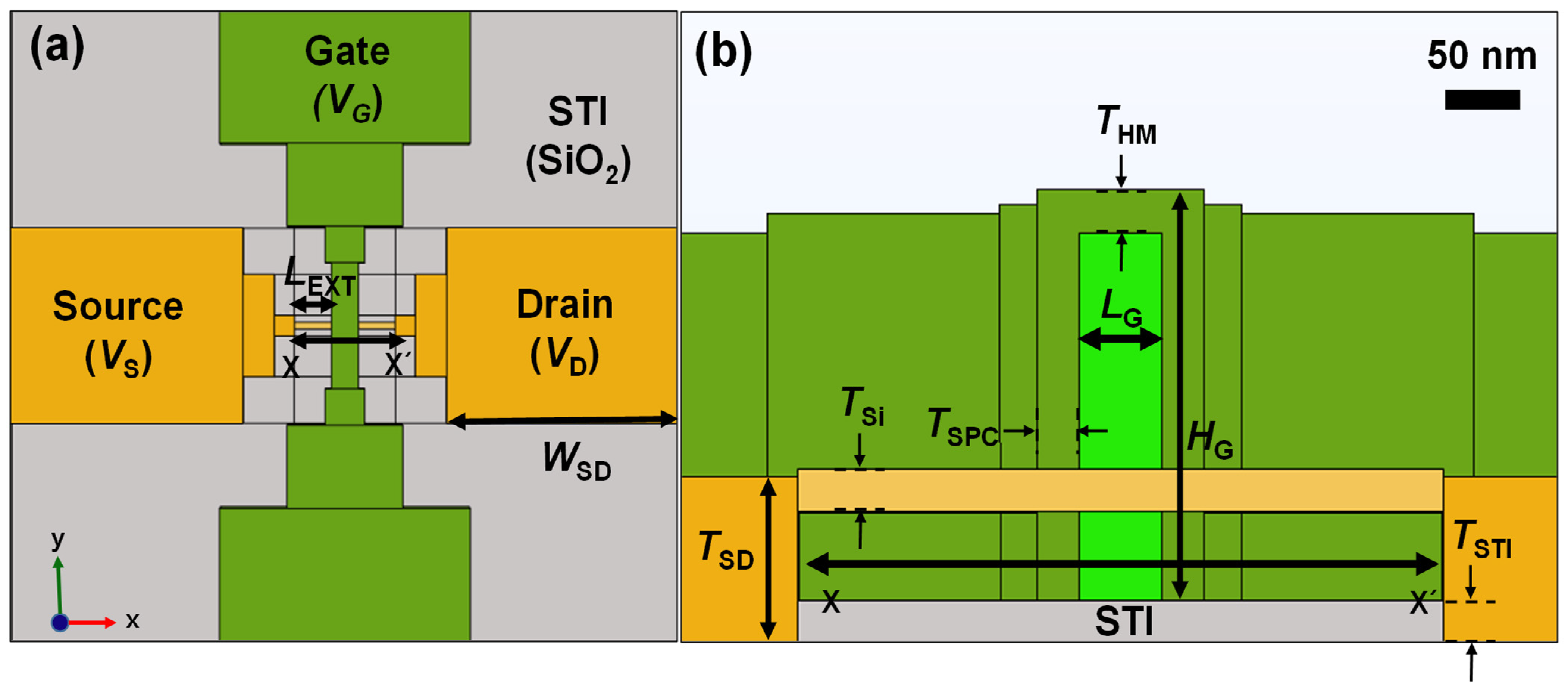

| Geometry | Dimension | Material | Thermal Conductivity [W/m∙K] |

|---|---|---|---|

| Gate length, LG [nm] | 60 | Poly-Si | 31.2 |

| Gate height, HG [nm] | 300 | ||

| Gate hard mask thickness, THM [nm] | 30 | SiO2 | 1 |

| Gate spacer thickness, TSPC [nm] | 30 | ||

| Gate dielectric thickness, TGD [nm] | 5 | ||

| STI thickness, TSTI [nm] | 70 | ||

| Source/drain pad thickness, TSD [nm] | 232 | Si | 149 |

| Source/drain pad width, WSD [nm] | 1040 | ||

| Channel thickness, TSi [nm] | 20 | ||

| Channel width, WNW [nm] | 20 | ||

| Source/drain extension length, LEXT [nm] | 165 |

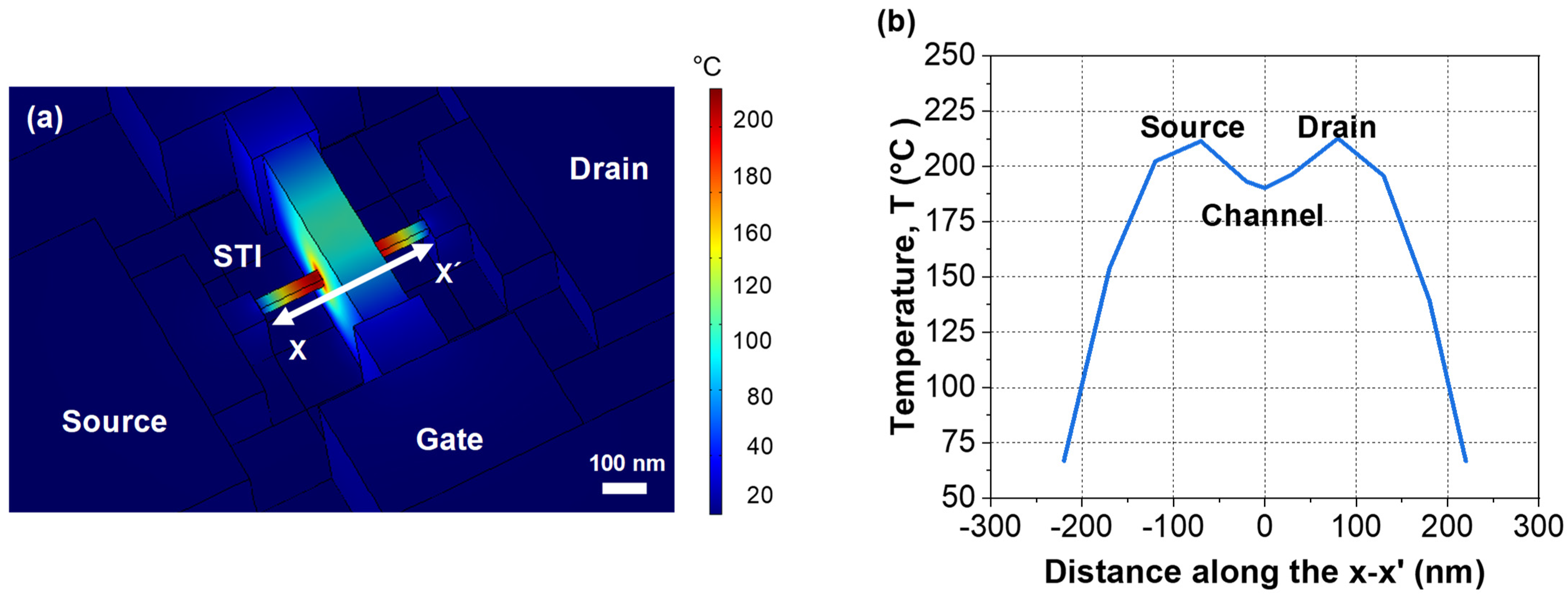

| Bias Condition | |

|---|---|

| Gate voltage (VG) | 0.5 V |

| Source voltage (VS) | 0 V |

| Drain voltage (VD) | 6 V |

| Punch-through current (IPunch) | 75 μA |

| Power consumption, (P = VD × IPunch) | 0.45 mW |

| Annealing time (t) | 100 μs |

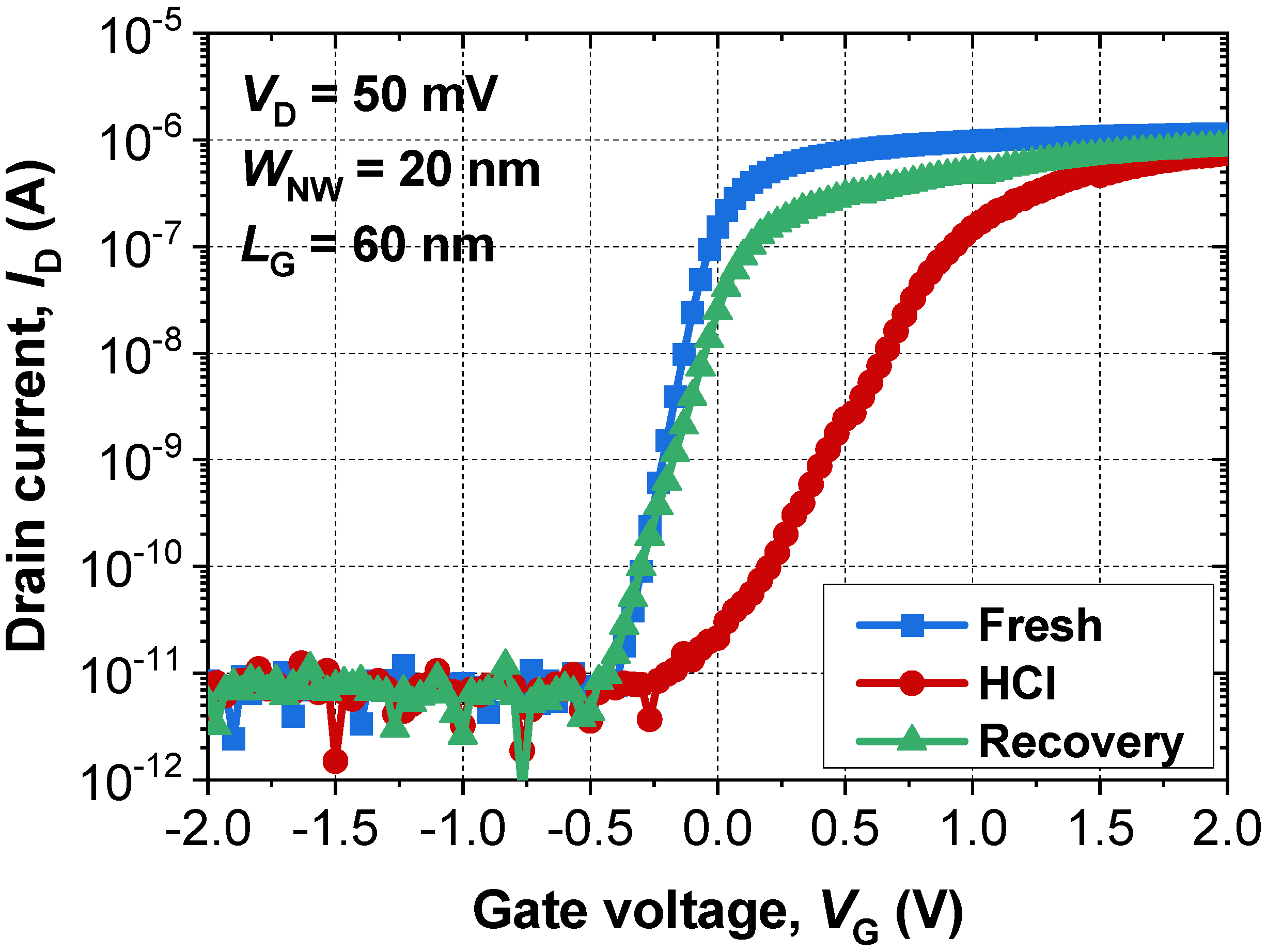

| Initial State (Before HCI) | After HCI | After Punch-Through ETA | |

|---|---|---|---|

| SS (mV/dec) | 82 mV/dec | 227 mV/dec | 124 mV/dec |

| VT (V) | −0.13 V | 0.65 V | −0.05 V |

| Gate Module | S/D Module | Isolation | |

|---|---|---|---|

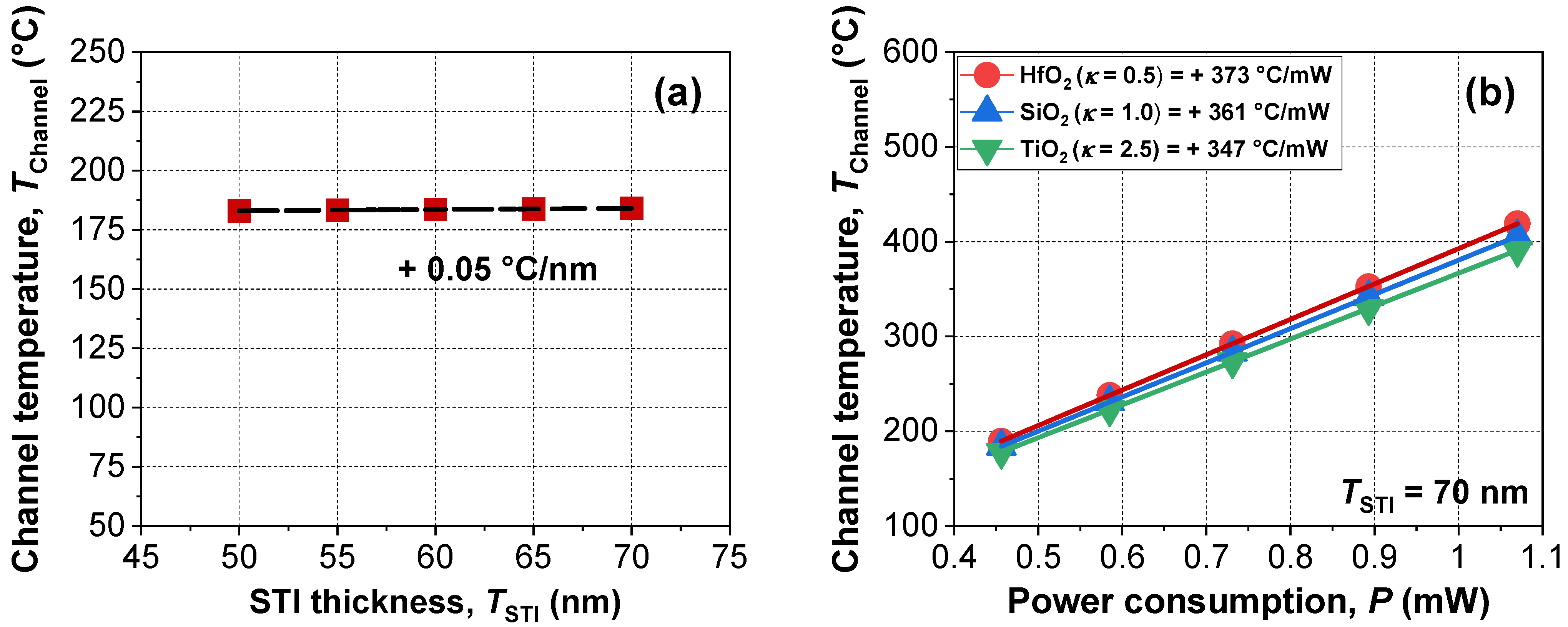

| Minimum (°C/nm) | −0.80 | 0.00 | +0.05 |

| Maximum (°C/nm) | +3.70 | +0.86 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, M.-K.; Choi, Y.-K.; Park, J.-Y. Power Reduction in Punch-Through Current-Based Electro-Thermal Annealing in Gate-All-Around FETs. Micromachines 2022, 13, 124. https://doi.org/10.3390/mi13010124

Kim M-K, Choi Y-K, Park J-Y. Power Reduction in Punch-Through Current-Based Electro-Thermal Annealing in Gate-All-Around FETs. Micromachines. 2022; 13(1):124. https://doi.org/10.3390/mi13010124

Chicago/Turabian StyleKim, Min-Kyeong, Yang-Kyu Choi, and Jun-Young Park. 2022. "Power Reduction in Punch-Through Current-Based Electro-Thermal Annealing in Gate-All-Around FETs" Micromachines 13, no. 1: 124. https://doi.org/10.3390/mi13010124

APA StyleKim, M.-K., Choi, Y.-K., & Park, J.-Y. (2022). Power Reduction in Punch-Through Current-Based Electro-Thermal Annealing in Gate-All-Around FETs. Micromachines, 13(1), 124. https://doi.org/10.3390/mi13010124