A 1T2C FeCAP-Based In-Situ Bitwise X(N)OR Logic Operation with Two-Step Write-Back Circuit for Accelerating Compute-In-Memory

Abstract

1. Introduction

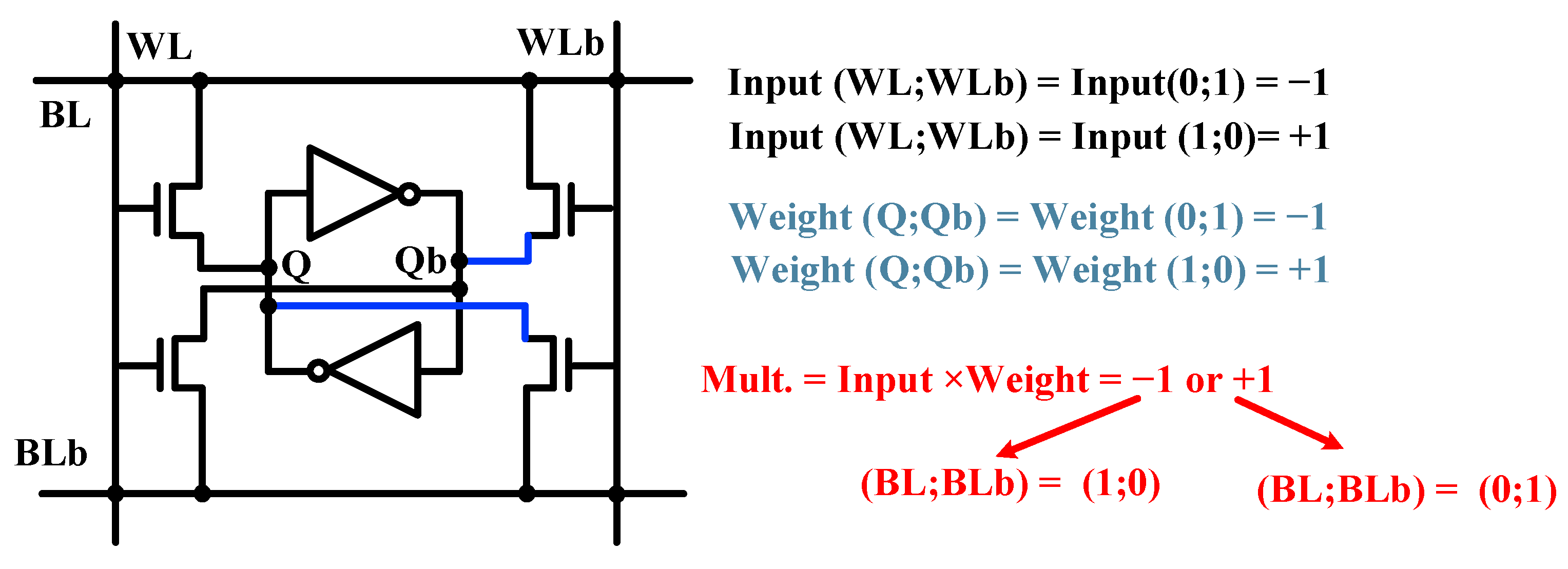

2. Previous Related Studies

3. Proposed 1T2C FeCAP-Based X(N)OR Logic Operation

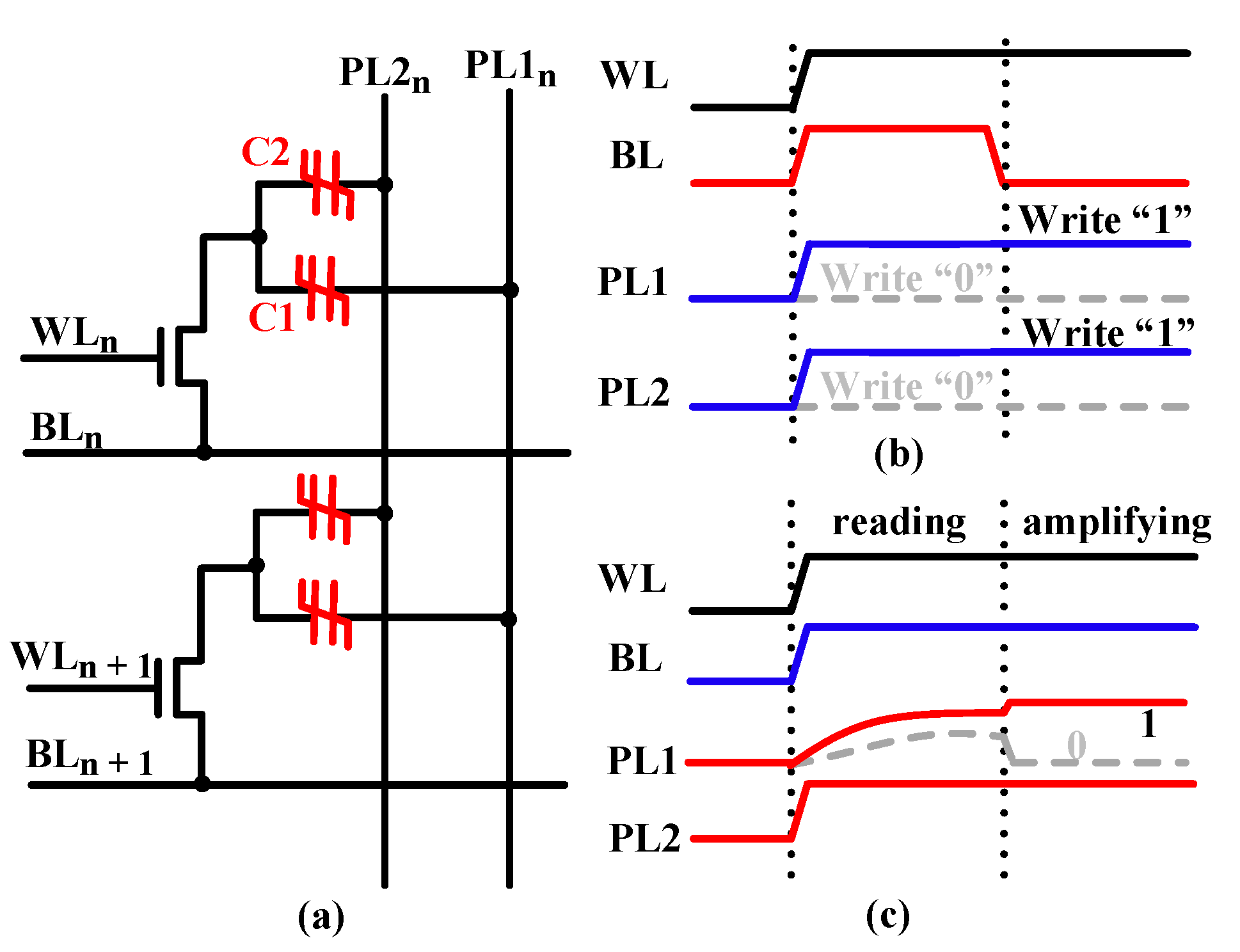

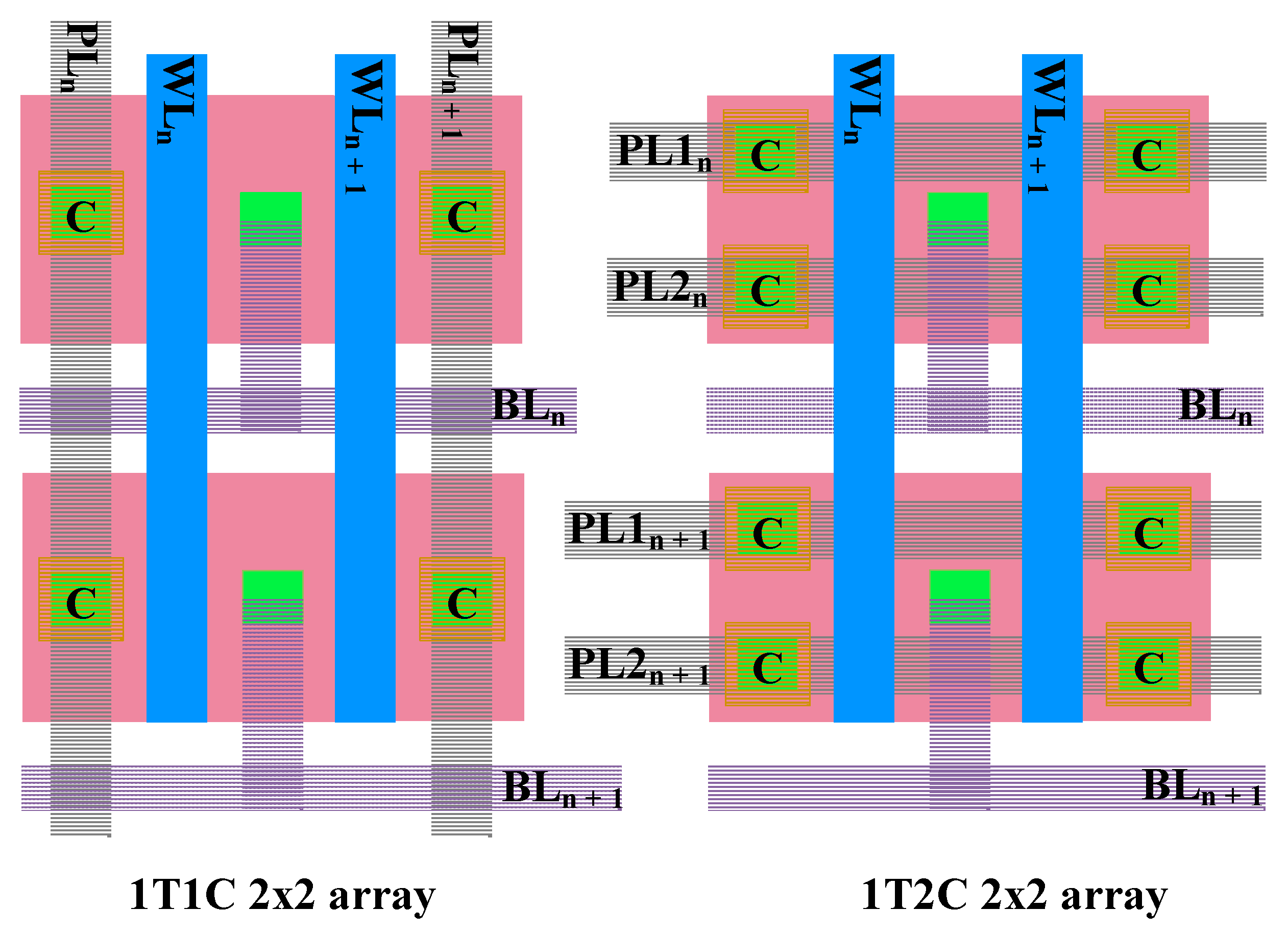

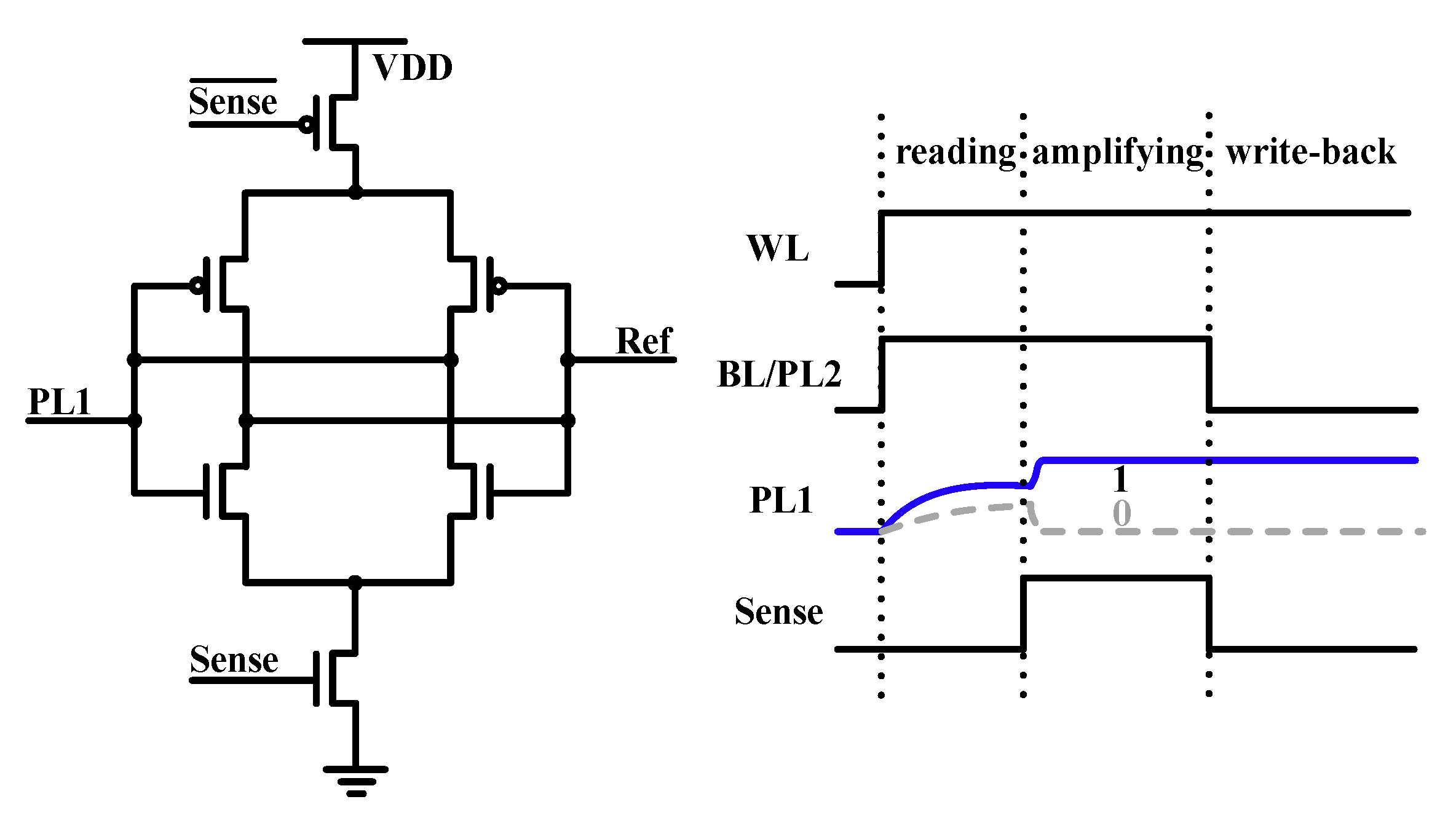

3.1. Operation of the Proposed 1T2C Cell

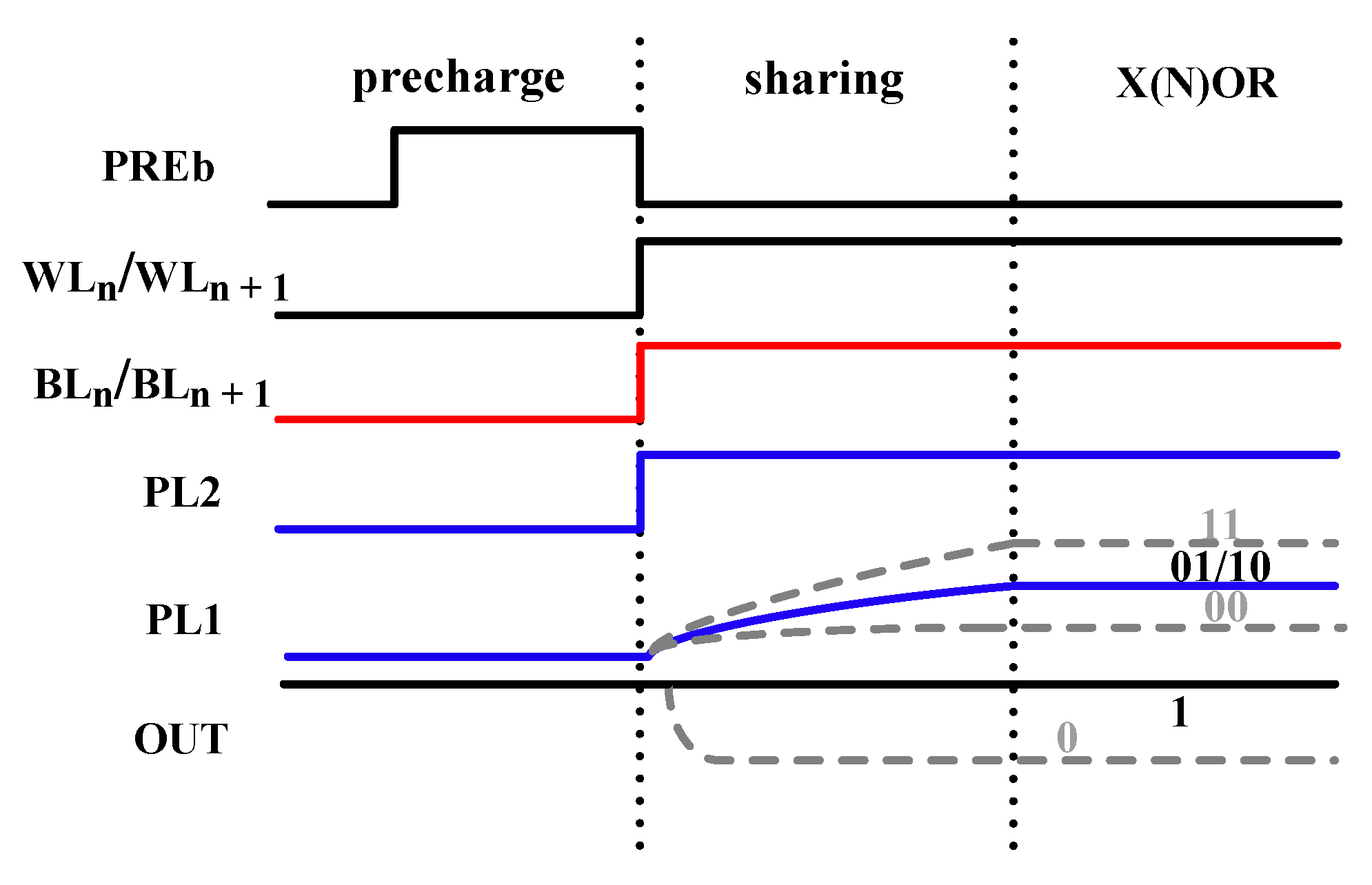

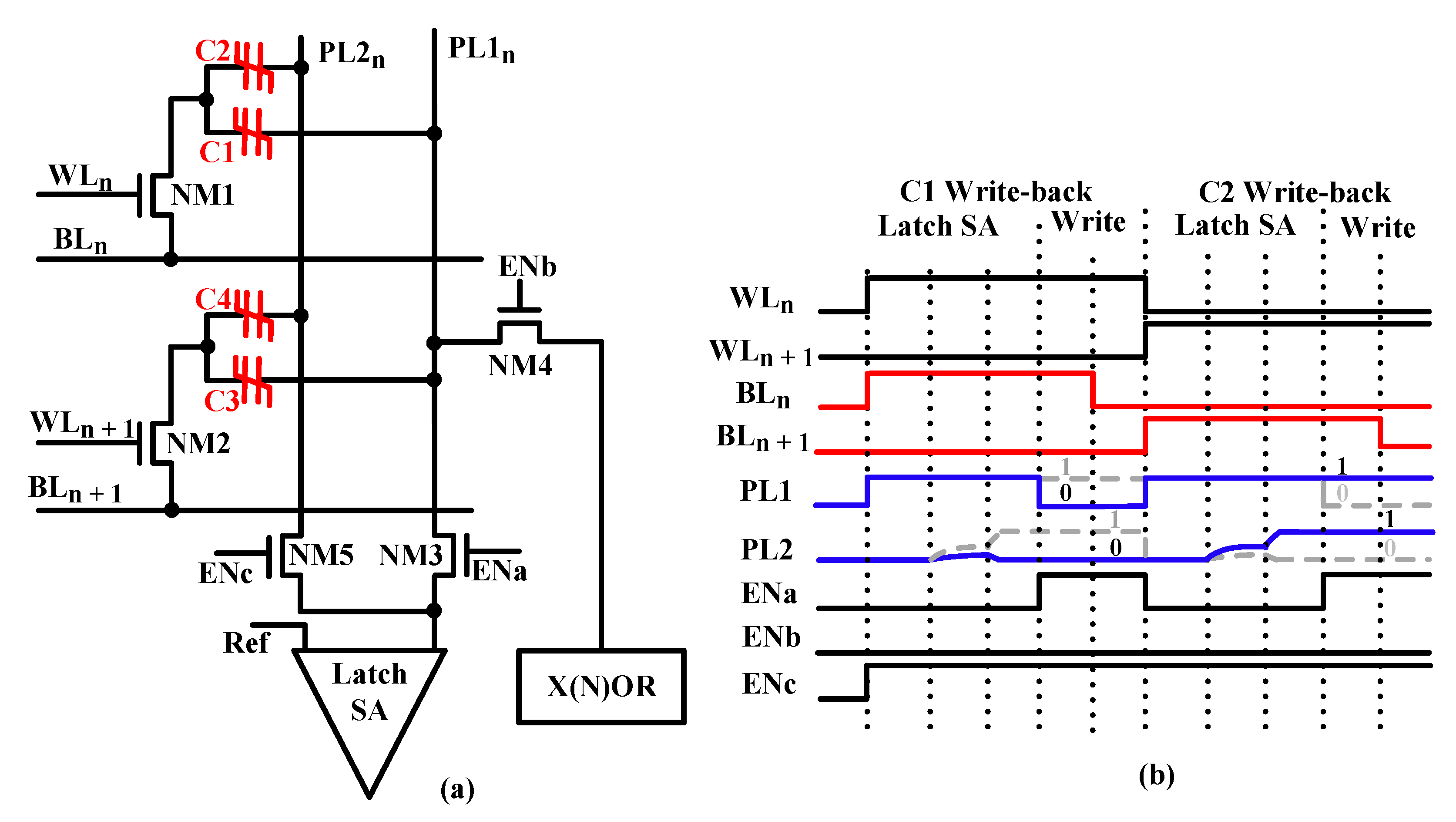

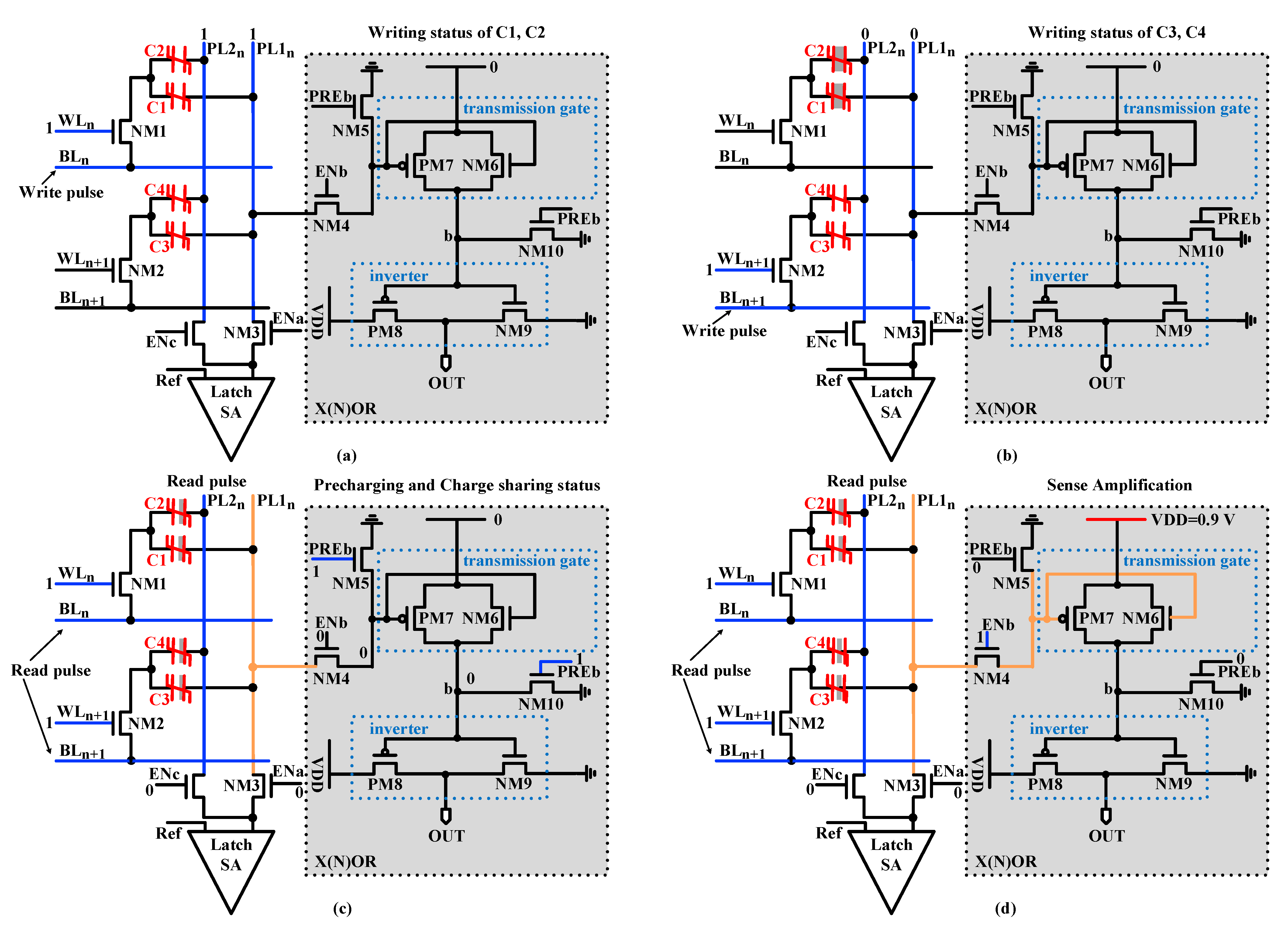

3.2. Dual-Row In-Memory X(N)OR Operation

3.3. Two-Step Write-Back Circuit

4. Verification Results and Discussion

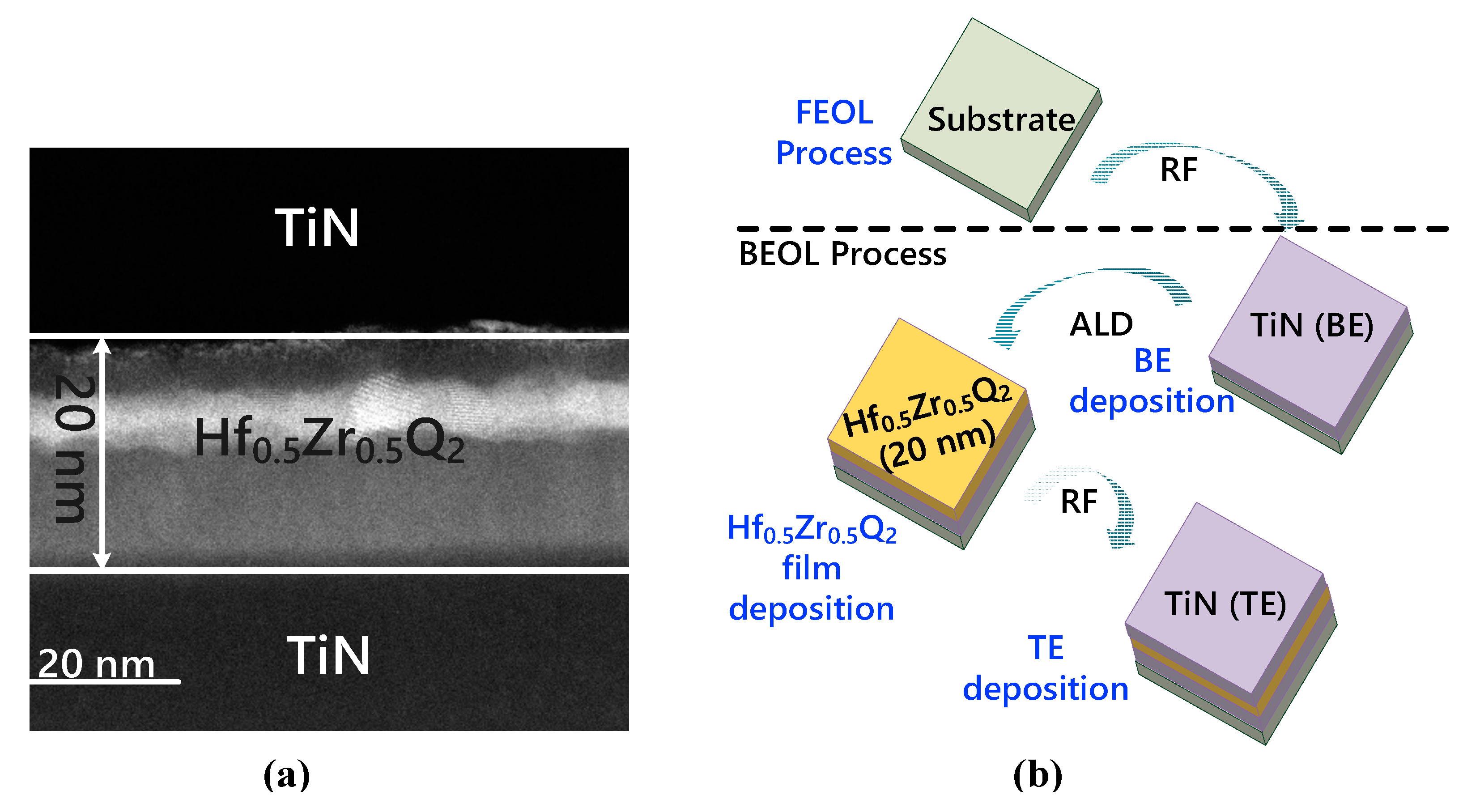

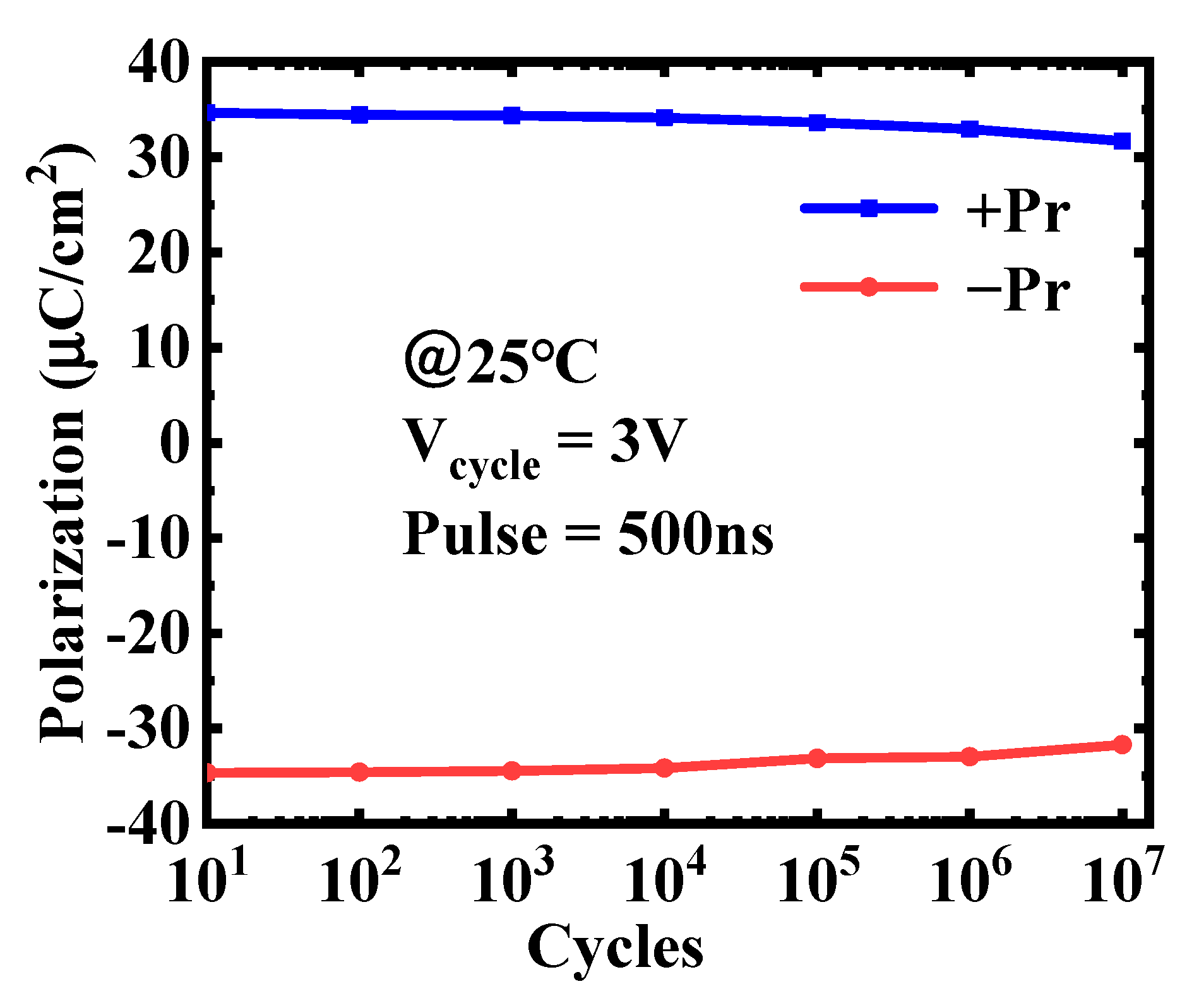

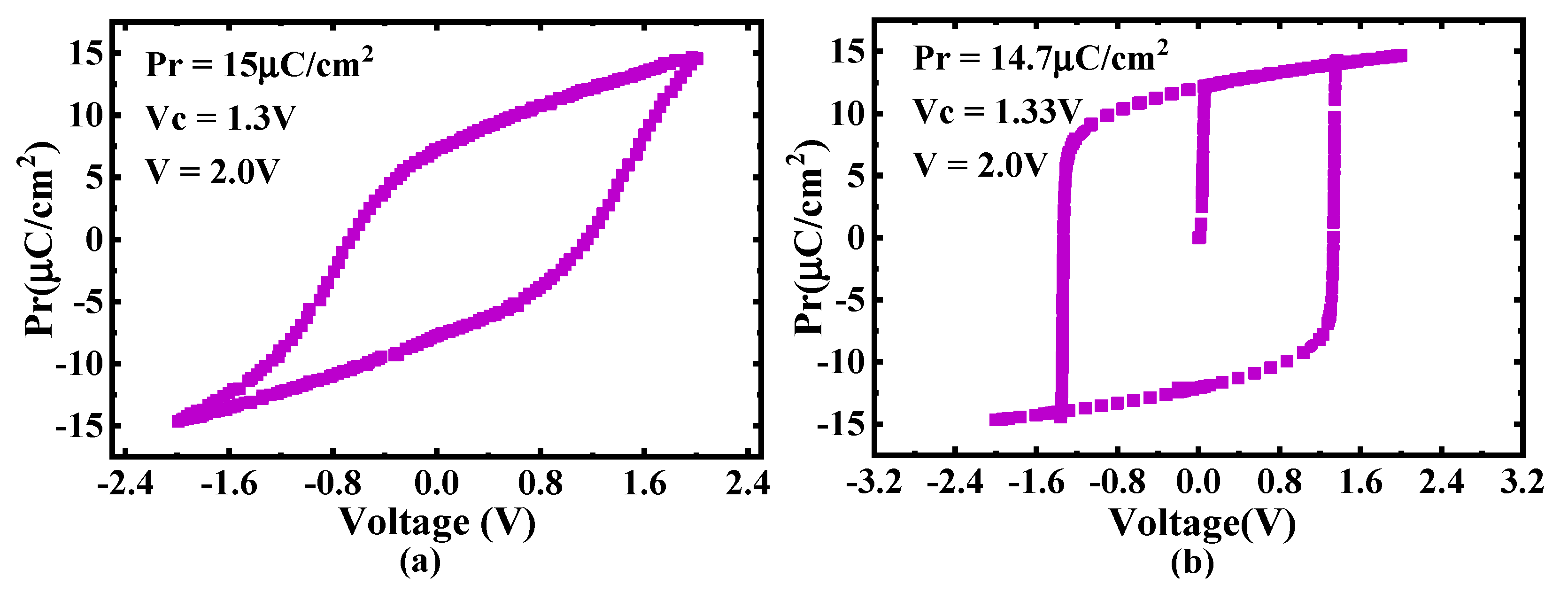

4.1. Device Fabrication, Performance, and Simulation Model

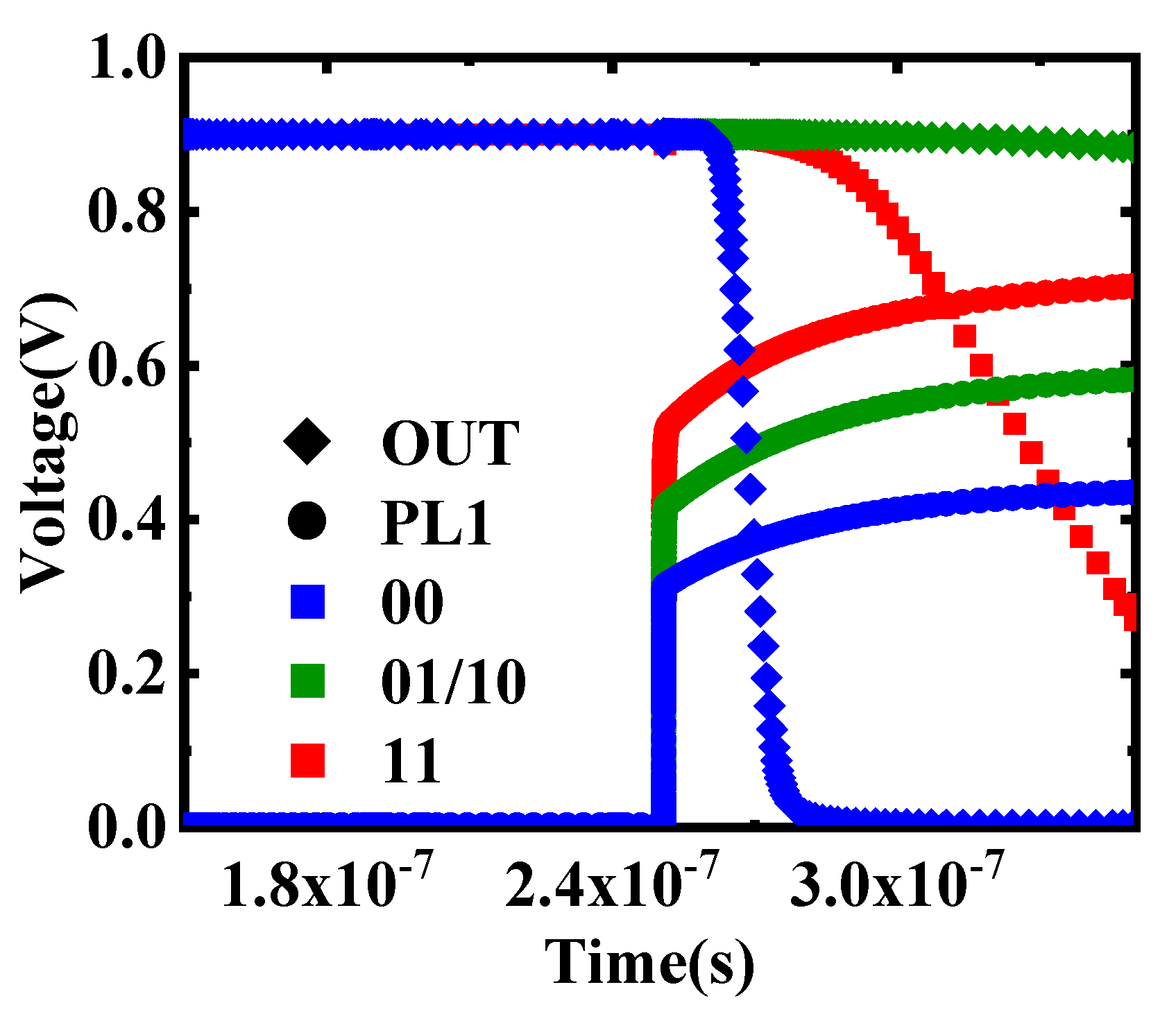

4.2. X(N)OR Logic Operation Simulation Results

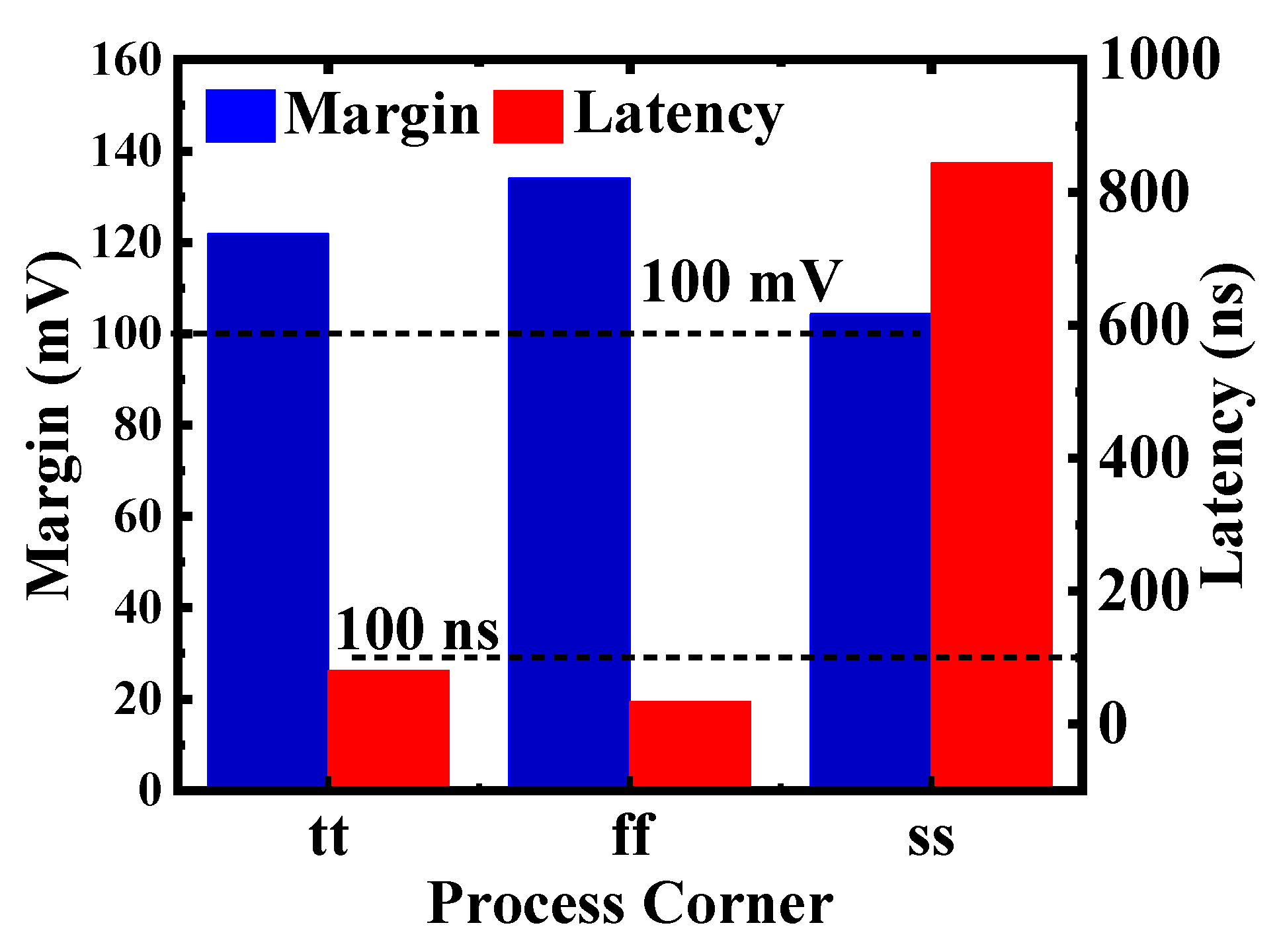

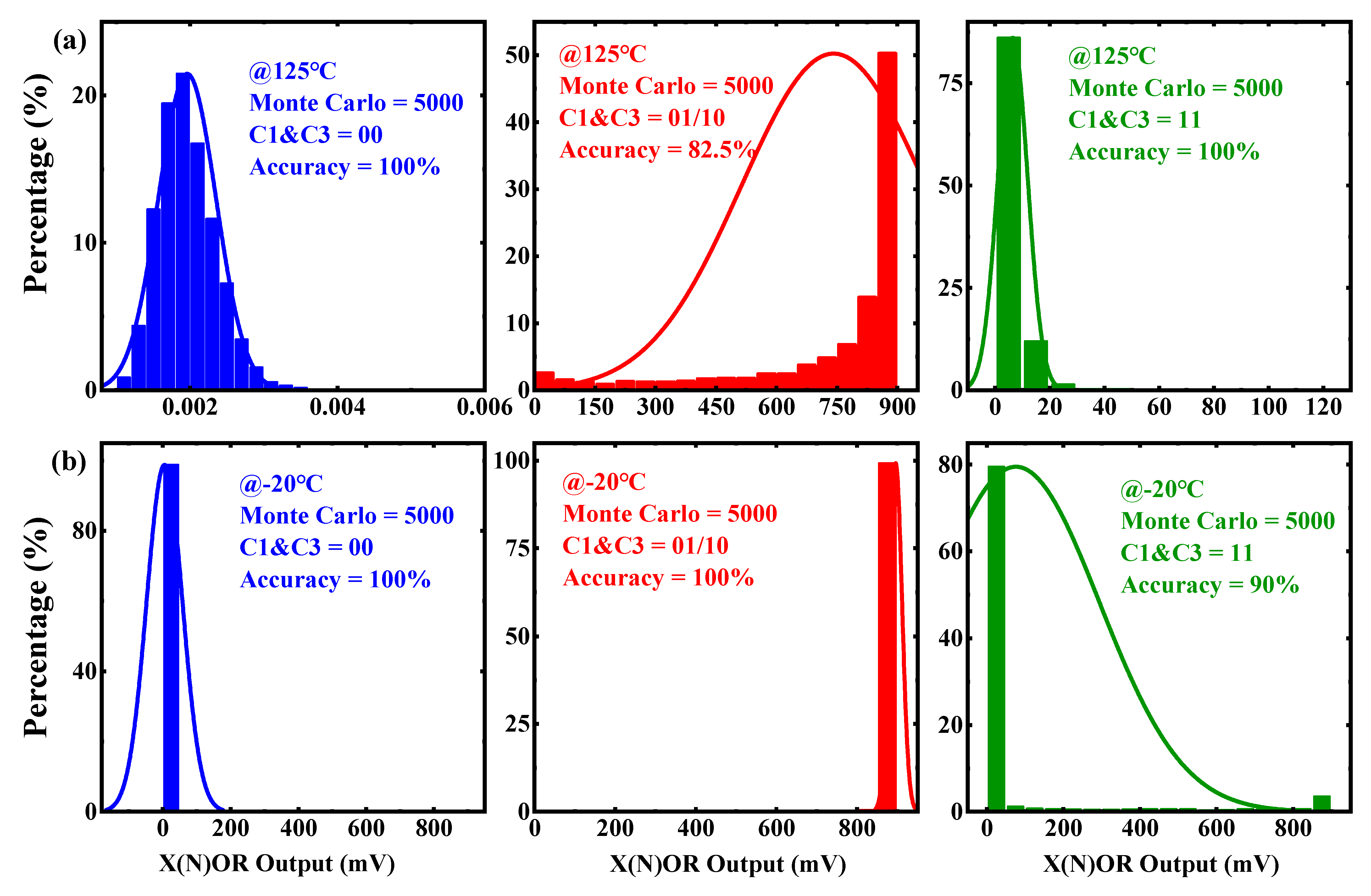

4.3. Reliability of In-Memory X(N)OR Logic Operation

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Chi, P.; Li, S.C.; Xu, C.; Zhang, T.; Zhao, J.; Liu, Y.P.; Wang, Y.; Xie, Y. PRIME: A Novel Processing-in-Memory Architecture for Neural Network Computation in ReRAM-Based Main Memory. In Proceedings of the ACM/IEEE 43rd Annual International Symposium on Computer Architecture (ISCA), Seoul, Korea, 18–22 June 2016; pp. 27–39. [Google Scholar]

- Yang, J.J.; Strukov, D.B.; Stewart, D.R. Memristive Devices for Computing. Nat. Nanotechnol. 2013, 8, 13–24. [Google Scholar] [CrossRef] [PubMed]

- Waldrop, M.M. The chips are down for Moore’s law. Nat. News 2016, 530, 145–147. [Google Scholar] [CrossRef] [PubMed]

- Horowitz, M. Computing’s energy problem (and what we can do about it). In Proceedings of the 2014 IEEE International Solid- State Circuits Conference (ISSCC), San Francisco, CA, USA, 9–13 February 2014; Volume 57, pp. 10–14. [Google Scholar]

- Xia, Q.; Yang, J.J. Memristive crossbar arrays for brain-inspired computing. Nat. Mater. 2019, 18, 309–323. [Google Scholar] [PubMed]

- Indiveri, G.; Liu, S.C. Optimizing Weight Mapping and Data Flow for Convolutional Neural Networks on RRAM Based Processing-In-Memory Architecture. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, 26–29 May 2015; pp. 1–5. [Google Scholar]

- Angizi, S.; He, Z.Z.; Parveen, F.; Fan, D.L. RIMPA: A new reconfigurable dual-mode in-memory processing architecture with spin hall effect-driven domain wall motion device. In Proceedings of the IEEE Computer Society Annual Symposium on VLSI (ISVLSI), Bochum, Germany, 3–5 July 2017; pp. 45–50. [Google Scholar]

- Dai, G.; Huang, T.H.; Chi, Y.Z.; Zhao, J.S.; Sun, G.Y.; Liu, Y.P.; Wang, Y.; Xie, Y.; Yang, H.Z. Graphh: A processing-in-memory architecture for largescale graph processing. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2019, 38, 640–653. [Google Scholar] [CrossRef]

- Gauchi, R.; Kooli, M.; Vivet, P.; Noel, J.-P.; Beigné, E.; Mitra, S.; Charles, H.-P. Memory Sizing of a Scalable SRAM In-Memory Computing Tile Based Architecture. In Proceedings of the International Conference on Very Large Scale Integration (VLSI-SoC), Cuzco, Peru, 6–9 October 2019; pp. 166–171. [Google Scholar]

- Zhu, Q.L.; Akin, B.; Sumbul, H.E.; Sadi, F.; Hoe, J.C.; Pileggi, L.; Franchetti, F. A 3D-stacked logic-in-memory accelerator for application-specific data intensive computing. In Proceedings of the IEEE International 3D Systems Integration Conference (3DIC), San Francisco, CA, USA, 2–4 October 2013; pp. 1–7. [Google Scholar]

- Ma, Y.; Zheng, L.F.; Zhou, P.Q. CoDRAM: A Novel Near Memory Computing Framework with Computational DRAM. In Proceedings of the IEEE International Conference on ASIC (ASICON), Chongqing, China, 29 October–1 November 2019; pp. 1–4. [Google Scholar]

- Yang, Z.; Wei, L. Logic Circuit and Memory Design for In-Memory Computing Applications using Bipolar RRAMs. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, 26–29 May 2019; pp. 1–5. [Google Scholar]

- Hsu, P.K.; Du, P.Y.; Lo, C.R.; Lue, H.T.; Chen, W.C.; Hsu, T.H.; Yeh, T.H.; Hsieh, C.C.; Wei, M.L.; Wang, K.C.; et al. An Approach of 3D NAND Flash Based Nonvolatile Computing-In-Memory (nvCIM) Accelerator for Deep Neural Networks (DNNs) with Calibration and Read Disturb Analysis. In Proceedings of the IEEE International Memory Workshop (IMW), Dresden, Germany, 17–20 May 2020; pp. 1–4. [Google Scholar]

- Marotta, G.G.; Macerola, A.; D’Alessandro, A.; Torsi, A.; Cerafogli, C.; Lattaro, C.; Musilli, C.; Rivers, D.; Sirizotti, E.; Paolini, F.; et al. A 3bit/cell 32Gb NAND flash memory at 34nm with 6MB/s program throughput and with dynamic 2b/cell blocks configuration mode for a program throughput increase up to 13MB/s. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 7–11 February 2010; pp. 444–445. [Google Scholar]

- Naso, G.; Botticchio, L.; Castelli, M.; Cerafogli, C.; Cichocki, M.; Conenna, P.; D’Alessandro, A.; Santis, L.D.; Cicco, D.D.; Francesco, W.D.; et al. A 128Gb 3b/cell NAND flash design using 20 nm planar-cell technology. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 17–21 February 2013; pp. 218–219. [Google Scholar]

- Kim, H.; Oh, H.; Kim, J.J. Energy-efficient XNOR-free In-Memory BNN Accelerator with Input Distribution Regularization. In Proceedings of the IEEE/ACM International Conference on Computer Aided Design (ICCAD), San Diego, CA, USA, 2–5 November 2020; pp. 1–9. [Google Scholar]

- Vetter, J.S.; Mittal, S. Opportunities for Nonvolatile Memory Systems in Extreme-Scale High-Performance Computing. Comput. Sci. Eng. 2015, 17, 73–82. [Google Scholar] [CrossRef]

- Wang, K.; Zhang, H.; Zhao, W.S. Spintronic Memories: From Memory to Computing-in-Memory. In Proceedings of the IEEE/ACM International Symposium on Nanoscale Architectures (NANOARCH), Qingdao, China, 17–19 July 2019; pp. 1–2. [Google Scholar]

- Lebdeh, M.A.; Abunahla, H.; Mohammad, B.; Al-Qutayri, M. An Efficient Heterogeneous Memristive xnor for In-Memory Computing. IEEE Trans. Circuits Syst. I Regul. Pap. 2017, 64, 2427–2437. [Google Scholar] [CrossRef]

- Sun, X.; Yin, S.; Peng, X.; Liu, R.; Seo, J.; Yu, S. XNOR-RRAM: A scalable and parallel resistive synaptic architecture for binary neural networks. In Proceedings of the Design, Automation & Test in Europe Conference & Exhibition (DATE), Dresden, Germany, 19–23 March 2018; pp. 1423–1428. [Google Scholar]

- Natsui, M.; Chiba, T.; Hanyu, T. Design of an energy-efficient XNOR gate based on MTJ-based nonvolatile logic-in-memory architecture for binary neural network hardware. Jpn. J. Appl. Phys. 2019, 58, SBBB01. [Google Scholar] [CrossRef]

- Chang, L.; Ma, X.; Wang, Z.; Zhang, Y.; Xie, Y.; Zhao, W. PXNOR-BNN: In/With Spin-Orbit Torque MRAM Preset-XNOR Operation-Based Binary Neural Networks. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2019, 27, 2668–2679. [Google Scholar] [CrossRef]

- Slesazeck, S.; Ravsher, T.; Havel, V.; Breyer, E.T.; Mulaosmanovic, H.; Mikolajick, T. A 2TnC ferroelectric memory gain cell suitable for compute-in-memory and neuromorphic application. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 1–38. [Google Scholar]

- Liu, R.; Peng, X.; Sun, X.; Khwa, W.S.; Si, X.; Chen, J.J.; Li, J.F.; Chang, M.F.; Yu, S. Parallelizing SRAM Arrays with Customized Bit-Cell for Binary Neural Networks. In Proceedings of the IEEE Design Automation Conference (DAC), San Francisco, CA, USA, 24–28 June 2018; pp. 24–28. [Google Scholar]

- Yin, S.; Jiang, Z.; Seo, J.S.; Seok, M. XNOR-SRAM: In-Memory Computing SRAM Macro for Binary/Ternary Deep Neural Networks. IEEE J. Solid State Circuits 2020, 55, 1733–1743. [Google Scholar] [CrossRef]

- Angizi, S.; Fan, D. ReDRAM: A Reconfigurable Processing-in-DRAM Platform for Accelerating Bulk Bit-Wise Operations. In Proceedings of the IEEE/ACM International Conference on Computer-Aided Design (ICCAD), Westminster, CO, USA, 4–7 November 2019; pp. 1–8. [Google Scholar]

- Wang, Q.; Zhao, Y.; Yang, J.; Liu, C.; Jiang, P.; Ding, Q.; Gong, T.; Luo, Q.; Lv, H.; Liu, M. Non-volatile In Memory Dual-Row X(N)OR Operation with Write Back Circuit Based on 1T1C. In Proceedings of the IEEE International Conference on Solid-State & Integrated Circuit Technology (ICSICT), Kunming, China, 3–6 November 2020; pp. 1–3. [Google Scholar]

- Endoh, T.; Koike, H.; Ikeda, S.; Hanyu, T.; Ohno, H. An Overview of Nonvolatile Emerging Memories—Spintronics for Working Memories. IEEE J. Emerg. Sel. Top. Circuits Syst. 2016, 6, 109–119. [Google Scholar] [CrossRef]

- Yamada, J.; Miwa, T.; Koike, H.; Toyoshima, H. A self-reference read scheme for a 1T/1C FeRAM. In Proceedings of the Symposium on VLSI Circuits. Digest of Technical Papers, Honolulu, HI, USA, 11–13 June 1998; pp. 238–241. [Google Scholar]

- Ali, M.F.; Jaiswal, A.; Roy, K. In-Memory Low-Cost Bit-Serial Addition Using Commodity DRAM Technology. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 67, 155–165. [Google Scholar] [CrossRef]

- Kimura, H.; Hanyu, T.; Kameyama, M. Multiple-valued logic-in-memory VLSI based on ferroelectric capacitor storage and charge addition. In Proceedings of the IEEE International Symposium on Multiple-Valued Logic (ISMVL), Boston, MA, USA, 15–18 May 2002; pp. 161–166. [Google Scholar]

- Elshamy, M.; Mostafa, H.; Said, M.S. New non-destructive Read/Write circuit for Memristor-based memories. In Proceedings of the International Conference on Engineering and Technology (ICET), Cairo, Egypt, 19–20 April 2014; pp. 1–5. [Google Scholar]

- Mulaosmanovic, H.; Dünkel, S.; Müller, J.; Trentzsch, M.; Beyer, S.; Breyer, E.T.; Mikolajick, T.; Slesazeck, S. Impact of Read Operation on the Performance of HfO2-Based Ferroelectric FETs. IEEE Electron Device Lett. 2020, 41, 1420–1423. [Google Scholar] [CrossRef]

- Ogiwara, R.; Tanaka, S.; Itoh, Y.; Miyakawa, T.; Takeuchi, Y.; Doumae, S.M.; Takenaka, H.; Kunishima, I.; Shuto, S.; Hidaka, O.; et al. A 0.5/spl mu/m 3V 1T1C 1Mb FRAM with a variable reference bit-line voltage scheme using a fatigue-free reference capacitor. IEEE J. Solid State Circuits 2000, 35, 545–551. [Google Scholar] [CrossRef]

- Kim, S.J.; Mohan, J.; Summerfelt, S.R. Ferroelectric Hf0.5Zr0.5O2 Thin Films: A Review of Recent Advances. JOM 2019, 71, 246–255. [Google Scholar] [CrossRef]

- Aziz, A.; Ghosh, S.; Datta, S.; Gupta, S.K. Physics-Based Circuit-Compatible SPICE Model for Ferroelectric Transistors. IEEE Electron Device Lett. 2016, 37, 805–808. [Google Scholar] [CrossRef]

- Milan, P.; Christopher, K.; Hoffmann, M.; Mulaosmanovic, H.; Stefan, M.; Evelyn, T.B.; Schroeder, U.; Kersch, A.; Mikolajick, T.; Slesazeck, S. A computational study of hafnia-based ferroelectric memories: From ab initio via physical modeling to circuit models of ferroelectric device. JCE 2017, 37, 1236–1256. [Google Scholar]

| Characteristics | PZT | BTO | HfO2 |

|---|---|---|---|

| Thickness (nm) | >70 | >25 | 5–40 |

| Bandgap (eV) | 3–4 | ~3.1 | 5.3–5.6 |

| Dielectric constant | ~1300 | 150–250 | ~30 |

| CMOS compatibility | Pb and O2 diffusion | Bi and O2 diffusion | Stable |

| Remnant polarization (2Pr) (μC/cm2) | 20–40 | <10 | 1–40 |

| Model parameter | α (m/F) | β (m5/F/C2) | γ (m9/F/C4) | R0 (Ω) | C0 (pF) |

| Value | −6.25 × 109 | 4.88 × 1027 | 1.43 × 1047 | 625 | 288 |

| C1 | C3 | OUT |

|---|---|---|

| 0 | 0 | 0 |

| 1 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 1 | 0 |

| Architecture | Nonvolatile | Memory Cell | Technology | X(N)OR-Aera |

|---|---|---|---|---|

| SRAM-based [16] | No | 6T | 28 nm | SA and Ref |

| DRAM-based [26] | No | 1T1C | 45 nm | 10T |

| RRAM-based [20] | Yes | 1T1R | 65 nm | CSA and Ref |

| MRAM-based [21,22] | Yes | 2T1MTJ/1MTJ | 28 nm/40 nm | 12T/15T |

| 1T1C FeCAP-based [27] | Yes | 1T1C | 28 nm | 5T |

| 1T2C FeCAP-based | Yes | 1T2C | 28 nm | 5T |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, Q.; Zhang, D.; Zhao, Y.; Liu, C.; Hu, Q.; Liu, X.; Yang, J.; Lv, H. A 1T2C FeCAP-Based In-Situ Bitwise X(N)OR Logic Operation with Two-Step Write-Back Circuit for Accelerating Compute-In-Memory. Micromachines 2021, 12, 385. https://doi.org/10.3390/mi12040385

Wang Q, Zhang D, Zhao Y, Liu C, Hu Q, Liu X, Yang J, Lv H. A 1T2C FeCAP-Based In-Situ Bitwise X(N)OR Logic Operation with Two-Step Write-Back Circuit for Accelerating Compute-In-Memory. Micromachines. 2021; 12(4):385. https://doi.org/10.3390/mi12040385

Chicago/Turabian StyleWang, Qiao, Donglin Zhang, Yulin Zhao, Chao Liu, Qiao Hu, Xuanzhi Liu, Jianguo Yang, and Hangbing Lv. 2021. "A 1T2C FeCAP-Based In-Situ Bitwise X(N)OR Logic Operation with Two-Step Write-Back Circuit for Accelerating Compute-In-Memory" Micromachines 12, no. 4: 385. https://doi.org/10.3390/mi12040385

APA StyleWang, Q., Zhang, D., Zhao, Y., Liu, C., Hu, Q., Liu, X., Yang, J., & Lv, H. (2021). A 1T2C FeCAP-Based In-Situ Bitwise X(N)OR Logic Operation with Two-Step Write-Back Circuit for Accelerating Compute-In-Memory. Micromachines, 12(4), 385. https://doi.org/10.3390/mi12040385