Post-Moore Memory Technology: Sneak Path Current (SPC) Phenomena on RRAM Crossbar Array and Solutions

Abstract

1. Introduction

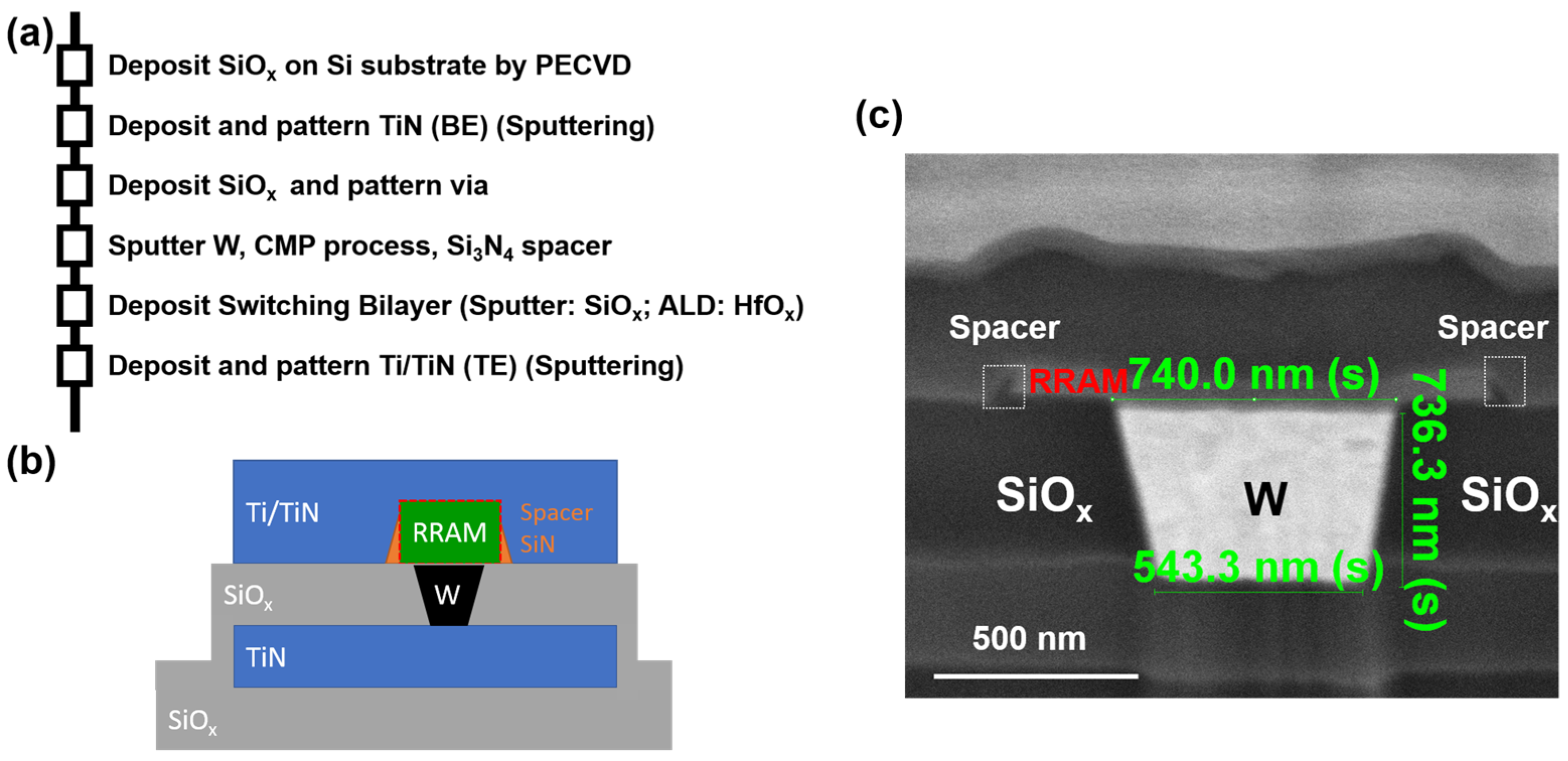

2. Materials and Methods

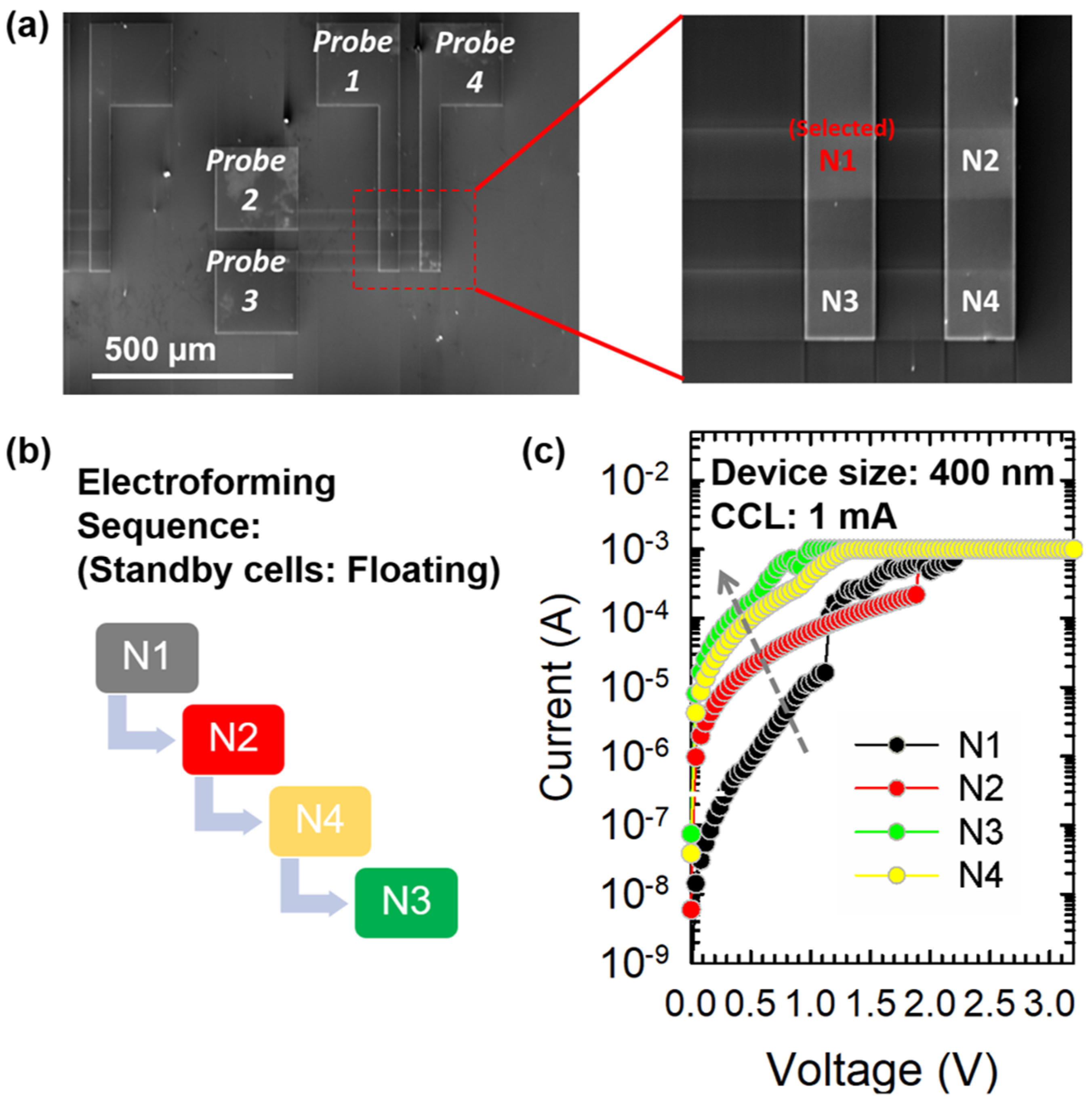

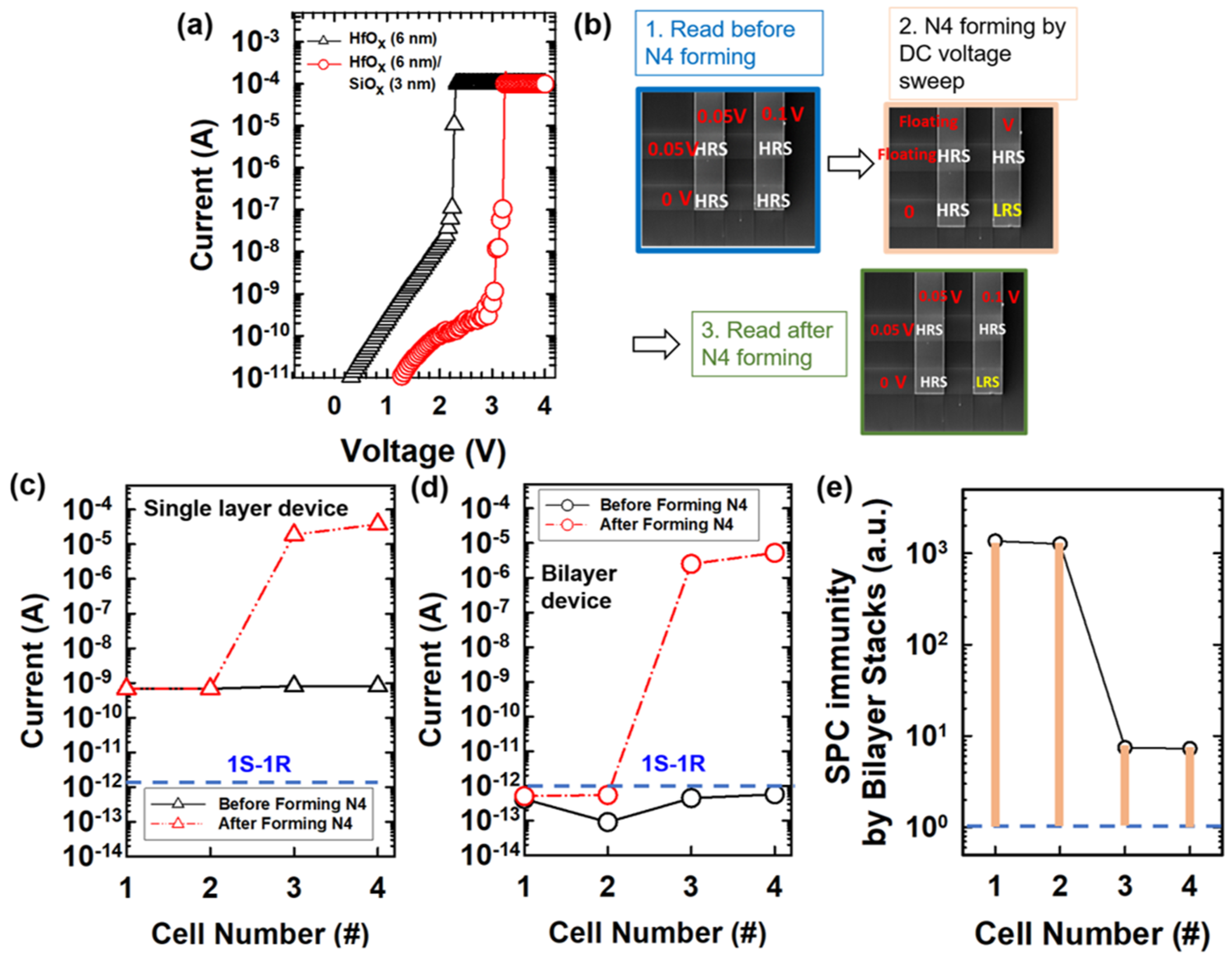

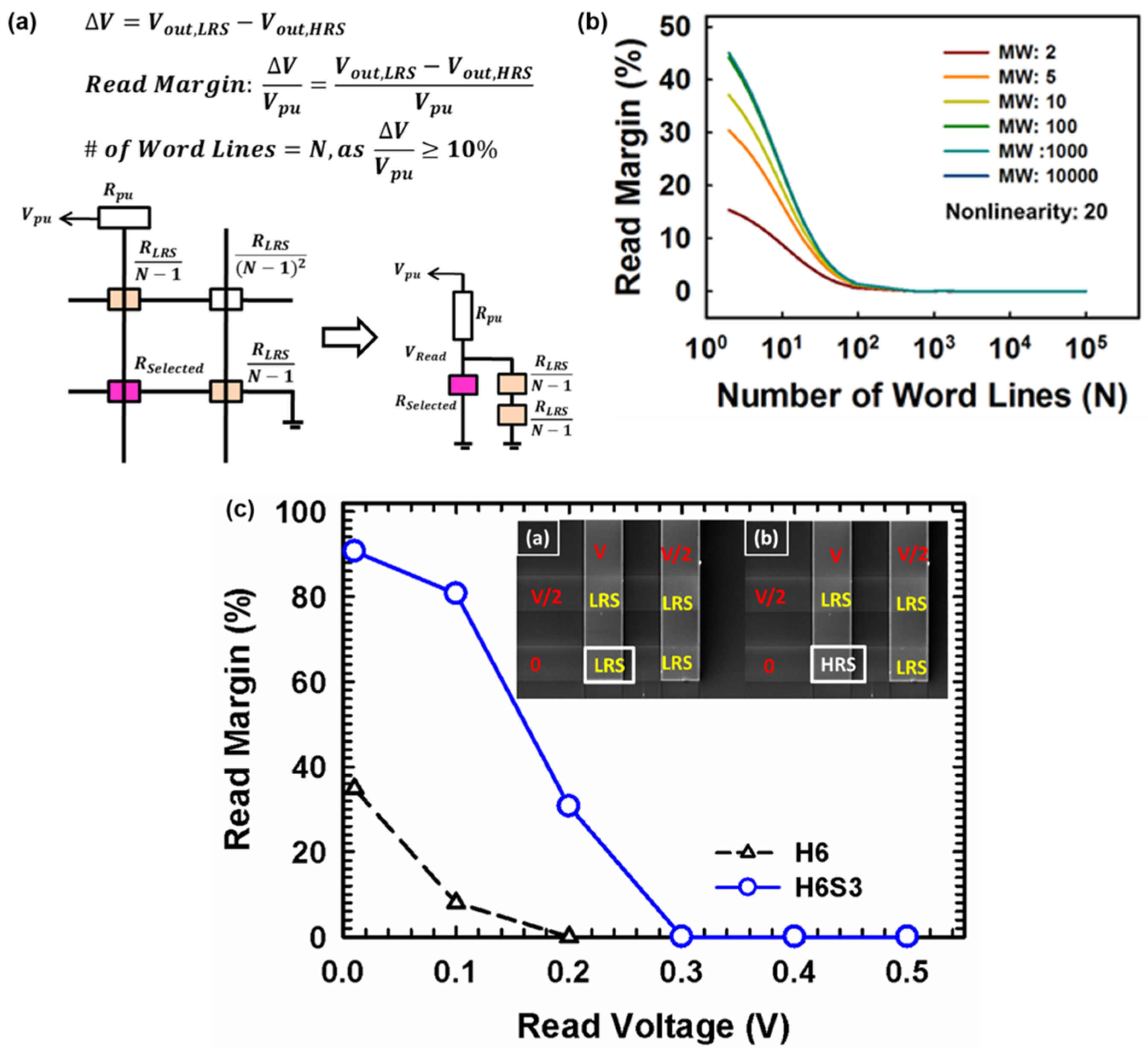

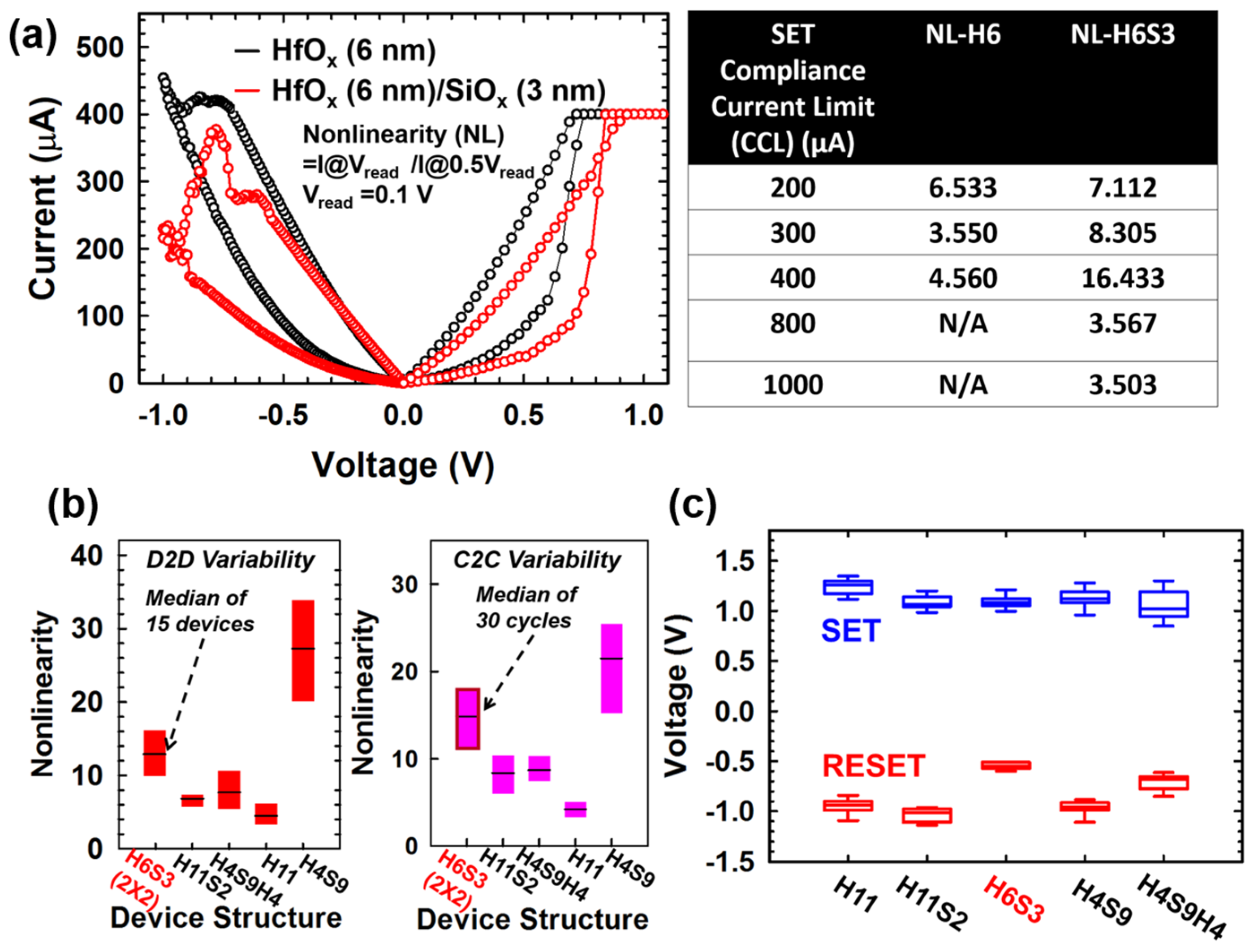

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Joshi, V.; le Gallo, M.; Haefeli, S.; Boybat, I.; Nandakumar, S.R.; Piveteau, C.; Dazzi, M.; Rajendran, B.; Sebastian, A.; Eleftheriou, E. Accurate deep neural network inference using computational phase-change memory. Nat. Commun. 2020, 11, 1–13. [Google Scholar] [CrossRef] [PubMed]

- Lin, Y.H.; Chen, W.C.; Chen, P.H.; Lin, C.Y.; Chang, K.C.; Chang, Y.C.; Yeh, C.-H.; Lin, C.-Y.; Jin, F.-Y.; Chen, K.-H.; et al. Effect of deposition temperature on electrical properties of one-transistor-one-capacitor (1T1C) FeRAM devices. Appl. Phys. Lett. 2020, 117, 023502. [Google Scholar] [CrossRef]

- Chen, Y.; Xu, M.; Hu, X.; Yue, Y.; Zhang, X.; Shen, Q. High-resolution structural mapping and single-domain switching kinetics in 2D-confined ferroelectric nanodots for low-power FeRAM. Nanoscale 2020, 12, 11997–12006. [Google Scholar] [CrossRef] [PubMed]

- Barla, P.; Joshi, V.K.; Bhat, S. A novel low power and reduced transistor count magnetic arithmetic logic unit using hybrid STT-MTJ/CMOS circuit. IEEE Access 2020, 8, 6876–6889. [Google Scholar] [CrossRef]

- Chand, U.; Huang, C.Y.; Kumar, D.; Tseng, T.Y. Metal induced crystallized poly-Si-based conductive bridge resistive switching memory device with one transistor and one resistor architecture. Appl. Phys. Lett. 2015, 107, 203502. [Google Scholar] [CrossRef]

- Waser, R.; Aono, M. Nanoionics-based resistive switching memories. Nat. Mater. 2007, 6, 833–840. [Google Scholar] [CrossRef]

- Cappelletti, P. Nonvolatile memory evolution and revolution. In IEEE International Electron Devices Meeting (IEDM); IEEE: New York, NY, USA, 2015; pp. 10–11. [Google Scholar]

- Wong, H.S.P.; Lee, H.Y.; Yu, S.; Chen, Y.S.; Wu, Y.; Chen, P.S.; Lee, B.; Chen, F.T.; Tsai, M.J. Metal—Oxide RRAM. Proc. IEEE 2012, 100, 1951–1970. [Google Scholar] [CrossRef]

- Chua, L. Memristor-the missing circuit element. IEEE Trans. Circuit Theory 1971, 18, 507–519. [Google Scholar] [CrossRef]

- Lee, H.D.; Kim, S.G.; Cho, K.; Hwang, H.; Choi, H.; Lee, J.; Lee, S.H.; Lee, H.J.; Suh, J.; Chung, S.O.; et al. Integration of 4F2 selector-less crossbar array 2Mb ReRAM based on transition metal oxides for high-density memory applications. In VLSI Technology (VLSIT); IEEE: New York, NY, USA, 2012; pp. 151–152. [Google Scholar]

- Yu, S. Neuro-inspired computing with emerging nonvolatile memories. Proc. IEEE 2018, 106, 260–285. [Google Scholar] [CrossRef]

- Ielmini, D. Brain-inspired computing with resistive switching memory (RRAM): Devices, synapses, and neural networks. Microelectron. Eng. 2018, 190, 44–53. [Google Scholar] [CrossRef]

- Chen, A. A review of emerging non-volatile memory (NVM) technologies and applications. Solid State Electron. 2016, 125, 25–38. [Google Scholar] [CrossRef]

- Azghadi, M.R.; Chen, Y.; Eshraghian, J.K.; Chen, J.; Lin, C.-Y.; Amirsoleimani, A.; Mehonic, A.; Mehonic, A.; Kenyon, A.J.; Fowler, B.; et al. Complementary metal-oxide semiconductor and memristive hardware for neuromorphic computing. Adv. Intell. Syst. 2020, 2, 1900189. [Google Scholar] [CrossRef]

- Xu, X.; Luo, Q.; Gong, T.; Lv, H.; Long, S.; Liu, Q.; Chung, S.S.; Li, J.; Liu, M. Fully CMOS compatible 3D vertical RRAM with self-aligned self-selective cell enabling sub-5nm scaling. In Proceedings of the 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016; IEEE: New York, NY, USA, 2016; pp. 1–2. [Google Scholar]

- Luo, Q.; Xu, X.; Liu, H.; Lv, H.; Gong, T.; Long, S.; Liu, Q.; Sun, H.; Banerjee, W.; Li, L.; et al. Demonstration of 3D vertical RRAM with ultra low-leakage, high-selectivity and self-compliance memory cells. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; IEEE: New York, NY, USA, 2015; pp. 10–12. [Google Scholar]

- Gao, S.; Zeng, F.; Li, F.; Wang, M.; Mao, H.; Wang, G.; Song, C.; Pan, F. Forming-free and self-rectifying resistive switching of the simple Pt/TaO x/n-Si structure for access device-free high-density memory application. Nanoscale 2015, 7, 6031–6038. [Google Scholar] [CrossRef] [PubMed]

- Woo, J.; Yu, S. Two-step read scheme in one-selector and one-RRAM crossbar-based neural network for improved inference robustness. IEEE Trans. Electron. Devices 2018, 65, 5549–5553. [Google Scholar] [CrossRef]

- Peng, X.; Madler, R.; Chen, P.; Yu, S. Cross-point memory design challenges and survey of selector device characteristics. J. Comput. Electron. 2017, 16, 1167–1174. [Google Scholar] [CrossRef]

- Zhou, J.; Kim, K.; Lu, W. Crossbar RRAM arrays: Selector device requirements during a read operation. IEEE Trans. Electron. Devices 2014, 61, 1369–1376. [Google Scholar] [CrossRef]

- Midya, R.; Wang, Z.; Zhang, J.; Savel’ev, S.E.; Li, C.; Rao, M.; Jang, M.H.; Joshi, S.; Jiang, H.; Lin, P.; et al. Anatomy of Ag/Hafnia-based selectors with 1010 nonlinearity. Adv. Mater. 2017, 29, 1604457. [Google Scholar] [CrossRef]

- Yan, B.; Mahmoud, A.M.; Yang, J.J.; Wu, Q.; Chen, Y.; Li, H.H. A neuromorphic ASIC design using one-selector-one-memristor crossbar. In Proceedings of the 2016 IEEE International Symposium on Circuits and Systems (ISCAS), Montreal, QC, Canada, 22–25 May 2016; IEEE: New York, NY, USA, 2016; pp. 1390–1393. [Google Scholar]

- Cha, E.; Park, J.; Woo, J.; Lee, D.; Prakash, A.; Hwang, H. Comprehensive scaling study of NbO2 insulator-metal-transition selector for cross-point array application. Appl. Phys. Lett. 2016, 108, 153502. [Google Scholar] [CrossRef]

- Kalcheim, Y.; Camjayi, A.; del Valle, J.; Salev, P.; Rozenberg, M.; Schuller, I.K. Non-thermal resistive switching in Mott insulator nanowires. Nat. Commun. 2020, 11, 1–9. [Google Scholar] [CrossRef]

- Huang, J.J.; Tseng, Y.M.; Hsu, C.W.; Hou, T.H. Bipolar nonlinear Ni/TiO2/Ni Selector for 1S1R Crossbar Array Applications. IEEE Electron. Device Lett. 2011, 32, 1427–1429. [Google Scholar] [CrossRef]

- Jang, G.; Park, M.; Kim, W.; Yang, J.; Hong, J. Bidirectional-nonlinear threshold switching behaviors and thermally robust stability of ZnTe selectors by nitrogen annealing. Sci. Rep. 2020, 10, 1–9. [Google Scholar] [CrossRef] [PubMed]

- Noé, P.; Verdy, A.; d’Acapito, F.; Dory, J.; Bernard, M.; Navarro, G.; Jager, J.; Gaudin, J.; Raty, J. Toward ultimate nonvolatile resistive memories: The mechanism behind ovonic threshold switching revealed. Sci. Adv. 2020, 6, eaay2830. [Google Scholar] [CrossRef] [PubMed]

- Choi, H.-S. Different degradation mechanism by conduction region in AsTeGeSiN threshold switching device. Electron. Lett. 2020, 56, 1202–1204. [Google Scholar] [CrossRef]

- Burr, G.W.; Virwani, K.; Shenoy, R.S.; Padilla, A.; BrightSky, M.; Joseph, E.A.; Lofaro, M.; Kellock, A.J.; King, R.S.; Nguyen, K.; et al. Large-scale (512kbit) integration of multilayer-ready access-devices based on mixed-ionic-electronic-conduction (MIEC) at 100% yield. In Proceedings of the 2012 Symposium on VLSI Technology (VLSIT), Honolulu, HI, USA, 12–14 June 2012; IEEE: New York, NY, USA, 2012; pp. 41–42. [Google Scholar]

- Chen, Y.-F.; O’Donnell, J.A.; Acosta, T.; Kotlyar, R.; Chen, A.; Quintero, P.A.; Strutt, N.; Golonzka, O.; Connor, C.; Hicks, J. eNVM RRAM reliability performance and modeling in 22FFL FinFET technology. In Proceedings of the 2020 IEEE International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 28 April–30 May 2020; IEEE: New York, NY, USA, 2020; pp. 1–4. [Google Scholar]

- Chen, Y.-C.; Hu, S.; Lin, C.; Fowler, B.; Huang, H.; Lin, C.; Kim, S.; Chang, Y.; Lee, J.C. Graphite-based selectorless RRAM: Improvable intrinsic nonlinearity for array applications. Nanoscale 2018, 10, 15608–15614. [Google Scholar] [CrossRef]

- Chen, Y.-C.; Lin, C.; Hu, S.; Lin, C.; Fowler, B.; Lee, J. A novel resistive switching identification method through relaxation characteristics for sneak-path-constrained selectorless RRAM application. Sci. Rep. 2019, 9, 1–6. [Google Scholar] [CrossRef]

- Chen, Y.-C.; Lin, C.-Y.; Huang, H.-C.; Kim, S.; Fowler, B.; Chang, Y.-F.; Wu, X.; Xu, G.; Chang, T.-C.; Lee, J.C. Internal filament modulation in low-dielectric gap design for built-in selector-less resistive switching memory application. J. Phys. D Appl. Phys. 2018, 51, 055108. [Google Scholar] [CrossRef]

- Cho, H.; Ryu, J.-H.; Mahata, C.; Ismail, M.; Chen, Y.-C.; Chang, Y.-F.; Cho, S.; Mikhaylov, A.; Lee, J.C.; Kim, S. Bipolar resistive switching with unidirectional selector function in nitride/oxide heterostructures. J. Phys. D Appl. Phys. 2020, 53, 435102. [Google Scholar] [CrossRef]

- Chen, Y.-C.; Huang, H.C.; Lin, C.Y.; Hu, S.T.; Lin, C.C.; Lee, J.C. Selectorless resistive switching memory: Non-uniform dielectric architecture and seasoning effect for low power array applications. AIP Adv. 2019, 9, 075119. [Google Scholar] [CrossRef]

- Ciprut, A.; Friedman, E.G. On the write energy of non-volatile resistive crossbar arrays with selectors. In Proceedings of the 2018 19th International Symposium on Quality Electronic Design (ISQED), Santa Clara, CA, USA, 13–14 March 2018; IEEE: New York, NY, USA, 2018; pp. 184–188. [Google Scholar]

- Chang, C.-C.; Huang, H.-H.; Hudec, B.; Wu, M.-H.; Chang, C.-C.; Liu, P.-T.; Hou, T.-H. Strong Read and Write Interference Induced by Breakdown Failure in Crossbar Arrays. IEEE Trans. Electron. Devices 2020, 67, 12. [Google Scholar] [CrossRef]

- Hsu, C.-W.; Wang, I.T.; Lo, C.-L.; Chiang, M.C.; Jang, W.Y.; Lin, C.H.; Hou, T.H. Self-rectifying bipolar TaOx/TiO2 RRAM with superior endurance over 10 12 cycles for 3D high-density storage-class memory. In Proceedings of the 2013 Symposium on VLSI Technology, Kyoto, Japan, 11–13 June 2013; IEEE: New York, NY, USA, 2013; pp. T166–T167. [Google Scholar]

- Chen, Y.-C.; Huang, H.C.; Lin, C.Y.; Kim, S.; Chang, Y.F.; Lee, J.C. Effects of ambient sensing on SiOx-based resistive switching and resilience modulation by stacking engineering. ECS J. Solid State Sci. Technol. 2018, 7, P350. [Google Scholar] [CrossRef]

- Chen, Y.-C.; Lin, C.Y.; Cho, H.; Kim, S.; Fowler, B.; Lee, J.C. Current-Sweep Operation on Nonlinear Selectorless RRAM for Multilevel Cell Applications. J. Electron. Mater. 2020, 49, 3499–3503. [Google Scholar]

- Long, S.; Lian, X.; Cagli, C.; Perniola, L.; Miranda, E.; Liu, M.; Suñé, J. A model for the set statistics of RRAM inspired in the percolation model of oxide breakdown. IEEE Electron. Device Lett. 2013, 34, 999–1001. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, Y.-C.; Lin, C.-C.; Chang, Y.-F. Post-Moore Memory Technology: Sneak Path Current (SPC) Phenomena on RRAM Crossbar Array and Solutions. Micromachines 2021, 12, 50. https://doi.org/10.3390/mi12010050

Chen Y-C, Lin C-C, Chang Y-F. Post-Moore Memory Technology: Sneak Path Current (SPC) Phenomena on RRAM Crossbar Array and Solutions. Micromachines. 2021; 12(1):50. https://doi.org/10.3390/mi12010050

Chicago/Turabian StyleChen, Ying-Chen, Chao-Cheng Lin, and Yao-Feng Chang. 2021. "Post-Moore Memory Technology: Sneak Path Current (SPC) Phenomena on RRAM Crossbar Array and Solutions" Micromachines 12, no. 1: 50. https://doi.org/10.3390/mi12010050

APA StyleChen, Y.-C., Lin, C.-C., & Chang, Y.-F. (2021). Post-Moore Memory Technology: Sneak Path Current (SPC) Phenomena on RRAM Crossbar Array and Solutions. Micromachines, 12(1), 50. https://doi.org/10.3390/mi12010050