On the Feasibility of Fan-Out Wafer-Level Packaging of Capacitive Micromachined Ultrasound Transducers (CMUT) by Using Inkjet-Printed Redistribution Layers

Abstract

1. Introduction

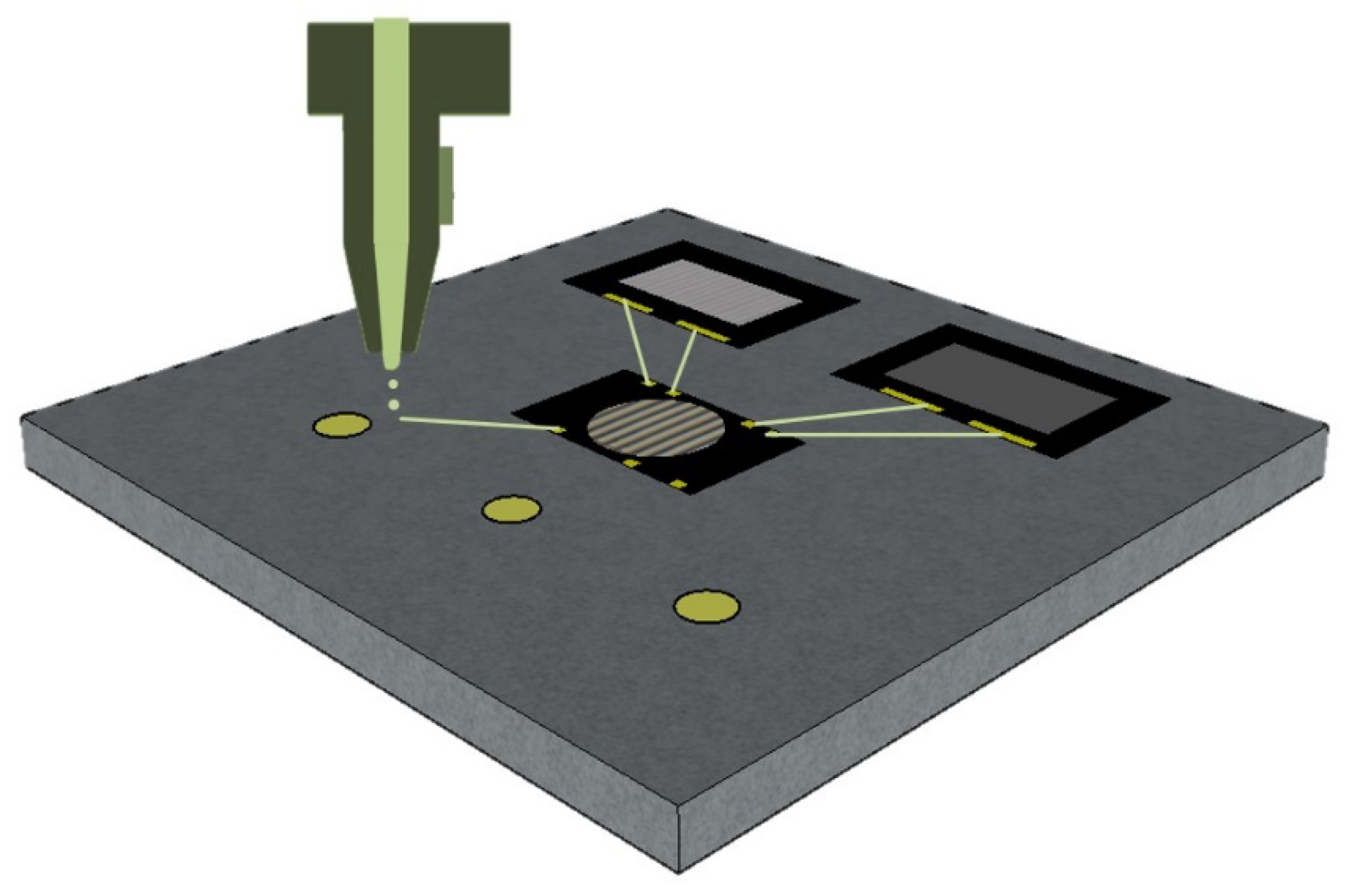

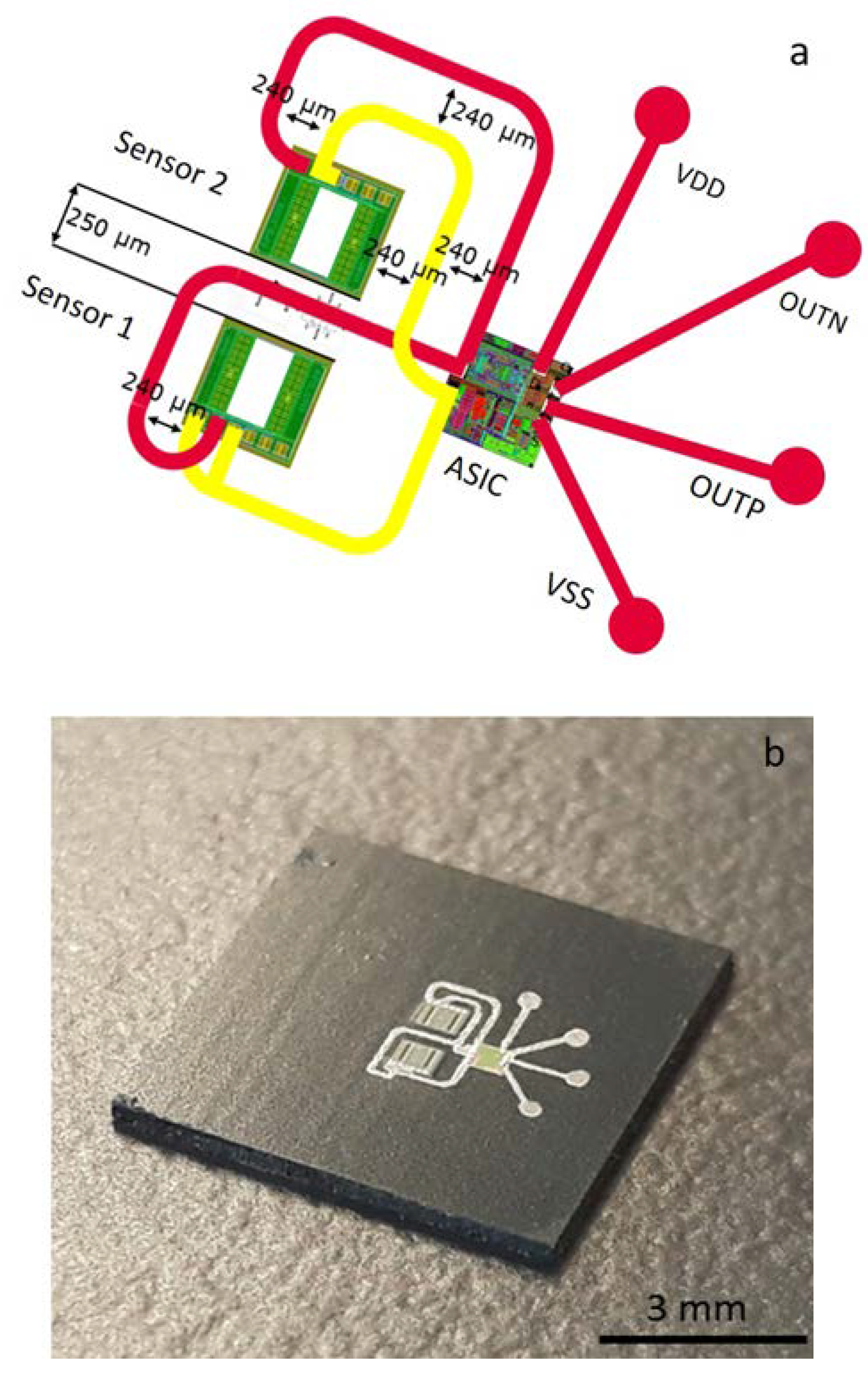

2. Materials and Methods

3. Results and Discussion

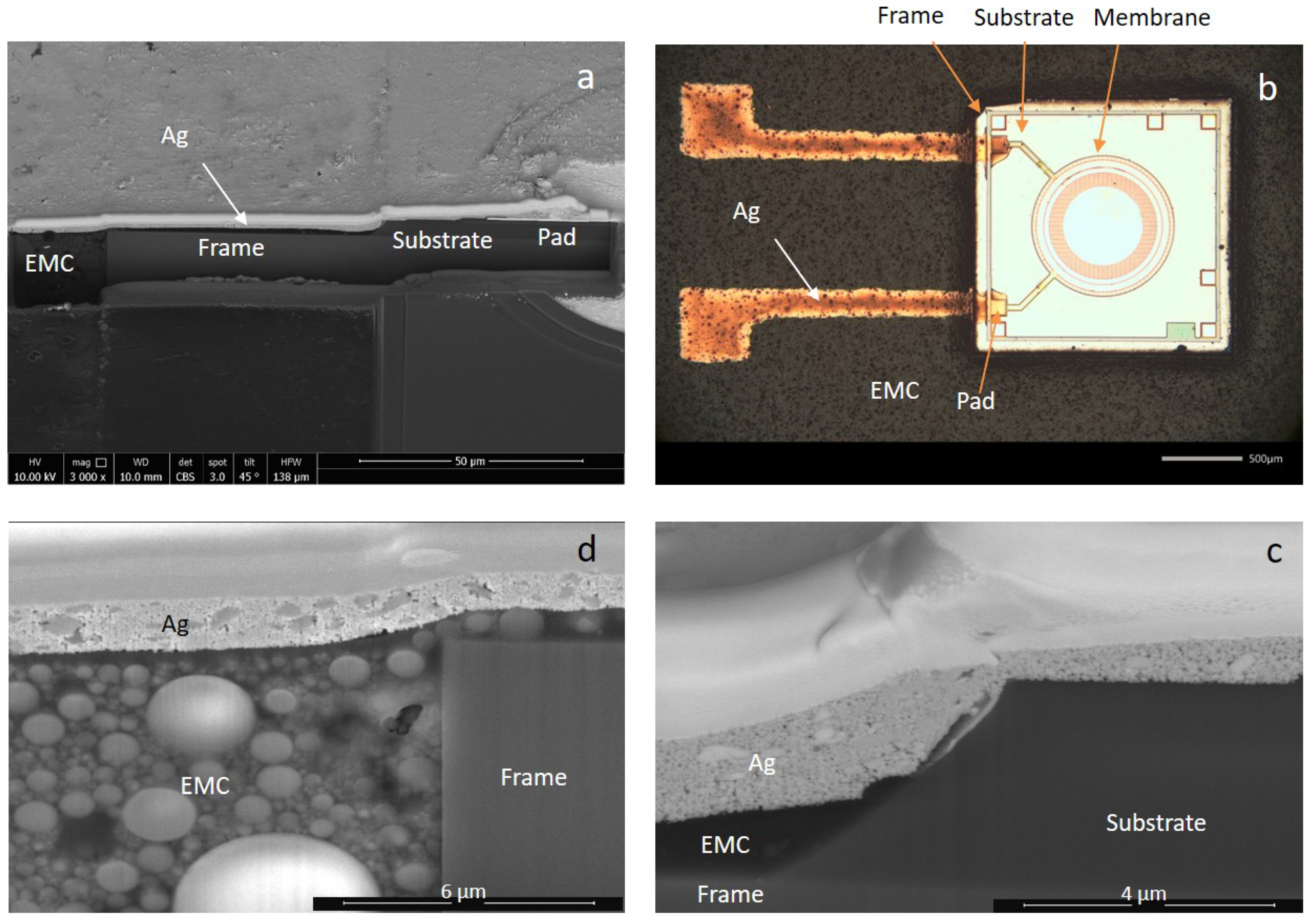

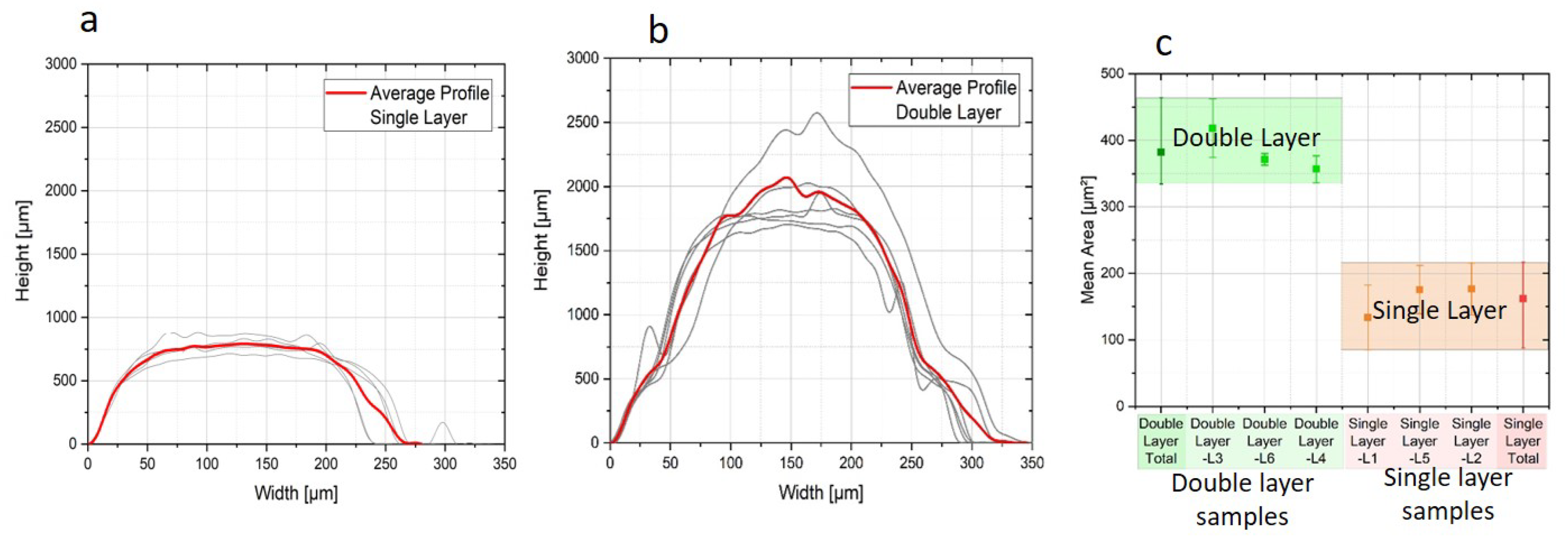

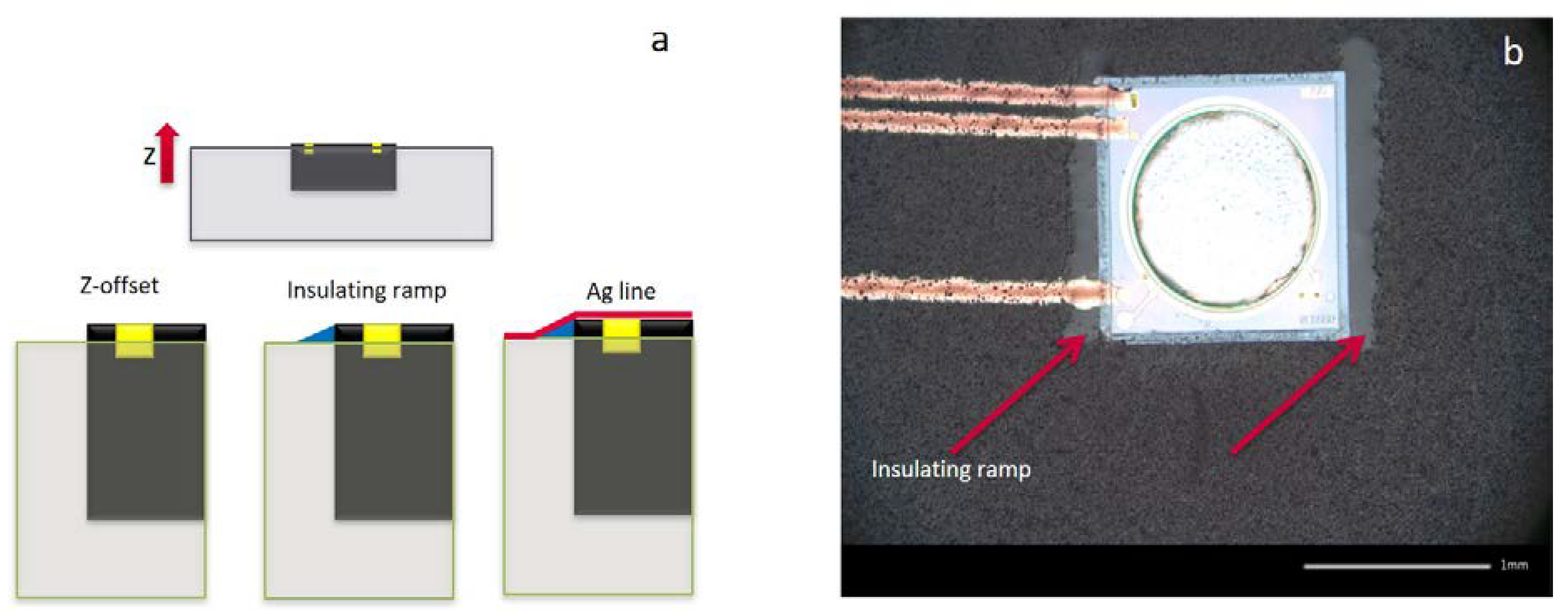

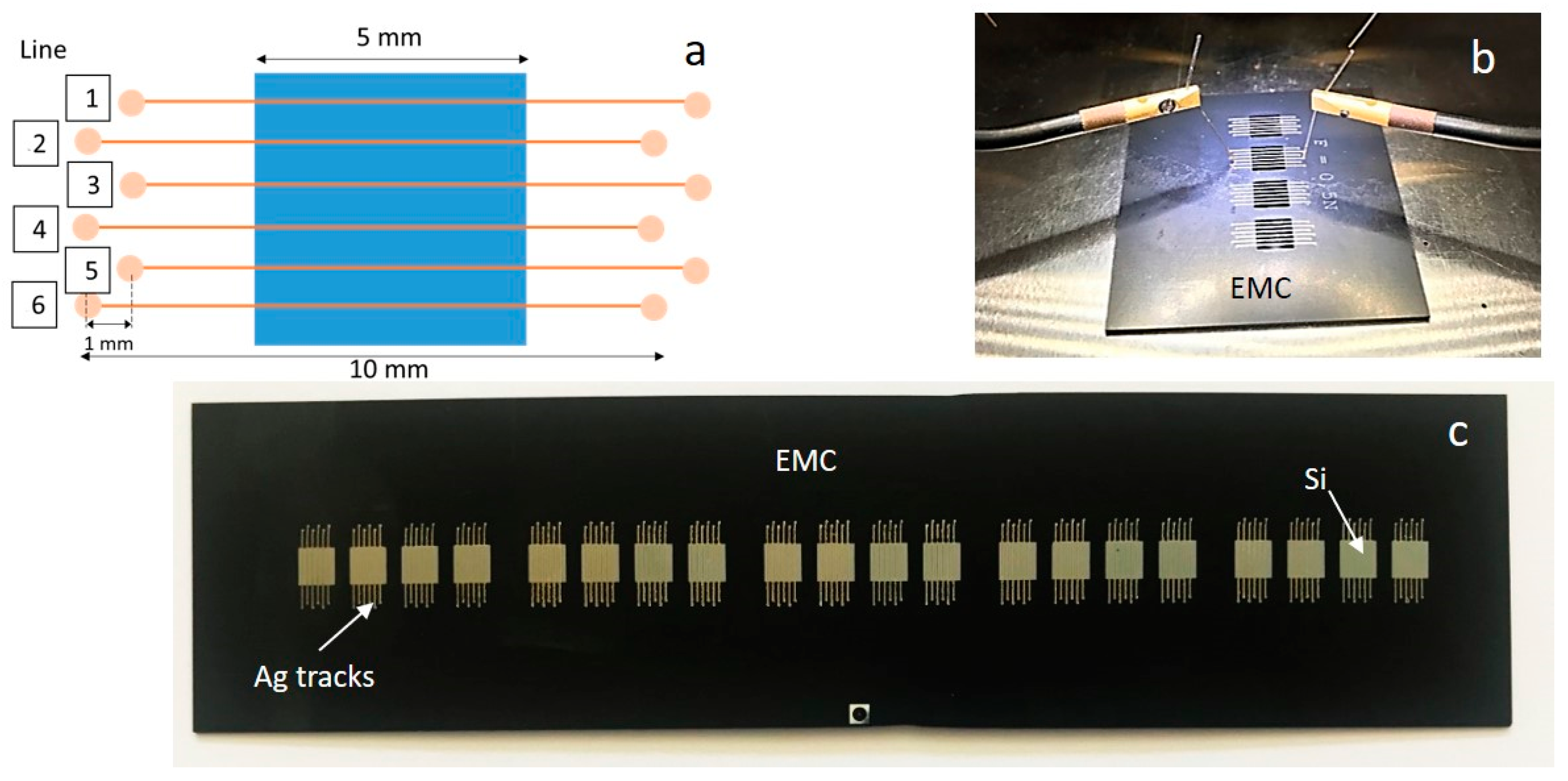

3.1. Microfabrication

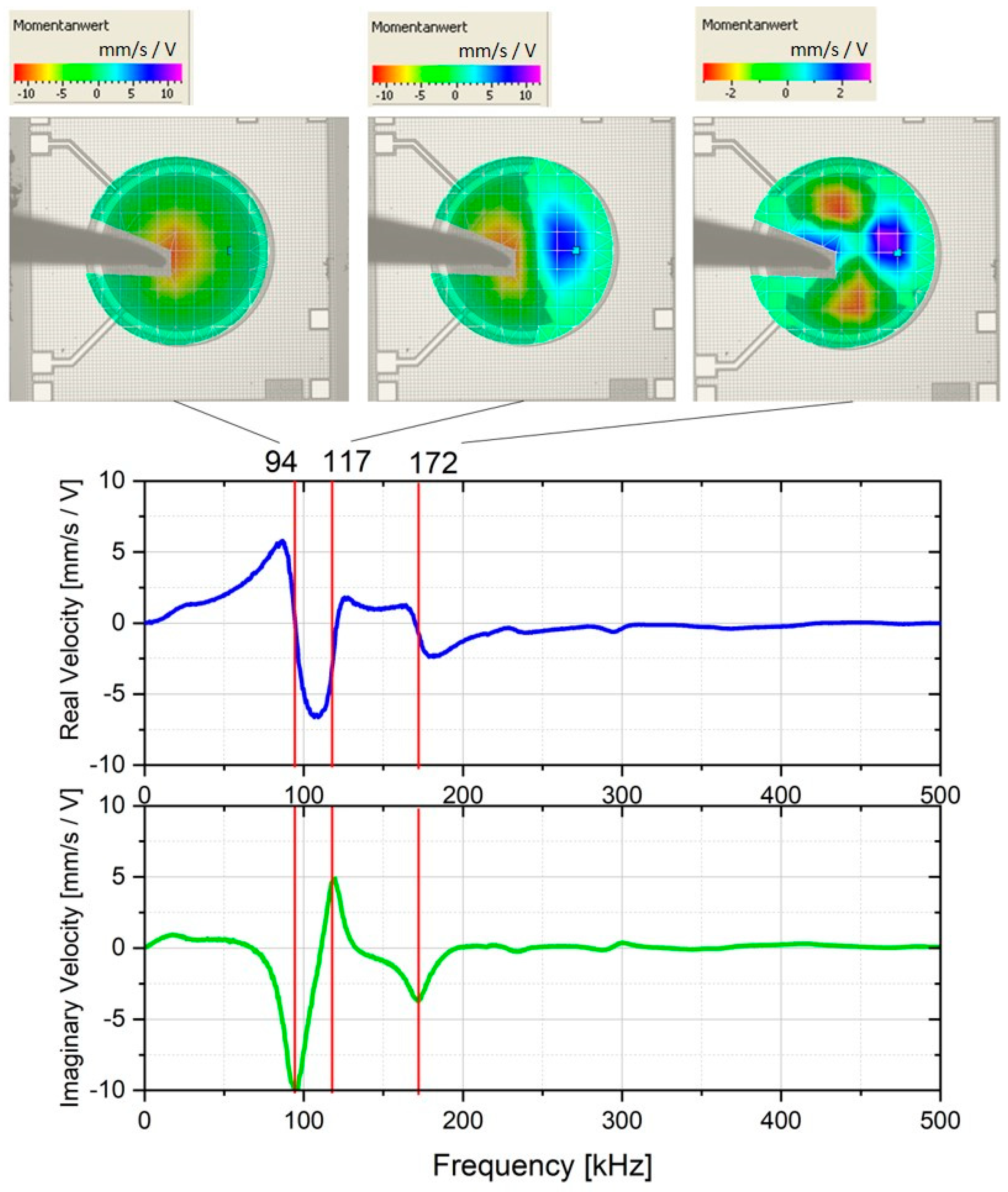

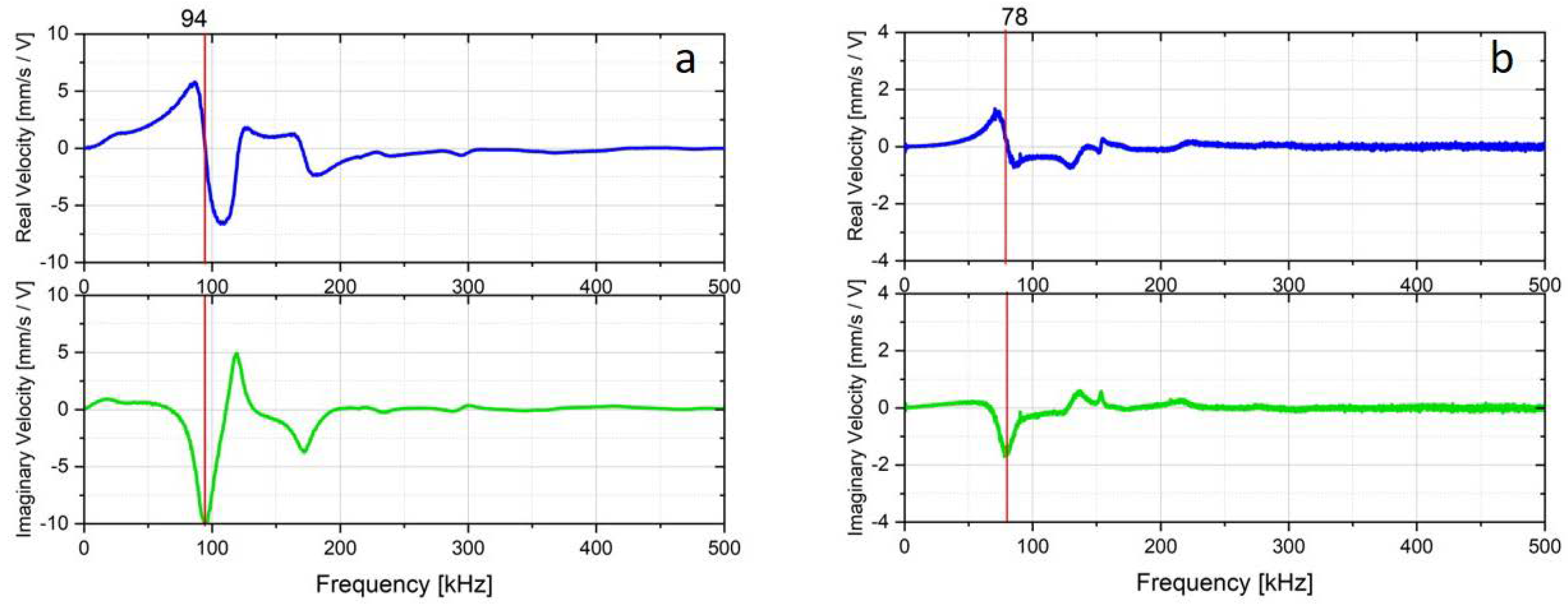

3.2. LDV Analysis

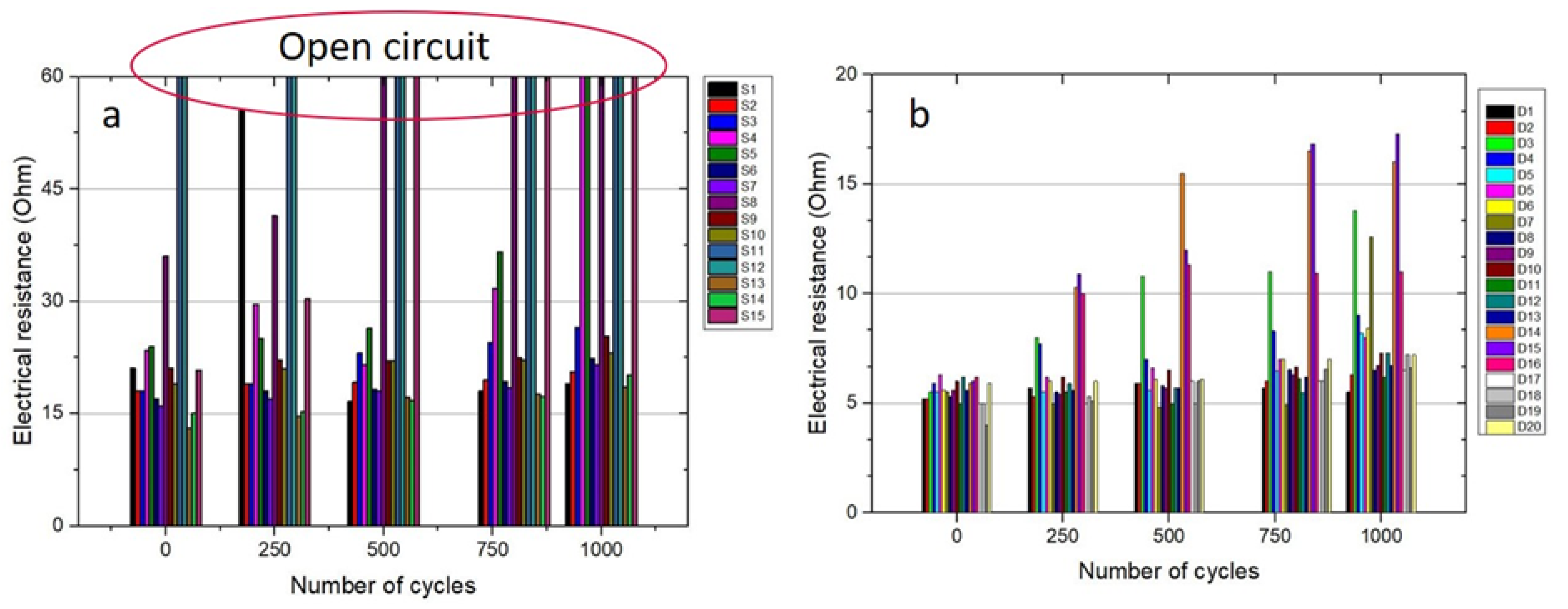

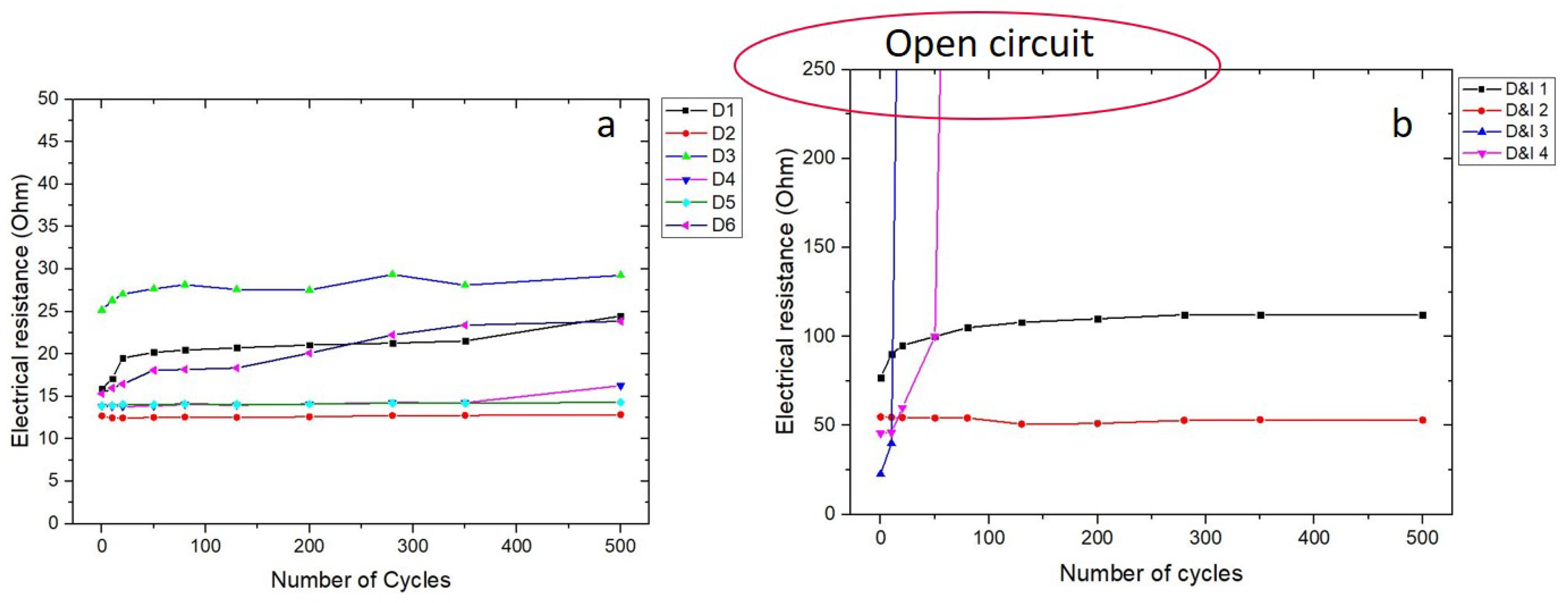

3.3. Reliability Analysis

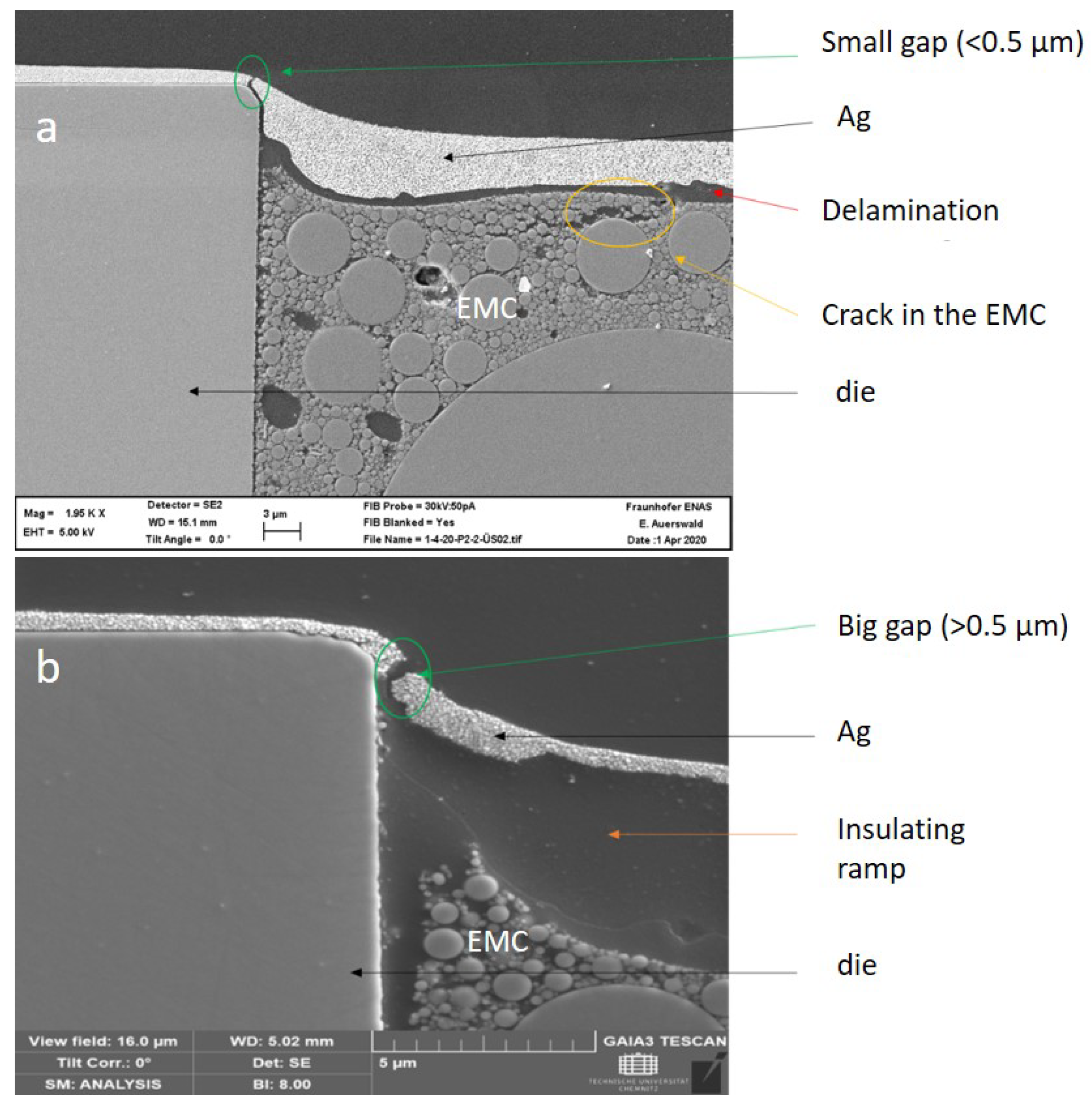

3.4. Barriers to Overcome

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Braun, T.; Becker, K.F.; Hoelck, O.; Voges, S.; Kahle, R.; Graap, P.; Wöhrmann, M.; Aschenbrenner, R.; Dreissigacker, M.; Schneider-Ramelow, M.; et al. Fan-Out Wafer Level Packaging-A Platform for Advanced Sensor Packaging. In Proceedings of the 2019 IEEE 69th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 28–31 May 2019; pp. 861–867. [Google Scholar]

- Cardoso, A.; Kroehnert, S.; Pinto, R.; Fernandes, E.; Barros, I. Integration of MEMS/Sensors in Fan-Out wafer-level packaging technology based system-in-package (WLSiP). In Proceedings of the 2016 IEEE 18th Electronics Packaging Technology Conference (EPTC), Singapore, 30 November–3 December 2016; pp. 801–807. [Google Scholar]

- Lau, J.H. Fan-Out Wafer-Level Packaging; Springer: Singapore, 2018. [Google Scholar]

- Kuisma, H.; Cardoso, A.; Braun, T. Fan-out wafer-level packaging as packaging technology for MEMS. In Handbook of Silicon Based MEMS Materials and Technologies; Elsevier: Amsterdam, The Netherlands, 2020; pp. 707–720. [Google Scholar]

- Kuisma, H.; Cardoso, A.; Mäntyoja, N.; Rosenkrantz, R.; Nurmi, S.; Gall, M. FO-WLP multi-DOF inertial sensor for automotive applications. In Proceedings of the 7th Electronic System-Integration Technology Conference (ESTC), Dresden, Germany, 18–21 September 2018; pp. 1–7. [Google Scholar]

- Martins, A.; Pinheiro, M.; Ferreira, A.F.; Almeida, R.; Matos, F.; Oliveira, J.; Silva, R.P.; Santos, H.; Monteiro, M.; Gamboa, H. Heterogeneous integration challenges within wafer level fan-out SiP for wearables and IoT. In Proceedings of the 2018 IEEE 68th Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 29 May–1 June 2018; pp. 1485–1492. [Google Scholar]

- Theuss, H.; Geissler, C.; Muehlbauer, F.X.; von Waechter, C.; Kilger, T.; Wagner, J.; Fischer, T.; Bartl, U.; Helbig, S.; Sigl, A.; et al. A MEMS Microphone in a FOWLP. In Proceedings of the 2019 IEEE 69th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 28–31 May 2019; pp. 855–860. [Google Scholar]

- Flack, W.W.; Hsieh, R.; Nguyen, H.A.; Slabbekoorn, J.; Lorant, C.; Miller, A. One micron redistribution for fan-out wafer level packaging. In Proceedings of the 2017 IEEE 19th Electronics Packaging Technology Conference (EPTC), Singapore, 6–9 December 2017; pp. 1–7. [Google Scholar]

- Anzinger, S.; Lickert, F.; Fusco, A.; Bosetti, G.; Tumpold, D.; Bretthauer, C.; Dehé, A. Low Power Capacitive Ultrasonic Transceiver Array for Airborne Object Detection. In Proceedings of the 2020 IEEE 33rd International Conference on Micro Electro Mechanical Systems (MEMS), Vancouver, BC, Canada, 18–22 January 2020; pp. 853–856. [Google Scholar]

- Available online: https://silense.eu/ (accessed on 4 May 2020).

- Roshanghias, A.; Ma, Y.; Dreissigacker, M.; Braun, T.; Bretthauer, C.; Becker, K.F.; Schneider-Ramelow, M. The Realization of Redistribution Layers for FOWLP by Inkjet Printing. Proceedings 2018, 2, 703. [Google Scholar] [CrossRef]

- Laurila, M.M.; Khorramdel, B.; Mäntysalo, M. Combination of E-jet and inkjet printing for additive fabrication of multilayer high-density RDL of silicon interposer. IEEE Trans. Electron Devices 2017, 64, 1217–1224. [Google Scholar] [CrossRef]

- Roshanghias, A.; Krivec, M.; Bardong, J.; Binder, A. Additive-manufactured organic interposers. J. Electron. Packag. 2020, 142, 014501. [Google Scholar] [CrossRef]

- Serpelloni, M.; Cantù, E.; Borghetti, M.; Sardini, E. Printed Smart Devices on Cellulose-Based Materials by means of Aerosol-Jet Printing and Photonic Curing. Sensors 2020, 20, 841. [Google Scholar] [CrossRef] [PubMed]

- Chia-Yen, L.; Tsai, H. Printing Method for Redistribution Layer and Filling of through Silicon Vias Using Sintering Silver Paste. In Proceedings of the 2014 9th International Microsystems, Packaging, Assembly and Circuits Technology Conference (IMPACT), Taipei, Taiwan, 22–24 October 2014. [Google Scholar] [CrossRef]

- Roshanghias, A.; Krivec, M.; Binder, A. Digital micro-dispension of non-conductive adhesives (NCA) by inkjet printer. In Proceedings of the 2017 IEEE 19th Electronics Packaging Technology Conference (EPTC), Singapore, 6–9 December 2017; pp. 1–3. [Google Scholar]

- Roshanghias, A.; Ma, Y.; Gaumont, E.; Neumaier, L. Inkjet printed adhesives for advanced M(O)EMS packaging. J. Mater. Sci. Mater. Electron. 2019, 30, 20285–20291. [Google Scholar] [CrossRef]

- ISO—International Organization of Standardization. ISO 25178 Geometrical Product Specifications (GPS)—Surface Texture: Areal; International Organization of Standardization: Geneva, Switzerland, 2016. [Google Scholar]

- Dehé, A.; Wurzer, M.; Füldner, M.; Krumbein, U. A4. 3-The infineon silicon MEMS microphone. Proc. Sens. 2013, 2013, 95–99. [Google Scholar]

- Dehe, A.; Froemel, A.; Infineon Technologies AG. MEMS Microphone with Low Pressure Region between Diaphragm and Counter Electrode. U.S. Patent 9,181,080, 10 November 2015. [Google Scholar]

- Rembe, C.; Siegmund, G.; Steger, H.; Wörtge, M. Measuring MEMS in motion by laser-Doppler vibrometry. In Optical Inspection of Microsystems; CRC Press: Boca Raton, FL, USA, 2006; pp. 245–292. [Google Scholar]

- Bhushan, B.; Luo, D.; Schricker, S.R.; Sigmund, W.; Zauscher, S. (Eds.) Handbook of Nanomaterials Properties; Springer Science & Business Media: Berlin/Heidelberg, Germany, 2014; p. 202. [Google Scholar]

- Nilsson, H.E.; Unander, T.; Siden, J.; Andersson, H.; Manuilskiy, A.; Hummelgard, M.; Gulliksson, M. System integration of electronic functions in smart packaging applications. IEEE Trans. Compon. Packag. Manuf. Technol. 2012, 2, 1723–1734. [Google Scholar] [CrossRef]

- AEC-Q100-REV-H. Failure Mechanism Based Stress Test Qualification for Integrated Circuits; Automotive Electronics Council: Denver, CO, USA, 2014. [Google Scholar]

- De Gans, B.J.; Duineveld, P.C.; Schubert, U.S. Inkjet printing of polymers: State of the art and future developments. Adv. Mater. 2004, 16, 203–213. [Google Scholar] [CrossRef]

- Tehrani, B.K.; Cook, B.S.; Tentzeris, M.M. Inkjet-printed 3D interconnects for millimeter-wave system-on-package solutions. In Proceedings of the 2016 IEEE MTT-S International Microwave Symposium (IMS), San Francisco, CA, USA, 22–27 May 2016; pp. 1–4. [Google Scholar]

- SU8 Datasheet, Microchem. Available online: http://web.mit.edu/3.042/team1_08f/documents/SU8-2050.pdf (accessed on 4 May 2020).

- Sundriyal, P.; Bhattacharya, S. Inkjet-printed sensors on flexible substrates. In Environmental, Chemical and Medical Sensors; Springer: Singapore, 2018; pp. 89–113. [Google Scholar]

- Han, Y.; Dong, J. Electrohydrodynamic printing for advanced micro/nanomanufacturing: Current progresses, opportunities, and challenges. J. Micro Nano Manuf. 2018, 6, 040802. [Google Scholar] [CrossRef]

- Zhou, P.; Yu, H.; Zou, W.; Wang, Z.; Liu, L. High-Resolution and Controllable Nanodeposition Pattern of Ag Nanoparticles by Electrohydrodynamic Jet Printing Combined with Coffee Ring Effect. Adv. Mater. Interfaces 2019, 6, 1900912. [Google Scholar] [CrossRef]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Roshanghias, A.; Dreissigacker, M.; Scherf, C.; Bretthauer, C.; Rauter, L.; Zikulnig, J.; Braun, T.; Becker, K.-F.; Rzepka, S.; Schneider-Ramelow, M. On the Feasibility of Fan-Out Wafer-Level Packaging of Capacitive Micromachined Ultrasound Transducers (CMUT) by Using Inkjet-Printed Redistribution Layers. Micromachines 2020, 11, 564. https://doi.org/10.3390/mi11060564

Roshanghias A, Dreissigacker M, Scherf C, Bretthauer C, Rauter L, Zikulnig J, Braun T, Becker K-F, Rzepka S, Schneider-Ramelow M. On the Feasibility of Fan-Out Wafer-Level Packaging of Capacitive Micromachined Ultrasound Transducers (CMUT) by Using Inkjet-Printed Redistribution Layers. Micromachines. 2020; 11(6):564. https://doi.org/10.3390/mi11060564

Chicago/Turabian StyleRoshanghias, Ali, Marc Dreissigacker, Christina Scherf, Christian Bretthauer, Lukas Rauter, Johanna Zikulnig, Tanja Braun, Karl-F. Becker, Sven Rzepka, and Martin Schneider-Ramelow. 2020. "On the Feasibility of Fan-Out Wafer-Level Packaging of Capacitive Micromachined Ultrasound Transducers (CMUT) by Using Inkjet-Printed Redistribution Layers" Micromachines 11, no. 6: 564. https://doi.org/10.3390/mi11060564

APA StyleRoshanghias, A., Dreissigacker, M., Scherf, C., Bretthauer, C., Rauter, L., Zikulnig, J., Braun, T., Becker, K.-F., Rzepka, S., & Schneider-Ramelow, M. (2020). On the Feasibility of Fan-Out Wafer-Level Packaging of Capacitive Micromachined Ultrasound Transducers (CMUT) by Using Inkjet-Printed Redistribution Layers. Micromachines, 11(6), 564. https://doi.org/10.3390/mi11060564