Binary Addition in Resistance Switching Memory Array by Sensing Majority

Abstract

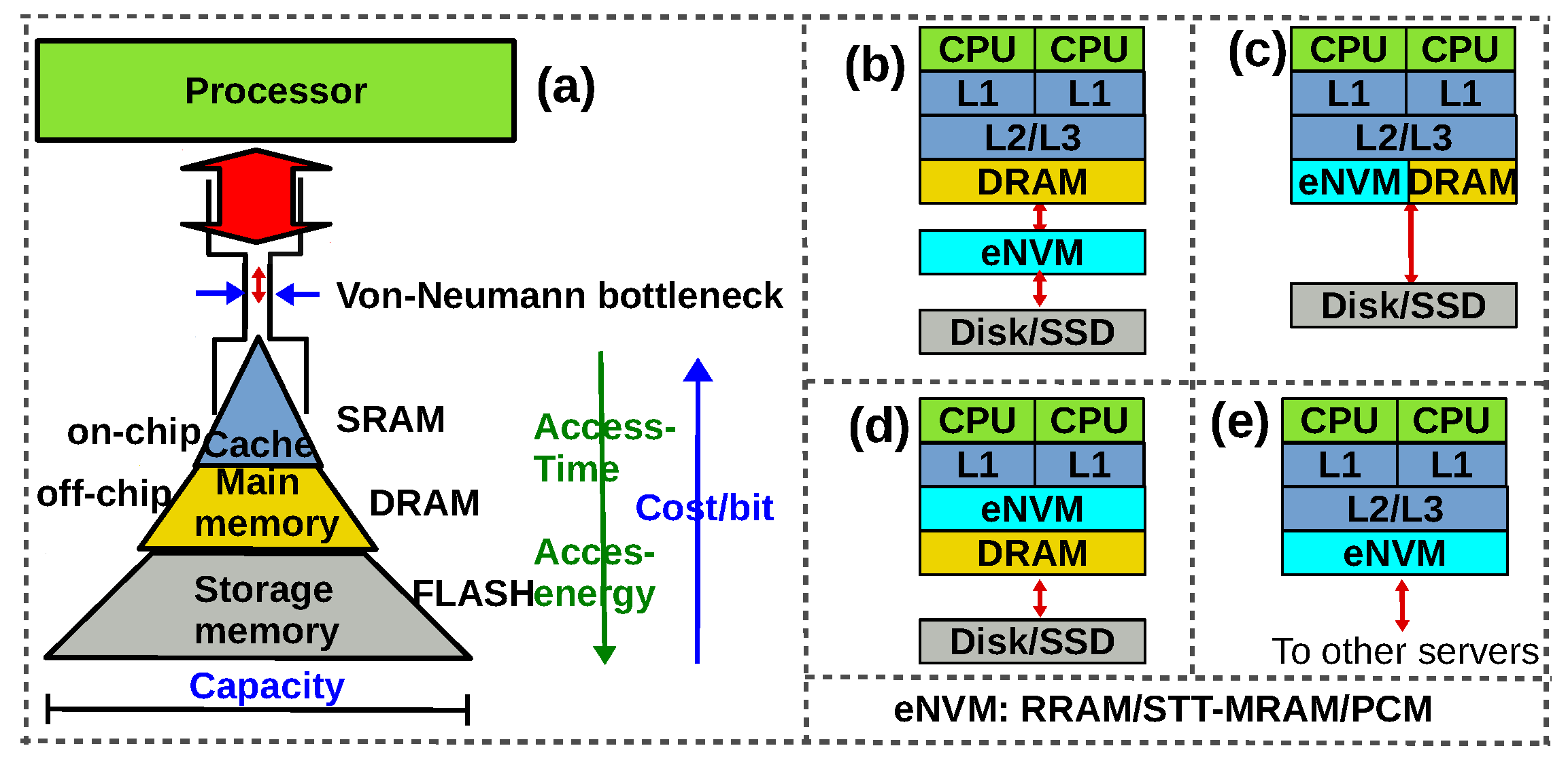

1. Introduction

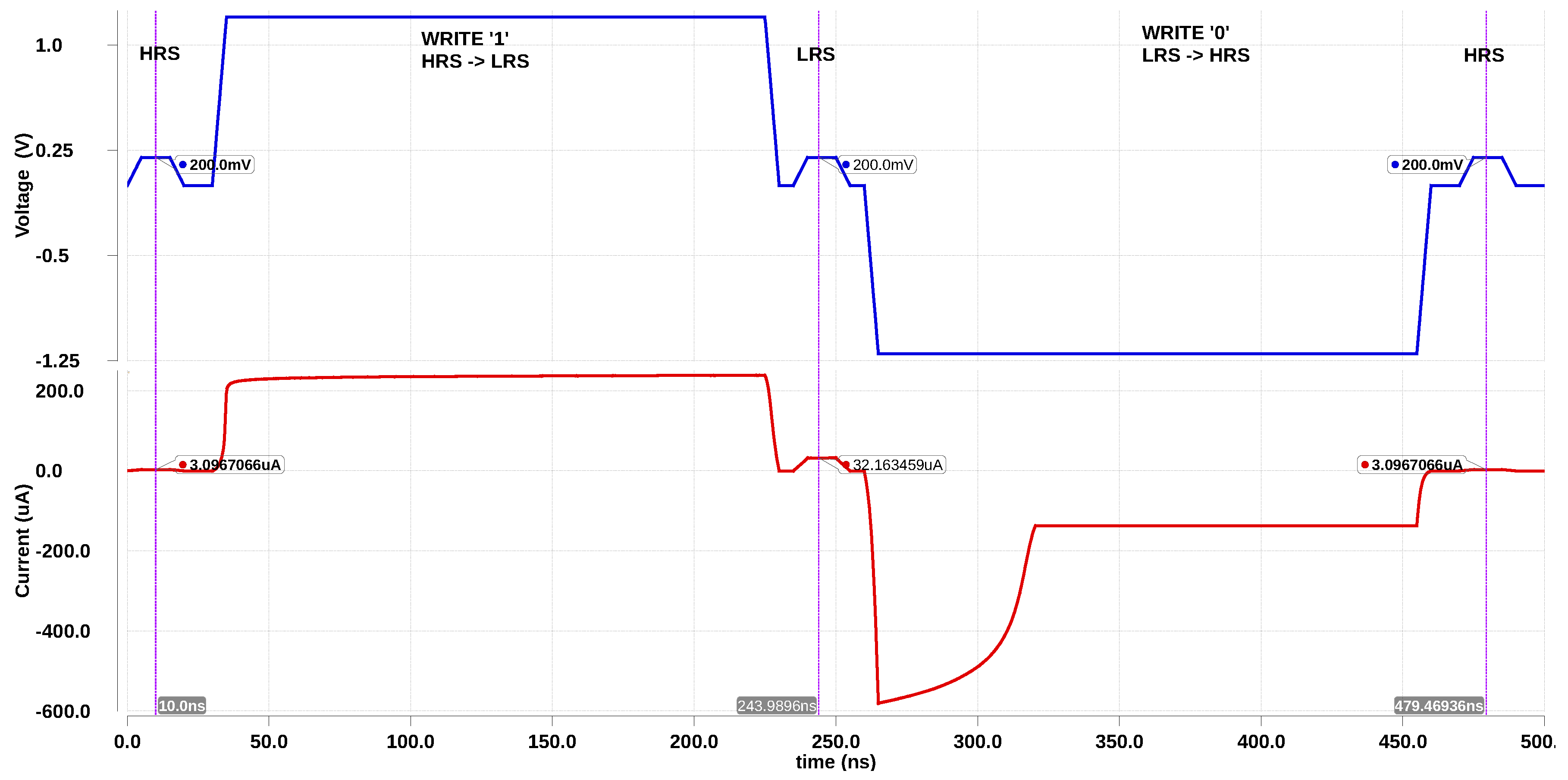

- Resistive Random Access Memory (RRAM) device is a Metal-Insulator-Metal structure where a conductive filament is created (LRS) or broken (HRS) in the insulator. The insulator is usually a transition metal oxide (OxRAM) or an electrolyte (Conductive Bridge RAM)

- Phase Change Memory (PCM) device is a Metal-Active Material-Metal structure where the active material is a chalcogenide phase-change material which is either in amorphous (HRS) or crystalline state (LRS)

- Spin Transfer Torque-Magnetic RAM (STT-MRAM) is a Free layer-Tunnel Layer-Reference layer structure where the magnetic polarization of the Reference layer is fixed while that of the free layer can be programmed to be either in the same direction (parallel, LRS) or opposite direction (anti-parallel, HRS)

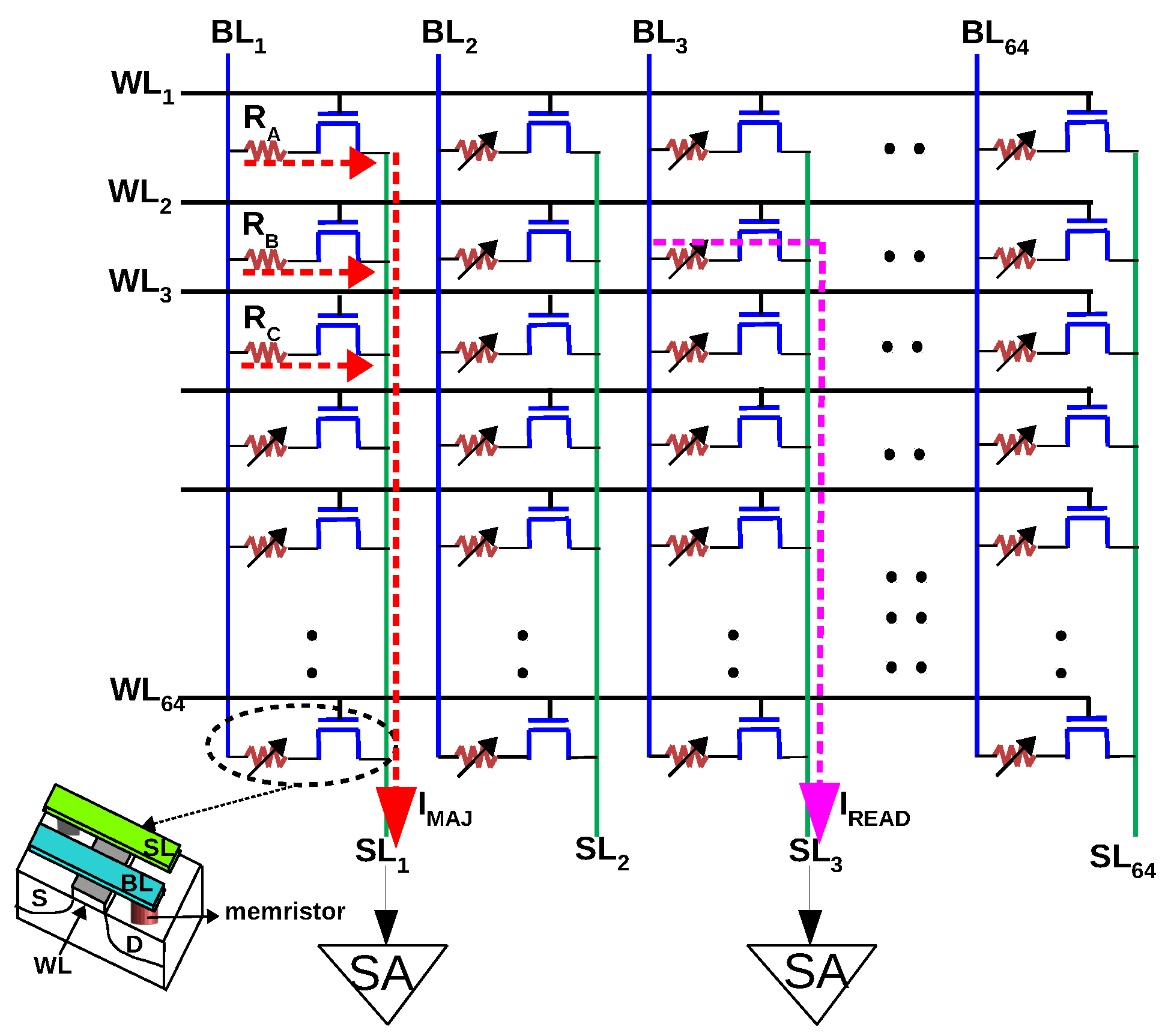

2. Majority Logic in 1T–1R Array

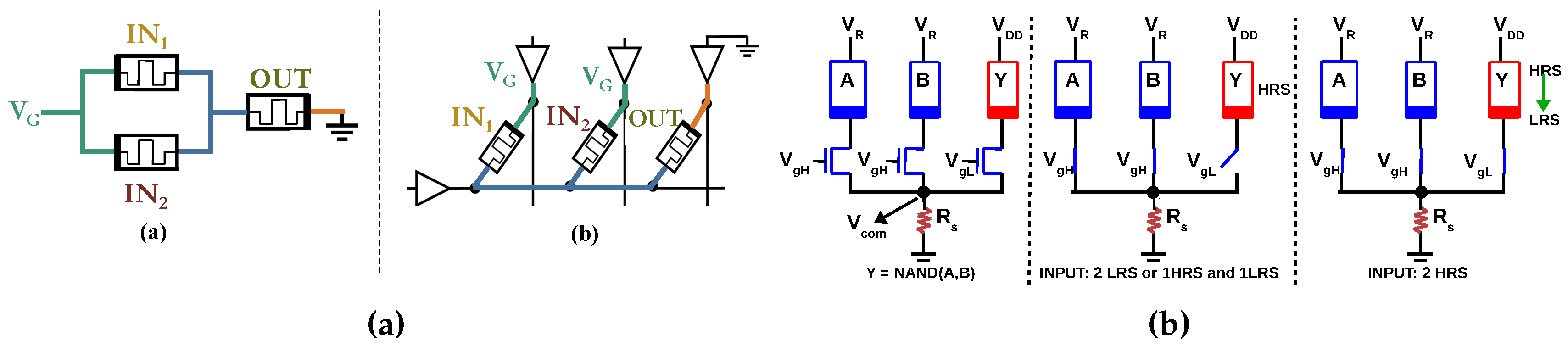

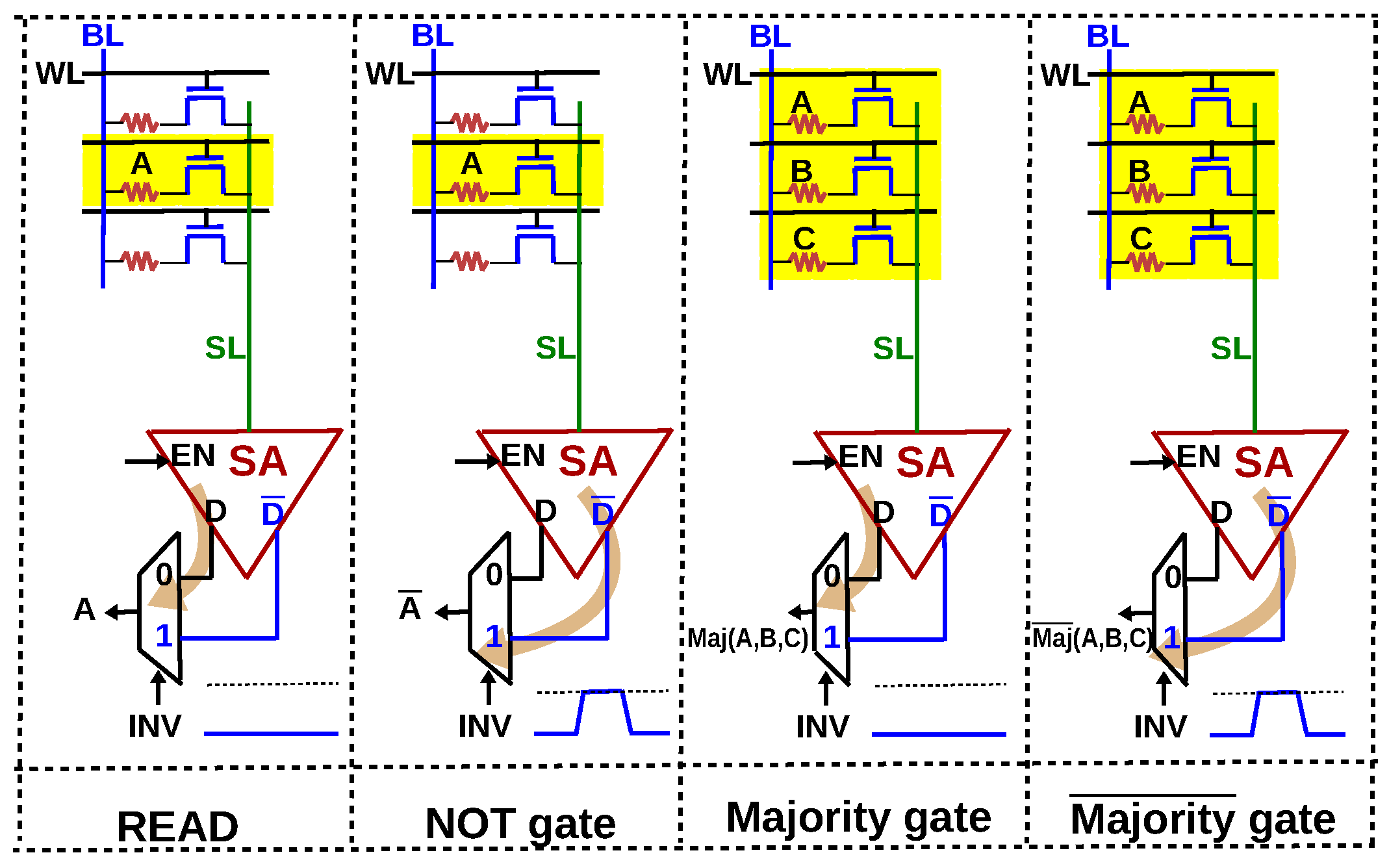

2.1. Majority Gate: Principle of Operation and Validation

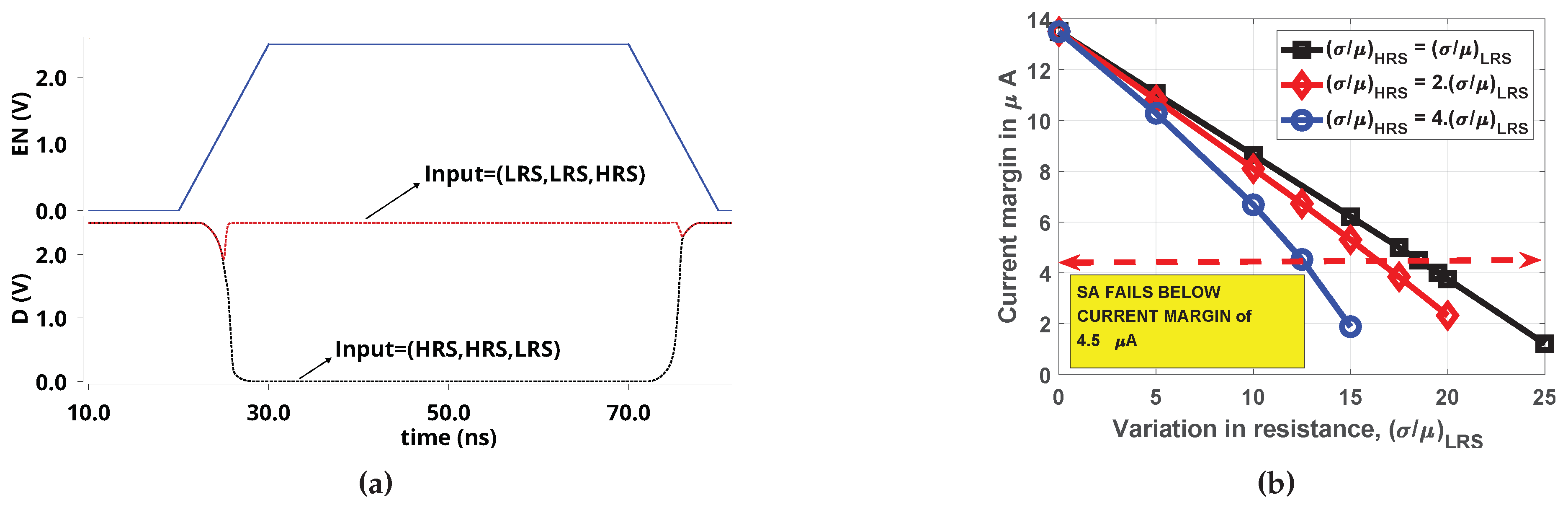

2.2. Sensing Methodology

2.3. Adapting the Majority Gate to Other RRAM Technologies

3. Framework to Compute in 1T–1R Array

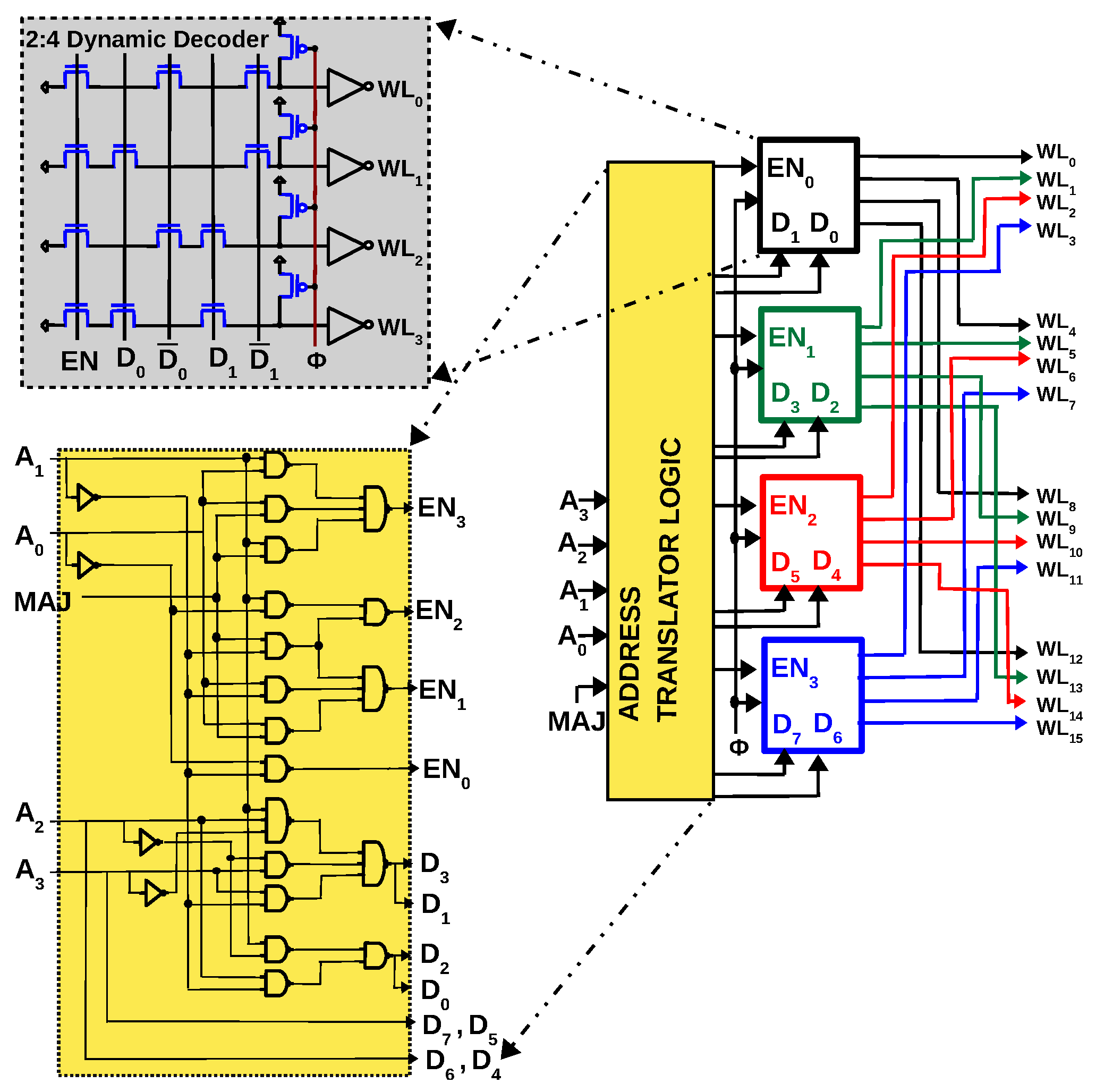

3.1. Multi-Row Decoder Design

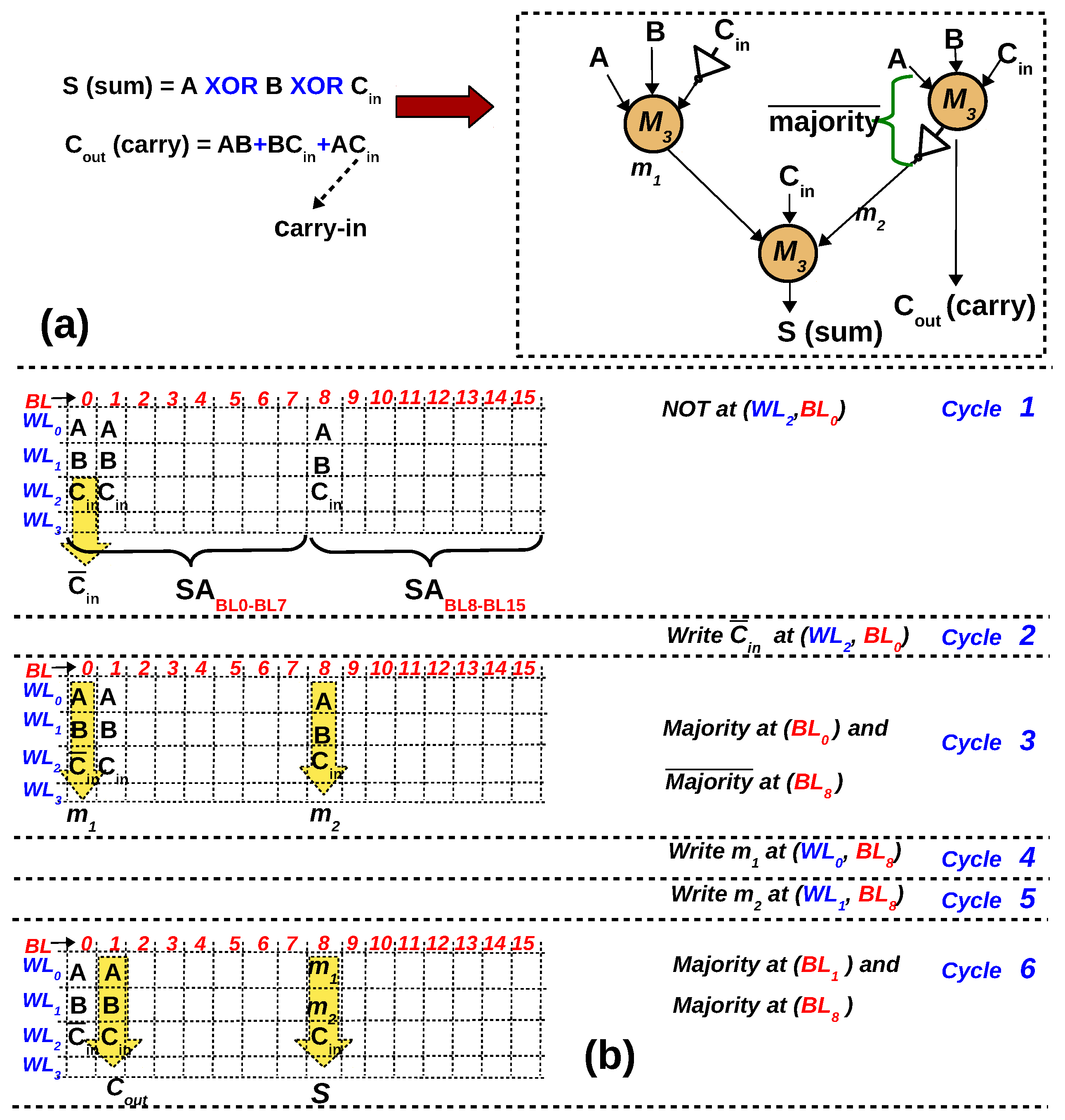

3.2. Functional Completeness and One-Bit Full Adder

3.3. Comparison with Other In-Memory Adders

4. Conclusions

Funding

Acknowledgments

Conflicts of Interest

References

- Molas, G.; Harrand, M.; Nail, C.; Blaise, P. 9—Advances in oxide-based conductive bridge memory (CBRAM) technology for computing systems. In Advances in Non-Volatile Memory and Storage Technology, 2nd ed.; Woodhead Publishing Series in Electronic and Optical Materials; Magyari-Köpe, B., Nishi, Y., Eds.; Woodhead Publishing: Cambridge, UK, 2019; pp. 321–364. [Google Scholar]

- Boukhobza, J.; Rubini, S.; Chen, R.; Shao, Z. Emerging NVM: A Survey on Architectural Integration and Research Challenges. ACM Trans. Des. Autom. Electron. Syst. 2017, 23. [Google Scholar] [CrossRef]

- Talati, N.; Ben-Hur, R.; Wald, N.; Haj-Ali, A.; Reuben, J.; Kvatinsky, S. mMPU—A Real Processing-in-Memory Architecture to Combat the von Neumann Bottleneck. In Applications of Emerging Memory Technology: Beyond Storage; Suri, M., Ed.; Springer: Singapore, 2020; pp. 191–213. [Google Scholar] [CrossRef]

- Kvatinsky, S.; Satat, G.; Wald, N.; Friedman, E.G.; Kolodny, A.; Weiser, U.C. Memristor-Based Material Implication (IMPLY) Logic: Design Principles and Methodologies. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2014, 22, 2054–2066. [Google Scholar] [CrossRef]

- Amarú, L.; Gaillardon, P.E.; Micheli, G.D. Majority-Inverter Graph: A New Paradigm for Logic Optimization. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2016, 35, 806–819. [Google Scholar] [CrossRef]

- Hur, R.B.; Wald, N.; Talati, N.; Kvatinsky, S. SIMPLE MAGIC: Synthesis and In-memory Mapping of Logic Execution for Memristor-aided Logic. In Proceedings of the 36th International Conference on Computer-Aided Design, ICCAD ’17, Irvine, CA, USA, 12–16 November 2017; pp. 225–232. [Google Scholar]

- Shen, W.; Huang, P.; Fan, M.; Han, R.; Zhou, Z.; Gao, B.; Wu, H.; Qian, H.; Liu, L.; Liu, X.; et al. Stateful Logic Operations in One-Transistor-One- Resistor Resistive Random Access Memory Array. IEEE Electron Device Lett. 2019, 40, 1538–1541. [Google Scholar] [CrossRef]

- Reuben, J.; Ben-Hur, R.; Wald, N.; Talati, N.; Ali, A.; Gaillardon, P.E.; Kvatinsky, S. Memristive Logic: A Framework for Evaluation and Comparison. In Proceedings of the Power And Timing Modeling, Optimization and Simulation (PATMOS), Thessaloniki, Greece, 25–27 September 2017; pp. 1–8. [Google Scholar]

- Shirinzadeh, S.; Soeken, M.; Gaillardon, P.; Drechsler, R. Fast logic synthesis for RRAM-based in-memory computing using Majority-Inverter Graphs. In Proceedings of the 2016 Design, Automation Test in Europe Conference Exhibition (DATE), Dresden, Germany, 14–18 March 2016; pp. 948–953. [Google Scholar]

- Li, S.; Xu, C.; Zou, Q.; Zhao, J.; Lu, Y.; Xie, Y. Pinatubo: A Processing-in-memory Architecture for Bulk Bitwise Operations in Emerging Non-volatile Memories. In Proceedings of the 53rd Annual Design Automation Conference; ACM: New York, NY, USA, 2016; pp. 173:1–173:6. [Google Scholar] [CrossRef]

- Ielmini, D.; Wong, H.S.P. In-memory computing with resistive switching devices. Nat. Electron. 2018, 1, 333–343. [Google Scholar] [CrossRef]

- Reuben, J.; Talati, N.; Wald, N.; Ben-Hur, R.; Ali, A.H.; Gaillardon, P.E.; Kvatinsky, S. A Taxonomy and Evaluation Framework for Memristive Logic. In Handbook of Memristor Networks; Chua, L., Sirakoulis, G.C., Adamatzky, A., Eds.; Springer International Publishing: Cham, Switzerland, 2019; pp. 1065–1099. [Google Scholar] [CrossRef]

- Reuben, J.; Fey, D.; Wenger, C. A Modeling Methodology for Resistive RAM Based on Stanford-PKU Model With Extended Multilevel Capability. IEEE Trans. Nanotechnol. 2019, 18, 647–656. [Google Scholar] [CrossRef]

- Bae, W.; Yoon, K.J.; Hwang, C.S.; Jeong, D.K. A crossbar resistance switching memory readout scheme with sneak current cancellation based on a two-port current-mode sensing. Nanotechnology 2016, 27, 485201. [Google Scholar] [CrossRef] [PubMed]

- Bae, W.; Yoon, K.J.; Song, T.; Nikolić, B. A Variation-Tolerant, Sneak-Current-Compensated Readout Scheme for Cross-Point Memory Based on Two-Port Sensing Technique. IEEE Trans. Circuits Syst. II Express Briefs 2018, 65, 1839–1843. [Google Scholar] [CrossRef]

- Prakash, A.; Hwang, H. Multilevel Cell Storage and Resistance Variability in Resistive Random Access Memory. Phys. Sci. Rev. 2016, 1. [Google Scholar] [CrossRef]

- Ambrosi, E.; Bricalli, A.; Laudato, M.; Ielmini, D. Impact of oxide and electrode materials on the switching characteristics of oxide ReRAM devices. Faraday Discuss. 2018. [Google Scholar] [CrossRef] [PubMed]

- Adam, G.C.; Khiat, A.; Prodromakis, T. Challenges hindering memristive neuromorphic hardware from going mainstream. Nat. Commun. 2018, 9. [Google Scholar] [CrossRef] [PubMed]

- Reuben, J.; Fey, D. A Time-based Sensing Scheme for Multi-level Cell (MLC) Resistive RAM. In Proceedings of the 2019 IEEE Nordic Circuits and Systems Conference (NORCAS): NORCHIP and International Symposium of System-on-Chip (SoC), Helsinki, Finland, 29–30 October 2019; pp. 1–6. [Google Scholar] [CrossRef]

- Parmar, V.; Suri, M. Exploiting Variability in Resistive Memory Devices for Cognitive Systems. In Advances in Neuromorphic Hardware Exploiting Emerging Nanoscale Devices; Suri, M., Ed.; Springer: New Delhi, India, 2017; pp. 175–195. [Google Scholar] [CrossRef]

- Zhang, R.; Walus, K.; Wang, W.; Jullien, G.A. A method of majority logic reduction for quantum cellular automata. IEEE Trans. Nanotechnol. 2004, 3, 443–450. [Google Scholar] [CrossRef]

- Amarú, L.; Gaillardon, P.; De Micheli, G. Boolean logic optimization in Majority-Inverter Graphs. In Proceedings of the 2015 52nd ACM/EDAC/IEEE Design Automation Conference (DAC), San Francisco, CA, USA, 8–12 June 2015; pp. 1–6. [Google Scholar] [CrossRef]

- Sheu, S.; Cheng, K.; Chang, M.; Chiang, P.; Lin, W.; Lee, H.; Chen, P.; Chen, Y.; Wu, T.; Chen, F.T.; et al. Fast-Write Resistive RAM (RRAM) for Embedded Applications. IEEE Des. Test Comput. 2011, 28, 64–71. [Google Scholar] [CrossRef]

- Rohani, S.G.; Taherinejad, N.; Radakovits, D. A Semiparallel Full-Adder in IMPLY Logic. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2019, 1–5. [Google Scholar] [CrossRef]

- Siemon, A.; Drabinski, R.; Schultis, M.J.; Hu, X.; Linn, E.; Heittmann, A.; Waser, R.; Querlioz, D.; Menzel, S.; Friedman, J.S. Stateful Three-Input Logic with Memristive Switches. Sci. Rep. 2019, 9, 14618. [Google Scholar] [CrossRef] [PubMed]

- Cheng, L.; Zhang, M.Y.; Li, Y.; Zhou, Y.X.; Wang, Z.R.; Hu, S.Y.; Long, S.B.; Liu, M.; Miao, X.S. Reprogrammable logic in memristive crossbar for in-memory computing. J. Phys. D Appl. Phys. 2017, 50. [Google Scholar] [CrossRef]

- Huang, P.; Kang, J.; Zhao, Y.; Chen, S.; Han, R.; Zhou, Z.; Chen, Z.; Ma, W.; Li, M.; Liu, L.; et al. Reconfigurable Nonvolatile Logic Operations in Resistance Switching Crossbar Array for Large-Scale Circuits. Adv. Mater. 2016, 28, 9758–9764. [Google Scholar] [CrossRef] [PubMed]

| A | B | C | |||

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 4.5 A | 4.27 A |

| 0 | 0 | 1 | 0 | 18 A | 17.54 A |

| 0 | 1 | 0 | 0 | 18 A | 17.54 A |

| 0 | 1 | 1 | 1 | 31.5 A | 30.75 A |

| 1 | 0 | 0 | 0 | 18 A | 17.54 A |

| 1 | 0 | 1 | 1 | 31.5 A | 30.75 A |

| 1 | 1 | 0 | 1 | 31.5 A | 30.75 A |

| 1 | 1 | 1 | 1 | 45 A | 44.03 A |

| Memory/Logic Operation | WL | BL | SL | EN(Sense Amplifier) | ||

|---|---|---|---|---|---|---|

| READ | single row activated | connected to SA | 1 | 0 | 0 | |

| NOT | single row activated | connected to SA | 1 | 1 | 0 | |

| Majority | three rows activated | /3 | connected to SA | 1 | 0 | 1 |

| three rows activated | /3 | connected to SA | 1 | 1 | 1 | |

| WRITE ‘1’ | single row activated | grounded | 0 | 0 | 0 | |

| WRITE ‘0’ | single row activated | grounded | 0 | 0 | 0 |

© 2020 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Reuben, J. Binary Addition in Resistance Switching Memory Array by Sensing Majority. Micromachines 2020, 11, 496. https://doi.org/10.3390/mi11050496

Reuben J. Binary Addition in Resistance Switching Memory Array by Sensing Majority. Micromachines. 2020; 11(5):496. https://doi.org/10.3390/mi11050496

Chicago/Turabian StyleReuben, John. 2020. "Binary Addition in Resistance Switching Memory Array by Sensing Majority" Micromachines 11, no. 5: 496. https://doi.org/10.3390/mi11050496

APA StyleReuben, J. (2020). Binary Addition in Resistance Switching Memory Array by Sensing Majority. Micromachines, 11(5), 496. https://doi.org/10.3390/mi11050496