Design and Control of Novel Single-Phase Multilevel Voltage Inverter Using MPC Controller

Abstract

:1. Introduction

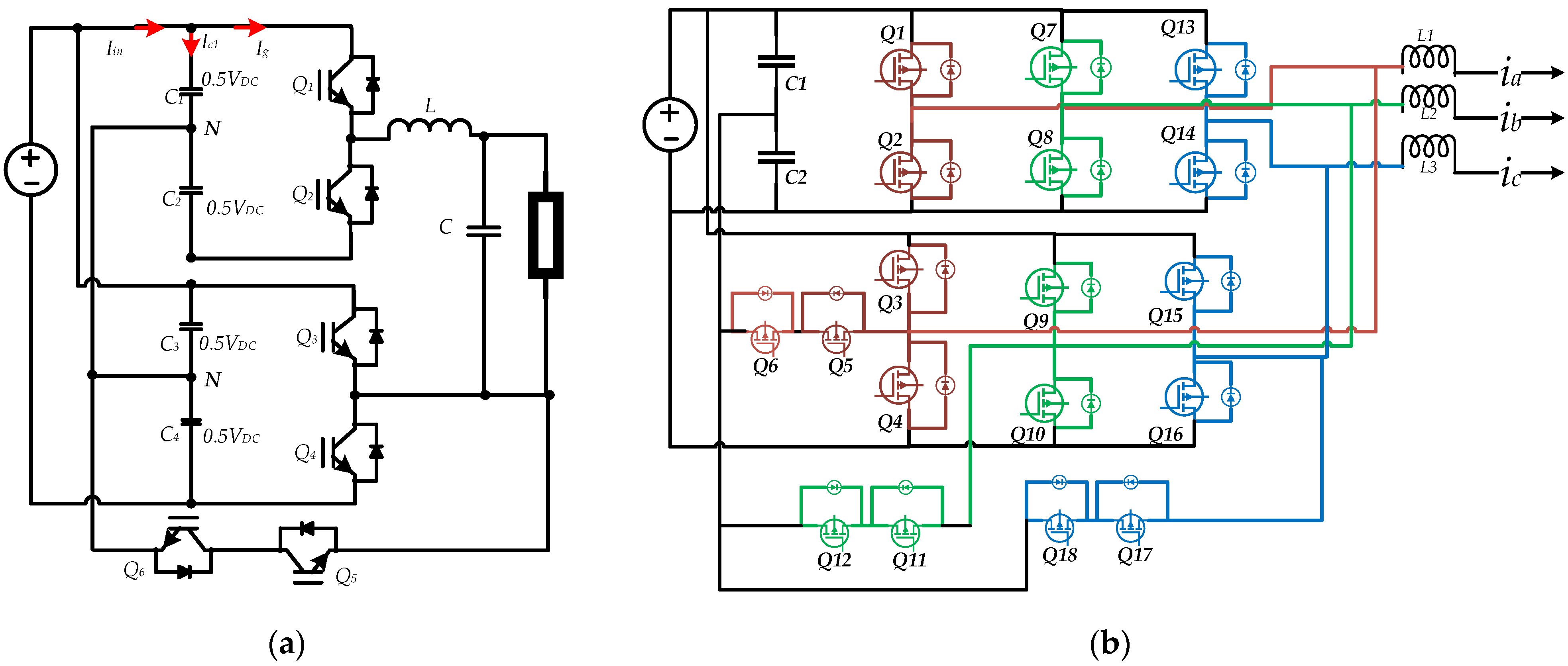

2. Proposed Topology

2.1. Switching State Analysis

- (1)

- State-1

- (2)

- State-2

- (3)

- State-3

- (4)

- State-4

- (5)

- State-5

- (6)

- State-6

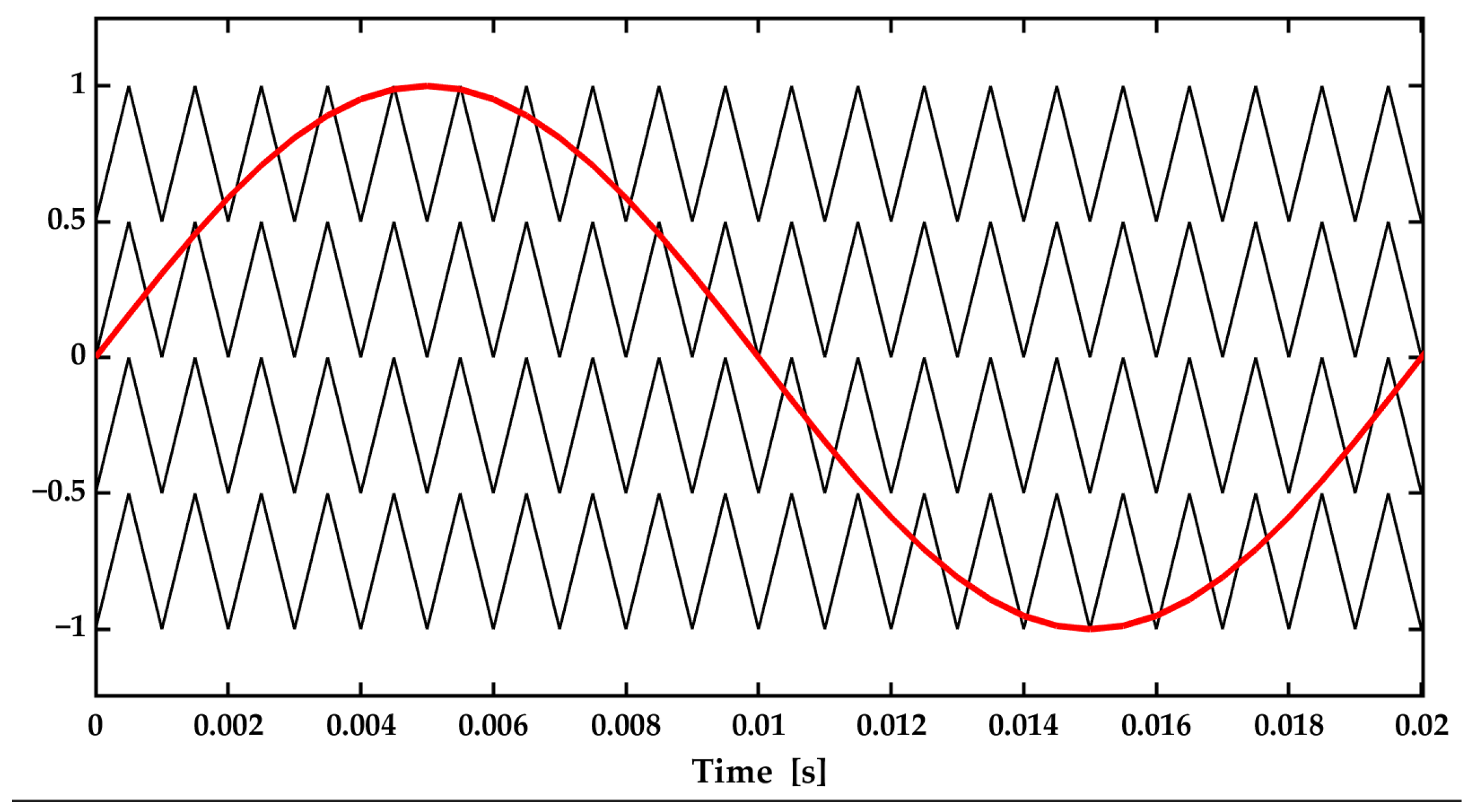

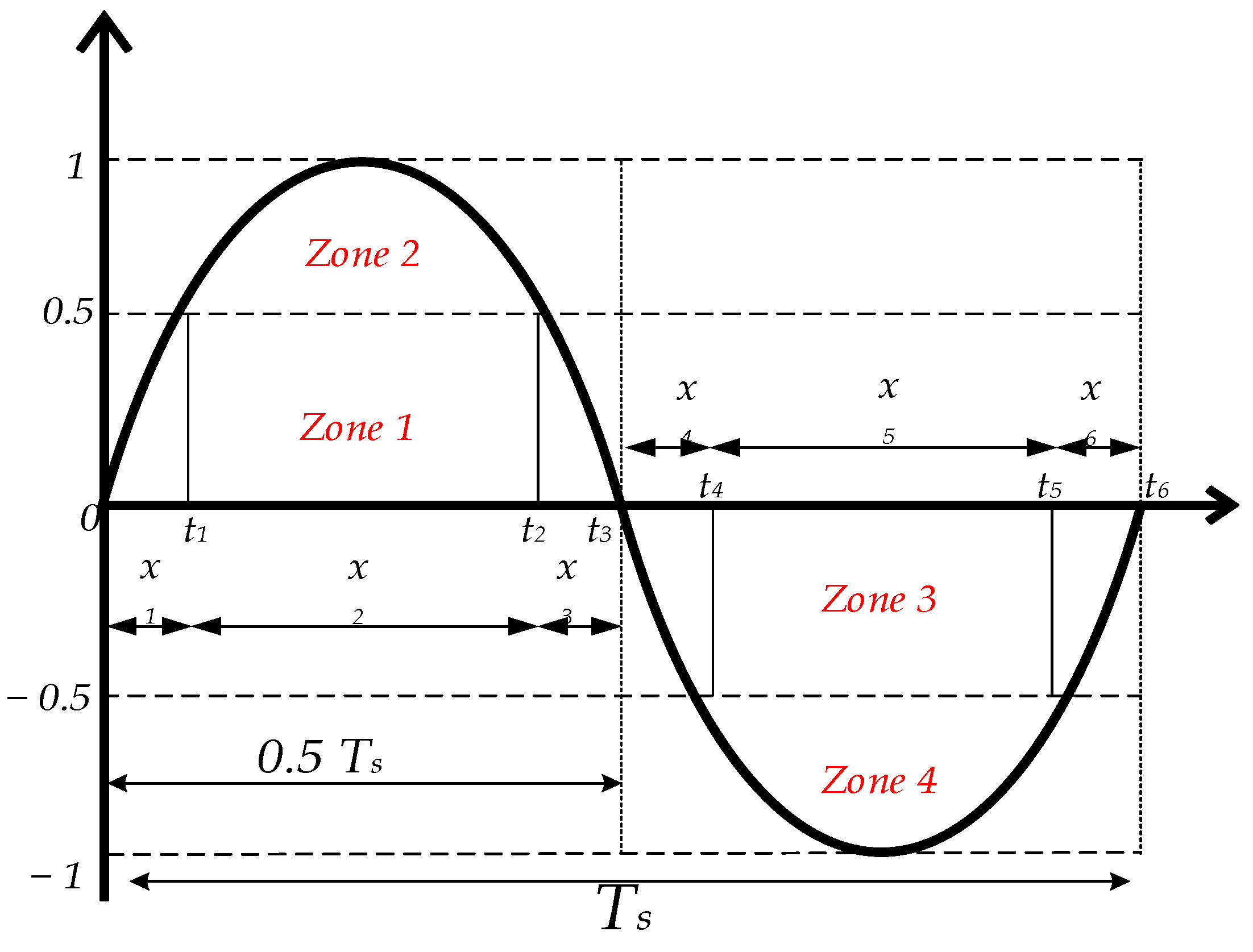

2.2. Controller Design for 5-Level Proposed Inverter

- The switching signal oscillates between states 2 and 6 in the first zone of the modulation wave.

- In the second region of the modulation wave, states 1 and 2 are used to form the switching signal.

- The switching signal produced in the third section oscillates between states 4 and 5.

- In the final portion of the modulation wave, signals will oscillate between states 3 and 4 for the generation of gate pulses.

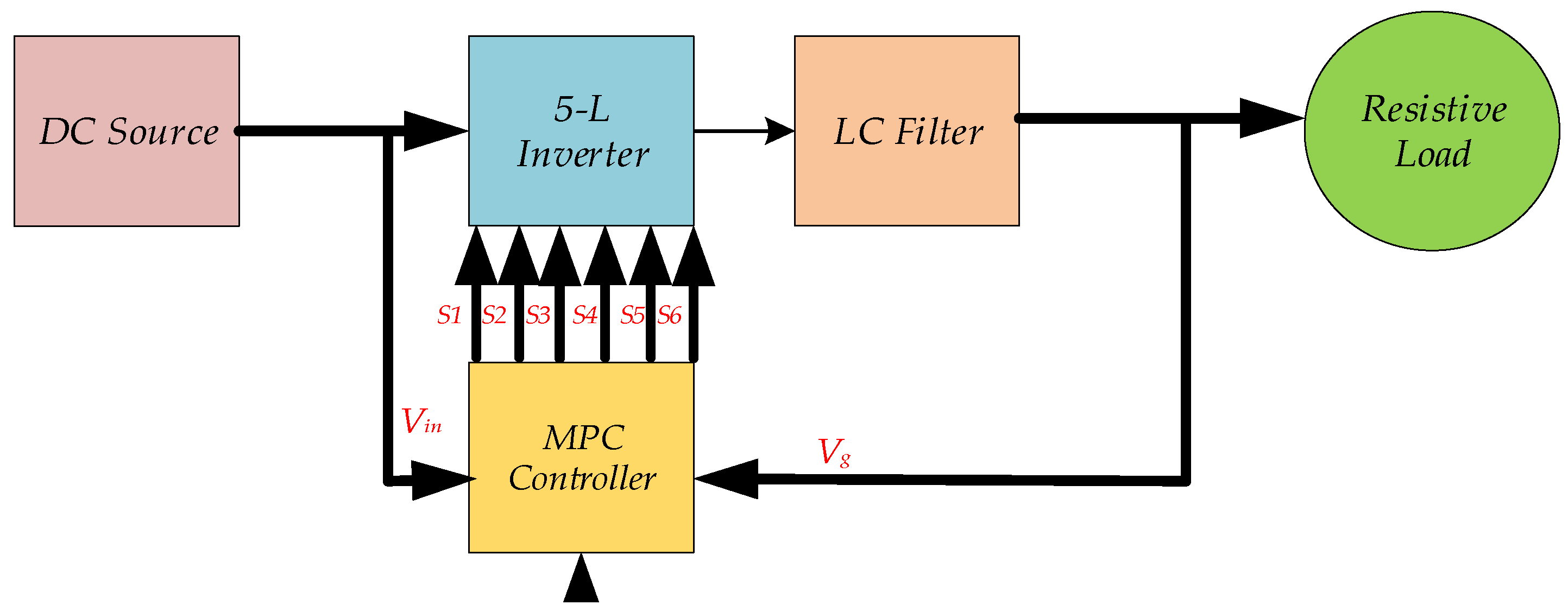

2.3. Inverter Output Controller

3. Loss Analysis

4. Simulation and Experimental Results

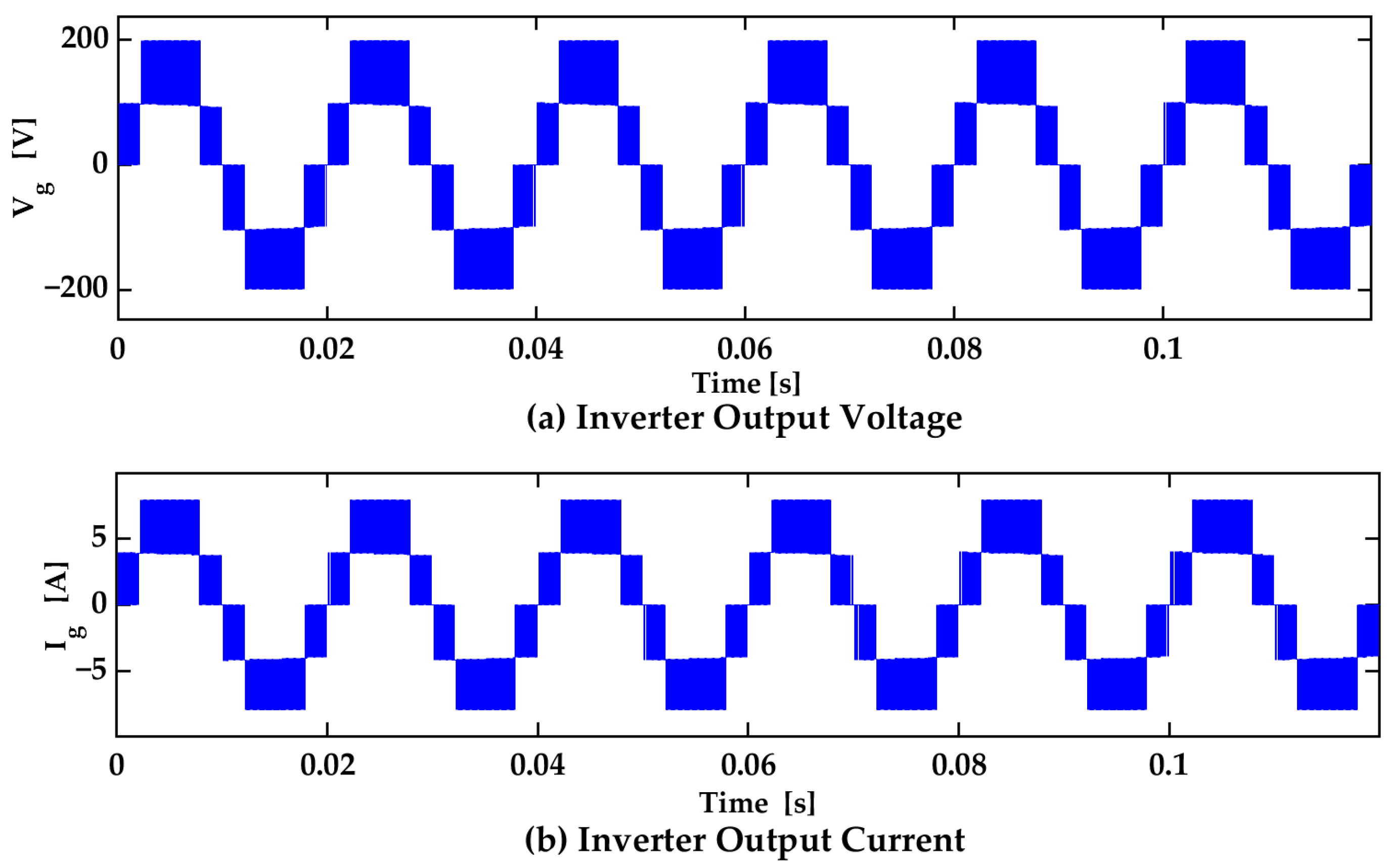

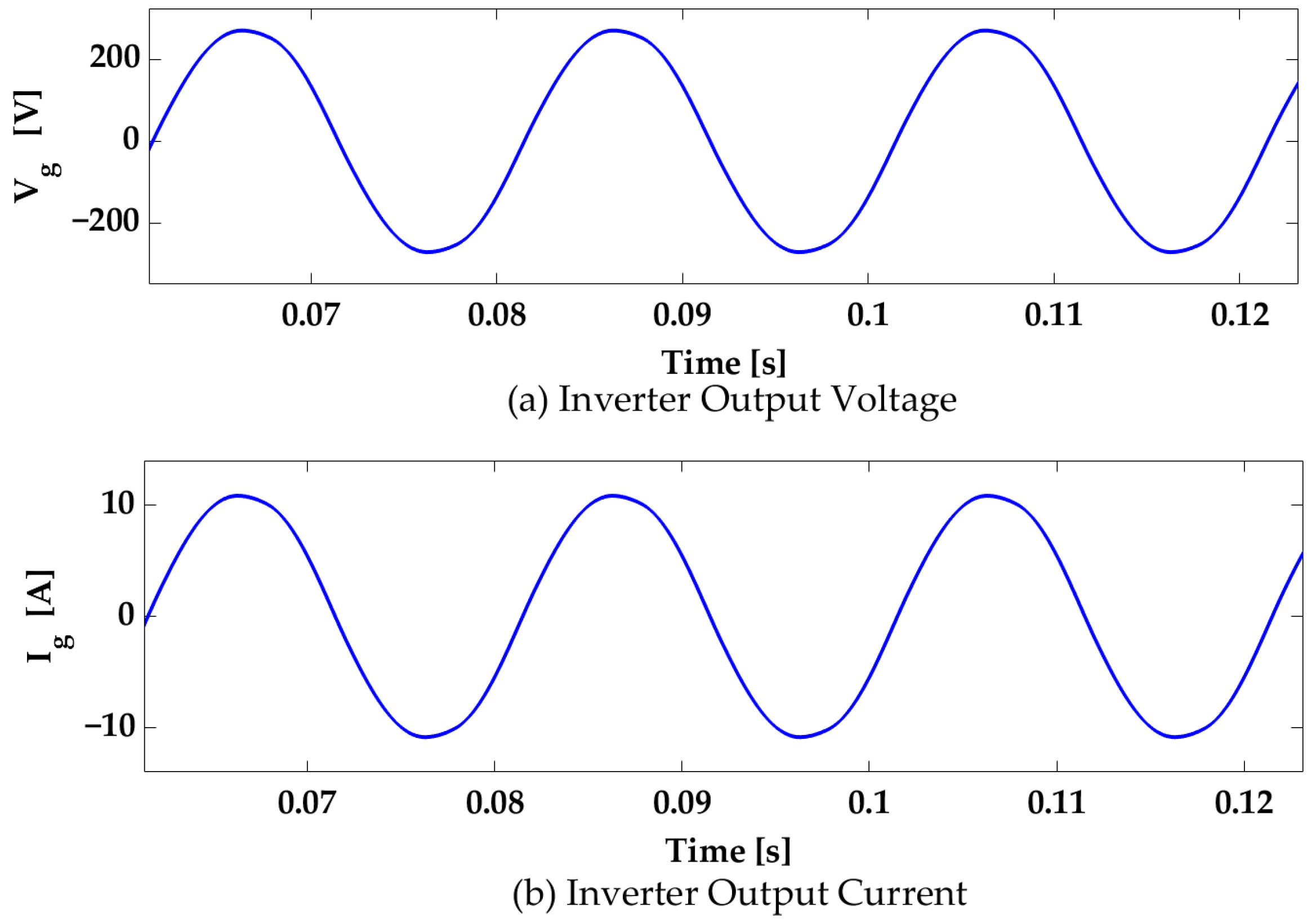

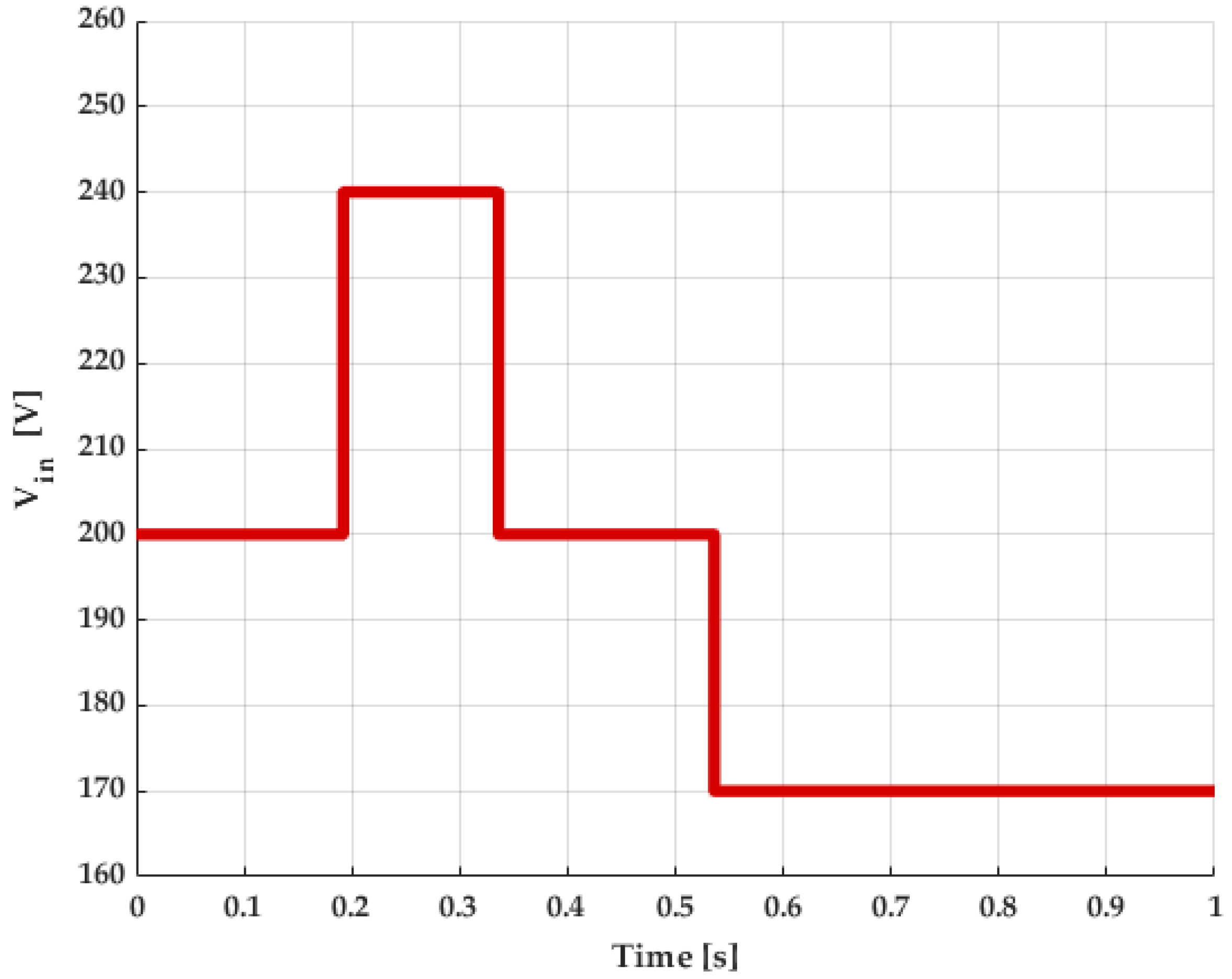

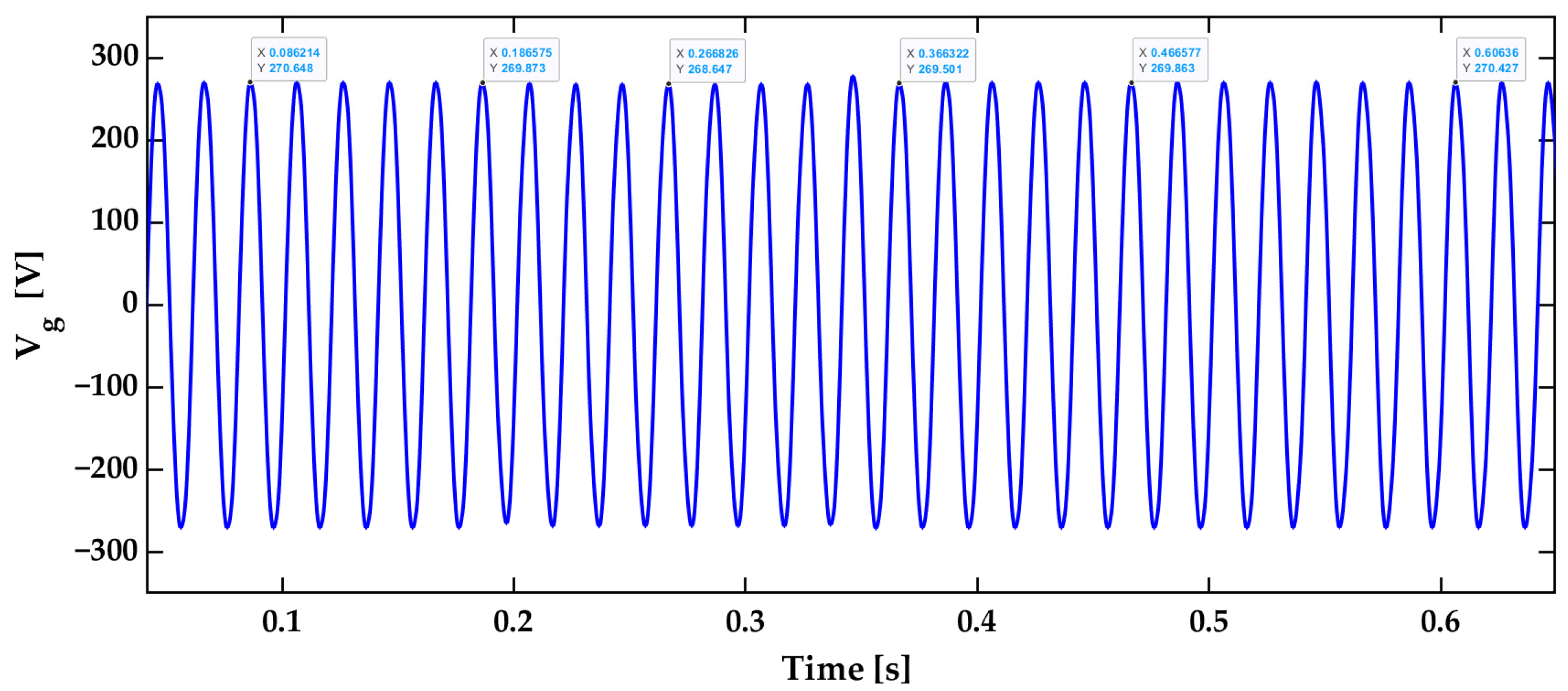

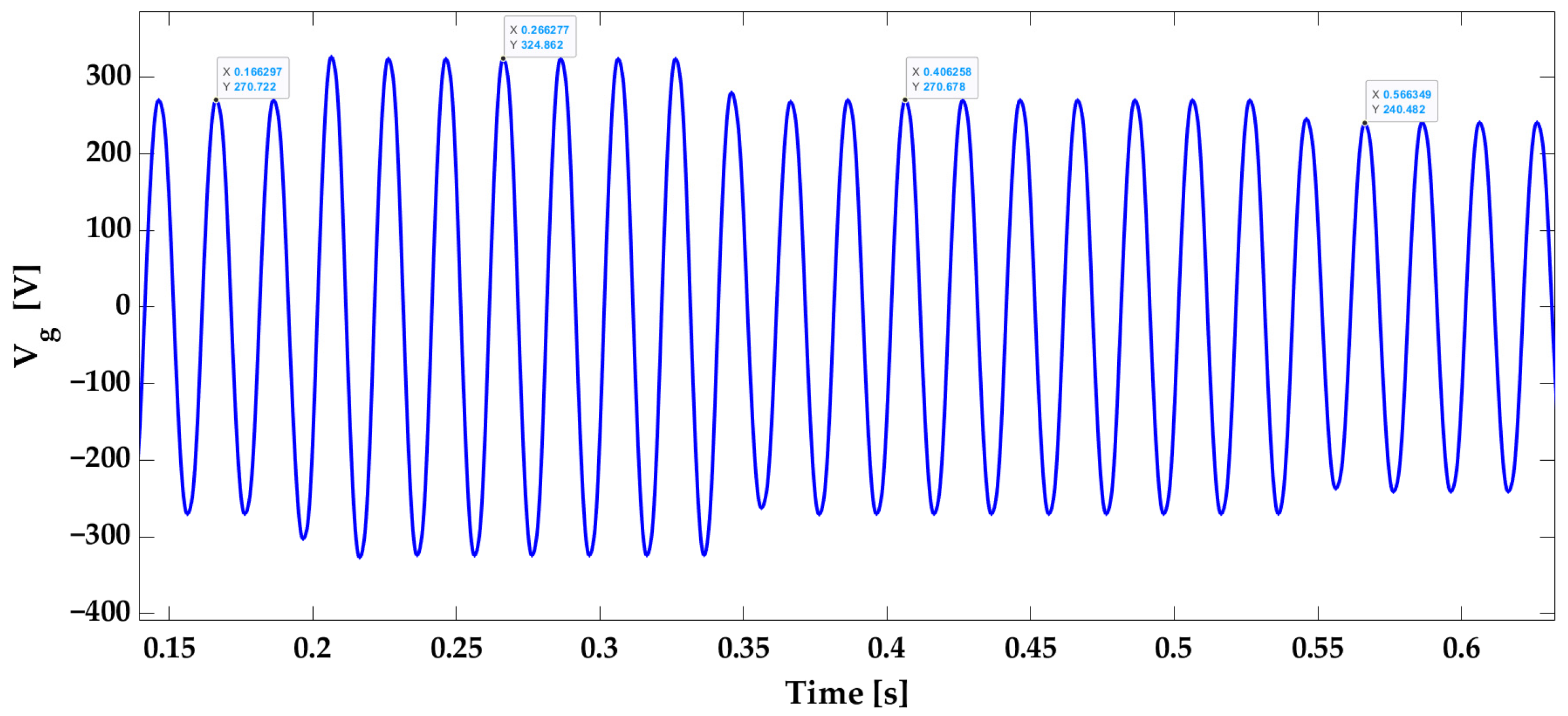

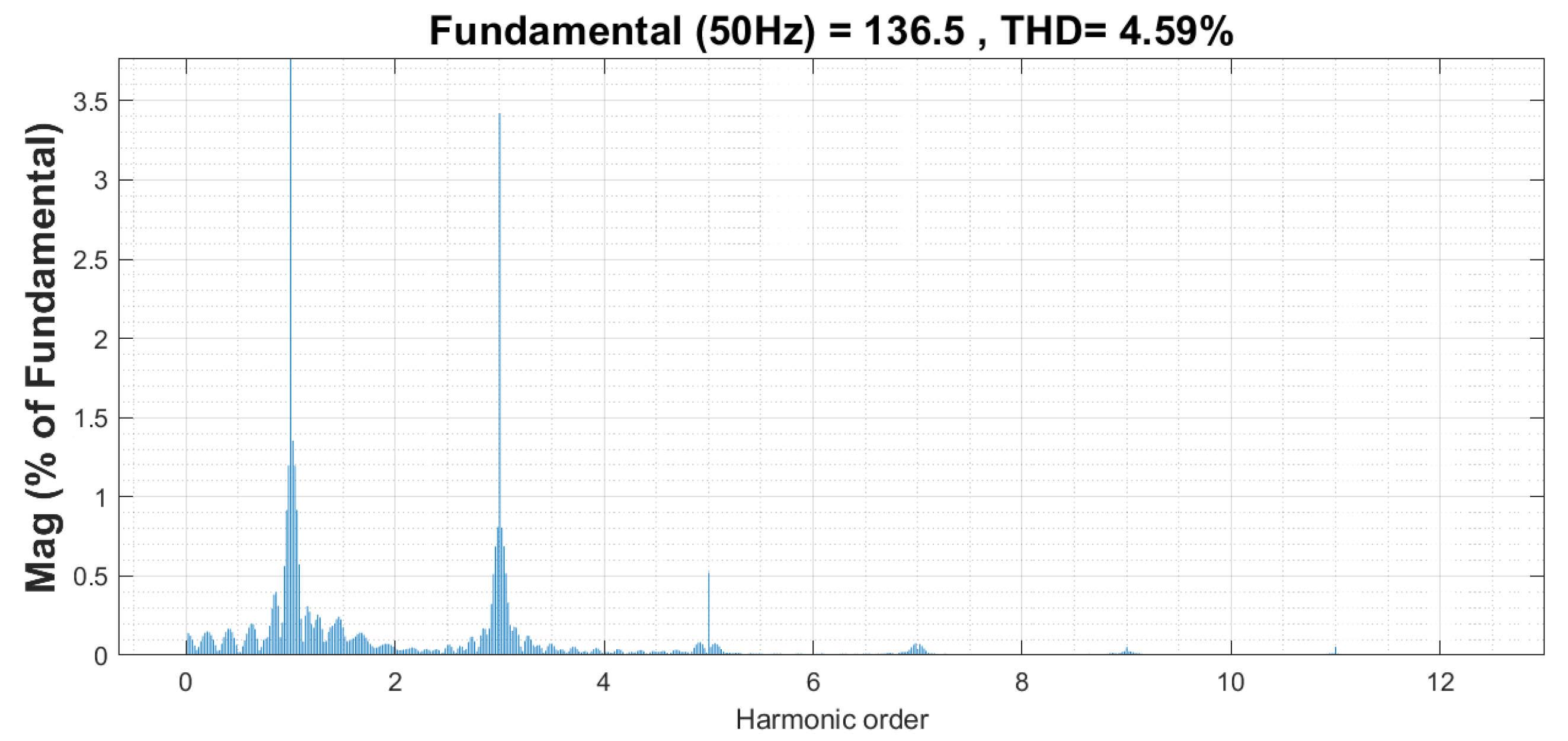

4.1. Simulation Results

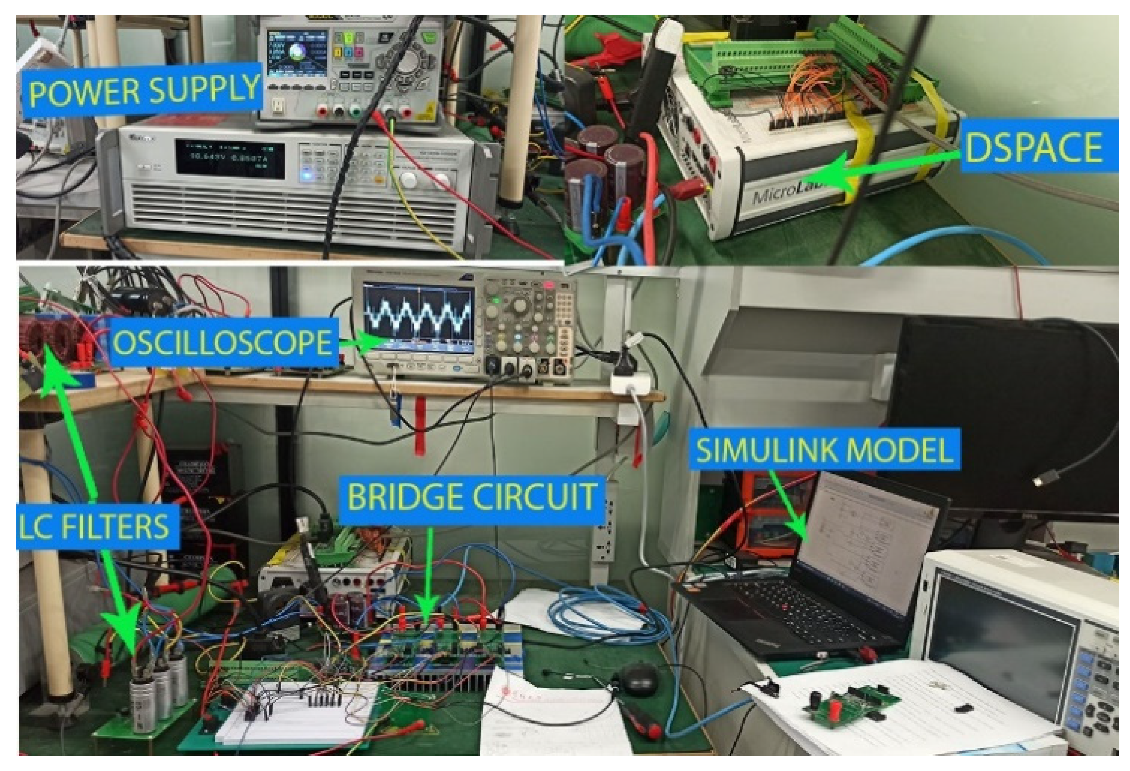

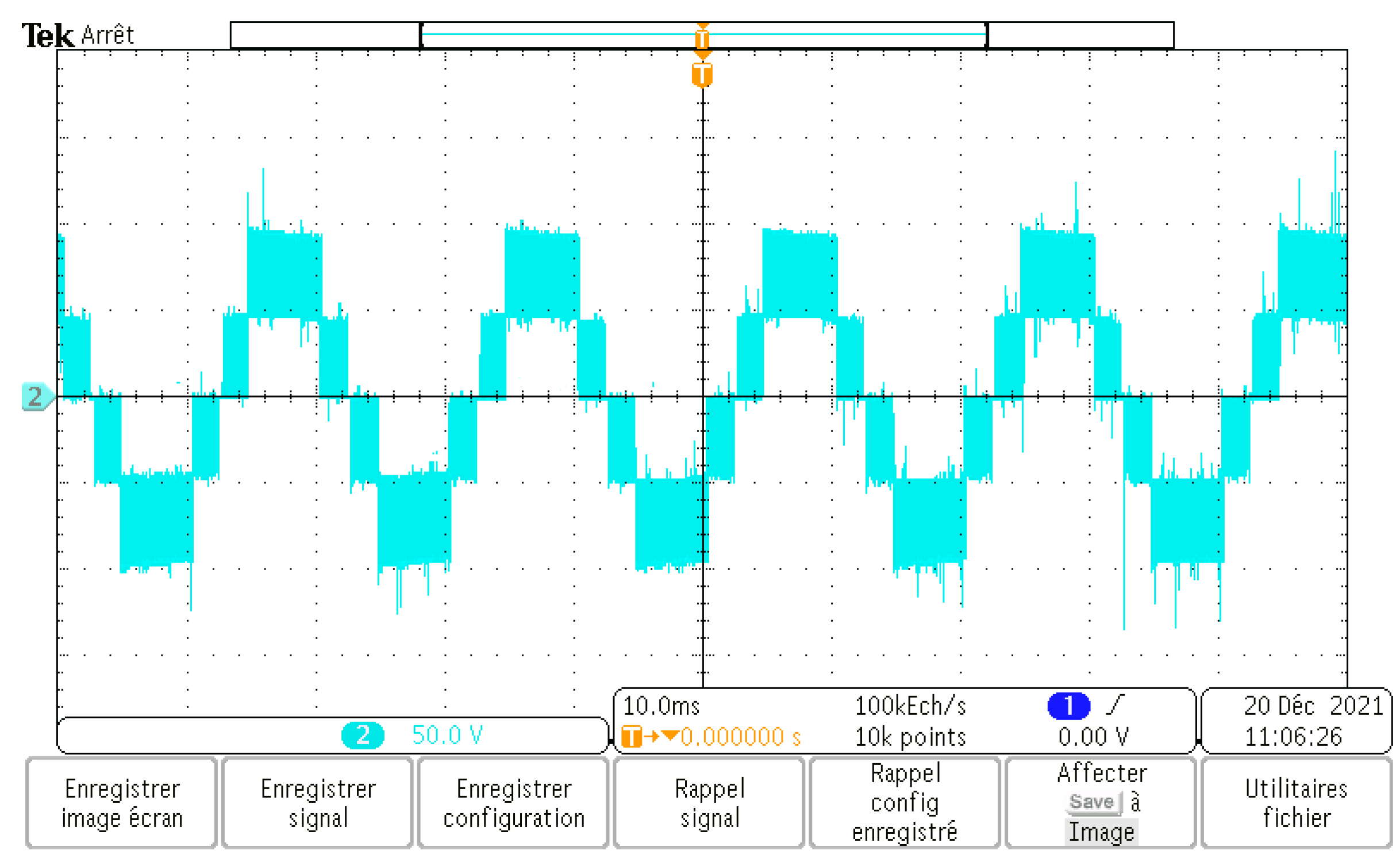

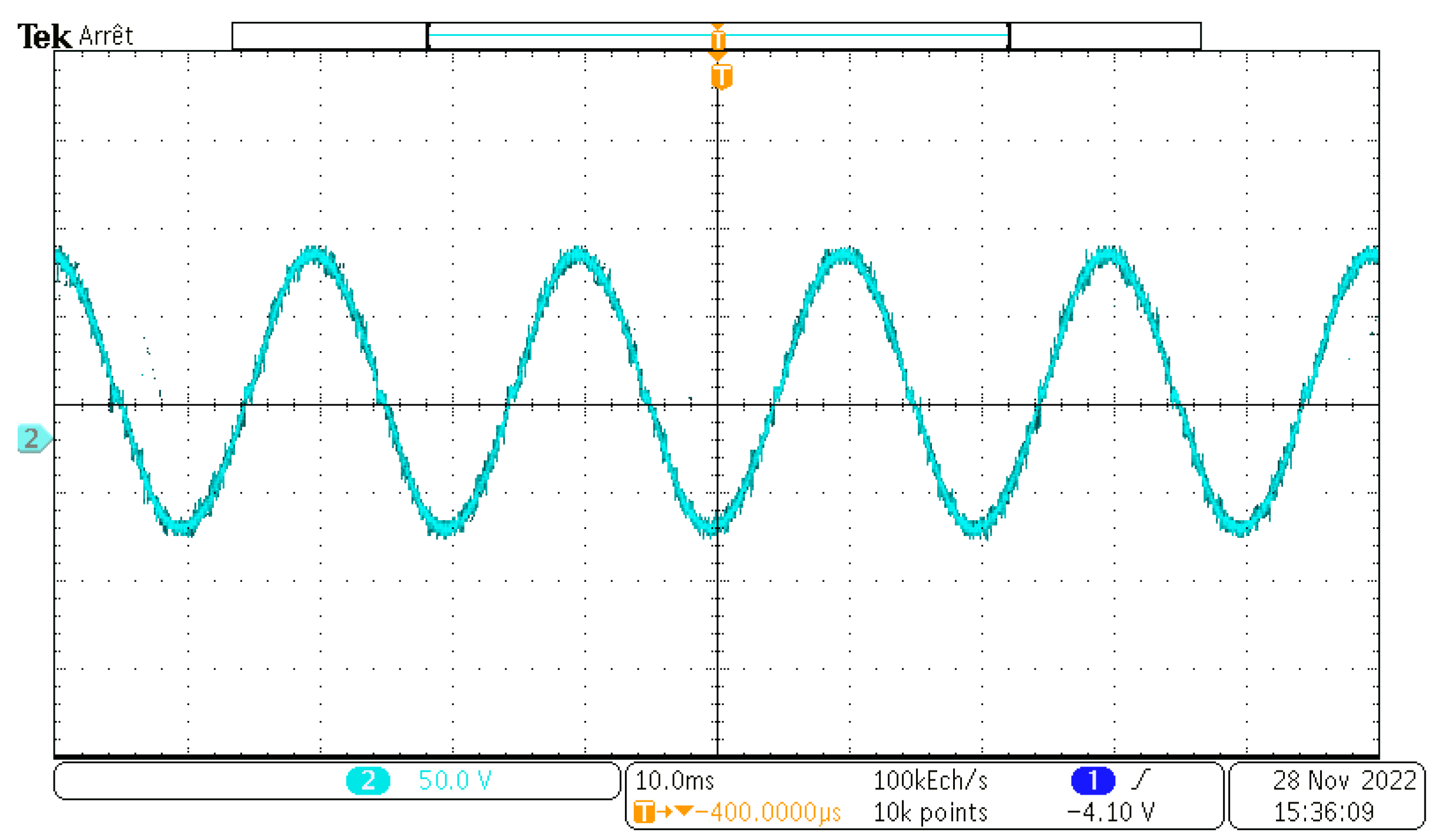

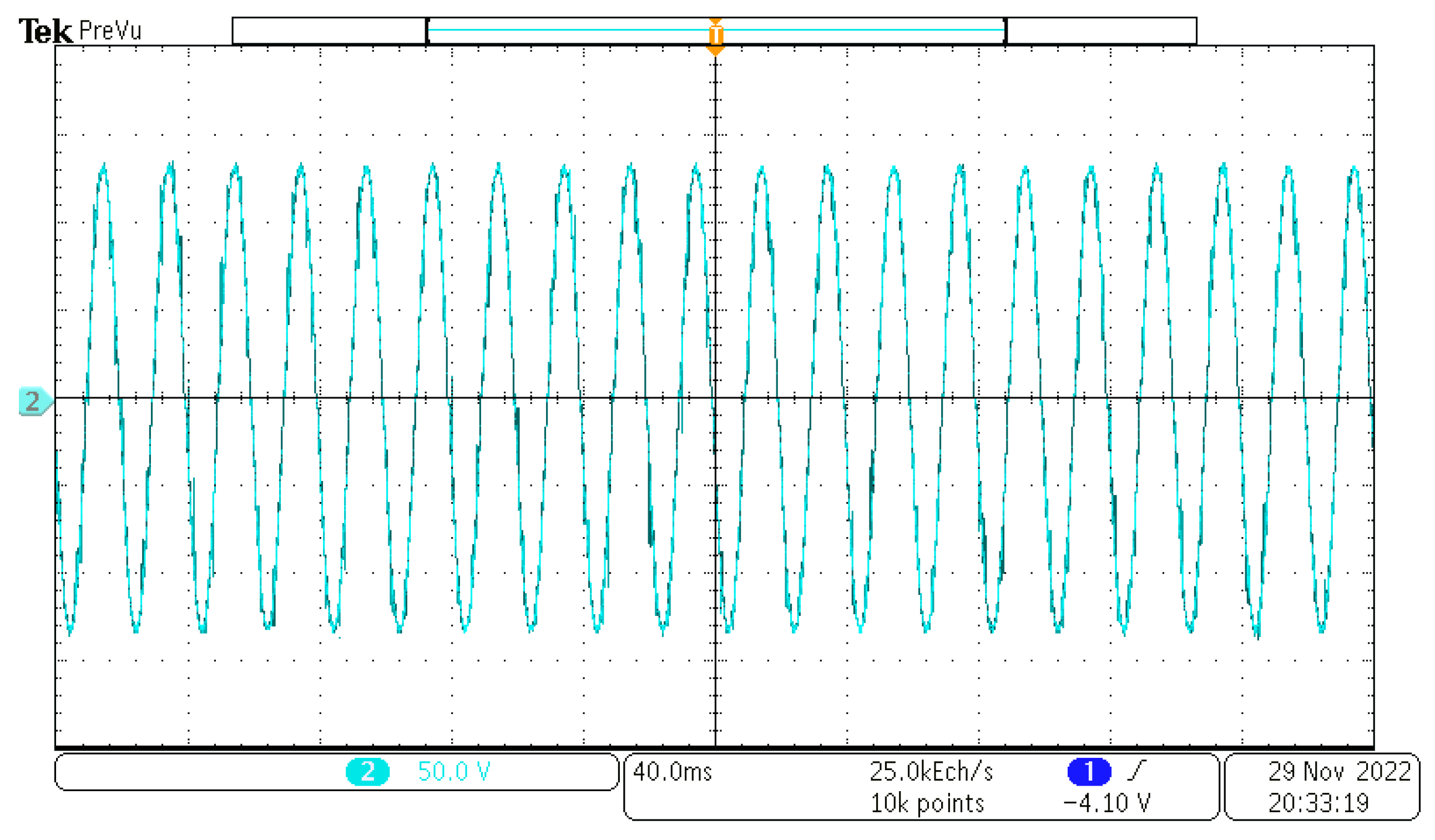

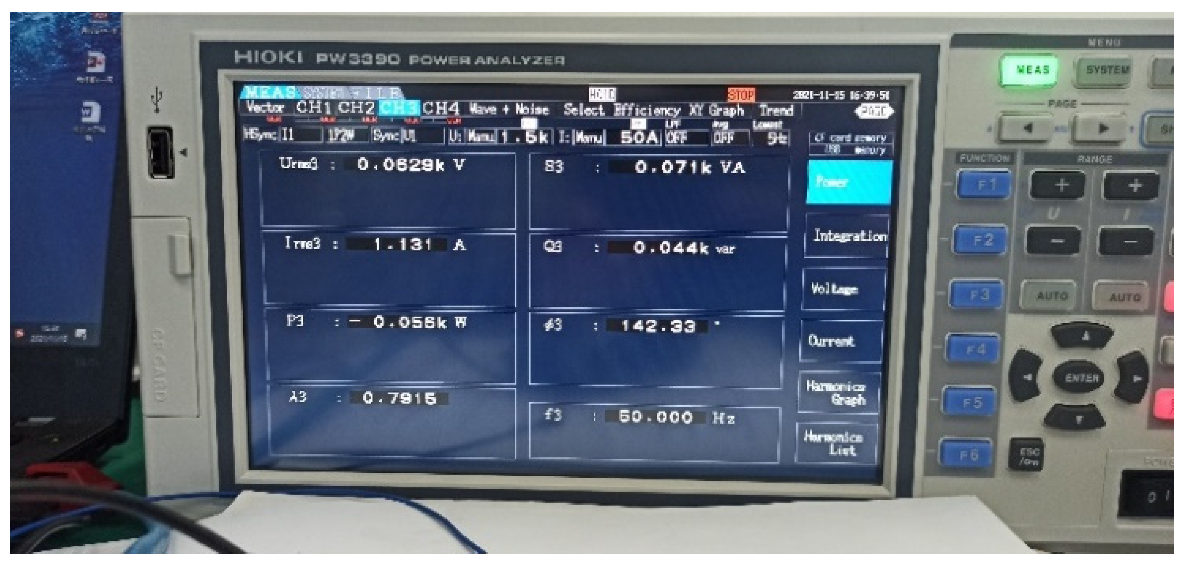

4.2. Experimental Results

4.3. Discussion

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Shi, Y.; Wang, L.; Xie, R.; Shi, Y.; Li, H. A 60-kW 3-kW/kg Five-Level T-Type SiC PV Inverter With 99.2% Peak Efficiency. IEEE Trans. Ind. Electron. 2017, 64, 9144–9154. [Google Scholar] [CrossRef]

- Gultekin, B.; Ermis, M. Cascaded Multilevel Converter-Based Transmission STATCOM: System Design Methodology and Development of a 12 kV ±12 MVAr Power Stage. IEEE Trans. Power Electron. 2013, 28, 4930–4950. [Google Scholar] [CrossRef]

- Wang, H.; Kou, L.; Liu, Y.-F.; Sen, P.C. A Seven-Switch Five-Level Active-Neutral-Point-Clamped Converter and Its Optimal Modulation Strategy. IEEE Trans. Power Electron. 2017, 32, 5146–5161. [Google Scholar] [CrossRef]

- Itoh, Y.K.J.; Itoh, J. Performance Evaluation among Four types of Five-level Topologies using Pareto Front Curves. In Proceedings of the 2013 IEEE Energy Conversion Congress and Exposition, Denver, CO, USA, 15–19 September 2013; pp. 1296–1303. (In English). [Google Scholar]

- Wang, K.; Zheng, Z.; Li, Y.; Liu, K.; Shang, J. Neutral-Point Potential Balancing of a Five-Level Active Neutral-Point-Clamped Inverter. IEEE Trans. Ind. Electron. 2012, 60, 1907–1918. [Google Scholar] [CrossRef]

- Rodriguez, J.; Bernet, S.; Steimer, P.K.; Lizama, I.E. A Survey on Neutral-Point-Clamped Inverters. IEEE Trans. Ind. Electron. 2010, 57, 2219–2230. [Google Scholar] [CrossRef]

- Shuvo, S.; Hossain, E.; Islam, T.; Akib, A.; Padmanaban, S.; Khan, Z.R. Design and Hardware Implementation Considerations of Modified Multilevel Cascaded H-Bridge Inverter for Photovoltaic System. IEEE Access 2019, 7, 16504–16524. [Google Scholar] [CrossRef]

- Kuncham, S.K.; Annamalai, K.; Subrahmanyam, N. A Two-Stage T-Type Hybrid Five-Level Transformerless Inverter for PV Applications. IEEE Trans. Power Electron. 2020, 35, 9510–9521. [Google Scholar] [CrossRef]

- Zhang, L.; Zheng, Z.; Li, C.; Ju, P.; Wu, F.; Gu, Y.; Chen, G. A Si/SiC Hybrid Five-Level Active NPC Inverter with Improved Modulation Scheme. IEEE Trans. Power Electron. 2019, 35, 4835–4846. [Google Scholar] [CrossRef]

- Yu, H.; Chen, B.; Yao, W.; Lu, Z. Hybrid Seven-Level Converter Based on T-Type Converter and H-Bridge Cascaded Under SPWM and SVM. IEEE Trans. Power Electron. 2017, 33, 689–702. [Google Scholar] [CrossRef]

- Baker. High Voltage Converter Circuit. United States, 1980.

- Meynard, T.; Fadel, M.; Aouda, N. Modeling of Multilevel Converters. IEEE Trans. Ind. Electron. 1997, 44, 356–364. [Google Scholar] [CrossRef]

- Zhao, Z.; Zhao, J.; Huang, C. An Improved Capacitor Voltage-Balancing Method for Five-Level Diode-Clamped Converters with High Modulation Index and High Power Factor. IEEE Trans. Power Electron. 2015, 31, 3189–3202. [Google Scholar] [CrossRef]

- Meynard, T.A.; Foch, H. Multi-Level Conversion High Voltage Choppers and Voltage Source Inverters. In Proceedings of the PESC '92 Record. 23rd Annual IEEE Power Electronics Specialists Conference, Toledo, Spain, 29 June–3 July 1992. [Google Scholar]

- Salinas, F.; Gonzalez, M.A.; Escalante, M.F.; Morales, J.D.L. Control Design Strategy for Flying Capacitor Multilevel Converters Based on Petri Nets. IEEE Trans. Ind. Electron. 2015, 63, 1728–1736. [Google Scholar] [CrossRef]

- Omer, P.; Kumar, J.; Surjan, B.S. A Review on Reduced Switch Count Multilevel Inverter Topologies. IEEE Access 2020, 8, 22281–22302. [Google Scholar] [CrossRef]

- Wu, P.-H.; Chen, Y.-T.; Cheng, P.-T. The Delta-Connected Cascaded H-Bridge Converter Application in Distributed Energy Resources and Fault Ride Through Capability Analysis. IEEE Trans. Ind. Appl. 2017, 53, 4665–4672. [Google Scholar] [CrossRef]

- Schweizer, M.; Kolar, J.W. Design and Implementation of a Highly Efficient Three-Level T-Type Converter for Low-Voltage Applications. IEEE Trans. Power Electron. 2012, 28, 899–907. [Google Scholar] [CrossRef]

- Bruckner, T.; Bernet, S. Loss balancing in three-level voltage source inverters applying active NPC switches. In Proceedings of the 32nd Annual Power Electronics Specialists Conference, Vancouver, BC, Canada, 17–21 June 2001; Volume 1–4, pp. 1135–1140. (In English). [Google Scholar]

- Bharath, G.V.; Hota, A.; Agarwal, V. A New Family of 1-Five-Level Transformerless Inverters for Solar PV Applications. IEEE Trans. Ind. Appl. 2019, 56, 561–569. [Google Scholar] [CrossRef]

- Davis, T.T.; Dey, A. A Neutral Point Voltage Balancing Scheme with Improved Transient Performance for 5-Level ANPC and TNPC Inverters. IEEE Trans. Power Electron. 2019, 34, 12513–12523. [Google Scholar] [CrossRef]

- Vujacic, M.; Dordevic, O.; Grandi, G. Evaluation of DC-Link Voltage Switching Ripple in Multiphase PWM Voltage Source Inverters. IEEE Trans. Power Electron. 2019, 35, 3478–3490. [Google Scholar] [CrossRef]

- Zhang, Y.; Qu, C. Model Predictive Direct Power Control of PWM Rectifiers Under Unbalanced Network Conditions. IEEE Trans. Ind. Electron. 2015, 62, 4011–4022. [Google Scholar] [CrossRef]

- Siddique, M.D.; Bhaskar, M.S.; Rawa, M.; Mekhilef, S.; Memon, M.A.; Padmanaban, S.; Almakhles, D.J.; Subramaniam, U. Single-phase hybrid multilevel inverter topology with low switching frequency modulation techniques for lower order harmonic elimination. IET Power Electron. 2020, 13, 4117–4127. [Google Scholar] [CrossRef]

- Bozorgi, A.M.; Gholami-Khesht, H.; Farasat, M.; Mehraeen, S.; Monfared, M. Model Predictive Direct Power Control of Three-Phase Grid-Connected Converters with Fuzzy-Based Duty Cycle Modulation. IEEE Trans. Ind. Appl. 2018, 54, 4875–4885. [Google Scholar] [CrossRef]

- Bouafia, A.; Gaubert, J.-P.; Krim, F. Predictive Direct Power Control of Three-Phase Pulsewidth Modulation (PWM) Rectifier Using Space-Vector Modulation (SVM). IEEE Trans. Power Electron. 2009, 25, 228–236. [Google Scholar] [CrossRef]

- Bouafia, A.; Krim, F.; Gaubert, J.-P. Fuzzy-Logic-Based Switching State Selection for Direct Power Control of Three-Phase PWM Rectifier. IEEE Trans. Ind. Electron. 2009, 56, 1984–1992. [Google Scholar] [CrossRef]

- Khan, S.A.; Guo, Y.; Zhu, J. Model Predictive Observer Based Control for Single-Phase Asymmetrical T-Type AC/DC Power Converter. IEEE Trans. Ind. Appl. 2018, 55, 2033–2044. [Google Scholar] [CrossRef]

- Choi, D.-K.; Lee, K.-B. Dynamic Performance Improvement of AC/DC Converter Using Model Predictive Direct Power Control with Finite Control Set. IEEE Trans. Ind. Electron. 2014, 62, 757–767. [Google Scholar] [CrossRef]

- Grigoletto, F.B. Five-Level Transformerless Inverter for Single-Phase Solar Photovoltaic Applications. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 8, 3411–3422. [Google Scholar] [CrossRef]

- Barzegarkhoo, R.; Siwakoti, Y.P.; Blaabjerg, F. A New Switched-Capacitor Five-Level Inverter Suitable for Transformerless Grid-Connected Applications. IEEE Trans. Power Electron. 2020, 35, 8140–8153. [Google Scholar] [CrossRef]

- Rahul S, A.; Pramanick, S.; Kaarthik, S.; Gopakumar, K.; Blaabjerg, F. Extending the Linear Modulation Range to the Full Base Speed Using a Single DC-Link Multilevel Inverter with Capacitor-Fed H-Bridges for IM Drives. IEEE Trans. Power Electron. 2016, 32, 5450–5458. [Google Scholar] [CrossRef]

- Dao, N.D.; Lee, D.-C. Operation and Control Scheme of a Five-Level Hybrid Inverter for Medium-Voltage Motor Drives. IEEE Trans. Power Electron. 2018, 33, 10178–10187. [Google Scholar] [CrossRef]

- Majumder, M.G.; R, R.; Gopakumar, K.; Umanand, L.; Al-Haddad, K.; Jarzyna, W. A Fault-Tolerant Five-Level Inverter Topology with Reduced Component Count for OEIM Drives. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 9, 961–969. [Google Scholar] [CrossRef]

- Dargahi, V.; Sadigh, A.K.; Corzine, K.A.; Enslin, J.H.; Rodriguez, J.; Blaabjerg, F. A New Control Technique for Improved Active-Neutral-Point-Clamped (I-ANPC) Multilevel Converters Using Logic-Equations Approach. IEEE Trans. Ind. Appl. 2019, 56, 488–497. [Google Scholar] [CrossRef]

| Output (Vo) | Q1 | Q2 | Q3 | Q4 | Q5 | Q6 | |

|---|---|---|---|---|---|---|---|

| State-1 | VDC | 1 | 0 | 0 | 1 | 0 | 0 |

| State-2 | VDC/2 | 1 | 0 | 0 | 0 | 0 | 1 |

| State-3 | −VDC | 0 | 1 | 1 | 0 | 0 | 0 |

| State-4 | −VDC/2 | 0 | 1 | 0 | 0 | 1 | 0 |

| State-5 | 0 | 1 | 0 | 1 | 0 | 0 | 0 |

| State-6 | 0 | 0 | 1 | 0 | 1 | 0 | 0 |

| Switches | Zone 1 | Zone 2 | Zone 3 | Zone 4 |

|---|---|---|---|---|

| S1 | 2d(t) | 4d(t) − 1 | 0 | 0 |

| S2 | 0 | 0 | −2d(t) | −4d(t) − 1 |

| S3 | 0 | 0 | 0 | 2 + 4d(t) |

| S4 | 0 | 2 − 4d(t) | 0 | 0 |

| S5 | 0 | 0 | 1 + 2d(t) | 0 |

| S6 | 1 − 2d(t) | 0 | 0 | 0 |

| Topology | Switch Count | Capacitors | Clamping Diodes | DC Sources |

|---|---|---|---|---|

| Proposed | 6 | 4 | 0 | 1 |

| 5-L inverter [32] | 10 | 6 | 0 | 1 |

| Hybrid 5-L [33] | 8 | 3 | 0 | 3 |

| NPC 5-L | 8 | 0 | 12 | 4 |

| FC 5-L | 8 | 18 | 0 | 1 |

| Standard ANPC | 8 | 3 | 0 | 1 |

| CHB 5-L | 8 | 0 | 0 | 6 |

| 5-L Inverter [34] | 8 | 4 | 0 | 1 |

| 5L-Improved ANPC [35] | 10 | 0 | 0 | 2 |

| S. No | Parameters | Value |

|---|---|---|

| 1 | Power Rating | 1000 watts |

| 2 | Input Voltage | 200 V |

| 3 | AC output Voltage | 200 V |

| 4 | Switching Frequency | 10 kHz |

| 5 | DC-Link Capacitors | 470 µF |

| 6 | Filter Inductors | 3 mH |

| 7 | Filter Capacitors | 30 µF |

| 8 | Load Resistor | 50 Ω |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ayub, M.A.; Aziz, S.; Liu, Y.; Peng, J.; Yin, J. Design and Control of Novel Single-Phase Multilevel Voltage Inverter Using MPC Controller. Sustainability 2023, 15, 860. https://doi.org/10.3390/su15010860

Ayub MA, Aziz S, Liu Y, Peng J, Yin J. Design and Control of Novel Single-Phase Multilevel Voltage Inverter Using MPC Controller. Sustainability. 2023; 15(1):860. https://doi.org/10.3390/su15010860

Chicago/Turabian StyleAyub, Muhammad Ahsan, Saddam Aziz, Yitao Liu, Jianchun Peng, and Jian Yin. 2023. "Design and Control of Novel Single-Phase Multilevel Voltage Inverter Using MPC Controller" Sustainability 15, no. 1: 860. https://doi.org/10.3390/su15010860

APA StyleAyub, M. A., Aziz, S., Liu, Y., Peng, J., & Yin, J. (2023). Design and Control of Novel Single-Phase Multilevel Voltage Inverter Using MPC Controller. Sustainability, 15(1), 860. https://doi.org/10.3390/su15010860