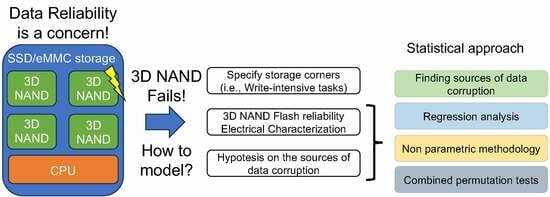

Modeling 3D NAND Flash with Nonparametric Inference on Regression Coefficients for Reliable Solid-State Storage

Abstract

:1. Introduction

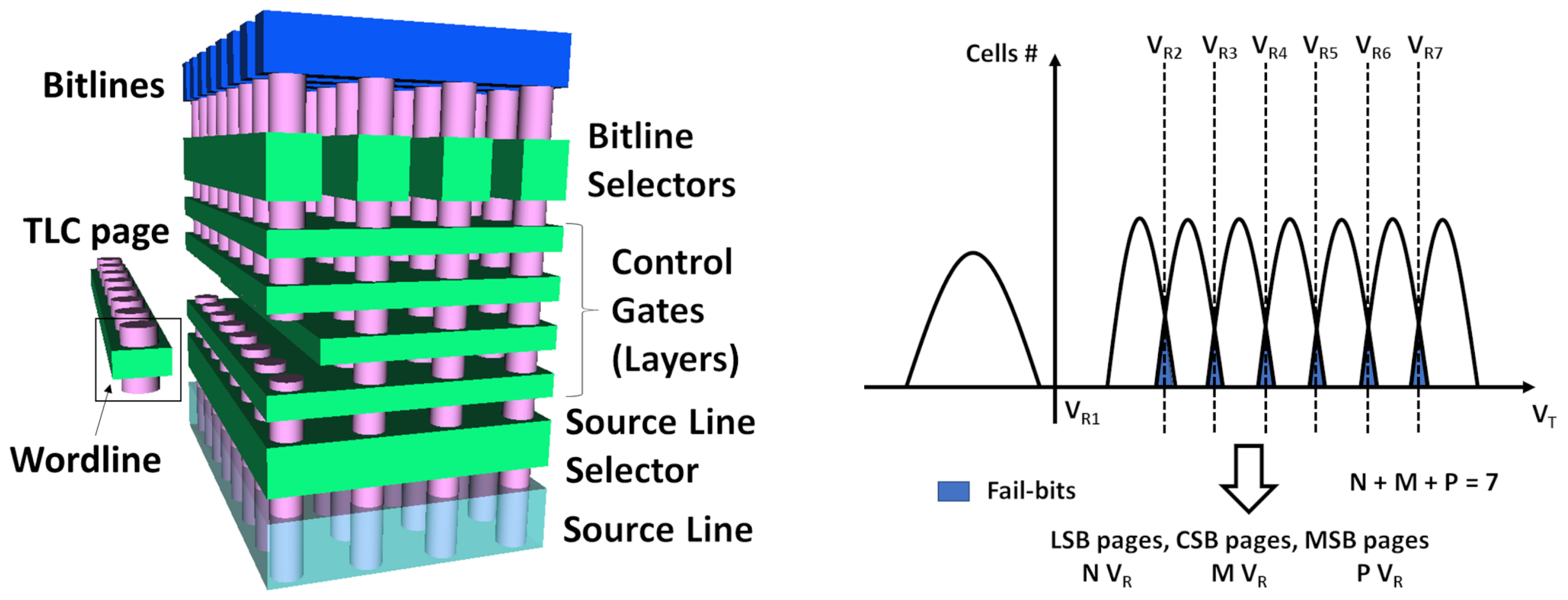

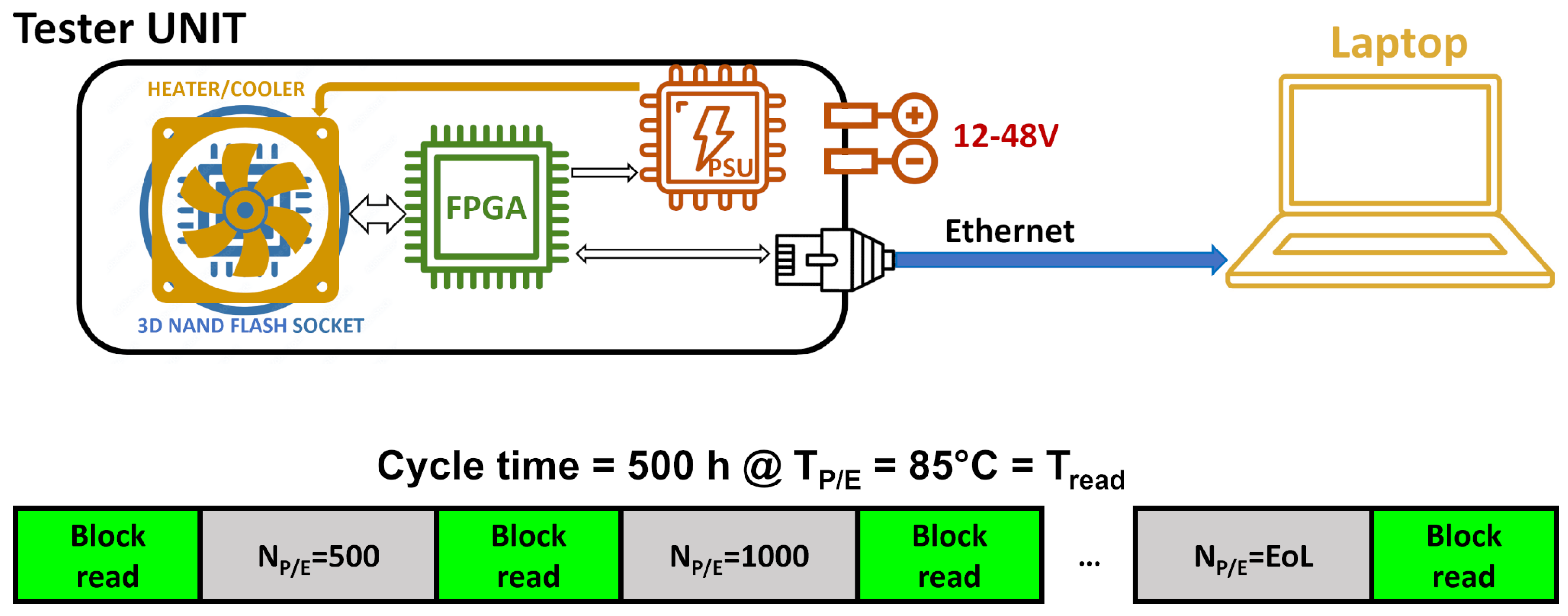

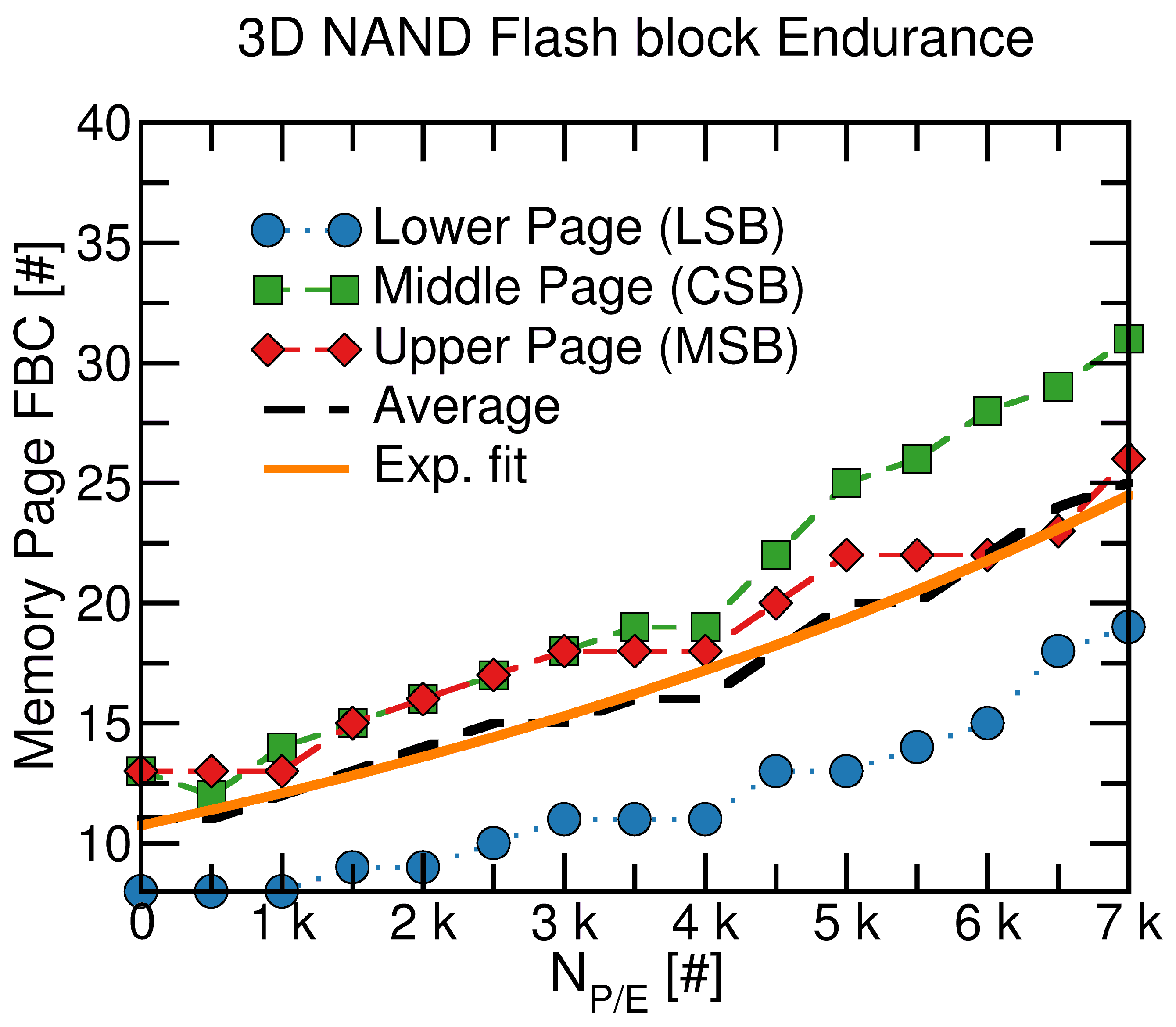

2. The 3D NAND Flash Endurance Reliability Case Study

2.1. Experimental Setup and Measurement Protocol

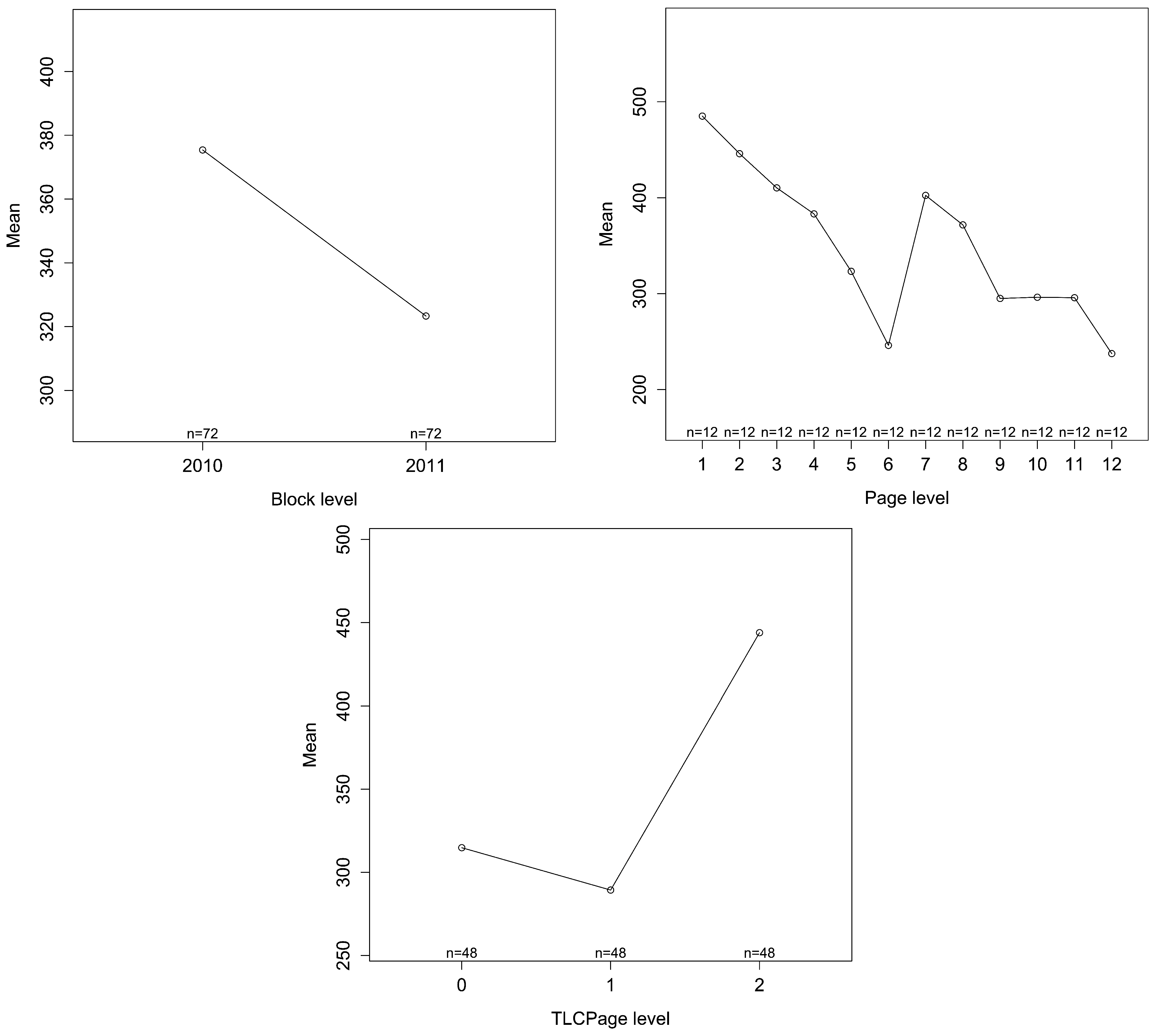

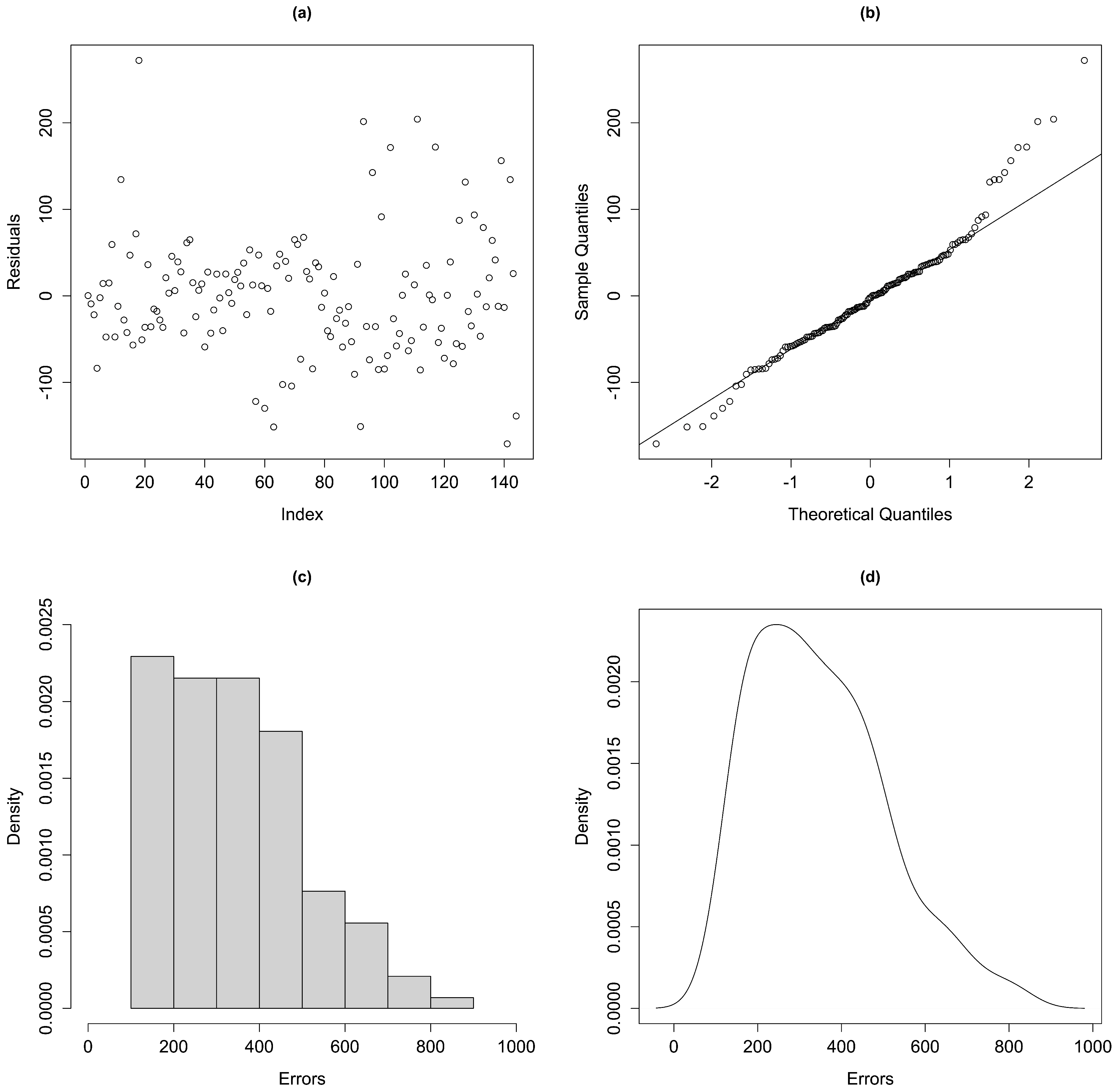

2.2. Data and Model

- sum-Errors, the dependent variable which represents the sum of the number of errors in Layer 0, 1, 2, 3 and for each TLC-Page;

- d-block, dummy explanatory variable which is 1 for block A and 0 for block B;

- d-page-c2, dummy explanatory variable which is 1 for cluster 2 of Page and 0 for all the other clusters in the measured block;

- d-page-c3, dummy explanatory variable which is 1 for cluster 3 of Page and 0 for all the other clusters in the measured block;

- d-page-c4, dummy explanatory variable which is 1 for cluster 4 of Page and 0 for all the other clusters in the measured block;

- d-page-c5, dummy explanatory variable which is 1 for cluster 5 of Page and 0 for all the other clusters in the measured block;

- d-page-c6, dummy explanatory variable which is 1 for cluster 6 of Page and 0 for all the other clusters in the measured block;

- d-page-c7, dummy explanatory variable which is 1 for cluster 7 of Page and 0 for all the other clusters in the measured block;

- d-page-c8, dummy explanatory variable which is 1 for cluster 8 of Page and 0 for all the other clusters in the measured block;

- d-page-c9, dummy explanatory variable which is 1 for cluster 9 of Page and 0 for all the other clusters in the measured block;

- d-page-c10, dummy explanatory variable which is 1 for cluster 10 of Page and 0 for all the other clusters in the measured block;

- d-page-c11, dummy explanatory variable which is 1 for cluster 11 of Page and 0 for all the other clusters in the measured block;

- d-page-c12, dummy explanatory variable which is 1 for cluster 12 of Page and 0 for all the other clusters in the measured block;

- d-tlcpage-1, dummy explanatory variable which is 1 if the read Page is associated with Middle Page (CSB) and 0 otherwise;

- d-tlcpage-2, dummy explanatory variable which is 1 if the read Page is associated with Upper Page (MSB) and 0 otherwise;

- PE-cycles, dummy explanatory variable representing the memory lifetime which is 1 for PE-cycles = EoL and 0 for PE-cycles = 0 (fresh device).

2.3. Hypotheses

3. Nonparametric Inference on the Regression Model

4. Results and Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Abbreviations

| SSD | Solid-State Drive |

| BER | Bit Error Rate |

| FBC | Fail Bits Count |

| OLS | Ordinary Least Squares |

| ANOVA | Univariate Analysis of Variance |

| VIF | Variance Inflation Factor |

References

- Dawson, D. The Future of Data Storage. 2022. Available online: https://circleid.com/posts/20220107-the-future-of-data-storage (accessed on 8 August 2023).

- Rydning, J.; Reinsel, D. Worldwide Global StorageSphere Forecast, 2021–2025: To Save or Not to Save Data, That Is the Question. Technical Report IDC Doc #US47509621, IDC Corp. 2021. Available online: https://www.marketresearch.com/IDC-v2477/Worldwide-Global-StorageSphere-Forecast-Save-14315473/ (accessed on 20 August 2023).

- Dang, S.; Han, R. An In-Network Cooperative Storage Schema Based on Neighbor Offloading in a Programmable Data Plane. Future Internet 2022, 14, 18. [Google Scholar] [CrossRef]

- Bayati, M.; Bhimani, J.; Lee, R.; Mi, N. Exploring Benefits of NVMe SSDs for BigData Processing in Enterprise Data Centers. In Proceedings of the 2019 5th International Conference on Big Data Computing and Communications (BIGCOM), Qingdao, China, 9–11 August 2019; pp. 98–106. [Google Scholar] [CrossRef]

- Goda, A. Recent Progress on 3D NAND Flash Technologies. Electronics 2021, 10, 3156. [Google Scholar] [CrossRef]

- Mielke, N.R.; Frickey, R.E.; Kalastirsky, I.; Quan, M.; Ustinov, D.; Vasudevan, V.J. Reliability of Solid-State Drives Based on NAND Flash Memory. Proc. IEEE 2017, 105, 1725–1750. [Google Scholar] [CrossRef]

- Zuolo, L.; Zambelli, C.; Micheloni, R.; Olivo, P. Solid-State Drives: Memory Driven Design Methodologies for Optimal Performance. Proc. IEEE 2017, 105, 1589–1608. [Google Scholar] [CrossRef]

- Zhang, T. Using LDPC Codes in SSD — Challenges and Solutions. In Proceedings of the Flash Memory Summit, Santa Clara, CA, USA, 21–23 August 2012. [Google Scholar]

- Li, Y.; Lee, P.P.; Lui, J.C. Analysis of Reliability Dynamics of SSD RAID. IEEE Trans. Comput. 2016, 65, 1131–1144. [Google Scholar] [CrossRef]

- Peleato, B.; Agarwal, R. Maximizing MLC NAND lifetime and reliability in the presence of write noise. In Proceedings of the 2012 IEEE International Conference on Communications (ICC), Ottawa, ON, Canada, 10–15 June 2012; pp. 3752–3756. [Google Scholar] [CrossRef]

- Moon, J.; No, J.; Lee, S.; Kim, S.; Choi, S.; Song, Y. Statistical Characterization of Noise and Interference in NAND Flash Memory. IEEE Trans. Circuits Syst. I Regul. Pap. 2013, 60, 2153–2164. [Google Scholar] [CrossRef]

- Lee, D.h.; Sung, W. Decision Directed Estimation of Threshold Voltage Distribution in NAND Flash Memory. IEEE Trans. Signal Process. 2014, 62, 919–927. [Google Scholar] [CrossRef]

- Fitzgerald, B.; Hogan, D.; Ryan, C.; Sullivan, J. Endurance prediction and error Reduction in NAND flash using machine learning. In Proceedings of the 2017 17th Non-Volatile Memory Technology Symposium (NVMTS), Aachen, Germany, 30 August–1 September 2017; pp. 1–8. [Google Scholar] [CrossRef]

- Liu, W.; Wu, F.; Zhou, J.; Zhang, M.; Yang, C.; Lu, Z.; Wang, Y.; Xie, C. Modeling of Threshold Voltage Distribution in 3D NAND Flash Memory. In Proceedings of the 2021 Design, Automation & Test in Europe Conference & Exhibition (DATE), Grenoble, France, 1–5 February 2021; pp. 1729–1732. [Google Scholar] [CrossRef]

- Zhang, H.; Wang, J.; Chen, Z.; Pan, Y.; Lu, Z.; Liu, Z. An SVM-Based NAND Flash Endurance Prediction Method. Micromachines 2021, 12, 746. [Google Scholar] [CrossRef] [PubMed]

- Santikellur, P.; Buddhanoy, M.; Sakib, S.; Ray, B.; Chakraborty, R.S. A shared page-aware machine learning assisted method for predicting and improving multi-level cell NAND flash memory life expectancy. Microelectron. Reliab. 2023, 140, 114867. [Google Scholar] [CrossRef]

- Monzio Compagnoni, C.; Ghidotti, M.; Lacaita, A.L.; Spinelli, A.S.; Visconti, A. Random Telegraph Noise Effect on the Programmed Threshold-Voltage Distribution of Flash Memories. IEEE Electron Device Lett. 2009, 30, 984–986. [Google Scholar] [CrossRef]

- Cai, Y.; Haratsch, E.F.; Mutlu, O.; Mai, K. Threshold voltage distribution in MLC NAND flash memory: Characterization, analysis, and modeling. In Proceedings of the 2013 Design, Automation and Test in Europe Conference and Exhibition (DATE), Grenoble, France, 18–22 March 2013; pp. 1285–1290. [Google Scholar] [CrossRef]

- Parnell, T.; Papandreou, N.; Mittelholzer, T.; Pozidis, H. Modelling of the threshold voltage distributions of sub-20nm NAND flash memory. In Proceedings of the IEEE Global Communications Conference, Austin, TX, USA, 8–12 December 2014; pp. 2351–2356. [Google Scholar] [CrossRef]

- Li, H. Modeling of Threshold Voltage Distribution in NAND Flash Memory: A Monte Carlo Method. IEEE Trans. Electron Devices 2016, 63, 3527–3532. [Google Scholar] [CrossRef]

- Wang, K.; Du, G.; Lun, Z.; Chen, W.; Liu, X. Modeling of program Vth distribution for 3-D TLC NAND flash memory. Sci. China Inf. Sci. 2019, 62, 42401. [Google Scholar] [CrossRef]

- Mielke, N.; Marquart, T.; Wu, N.; Kessenich, J.; Belgal, H.; Schares, E.; Trivedi, F.; Goodness, E.; Nevill, L.R. Bit error rate in NAND Flash memories. In Proceedings of the 2008 IEEE International Reliability Physics Symposium, Phoenix, AZ, USA, 27 April–1 May 2008; pp. 9–19. [Google Scholar] [CrossRef]

- Wang, N.J.; Lee, K.Y.; Lin, H.Y.; Hsiao, W.H.; Lee, M.Y.; Kuo, L.K.; Lin, D.J.; Chao, Y.H.; Lu, C.Y. Statistical Analysis of Bit-Errors Distribution for Reliability of 3-D NAND Flash Memories. In Proceedings of the 2020 IEEE International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 28 April–30 May 2020; pp. 1–5. [Google Scholar] [CrossRef]

- Zambelli, C.; Crippa, L.; Micheloni, R.; Olivo, P. Investigating 3D NAND Flash Read Disturb Reliability With Extreme Value Analysis. IEEE Trans. Device Mater. Reliab. 2021, 21, 486–493. [Google Scholar] [CrossRef]

- Nakamura, T.; Deguchi, Y.; Takeuchi, K. Adaptive Artificial Neural Network-Coupled LDPC ECC as Universal Solution for 3-D and 2-D, Charge-Trap and Floating-Gate NAND Flash Memories. IEEE J. Solid-State Circuits 2019, 54, 745–754. [Google Scholar] [CrossRef]

- Abe, M.; Matsui, C.; Mizushina, K.; Suzuki, S.; Takeuchi, K. Computational Approximate Storage with Neural Network-based Error Patrol of 3D-TLC NAND Flash Memory for Machine Learning Applications. In Proceedings of the 2020 IEEE International Memory Workshop (IMW), Dresden, Germany, 17–20 May 2020; pp. 1–4. [Google Scholar] [CrossRef]

- Mei, Z.; Cai, K.; He, X. Deep Learning-Aided Dynamic Read Thresholds Design for Multi-Level-Cell Flash Memories. IEEE Trans. Commun. 2020, 68, 2850–2862. [Google Scholar] [CrossRef]

- Khodadadian, A.; Parvizi, M.; Teshnehlab, M.; Heitzinger, C. Rational Design of Field-Effect Sensors Using Partial Differential Equations, Bayesian Inversion, and Artificial Neural Networks. Sensors 2022, 22, 4785. [Google Scholar] [CrossRef] [PubMed]

- Marquart, T.A. Solid-State-Drive qualification and reliability strategy. In Proceedings of the 2015 IEEE International Integrated Reliability Workshop (IIRW), South Lake Tahoe, CA, USA, 11–15 October 2015; pp. 3–6. [Google Scholar] [CrossRef]

- Pesarin, F. Nonparametric Combination Methodology. In Multivariate Permutation Tests with Applications in Biostatistics, 2nd ed.; Wiley: Chichester, UK, 2001. [Google Scholar]

- Harrar, S.W.; Bathke, A.C. A non-parametric version of the Bartlett-Nanda-Pillai multivariate test. Asymptotics, approximations, and applications. Am. J. Math. Manag. Sci. 2008, 28, 309–335. [Google Scholar]

- Zambelli, C.; Micheloni, R.; Scommegna, S.; Olivo, P. First Evidence of Temporary Read Errors in TLC 3D-NAND Flash Memories Exiting From an Idle State. IEEE J. Electron Devices Soc. 2020, 8, 99–104. [Google Scholar] [CrossRef]

- JESD22-A117E; Electrically Erasable Programmable ROM (EEPROM) Program/Erase Endurance and Data Retention Stress Test. JEDEC: Arlington, VA, USA, 2018.

- JESD47L; Stress-Test-Driven Qualification of Integrated Circuits. JEDEC: Arlington, VA, USA, 2022.

- Papandreou, N.; Pozidis, H.; Parnell, T.; Ioannou, N.; Pletka, R.; Tomic, S.; Breen, P.; Tressler, G.; Fry, A.; Fisher, T. Characterization and Analysis of Bit Errors in 3D TLC NAND Flash Memory. In Proceedings of the 2019 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 31 March–4 April 2019; pp. 1–6. [Google Scholar] [CrossRef]

- Fang, X.; Zhang, M.; Guo, Y.; Chen, F.; Chen, B.; Zhan, X.; Wu, J.; Wu, F.; Chen, J. Work-in-Progress: High-Precision Short-Term Lifetime Prediction in TLC 3D NAND Flash Memory as Hot-data Storage. In Proceedings of the 2022 International Conference on Compilers, Architecture, and Synthesis for Embedded Systems (CASES), Shanghai, China, 7–14 October 2022; pp. 11–12. [Google Scholar] [CrossRef]

- Raquibuzzaman, M.; Hasan, M.M.; Milenkovic, A.; Ray, B. Layer-to-Layer Endurance Variation of 3D NAND Flash Memory. In Proceedings of the 2022 IEEE International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 27–31 March 2022; pp. 1–5. [Google Scholar] [CrossRef]

- Bonnini, S.; Corain, L.; Marozzi, M.; Salmaso, L. Nonparametric Hypothesis Testing, Rank and Permutation Methods with Applications in R; Wiley: Hoboken, NY, USA, 2014. [Google Scholar]

- Pesarin, F.; Salmaso, L. Permutation Tests for Complex Data: Theory, Applications and Software; Wiley: Hoboken, NY, USA, 2010. [Google Scholar]

- Shrestha, N. Detecting multicollinearity in regression analysis. Am. J. Appl. Math. Stat. 2020, 8, 39–42. [Google Scholar] [CrossRef]

- Westfall, P.H.; Young, S. Resampling-Based Multiple Testing: Examples and Methods for p-Value Adjustment; Wiley-Interscience: New York, NY, USA, 1992. [Google Scholar]

| Variable | VIF |

|---|---|

| d-block | 1.00 |

| d-page-c2 | 1.83 |

| d-page-c3 | 1.83 |

| d-page-c4 | 1.83 |

| d-page-c5 | 1.83 |

| d-page-c6 | 1.83 |

| d-page-c7 | 1.83 |

| d-page-c8 | 1.83 |

| d-page-c9 | 1.83 |

| d-page-c10 | 1.83 |

| d-page-c11 | 1.83 |

| d-page-c12 | 1.83 |

| d-tlcpage-1 | 1.33 |

| d-tlcpage-2 | 1.33 |

| PE-cycles | 1.00 |

| Estimate | Non Adjusted p-Values | Adj. p-Values | |

|---|---|---|---|

| Intercept | 381.74 | ||

| d-block | −52.08 | 0.04950 | 0.3465 |

| d-page-c2 | −39.17 | 0.5439 | 0.8541 |

| d-page-c3 | −74.83 | 0.2477 | 0.8099 |

| d-page-c4 | −101.92 | 0.1126 | 0.5629 |

| d-page-c5 | −161.83 | 0.0121 | 0.0968 |

| d-page-c6 | −239 | 0.0004 | 0.0048 |

| d-page-c7 | −82.67 | 0.2025 | 0.8099 |

| d-page-c8 | −113.42 | 0.0790 | 0.4740 |

| d-page-c9 | −190.08 | 0.0033 | 0.0363 |

| d-page-c10 | −188.83 | 0.0044 | 0.0396 |

| d-page-c11 | −189.33 | 0.0039 | 0.0390 |

| d-page-c12 | −247.58 | 0.0002 | 0.0026 |

| d-tlcpage-1 | −25.48 | 0.4271 | 0.8541 |

| d-tlcpage-2 | 129.12 | 0.0001 | 0.0015 |

| PE-cycles | 189.67 | 0.0001 | 0.0015 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Borghesi, M.; Zambelli, C.; Micheloni, R.; Bonnini, S. Modeling 3D NAND Flash with Nonparametric Inference on Regression Coefficients for Reliable Solid-State Storage. Future Internet 2023, 15, 319. https://doi.org/10.3390/fi15100319

Borghesi M, Zambelli C, Micheloni R, Bonnini S. Modeling 3D NAND Flash with Nonparametric Inference on Regression Coefficients for Reliable Solid-State Storage. Future Internet. 2023; 15(10):319. https://doi.org/10.3390/fi15100319

Chicago/Turabian StyleBorghesi, Michela, Cristian Zambelli, Rino Micheloni, and Stefano Bonnini. 2023. "Modeling 3D NAND Flash with Nonparametric Inference on Regression Coefficients for Reliable Solid-State Storage" Future Internet 15, no. 10: 319. https://doi.org/10.3390/fi15100319

APA StyleBorghesi, M., Zambelli, C., Micheloni, R., & Bonnini, S. (2023). Modeling 3D NAND Flash with Nonparametric Inference on Regression Coefficients for Reliable Solid-State Storage. Future Internet, 15(10), 319. https://doi.org/10.3390/fi15100319