Hardware–Software Co-Design Architecture for Real-Time EMG Feature Processing in FPGA-Based Prosthetic Systems

Abstract

1. Introduction

- A novel co-processing architecture that integrates time-domain feature extraction (Mean Absolute Value, MAV; Waveform Length, WL; Slope Sign Changes, SSC; Zero Crossings, ZC) with PCA transformation in a unified FPGA pipeline, eliminating traditional software processing bottlenecks.

- Comparative architectural analysis of three matrix multiplication implementations (full, block-based, and column-based), demonstrating optimal resource utilization strategies for EMG processing in resource-constrained environments.

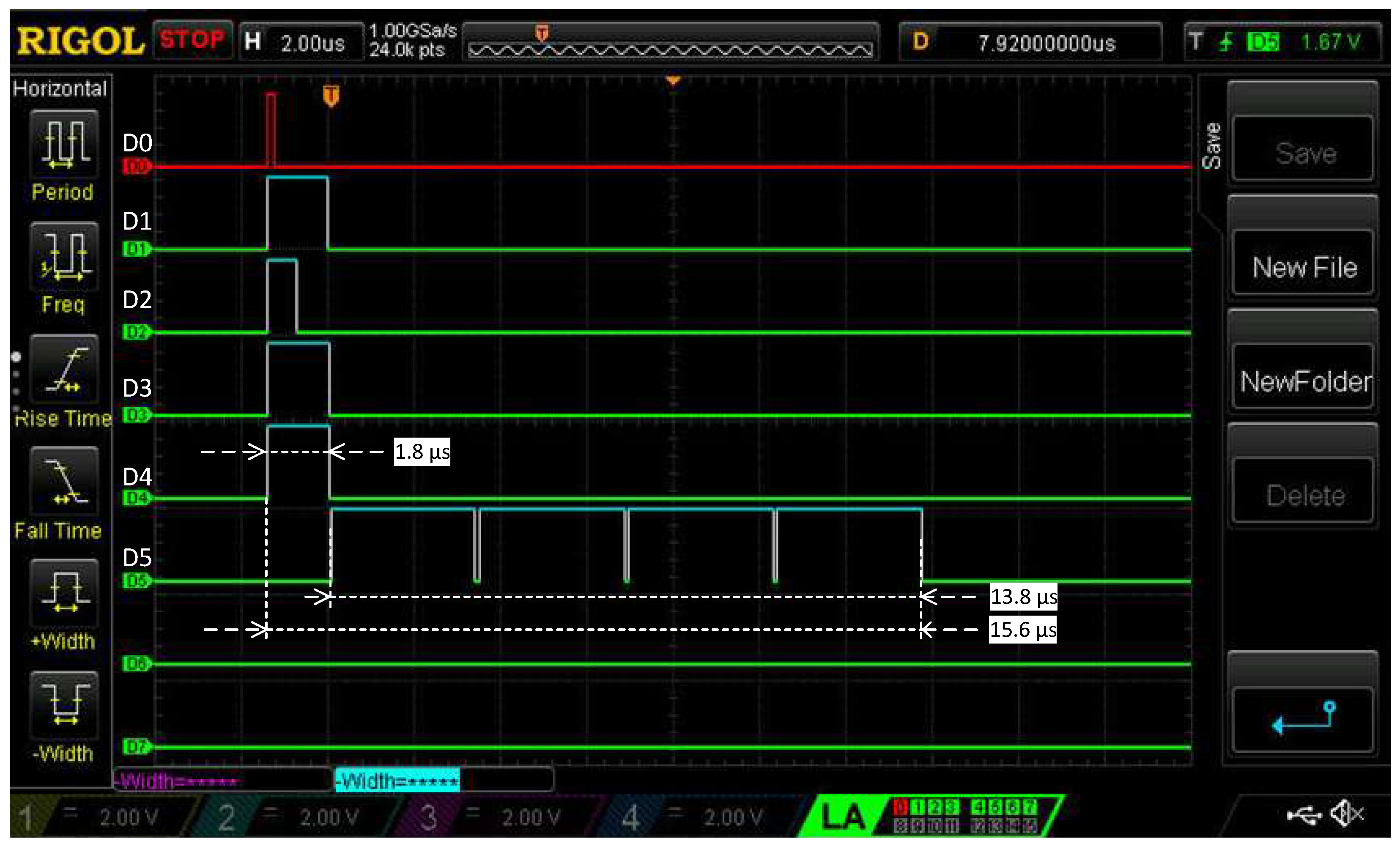

- Quantitative performance evaluation showing 7.3× speed improvement and 3.1× energy efficiency gain compared to ARM Cortex-A9 software implementation, validating the architectural approach for battery-powered prosthetic applications.

- A complete hardware–software co-design methodology using Zynq SoC platform that enables rapid prototyping and validation of EMG processing algorithms in embedded systems.

2. Methods

2.1. Hardware-Implemented EMG Feature Extraction Metrics

2.1.1. MAV—Mean Absolute Value

2.1.2. WL—Waveform Length

2.1.3. SSC—Slope Sign Changes

2.1.4. ZC—Zero Crossings

2.2. FPGA-Efficient PCA Matrix Computation Architecture

- The average/mean by row is computed,

- Then, it is subtracted from each sample in the dataset,(remember that ), where ,

- To compute the covariance matrix,

- Given that is a symmetric matrix, its eigenvectors , …, and its corresponding eigenvalues , …, are computed using the Jacobi eigenvalue algorithm [36] to obtainwherenotice that, given that is symmetric with real entries, is orthogonal, that is, .

2.3. Architectural Design Rationale

- Hardware Simplicity: They require only basic arithmetic operations (addition, subtraction, comparison) that map efficiently to FPGA resources.

- Pipeline Compatibility: Sequential computation pattern enables efficient streaming architecture with minimal memory requirements.

- Established Baseline: Well-documented algorithms allow focus on architectural optimization rather than algorithmic development.

3. Database and Experimental System

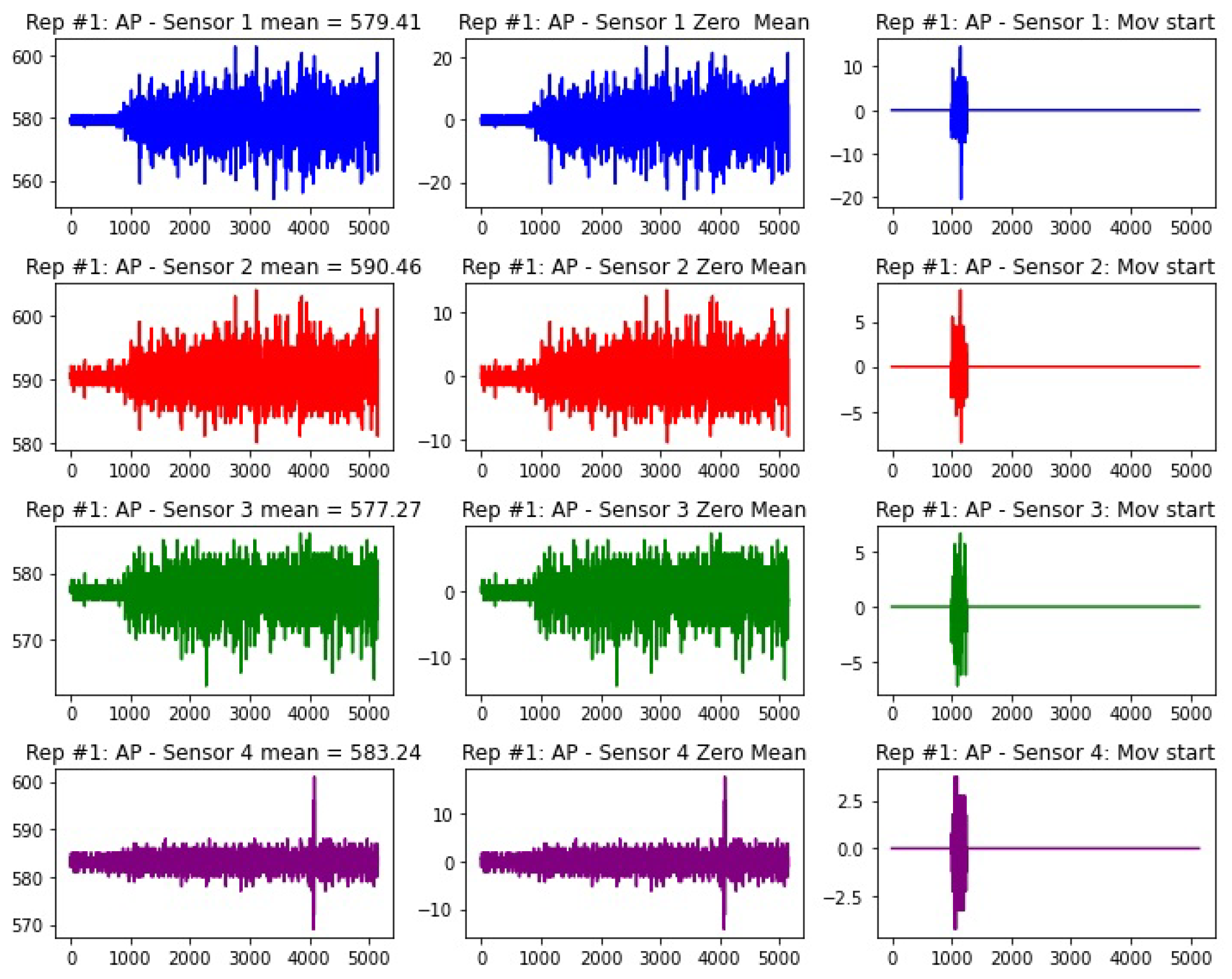

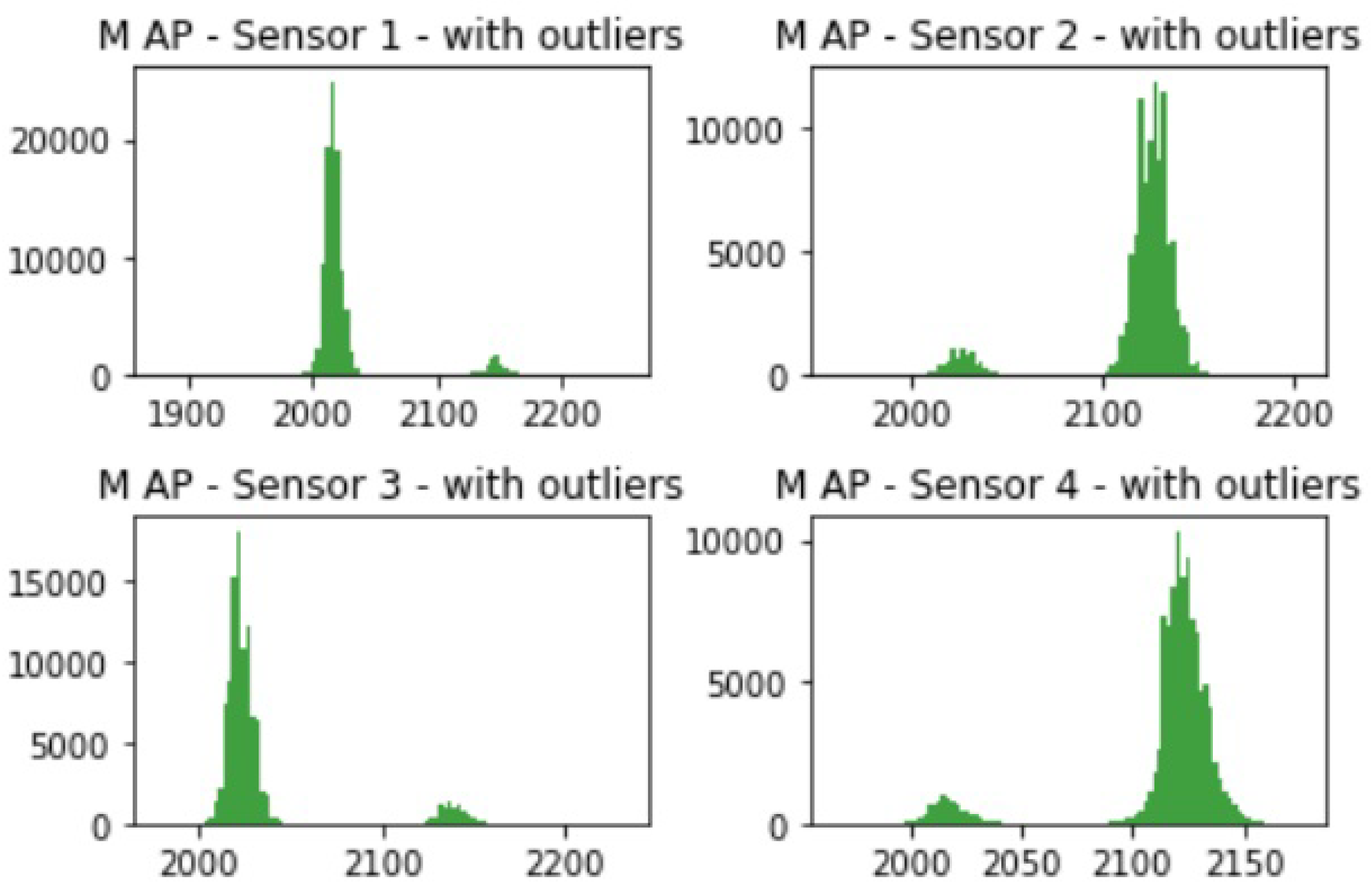

3.1. Database

- AP Support toe without raising heel.

- AT Support the heel without raising the toe.

- LP Raise the toe.

- LT Lift the heel.

- PD Move tip to the right.

- PI Move tip to the left.

- RR Relaxed state or rest.

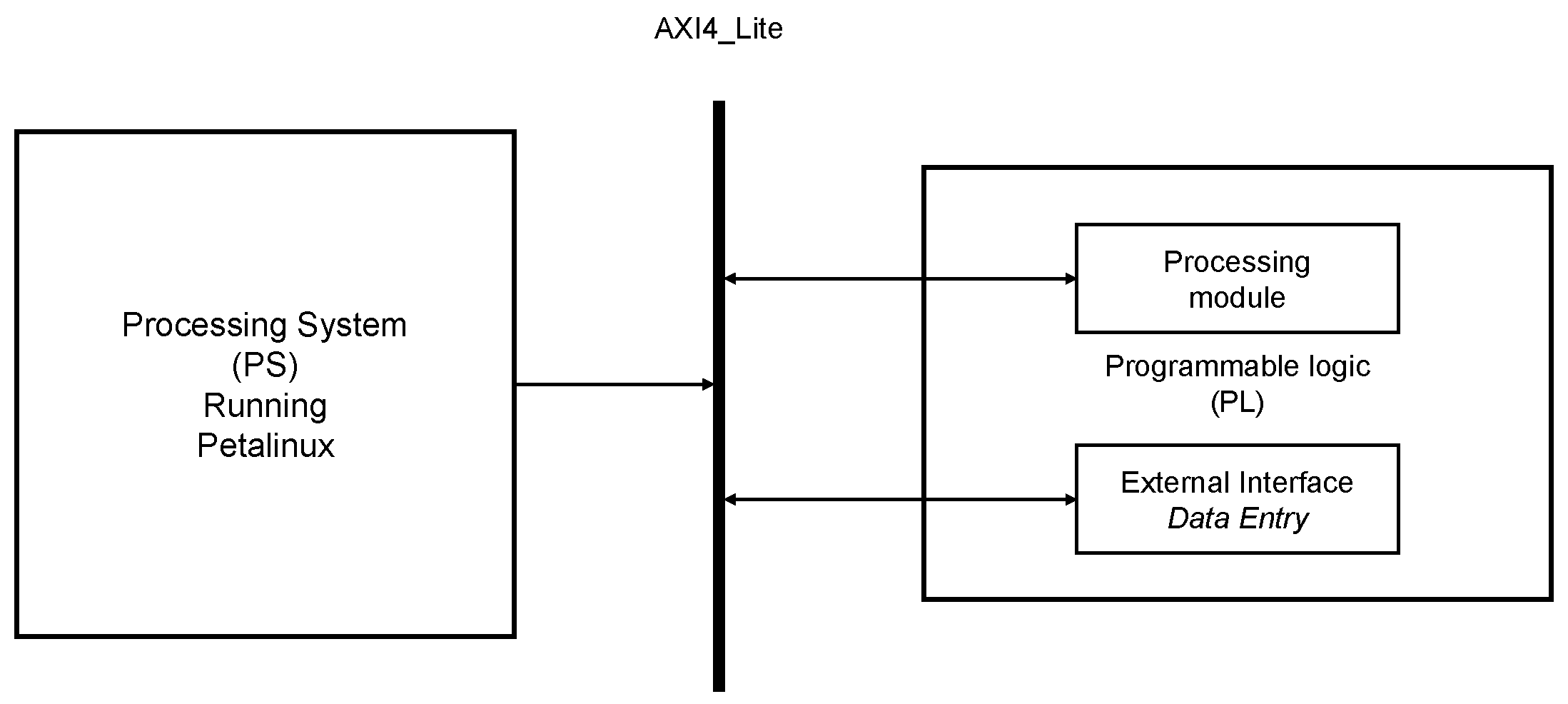

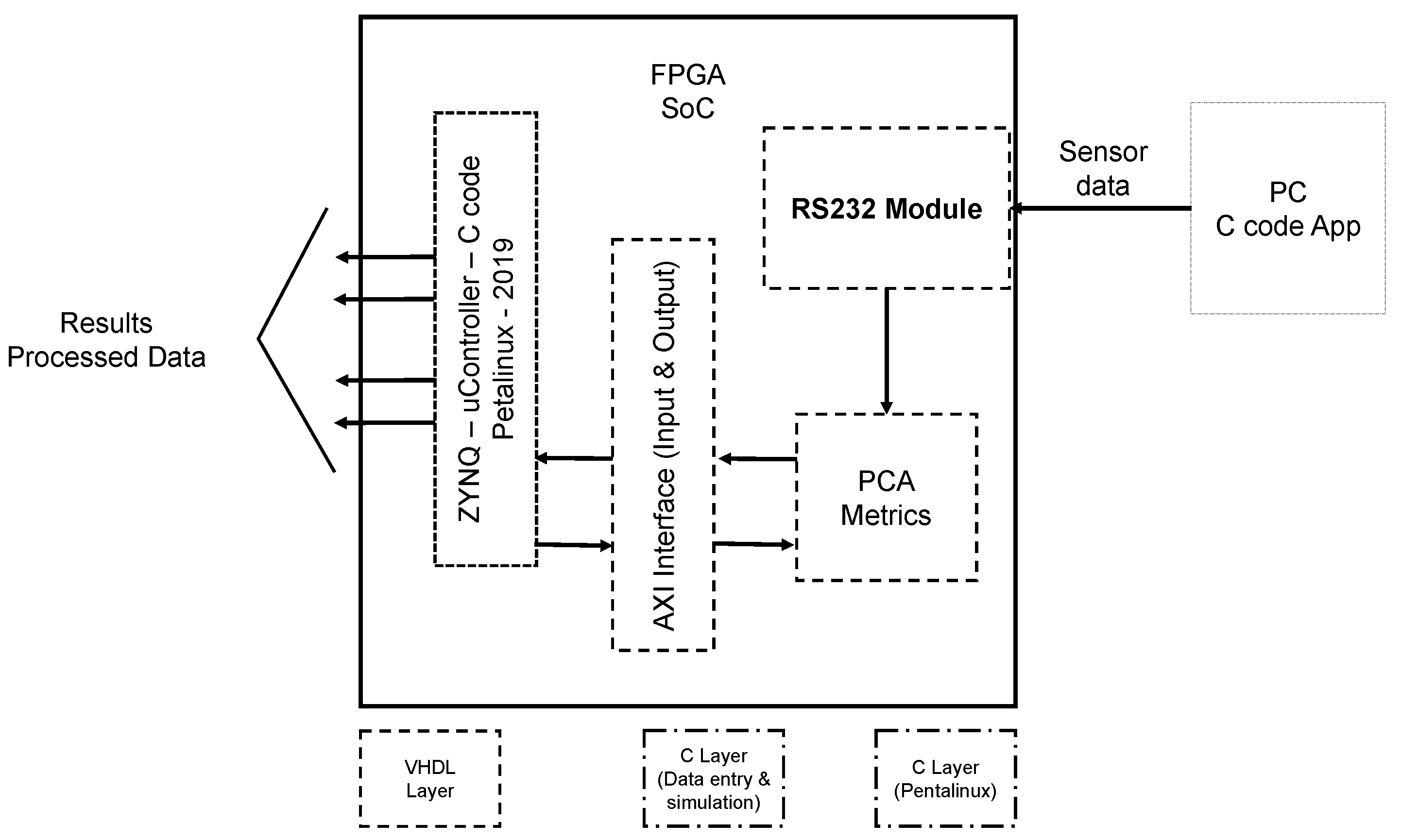

3.2. Experimentation Platform

3.2.1. Design Choice Rationale

3.2.2. Hardware Description

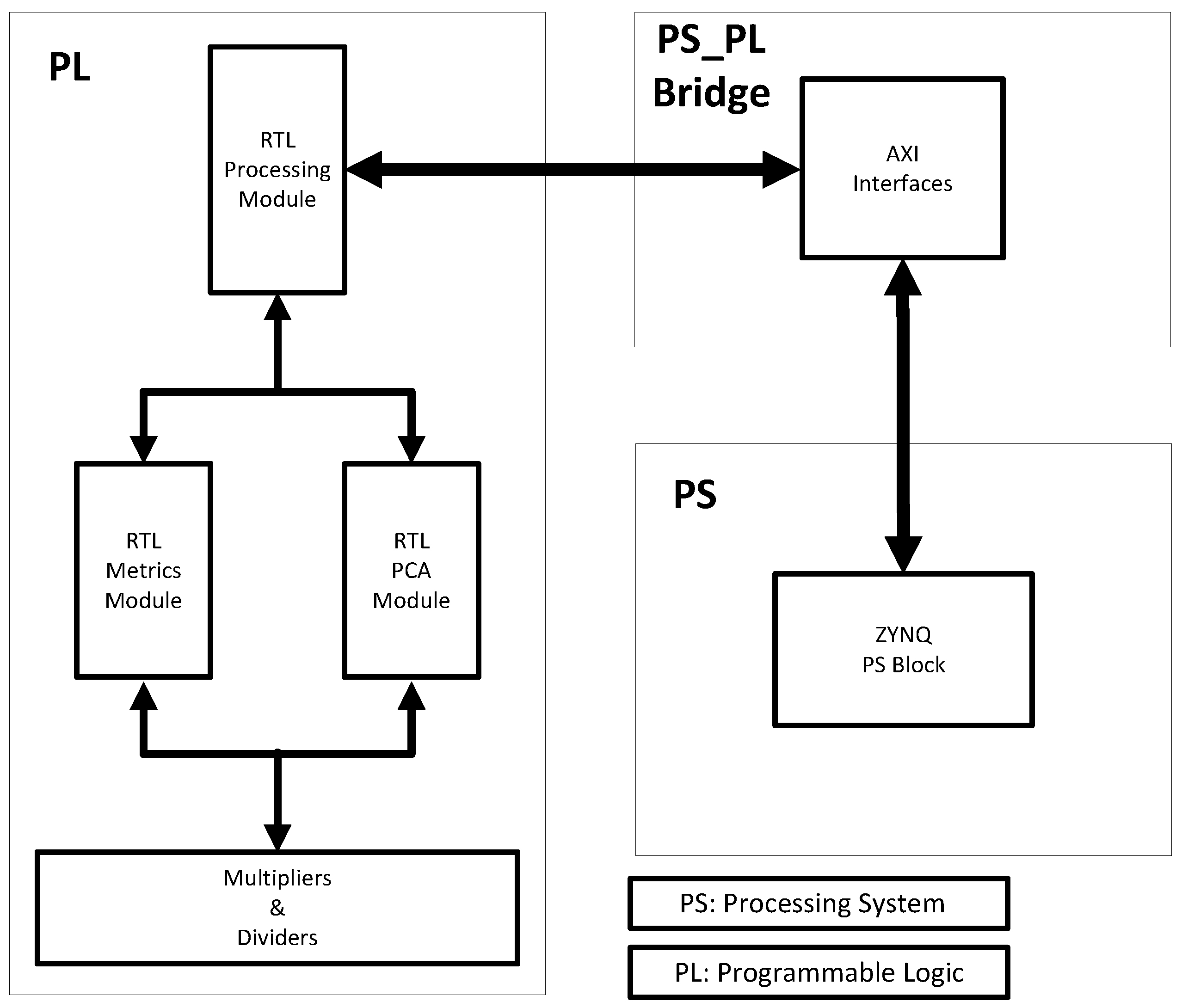

- The AXI I/F module is the main communication interface between the PL and the PS; this interface implements a register-based communication protocol that enables data transfer between the PS, where the Petalinux software stack resides, and two primary processing modules in the PL: the “Metrics” module and the “PCA” module.

- The main block from the perspective of where the calculations of the algorithm are performed is the “Processing” module shown as RTL near the center of Figure 5. This module coordinates the data entry from sensors and delivers these data to the “Metrics” module.

- The “Metrics” module is encapsulated within the “Processing” module, and computes the four metrics for each sensor described in Section 2.1, thus producing 16 parameters that become the input data to the “PCA” module.

- The “PCA” module is also stored in the RTL module block and performs the change of coordinates from to given in Equation (1) using the procedure described in Section 3.2.3. The output of the PCA module is then collected to review the first r components.

- These two last modules rely on the modules depicted on the left, which are multipliers and dividers. The dividers on the “Metrics” module perform the division operations needed mainly within the MAV metric. The multipliers serve to compute the product of the computed metrics with the PCA matrix (that is calculated beforehand in the C language program running in SW in Petalinux) as in Equation (1).

- Send the received metrics vector to an array that later will be used to calculate the PCA matrix, if in matrix calculation mode;

- Process the received metrics vector through the PCA matrix, if in continuous operation mode.

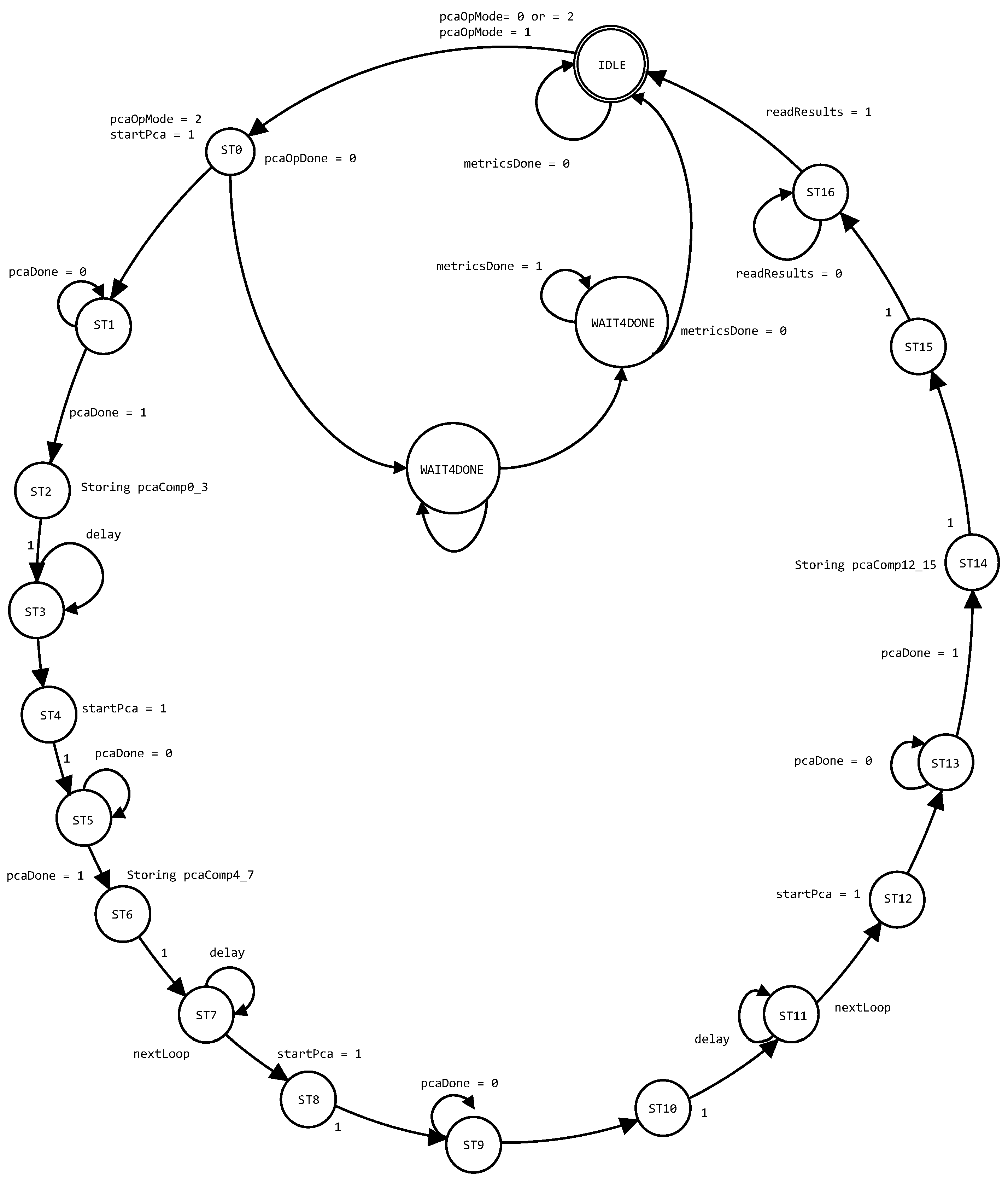

3.2.3. PCA Matrix Multiplication Process

- The amount of reprogrammable logical resources available in the FPGA.

- The processing time it takes the matrix multiplication as part of the processing algorithm.

- Full Multiplication: The first and straightforward approach of performing the typical complete matrix multiplication, as described in Equation (2), was an early consideration. However, due to its excessive resource requirements, it was deemed infeasible for the target FPGA.

- -Block Multiplication: The second option was to split the multiplication operation in Equation (2) into block operations of the formby computingfor each sensor , 2, 3, 4, and for each column block , 2, 3, 4. Keeping ℓ fixed and summing over the sensor index k yieldsThe results of this approach were not as good as expected, as the logic to control the sequence of multiplications and additions involved in the whole process required a large amount of logic within the FPGA.

- 4-Column Multiplication Modules: The last approach implemented, which is the architecture that provided the best results, was achieved by ‘balancing’ the two previous approaches by multiplying the 16-entry vector times a matrix, that is, by multiplyingfor each column block , 2, 3, 4. If less than 16 principal components are needed, the column block index can iterate over a smaller range. Remark that this approach has the advantage of directly producing actual components of while at the same time offering a reasonable balance between resource requirements and the amount of logic required within the FPGA. Section 4 presents statistics on the resources used within the FPGA. Besides, this approach provides the expected results and complies with the timing requirements.

3.2.4. Software Description

3.2.5. Operation Sequence and Operation Modes

- Initialization Phase:

- I1

- Both the PS and PL initialize their respective components.

- I2

- The PS configures the PL registers and sets up the data flow paths.

- I3

- Depending on the data input mode (external UART-based application or BRAM), the PL selects the four input channels of the sensor values to be processed.

- Sampling:

- S1

- The PS signals the PL to collect metrics from incoming sensor data.

- S2

- The PL initializes the input sensor buffer.

- S3

- The “Processing” module (from the PL) reads the input sensor values (counting from to , where N is the window size) and stores them in the 4-channel input buffer of length N.

- S4

- Once there are N samples, the “Metrics” module is prompted by the “Processing” module to immediately compute the four time-domain features (MAV, WL, SSC, ZC) per sensor:

Sensor 1 Sensor 2 Sensor 3 Sensor 4 MAV-WL-ZC-SSC MAV-WL-ZC-SSC MAV-WL-ZC-SSC MAV-WL-ZC-SSC - S5

- The PL transfers the computed metrics to the PS, which stores them (in a DataSet object) for PCA matrix calculation.

- Learning Mode:

- L1

- The PS computes the covariance matrix from the collected metrics vectors.

- L2

- It performs Jacobi eigenvalue decomposition to find eigenvalues and eigenvectors .

- L3

- The PCA transformation matrix has its columns (eigenvectors) sorted in the proper descending order according to the magnitude of its corresponding eigenvalues.

- L4

- The PS transfers the PCA matrix coefficients to the PL through the AXI interface. The “PCA” module stores these coefficients in internal registers.

- Operation Mode:

- O1

- The PS signals the PL to switch to operational mode.

- O2

- Instead of transferring metrics to the PS, the “PCA” module now applies the transformation matrix to the metrics vectors, that is, computes .

- O3

- The resulting PCA components are transferred back to the PS for further analysis or classification.

4. Results

4.1. FPGA Used Resources

4.2. Application Results

- A sample of the data entry for the four sensors. A sample of the sensor data is shown below:-0.00436020 -0.02589910 -0.00280167 0.00802203-0.02873340 0.00672732 0.00186870 -0.015897900.00176235 -0.03466060 -0.01619870 0.02321670-0.03075060 0.03271290 0.01021340 -0.019829000.00216684 0.00063915 -0.04133170 -0.008589400.06235370 0.04674370 0.04463140 0.04991990-0.06014440 -0.09982760 -0.05358500 -0.06827760-0.04320210 -0.00448979 0.06629640 0.04391780-0.02117970 0.01781130 -0.01843370 -0.03890570-0.00947362 -0.02973350 -0.02852140 0.027097300.00409025 0.03296500 0.01918160 0.002115510.10056500 0.03024860 -0.04497290 0.03854670-0.06442331 -0.06319550 0.00636181 -0.04414980

- Training—Creating PCA Matrix. Receiving data, most left represents data for sensor #1, then sensor #2, and so on. At start, the system is in what we call “learning mode”; during this time, the metrics vectors are used to create the PCA matrix. In this example, the process is completed using a window size , which means that we require seven entry vectors of raw sensor data in order to have an output metrics vector.Sample#: 1Waiting for dataValid = 1S1:-0.004360 S2:-0.025899 S3:-0.002802 S4:0.008022Waiting for dataValid = 0Sample#: 2Waiting for dataValid = 1S1:-0.028733 S2:0.006727 S3:0.001869 S4:-0.015898Waiting for dataValid = 0Sample#: 3Waiting for dataValid = 1S1:0.001762 S2:-0.034661 S3:-0.016199 S4:0.023217Waiting for dataValid = 0Sample#: 4Waiting for dataValid = 1S1:-0.030751 S2:0.032713 S3:0.010213 S4:-0.019829Waiting for dataValid = 0Sample#: 5Waiting for dataValid = 1S1:0.002167 S2:0.000639 S3:-0.041332 S4:-0.008589Waiting for dataValid = 0Sample#: 6Waiting for dataValid = 1S1:0.062354 S2:0.046744 S3:0.044631 S4:0.049920Waiting for dataValid = 0Sample#: 7Waiting for dataValid = 1S1:-0.060144 S2:-0.099828 S3:-0.053585 S4:-0.068278Waiting for dataValid = 0Metrics done!Input to PCA Module:S1:AAV-WL-ZS-SSC; S2:AAV-WL-ZS-SSC;0.027182 0.302984 4.000000 4.0000000.035316 0.366137 4.000000 5.000000S3:AAV-WL-ZS-SSC; S4:AAV-WL-ZS-SSC;0.024376 0.284874 6.000000 5.0000000.027679 0.294027 5.000000 4.000000Sample for PCA calculationOnce the indicated number of metrics’ vectors is reached, then the system goes into “operation mode”. In this example, the required number of entry metrics’ vectors is . Thus, in our case, we required seven (7) windows of size , so in total, we needed to process samples.Sample#: 43Waiting for dataValid = 1S1:-0.041569 S2:0.057423 S3:0.025218 S4:-0.018170Waiting for dataValid = 0Sample#: 44Waiting for dataValid = 1S1:0.033394 S2:-0.079262 S3:-0.038959 S4:0.036694Waiting for dataValid = 0Sample#: 45Waiting for dataValid = 1S1:0.006929 S2:0.051741 S3:-0.001391 S4:0.020102Waiting for dataValid = 0Sample#: 46Waiting for dataValid = 1S1:0.026344 S2:0.031666 S3:0.025776 S4:0.027777Waiting for dataValid = 0Sample#: 47Waiting for dataValid = 1S1:-0.036288 S2:-0.031773 S3:-0.018986 S4:-0.104803Waiting for dataValid = 0Sample#: 48Waiting for dataValid = 1S1:-0.070014 S2:0.032346 S3:0.067164 S4:0.001208Waiting for dataValid = 0Sample#: 49Waiting for dataValid = 1S1:0.067987 S2:0.035339 S3:-0.005998 S4:0.092489Waiting for dataValid = 0Metrics done!Input to PCA Module:S1:AAV-WL-ZS-SSC; S2:AAV-WL-ZS-SSC;0.040361 0.355202 3.000000 4.0000000.045650 0.418315 4.000000 3.000000S3:AAV-WL-ZS-SSC; S4:AAV-WL-ZS-SSC;0.026213 0.332987 5.000000 4.0000000.043035 0.409004 3.000000 4.000000Sample for PCA calculationThe processes completed after capturing raw input data for sample #49 are the following:

- -

- Compute covariance using the received data (the data from the metrics’ vectors, calculated values derived from the raw input sensor’ data).

- -

- Calculate the Jacobi for the created matrix.

- -

- Calculate the eigensystem: eigenvalues and eigenvectors.

- -

- Determine the PCA matrix coefficients.

- -

- Transfer the PCA matrix coefficients to the FPGA internal registers to be used by the PCA module in the FW.

- Operation mode. Once the system is running and the sequence is the same, we wait for ( in the example shown) raw entry data vectors to get one output metrics vector, and then this metrics vector is processed by the PCA module. The output of the FPGA implementation is then compared with another process running in the Petalinux system for comparison purposes, which are shown as “Calculated PCA Components”.

5. Conclusions and Future Work

Author Contributions

Funding

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

Abbreviations

| AXI | Advanced eXtensible Interface |

| ECG | Electrocardiograms |

| EMG | Electromyography |

| FPGA | Field-Programmable Gate Array |

| FSM | Finite State Machine |

| FW | Firmware |

| HW | Hardware |

| I/F | Interface |

| IP | Intellectual Property |

| MAV | Mean Absolute Value |

| PCA | Principal Component Analysis |

| PL | Programmable Logic |

| PS | Processing System |

| RTL | Register Transfer Level |

| SSC | Slope Sign Changes |

| SW | Software |

| UART | Universal Asynchronous Receiver-Transmitter |

| WL | Waveform Length |

| ZC | Zero Crossings |

Appendix A

- Time-Domain Features: These features are computed directly from the raw EMG signal.

- Mean Absolute Value (MAV):This is also known as the Average Rectified Value (ARV) and is a commonly used feature to quantify muscle activity and can be used to assess muscle fatigue.

- Root Mean Square (RMS):The RMS value is proportional to the amplitude of the EMG signal and reflects the intensity of muscle contraction. RMS is less sensitive to noise than the MAV.

- Zero Crossings (ZC): Counts the number of times the signal crosses zero with a threshold to avoid noise.

- Slope Sign Changes (SSC): Counts the number of changes in the slope direction, indicating fluctuations in the signal.

- Waveform Length (WL):

- Integrated EMG (IEMG):

- Frequency-Domain Features: These features are obtained after applying a transform such as the Fast Fourier Transform (FFT).

- Mean Frequency (MNF):

- Median Frequency (MDF): The frequency that divides the power spectrum into two equal halves.

- Power Spectrum Entropy (PSE): Measures the distribution of power across different frequencies.

- Total Power: The sum of all power spectral densities, representing the overall power of the signal.

- Time-Frequency Domain Features: These features provide information about the signal in both time and frequency domains.

- Wavelet Coefficients: Extracted using wavelet decomposition, capturing both time and frequency information.

- Spectrogram Features: Time-varying frequency content, useful for non-stationary signals.

- Statistical Features: These features describe the statistical properties of the EMG signal.

- Mean: The average value of the signal.

- Standard Deviation (STD): Measures the variability of the signal.

- Skewness: Indicates the asymmetry of the signal distribution.

- Kurtosis: Measures the "tailedness" of the signal distribution.

- Non-linear Features: These features capture the complex, non-linear nature of EMG signals.

- Approximate Entropy (ApEn): Measures the complexity of the signal, with higher values indicating more irregularity.

- Fractal Dimension (FD): Describes the self-similarity of the signal.

- Lyapunov Exponent: Measures the chaotic behavior of the signal; positive values indicate chaos.

References

- Namboothiripad, M.K.; Vadhyan, G. Efficient implementation of artificial neural networks on FPGAs using high-level synthesis and parallelism. Int. J. Adv. Technol. Eng. Explor. 2024, 11, 1497–1511. [Google Scholar] [CrossRef]

- Fejér, A.; Nagy, Z.; Benois-Pineau, J.; Szolgay, P.; de Rugy, A.; Domenger, J.P. Implementation of Scale Invariant Feature Transform detector on FPGA for low-power wearable devices for prostheses control. Int. J. Circuit Theory Appl. 2021, 49, 2255–2273. [Google Scholar] [CrossRef]

- Pal, S.; Upadhyaya, B.K.; Majumder, T.; Dasgupta, S.; Das, N.; Bhattacharjee, A. Dynamic configuration optimization of FPGA accelerators through reinforcement learning for enhanced performance and resource utilization. Eng. Res. Express 2025, 7, 015317. [Google Scholar] [CrossRef]

- Patel, V.; Shah, A. Design and implementation of low power FPGA-based optimal multiband filter with Spline function for denoising ECG signals. Comput. Methods Biomech. Biomed. Eng. 2025, 28, 226–237. [Google Scholar] [CrossRef]

- Reddy, V.H.P.; Kumar, P.K. FPGA enabled ECG signal reconstruction based on an enhanced orthogonal matching pursuit algorithm. Integration 2025, 101, 102311. [Google Scholar] [CrossRef]

- Cai, Z.; Li, P.; Cheng, L.; Yuan, D.; Li, M.; Li, H. A high performance heterogeneous hardware architecture for brain computer interface. Biomed. Eng. Lett. 2024, 15, 217–227. [Google Scholar] [CrossRef]

- Pillai, H.H.; P S, L.P.; Ekanayaka, K.U.; Suthakorn, J.; Pillai, B.M. Bio-Signal Activated FPGA-Based System for Robotic-Assisted Rehabilitation. In Proceedings of the 2023 3rd International Conference on Robotics, Automation and Artificial Intelligence (RAAI), Singapore, 14–16 December 2023; pp. 195–199. [Google Scholar] [CrossRef]

- Perry, J.; Bekey, G. EMG-force relationships in skeletal muscle. Crit. Rev. Biomed. Eng. 1981, 7, 1–22. [Google Scholar] [PubMed]

- Gao, B.; Han, Y.; Zhou, Y.; Yu, J.; Li, S.; Dong, A. Wireless Portable Dry Electrode Multi-channel sEMG Acquisition System. In Proceedings of the Wireless Artificial Intelligent Computing Systems and Applications; Cai, Z., Takabi, D., Guo, S., Zou, Y.,, Eds.; Springer: Cham, Switzerland, 2025; pp. 124–135. [Google Scholar] [CrossRef]

- Gautam, Y.; Jebelli, H. Design of flexible polyimide-based serpentine EMG sensor for AI-enabled fatigue detection in construction. Sens. Bio-Sens. Res. 2024, 46, 100713. [Google Scholar] [CrossRef]

- Hambly, M.J.; de Sousa, A.C.C.; Pizzolato, C. Comparison of filtering methods for real-time extraction of the volitional EMG component in electrically stimulated muscles. Biomed. Signal Process. Control 2024, 87, 105471. [Google Scholar] [CrossRef]

- Esposito, D.; Centracchio, J.; Bifulco, P.; Andreozzi, E. A smart approach to EMG envelope extraction and powerful denoising for human–machine interfaces. Sci. Rep. 2023, 13, 7768. [Google Scholar] [CrossRef]

- Choi, H.S. Electromyogram (EMG) Signal Classification Based on Light-Weight Neural Network with FPGAs for Wearable Application. Electronics. 2023, 12, 1398. [Google Scholar] [CrossRef]

- Kok, C.L.; Ho, C.K.; Tan, F.K.; Koh, Y.Y. Machine Learning-Based Feature Extraction and Classification of EMG Signals for Intuitive Prosthetic Control. Appl. Sci. 2024, 14, 5784. [Google Scholar] [CrossRef]

- Dhanush Babu, R.; Siva Adithya, S.; Dhanalakshmi, M. Design and development of an EMG controlled transfemoral prosthesis. Meas. Sensors 2024, 36, 101399. [Google Scholar] [CrossRef]

- Boschmann, A.; Agne, A.; Thombansen, G.; Witschen, L.; Kraus, F.; Platzner, M. Zynq-based acceleration of robust high density myoelectric signal processing. J. Parallel Distrib. Comput. 2019, 123, 77–89. [Google Scholar] [CrossRef]

- Farina, D.; Merletti, R.; Enoka, R.M. The extraction of neural strategies from the surface EMG: 2004–2024. J. Appl. Physiol. 2025, 138, 121–135. [Google Scholar] [CrossRef]

- Andalib, A.; Farina, D.; Vujaklija, I.; Negro, F.; Aszmann, O.C.; Bashirullah, R.; Principe, J.C. Unsupervised decoding of spinal motor neuron spike trains for estimating hand kinematics following targeted muscle reinnervation. arXiv 2019. [Google Scholar] [CrossRef]

- Konuk, M.E.; Şahin, D.O.; Kılıç, E. EMG Verilerinin Sınıflandırılmasında PCA Boyut İndirgeme Tekniğinin Etkisinin İncelenmesi/Investigating the Effect of PCA Dimension Reduction Technique in Classifying EMG Data. In Proceedings of the 2024 International Congress on Human–Computer Interaction, Optimization and Robotic Applications (HORA), Istanbul, Turkiye, 23–25 May 2024; pp. 1–6. [Google Scholar] [CrossRef]

- Bosco, G. Principal component analysis of electromyographic signals: An overview. Open Rehabil. J. 2010, 3, 127–131. [Google Scholar] [CrossRef]

- Zhu, M.; Guan, X.; Li, Z.; He, L.; Wang, Z.; Cai, K. sEMG-based lower limb motion prediction using CNN-LSTM with improved PCA optimization algorithm. J. Bionic Eng. 2023, 20, 612–627. [Google Scholar] [CrossRef]

- Matrone, G.C.; Cipriani, C.; Carrozza, M.C.; Magenes, G. Real-time myoelectric control of a multi-fingered hand prosthesis using principal components analysis. J. NeuroEng. Rehabil. 2012, 9, 40. [Google Scholar] [CrossRef]

- Cabegin, K.; Lim, M.; Fernan, D.T.; Garcia Santos, R.; Magwili, G. Electromyography-based Control of Prosthetic Arm for Transradial Amputees using Principal Component Analysis and Support Vector Machine Algorithms. In Proceedings of the 2019 IEEE 11th International Conference on Humanoid, Nanotechnology, Information Technology, Communication and Control, Environment, and Management, HNICEM 2019, Laoag, Philippines, 29 November–1 December 2019. [Google Scholar] [CrossRef]

- Geethanjali, P. Comparative study of PCA in classification of multichannel EMG signals. Australas. Phys. Eng. Sci. Med. 2015, 38, 331–343. [Google Scholar] [CrossRef] [PubMed]

- Qi, J.; Jiang, G.; Li, G.; Sun, Y.; Tao, B. Surface EMG hand gesture recognition system based on PCA and GRNN. Neural Comput. Appl. 2020, 32, 6343–6351. [Google Scholar] [CrossRef]

- Bachanna, P.; Gadgay, B.; Chatterjee, S. Probabilistic Principle Component Analysis based Feature Extraction of Embedded System Applications with Deep Neural Network based Implementation in FPGA. Int. J. Recent Innov. Trends Comput. Commun. 2023, 11, 45–51. [Google Scholar] [CrossRef]

- Yadav, M.; Koul, R.; Suneja, K. FPGA Based Hardware Design of PCA for Face Recognition. In Proceedings of the 2020 7th International Conference on Signal Processing and Integrated Networks (SPIN), Noida, India, 27–28 February 2020; pp. 642–646. [Google Scholar] [CrossRef]

- Ghasemzadeh, H.; Fallahzadeh, R.; Jafari, R. A Hardware-Assisted Energy-Efficient Processing Model for Activity Recognition Using Wearables. ACM Trans. Des. Autom. Electron. Syst. 2016, 21, 1–27. [Google Scholar] [CrossRef]

- Castruita-López, J.F.; Aviles, M.; Toledo-Pérez, D.C.; Macías-Socarrás, I.; Rodríguez-Reséndiz, J. Electromyography Signals in Embedded Systems: A Review of Processing and Classification Techniques. Biomimetics 2025, 10, 166. [Google Scholar] [CrossRef] [PubMed]

- Cerina, L.; Cancian, P.; Franco, G.; Santambrogio, M.D. A hardware acceleration for surface EMG non-negative matrix factorization. In Proceedings of the 2017 IEEE International Parallel and Distributed Processing Symposium Workshops (IPDPSW), Lake Buena Vista, FL, USA, 29 May–2 June 2017; pp. 168–174. [Google Scholar] [CrossRef]

- Najafi, T.A.; Calero, J.A.M.; Thevenot, J.; Duc, B.; Albini, S.; Amirshahi, A.; Taji, H.; Beneyto, M.J.B.; Affanni, A.; Atienza, D. VersaSens: An Extendable Multimodal Platform for Next-Generation Edge-AI Wearables. IEEE Trans. Circuits Syst. Artif. Intell. 2024, 1, 83–96. [Google Scholar] [CrossRef]

- Meddah, K.; Zairi, H.; Bessekri, B.; Cherrih, H.; Kedir-Talha, M. FPGA implementation of Epileptic Seizure detection based on DWT, PCA and Support Vector Machine. In Proceedings of the 2020 Second International Conference on Embedded & Distributed Systems (EDiS), Oran, Algeria, 3 November 2020; pp. 141–146. [Google Scholar] [CrossRef]

- Cerina, L.; Franco, G.; Cancian, P.; Santambrogio, M.D. Robustness of Surface EMG Classifiers with Fixed-Point Decomposition on Reconfigurable Architecture. In Proceedings of the 2018 IEEE International Parallel and Distributed Processing Symposium Workshops (IPDPSW), Vancouver, BC, Canada, 21–25 May 2018; pp. 146–153. [Google Scholar] [CrossRef]

- Lv, H.; Wang, Y.; Hao, B. Lower limb joint angle estimation based on surface electromyography signals. Biomed. Signal Process. Control 2025, 104, 107563. [Google Scholar] [CrossRef]

- Kokkinis, A.; Siozios, K. Fast Resource Estimation of FPGA-Based MLP Accelerators for TinyML Applications. Electronics 2025, 14, 247. [Google Scholar] [CrossRef]

- Press, W.H.; Teukolsky, S.A.; Vetterling, W.T.; Flannery, B.P. Numerical Recipes: Example Book C, 2nd ed.; Cambridge University Press: Cambridge, UK, 1992. [Google Scholar]

- Fay, R.; Hsieh, A.; Jeang, D.; Jenkins, B. Floating Point Library. 2023. Available online: https://github.com/xesscorp/Floating_Point_Library-JHU (accessed on 5 May 2023).

- Kirti; Sohal, H.; Jain, S. FPGA implementation of collateral and sequence pre-processing modules for low power ECG denoising module. Inform. Med. Unlocked 2022, 28, 100838. [Google Scholar] [CrossRef]

- Sohal, H.; Jain, S. FPGA Implementation of Power-Efficient ECG Pre-Processing Block; Jaypee University of Information Technology: Solan, India, 2019. [Google Scholar]

| Metric | Main Purpose | Sensitivity | Applications |

|---|---|---|---|

| MAV | Measures average amplitude. | Signal amplitude. | Muscle activation, fatigue. |

| WL | Captures signal complexity and energy. | Amplitude and frequency. | Feature extraction, signal analysis. |

| SSC | Measures frequency content. | Changes in slope. | Movement detection, fatigue. |

| ZC | Measures signal frequency. | Zero-crossing events. | Pattern recognition, movement control. |

| Implementation | Processing Time (µs) | Power (mW) |

|---|---|---|

| PS (ARM Cortex-A9) | 660 | 1531 |

| PL (Custom Logic) | 90 | 489 |

| Offset | Address | Description |

|---|---|---|

| 18 | 43C0048 | MAV Sensor 1 |

| 16 | 43C0040 | WL Sensor 1 |

| 22 | 43C0058 | ZC Sensor 1 |

| 30 | 43C0078 | SSC Sensor 1 |

| 15 | 43C003C | MAV Sensor 2 |

| 13 | 43C0034 | WL Sensor 2 |

| 21 | 43C0054 | ZC Sensor 2 |

| 29 | 43C0074 | SSC Sensor 2 |

| 12 | 43C0030 | MAV Sensor 3 |

| 10 | 43C0028 | WL Sensor 3 |

| 20 | 43C0050 | ZC Sensor 3 |

| 28 | 43C0070 | SSC Sensor 3 |

| 9 | 43C0024 | MAV Sensor 4 |

| 7 | 43C001C | WL Sensor 4 |

| 19 | 43C004C | ZC Sensor 4 |

| 27 | 43C006C | SSC Sensor 4 |

| Module (ID) | LUTs | Registers | F7Mux | F8Mux | Slice | LUT/Logic | LUT/Memory | RAM | DSPs |

|---|---|---|---|---|---|---|---|---|---|

| AXI BRAM_CTRL | 184 | 197 | 0 | 0 | 86 | 184 | 0 | 0 | 0 |

| AXI MEM_GEN | 9 | 12 | 0 | 0 | 10 | 7 | 2 | 2 | 0 |

| fp_divAav1 | 764 | 1352 | 0 | 0 | 257 | 728 | 36 | 0 | 0 |

| fp_divAav2 | 764 | 1352 | 0 | 0 | 272 | 728 | 36 | 0 | 0 |

| fp_divAav3 | 764 | 1352 | 0 | 0 | 271 | 728 | 36 | 0 | 0 |

| fp_divAav4 | 764 | 1352 | 0 | 0 | 315 | 728 | 36 | 0 | 0 |

| fp_mulPCA0 | 87 | 166 | 0 | 0 | 79 | 75 | 12 | 0 | 2 |

| fp_mulPCA1 | 86 | 166 | 0 | 0 | 71 | 75 | 11 | 0 | 2 |

| fp_mulPCA2 | 87 | 166 | 0 | 0 | 76 | 75 | 12 | 0 | 2 |

| fp_mulPCA3 | 87 | 166 | 0 | 0 | 79 | 75 | 11 | 0 | 2 |

| mySystemip | 2509 | 4405 | 64 | 0 | 1729 | 2509 | 0 | 0 | 0 |

| processing_module | 24,025 | 19,029 | 2368 | 1184 | 9137 | 24,025 | 0 | 0 | 0 |

| Processing_system | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| AXI_Periph | 537 | 496 | 0 | 0 | 213 | 498 | 39 | 0 | 0 |

| rst_ps7_100M | 16 | 40 | 0 | 0 | 15 | 15 | 1 | 0 | 0 |

| fp_S1SSC_Div | 764 | 1352 | 0 | 0 | 308 | 728 | 36 | 0 | 0 |

| fp_S1ZC_Div | 764 | 1352 | 0 | 0 | 263 | 728 | 36 | 0 | 0 |

| fp_S2SSC_Div | 764 | 1352 | 0 | 0 | 302 | 728 | 36 | 0 | 0 |

| fp_S2ZC_Div | 764 | 1352 | 0 | 0 | 279 | 728 | 36 | 0 | 0 |

| fp_S3SSC_Div | 764 | 1352 | 0 | 0 | 264 | 728 | 36 | 0 | 0 |

| fp_S3ZC_Div | 764 | 1352 | 0 | 0 | 288 | 728 | 36 | 0 | 0 |

| fp_S4SSC_Div | 764 | 1352 | 0 | 0 | 265 | 728 | 36 | 0 | 0 |

| fp_S4ZC_Div | 764 | 1352 | 0 | 0 | 286 | 728 | 36 | 0 | 0 |

| Total | 36,795 | 41,067 | 2432 | 1184 | 14,865 | 36,274 | 520 | 2 | 8 |

| Module (ID) | LUTs | Registers | F7Mux | F8Mux | Slice | LUT/Logic | LUT/Memory | RAM | DSPs |

|---|---|---|---|---|---|---|---|---|---|

| module_metrics | 15,395 | 7028 | 0 | 0 | 4793 | 15,395 | 0 | 0 | 0 |

| met_mod_s1 | 3850 | 1757 | 0 | 0 | 1261 | 3850 | 0 | 0 | 0 |

| met_mod_s2 | 3851 | 1757 | 0 | 0 | 1214 | 3851 | 0 | 0 | 0 |

| met_mod_s3 | 3845 | 1757 | 0 | 0 | 1352 | 3845 | 0 | 0 | 0 |

| met_mod_s4 | 3849 | 1757 | 0 | 0 | 1236 | 3849 | 0 | 0 | 0 |

| pca_module | 8427 | 10,498 | 2368 | 1184 | 4731 | 8427 | 0 | 0 | 0 |

| gen_add_mul_0 | 734 | 130 | 0 | 0 | 217 | 734 | 0 | 0 | 0 |

| gen_add_mul_1 | 734 | 130 | 0 | 0 | 213 | 734 | 0 | 0 | 0 |

| gen_add_mul_2 | 733 | 130 | 0 | 0 | 206 | 733 | 0 | 0 | 0 |

| gen_add_mul_3 | 737 | 130 | 0 | 0 | 210 | 737 | 0 | 0 | 0 |

| Total | 42,155 | 25,074 | 2368 | 1184 | 15,433 | 42,155 | 0 | 0 | 0 |

| Project | Sections | DSPs | Slice DUT | Power (W) |

|---|---|---|---|---|

| ECG denoising paper [38] | Wavelet Implementations | |||

| Wavelet Haar | 18 | 309 | 0.262 | |

| Wavelet Daubechies | 34 | 729 | 0.316 | |

| Wavelet Coiflets | 34 | 729 | 0.313 | |

| Wavelet Biorthogonal | 34 | 729 | 0.301 | |

| Totals | 120 | 2496 | 1.192 | |

| Pre-processing paper [39] | ||||

| Hanning | 7 | 225 | 0.144 | |

| Kaiser | 6 | 220 | 0.121 | |

| Hamming | 6 | 220 | 0.136 | |

| Bartlett | 6 | 220 | 0.121 | |

| Rectangular | 6 | 247 | 0.136 | |

| Blackman | 7 | 247 | 0.142 | |

| Totals | 38 | 1379 | 0.8 | |

| This work | Modules and Main Areas | |||

| Metrics Module | 0 | 15,412 | ||

| PCA Module | 8 | 10,507 | ||

| Clocks | 0.104 | |||

| Signals | 0.179 | |||

| Logic | 0.191 | |||

| DSP | 0.006 | |||

| BRAM and IOs | 0.009 | |||

| Totals | 8 | 25,919 | 0.489 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Mireles-Preciado, C.G.; Toledo-Pérez, D.C.; Gómez-Loenzo, R.A.; Aviles, M.; Rodríguez-Reséndiz, J. Hardware–Software Co-Design Architecture for Real-Time EMG Feature Processing in FPGA-Based Prosthetic Systems. Algorithms 2025, 18, 617. https://doi.org/10.3390/a18100617

Mireles-Preciado CG, Toledo-Pérez DC, Gómez-Loenzo RA, Aviles M, Rodríguez-Reséndiz J. Hardware–Software Co-Design Architecture for Real-Time EMG Feature Processing in FPGA-Based Prosthetic Systems. Algorithms. 2025; 18(10):617. https://doi.org/10.3390/a18100617

Chicago/Turabian StyleMireles-Preciado, Carlos Gabriel, Diana Carolina Toledo-Pérez, Roberto Augusto Gómez-Loenzo, Marcos Aviles, and Juvenal Rodríguez-Reséndiz. 2025. "Hardware–Software Co-Design Architecture for Real-Time EMG Feature Processing in FPGA-Based Prosthetic Systems" Algorithms 18, no. 10: 617. https://doi.org/10.3390/a18100617

APA StyleMireles-Preciado, C. G., Toledo-Pérez, D. C., Gómez-Loenzo, R. A., Aviles, M., & Rodríguez-Reséndiz, J. (2025). Hardware–Software Co-Design Architecture for Real-Time EMG Feature Processing in FPGA-Based Prosthetic Systems. Algorithms, 18(10), 617. https://doi.org/10.3390/a18100617