1. Introduction

The inverter is known as the basic logic gate of any digital Integrated Circuit (IC) technology, and it is an integral part of all digital systems. With the emergence of new technologies, designers are focusing on building the basic blocks, such as inverters [

1,

2]. Much work has been conducted to overcome the performance bottleneck in CMOS inverters [

3]. The inverters’ performance has been investigated in order to come up with robust circuits [

4]. As technology has been sized down, circuit design has become more challenging, and the need for designing accurate and fast circuits with low time delay has become an important issue [

5,

6]. The switching characteristics of the inverter are the fundamental parameters used to describe the inverter’s performance. Thus, the switching speed of the inverter’s circuit should be optimized before the design steps to achieve symmetrical switching. Switching time from high to low or from low to high depends on the channel width, length of the transistors, and load capacitance C

L.

The physical structure of the transistors in the CMOS inverter causes parasitic capacitances, because of the segregation of mobile charges across different regions within the device. The value of parasitic capacitances in a transistor depends on its width (W) and the length (L) of its channel. The currents charging and discharging these capacitances are I

Ch and I

Dis, respectively. I

Ch is responsible for the rise time and I

Dis is responsible for the fall time. The flow of I

Ch is through the pull-up section and the flow of I

Dis flow is through the pull-down section [

7]. The significance of output rise and fall time has been discussed on numerous occasions [

8,

9,

10,

11,

12]. To ensure symmetrical sequence many techniques have been developed. In Ref. [

7] two additional transistors were added to regulate the same amount of current from V

dd to match I

Ch with I

Dis. The problem with this method is that the addition of new transistors will lead to larger size circuits and can introduce more noise to the circuit. Others have used time-delay elements to correct the mismatch in the time delay on a chip [

13,

14]. Nevertheless, creating delay elements can be a challenging task due to their extensive design specifications and various trade-offs involved. In this work, instead of adding any new transistors, we focus on matching the rise time and the fall time by finding the optimum values of W and L using the Mayfly Algorithm.

Optimization algorithms use mathematical techniques to iteratively refine the solution until the optimal value is achieved. There are various optimization algorithms available in the literature. Gradient descent [

15,

16], genetic algorithms [

17,

18,

19], RMSProp [

20], and many other optimization algorithms have been used to improve the efficiency and accuracy of solving complex problems. In the published literature, different evolutionary optimization methods have been used to design inverters with optimal switching characteristics. For instance, the PSO technique was used to design the CMOS inverter and its transient performance [

21,

22]. The authors investigated the overall performance of the PSO technique. In [

23,

24], the PSO algorithm was used to design a nano-scale CMOS inverter to improve its symmetrical switching. The results of the PSO method were compared to Spice simulation results.

In [

25,

26,

27,

28,

29], De, Bishnu Prasad, et al., implemented different optimization techniques to obtain the symmetrical switching characteristic of CMOS inverters. In [

25], the PSO with constriction factor and inertia weight approach PSO-CFIWA was used to get the optimal symmetrical switching properties of the CMOS inverter. The performance of the PSO-CFIWA method was compared to that of the real coded genetic algorithm (RGA) and the results showed an improved performance of the PSO-CFIWA. Two different evolutionary optimization methods (DE and RGA) were used in [

26] to obtain an optimal global design. The DE and RGA methods were applied to three different studies with different design parameter ranges and the comparison between them was presented. The DE method was found to be the least cost-effective function compared to other design methods. The Craziness-based Particle Swarm Optimization (CRPSO), presented in [

27], was used to design the CMOS inverter with the optimal switching speed characteristics. The results of the CRPSO method were compared to the RGA method results and the CRPSO method gave better symmetrical switching for the CMOS inverter. In [

28], a hybrid meta-heuristic search method was suggested with a harmony search algorithm (HS) and DE algorithm. This method was called HS-–DE and it was used in CMOS inverter design with symmetrical switching properties to find an improved global solution. The results of HS–DE were compared with PSPICE results. In [

29], the PSO with an aging leader and challenger (ALCPSO) method was employed to design the CMOS inverter with the optimal symmetrical switching characteristics. The simulation results of the ALCPSO method were compared with the simulation results of the RGA. In [

30], a Cuckoo Search Algorithm (CSA), inspired by the parasitic nature brood of a few cuckoo types, was used to optimize the CMOS inverter and to achieve equal values of both the fall time (t

f) and rise time (t

r). The CSA algorithm was also used to achieve equal propagation delay time when switching from low to high and from high to low. The results of the CSA were compared with different methods such as the PSO, the RGA, and the PSO-CFIWA methods. The authors in [

31] used different optimization methods to derive the accuracy equation for the propagation delay time of a ring oscillator. In [

32], the SOS was presented to determine the best values of the channel width (W), length (L), and the output-load’s capacitance (C

L) to achieve symmetrical switching characteristics for the CMOS inverter. The modified approach for Multi-Objective Optimization of Heat Transfer Search (MOMHTS) was presented in [

33]. The MOMHTS method was applied to five problem sets. The modified optimizer method was compared to Multi-Objective Symbiotic Organism Search (MOSOS), Multi-Objective Synchronous Heat Transfer (MOHTS), Multi-Objective Ant System (MOAS), and Multi-Objective Ant Colony System (MOACS).

A novel MA was presented in [

34]. The MA is an optimization algorithm used to find the best solution to a problem in terms of the convergence position and convergence speed. The authors in [

34] compared the results of the MA with the PSO and Firefly Algorithm (FA) algorithms. The MA was improved in [

35]. The equations of the velocity were updated to achieve better results. In [

36], the authors conducted research to examine the key role of the oppositional mayfly optimization for the use in tasks scheduling technique (OMO-TST) related to the cloud computing environment (CC). The OMO–TST was implemented, and the cloud computing environment performance was optimized and controlled. The results showed that implementing the OMO–TST technique for CC can contribute to a significant reduction in the level of complexity related to the computations required for processing data in a cloud system. In addition, the results of their analysis revealed that utilizing the OMO technique for CC can achieve practical usage of resources and enhance the performance of CC at the level of individuals and companies. In [

37], the performance of the negative mayfly optimization method is presented to get the best positions and velocities of the mayflies.

The MA was utilized by researchers to solve various problems and obtain optimal solutions. In a study conducted by Bhattacharyya, et al., the role of MA in machine learning was evaluated for reducing the dataset dimension by eliminating redundant and excessive characteristics [

38]. A novel feature collection method, MA–HS, was developed to achieve this goal [

38]. The MA–HS was employed to enhance feature selection performance by improving the search space and fitness function. The experimental results showed that it outperformed other algorithms such as the genetic algorithm (GA), binary dragonfly algorithm (BDA), binary salp swarm algorithm (BSSA), and whale optimization algorithm (WOA) [

38]. Work was conducted to employ the initial center frequency-guided filter (ICFGF) approach to detect bearing faults through a two-phase process [

39]. In the first phase, energy spectrum distributions were assessed using a variation analysis scale. In the second phase, a modified Mayfly optimization method (MMA) was used to determine the optimal resonance demodulation frequency. Employing the MMA in the ICFGF was found to be effective in detecting faults with high accuracy, as evidenced by results from [

39]. The study also compared ICFGF to other techniques such as conditional variation selection and fast kurtogram, demonstrating its superior performance. The Mayfly method was also used to optimize the model of combined cooling heat and power (CCHP) systems [

40]. The authors in [

40] were able to obtain the optimal size of the components and minimum fuel consumption in the system. It was noted that the Mayfly Algorithm was more effective in providing the required solution in a shorter time. Researchers carried out a study assessing the major contribution of implementing the MA to conduct optimization of the performance of solar photovoltaic thermal collectors PVTC that are integrated with an electric hydrogen generation system [

41]. To achieve the study goal, a solar (PVTC) with a hydrogen generation system has been modeled for predicting several factors related to the performance of the system using artificial intelligence and the Mayfly Algorithm. The MA has been used to improve the forecasting accuracy in the model.

The aim of this research is to utilize the Mayfly Algorithm to determine the ideal circuit parameters that result in minimal rise time in Case I. In Case II, the goal is to use the same algorithm to find the optimal circuit parameters that produce symmetrical fall and rise times for the inverter. In Case III, the focus will be on finding the optimal circuit parameters that lead to an output waveform with symmetrical rise and fall times, as well as a symmetrical propagation delay time. The rest of this paper is organized as follows: the MA is briefly described in

Section 2; the switching characteristics of the CMOS inverter are presented in

Section 3;

Section 4 explains the formulation of the problem; results and Spice simulations are provided in

Section 5; finally,

Section 6 concludes the paper.

2. Mayfly Optimization Algorithm

Optimization problem-solving techniques can be classified into two categories. The first category is heuristic methods, such as kinetic gas molecules, evolutionary programming, particle swarm optimization, simulated annealing, genetic algorithm, and Mayfly Algorithm [

38]. The second category is mathematical methods, such as linear programming, nonlinear programming, and mixed-integer linear programming [

42].

The main goal of an optimization algorithm is to determine the optimal solution to an optimization problem. The MA is a recently proposed algorithm by Zervoudakis and Tsafarakis in 2020 [

34]. The MA is based on the mayfly’s mating procedure and the flight behavior that combines the evolutionary algorithms and the best features of the swarm intelligence optimization algorithms [

34]. In MA, two population sets are randomly generated to represent the female and male sets of the mayflies. The position of each mayfly in the problem space represents a candidate solution to the optimization problem. The mayfly’s position is given by an n-dimensional vector x = (x

1, x

2, …, x

n), where the objective function is computed to evaluate each mayfly’s performance. Each mayfly’s position is updated using its velocity, given by the vector v = (v

1, v

2, …, v

n), and flying direction. The mayfly’s flying direction is determined by the best individual flying experiences of each mayfly’s p

best and the best swarm’s social flying experiences g

best [

34].

The individuals in the MA update their location in the problem space based on their current positions p

it and their velocity v

it for each iteration using Equation (1) [

34].

In the Mayfly Algorithm, a mayfly’s velocity can be explained as the alteration in its location. The flight path of a mayfly is influenced by a complex interplay of its own and the group’s flying encounters. Every mayfly modifies its flight path to get closer to its optimal position (“pbest”) and the most favorable position acquired by any mayfly in the swarm (“gbest”).

The working mechanism of the MA is presented in the following discussion.

2.1. Movement of Male Mayflies

In each iteration, the male mayflies continue the exploring process in swarms. The position of a male mayfly is updated using Equation (2) [

34].

where x

it is the current position of the male mayfly at time step t, and v

it+1 is the mayfly’s velocity. The male mayflies fly a few meters above the water’s surface and evolve at high speeds. The velocity of a male mayfly is calculated as in Equation (3) [

34].

where a

1 and a

2 are the personal and global positive coefficients, respectively, r

p and r

g are the Cartesian distance for personal and global positions, respectively, β represents visibility coefficient, p

best is the best position of a mayfly and g

best is the best global position of a mayfly.

The velocity of the best male mayflies in the current iteration is updated using Equation (4) [

34].

where d is the nuptial dance parameter and r is a random number in the range [−1, 1].

2.2. Movement of Female Mayflies

The female mayflies’ velocity depends on the distance between the females and the males. The female mayflies fly to the male mayflies for mating. The position of a female Mayfly is updated using Equation (5) [

34].

where y

it is the current position of the female mayfly at time step t. In the MA, the best female. The velocity of the female is calculated using Equation (6) [

34].

where v

tij is a female mayfly’s velocity in dimension j at time t, y

tij is the position of female mayfly in the dimension j at time t, x

tij is the position of male mayfly in j at time t, β and a

2 represent visibility coefficient, and a positive constant, respectively, r

mf is the Cartesian distance between female and male mayflies, while f

1 and r represent a random walk coefficient and a random number in the range [−1, 1], respectively.

2.3. Mating of Mayflies

In MA, each couple of mayflies produces two offspring. One is added to the female population arbitrarily and the other is added to the male population. Two offspring are generated after mating as shown in Equations (7) and (8) [

34].

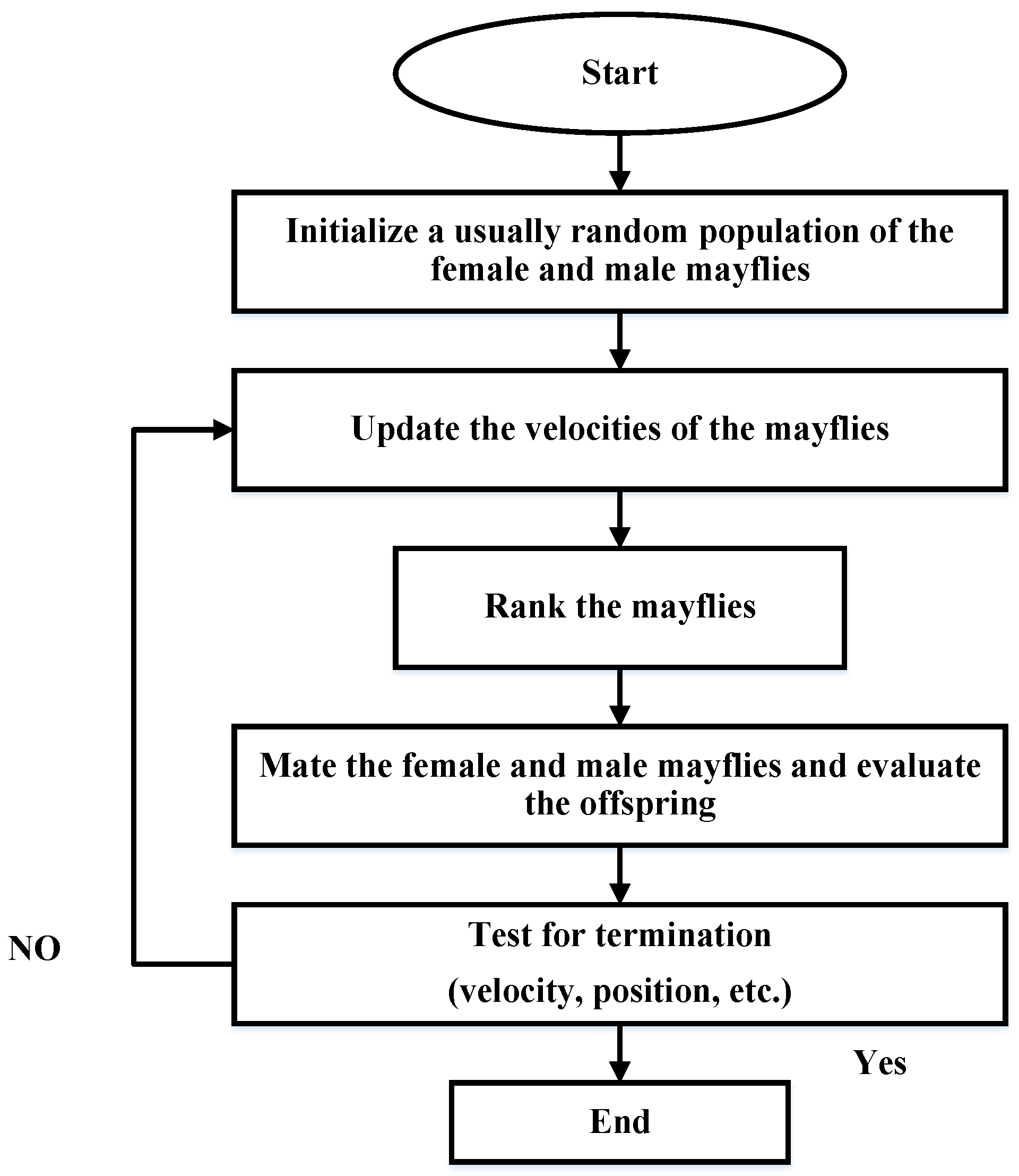

where L is a random number with a Gaussian distribution. The procedure of the MA is described in the flow chart shown in

Figure 1 below [

36].

5. Results

In this section, the optimal switching characteristics of the CMOS inverter are obtained using the Mayfly Optimization Algorithm. A total of eight different design sets are considered with the lower and upper bounds for the design parameters of each design set as seen in

Table 1,

Table 2 and

Table 3 for the three different case studies. TSMC 0.25 µm CMOS model is used in the LT-Spice simulation to get simulation results. The model parameters are V

DD = 2.5 V, V

tn = 0.3655 V, V

tp = 0.5466 V, µ

pC

ox = 51.6 µA/V

2 and µ

nC

ox = 243.6 µA/V

2 [

25,

26,

27,

28,

29,

30,

32].

For Case I, the MA is implemented using MATLAB to find the design parameters needed to minimize the fall time of the output voltage for the CMOS inverter with an identical size of PMOS and NMOS transistors. For each design set in

Table 1, the MA parameters are population size (males and females) equal 20 and number of iterations equal 50. The result of the MA gives the optimal design parameters, i.e., C

L, (W/L) and (t

f), for the CMOS inverter with the minimum fall time. These results are summarized in

Table 4. The results show that the design parameters are within the limits given in

Table 1.

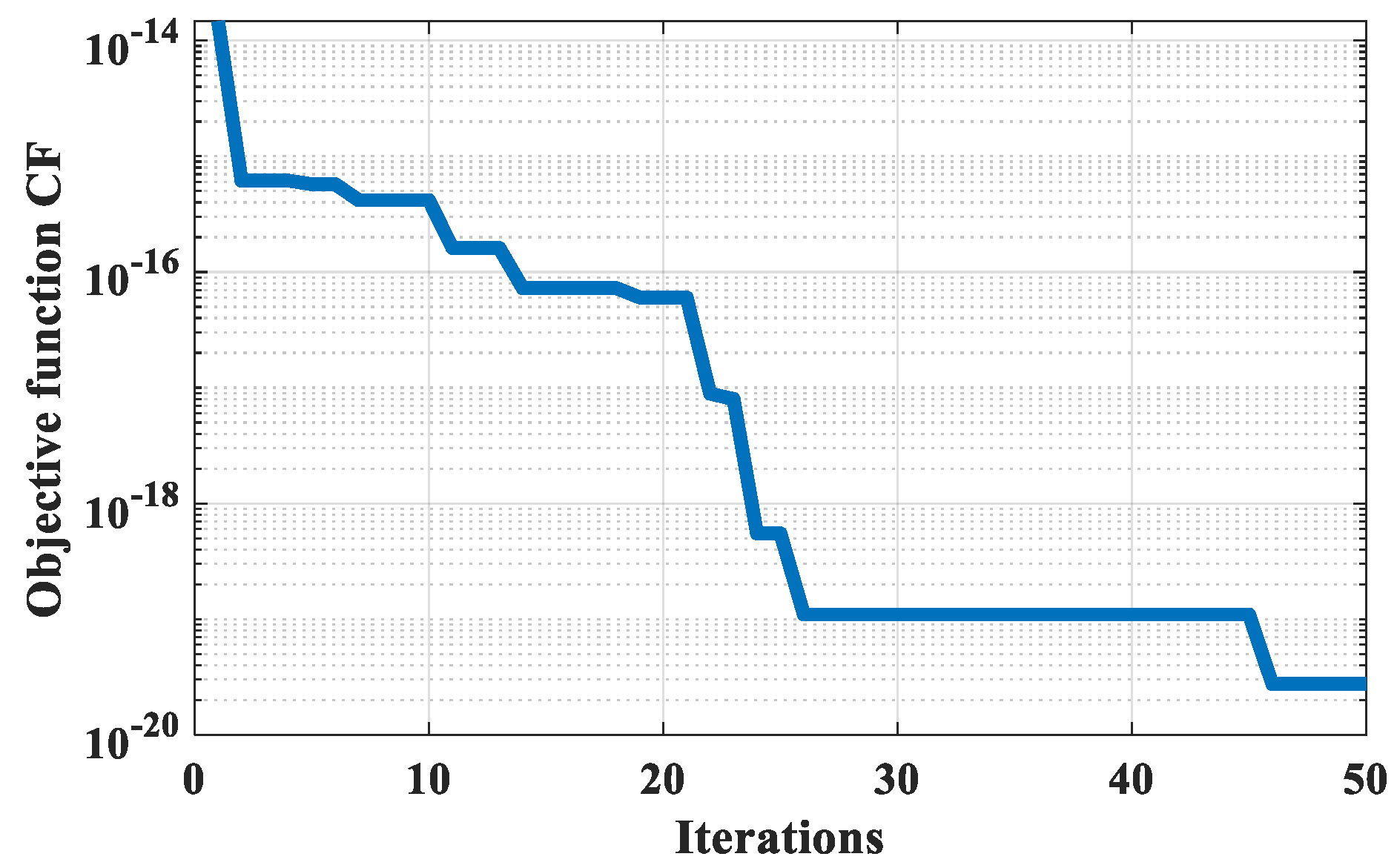

Figure 4 shows the convergence of the objective function, given in 13, with the iterations for the seventh design set. In

Figure 4, it can be seen that the objective function reaches an optimal value of 2.7473019 × 10

−20 s. The 7th design set wass chosen since it has the lowest value of the cost function.

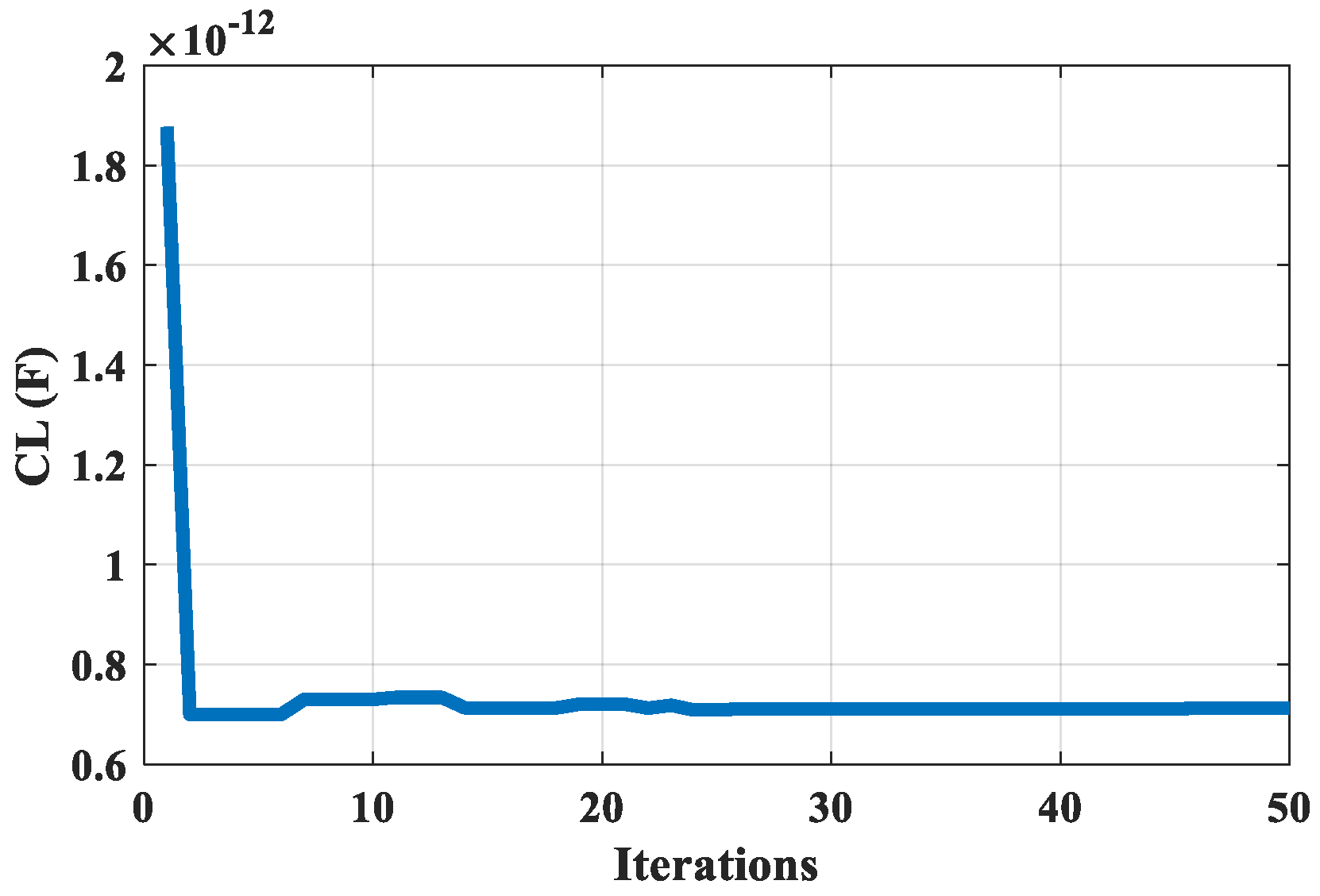

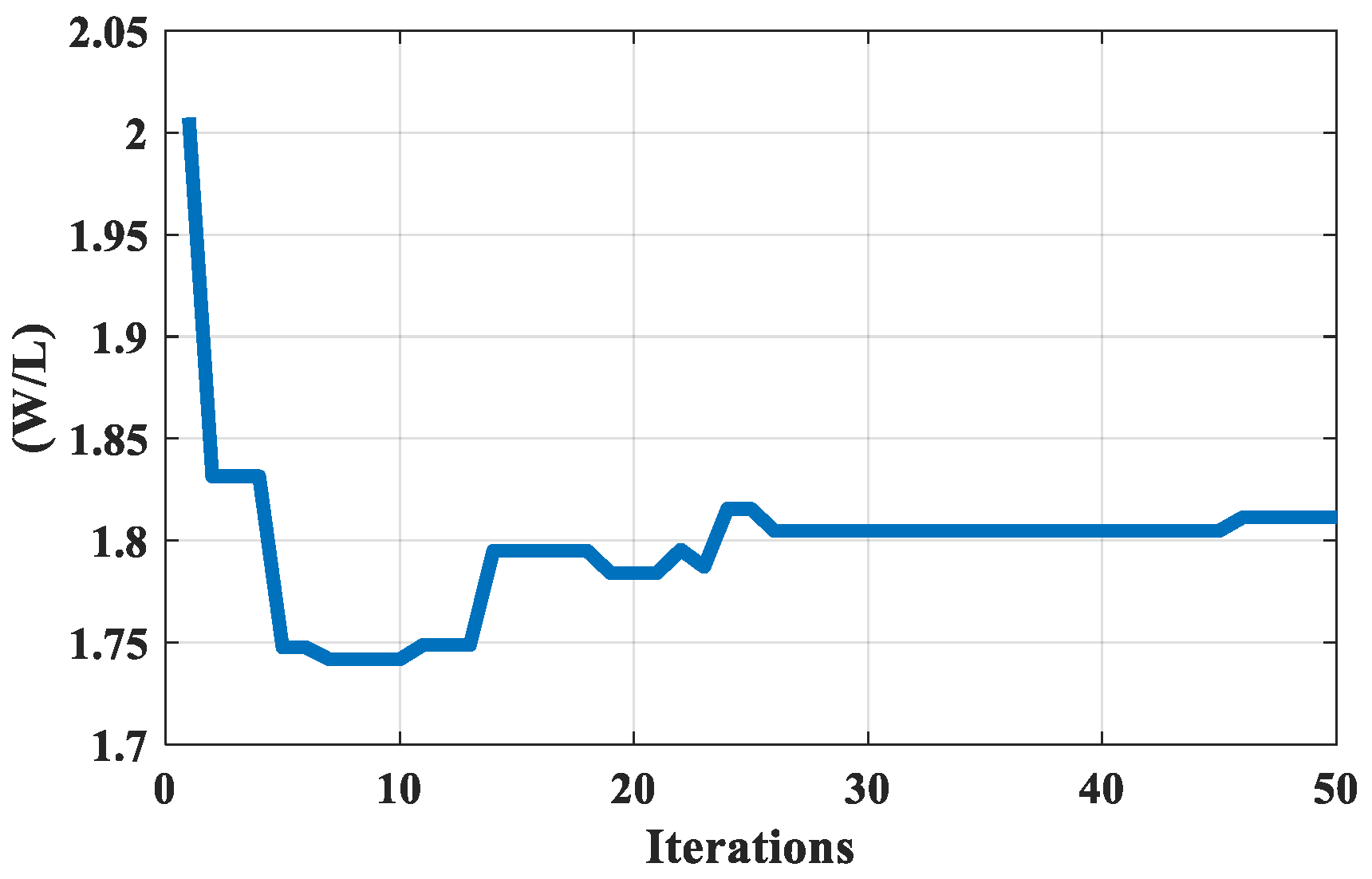

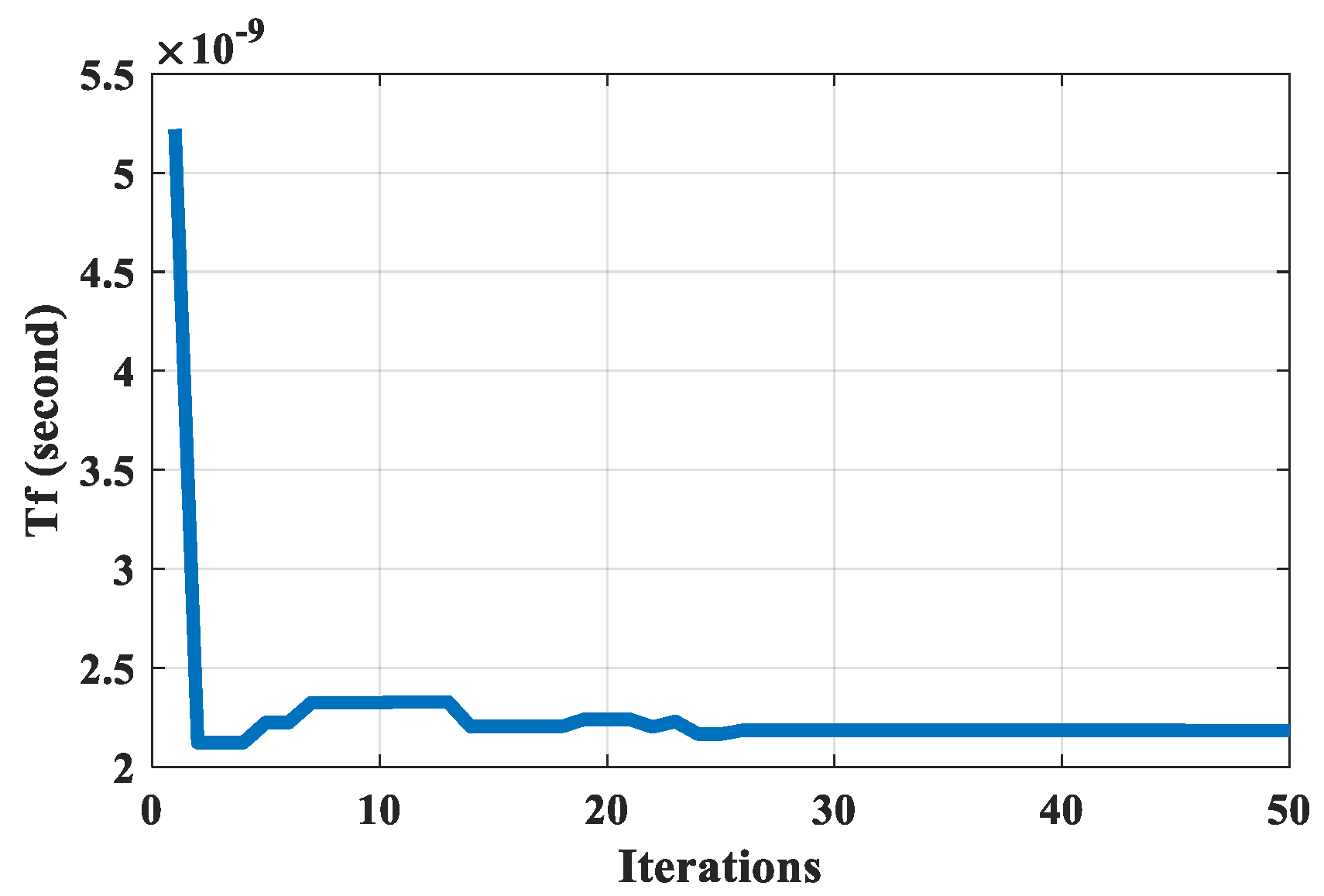

Figure 5,

Figure 6 and

Figure 7 show the convergence plots of the inverter design parameters, C

L, (W/L), and (t

f), for the same design set. In

Figure 5, the optimum value for the load capacitance is 0.7122034 pF and it starts to converge after 24 iterations. The aspect ratio (W/L) optimum value for the seventh set is shown in

Figure 3 to be equal to 1.8113496. The optimum value for the fall time is equal to 2.1820107 ns as shown in

Figure 7.

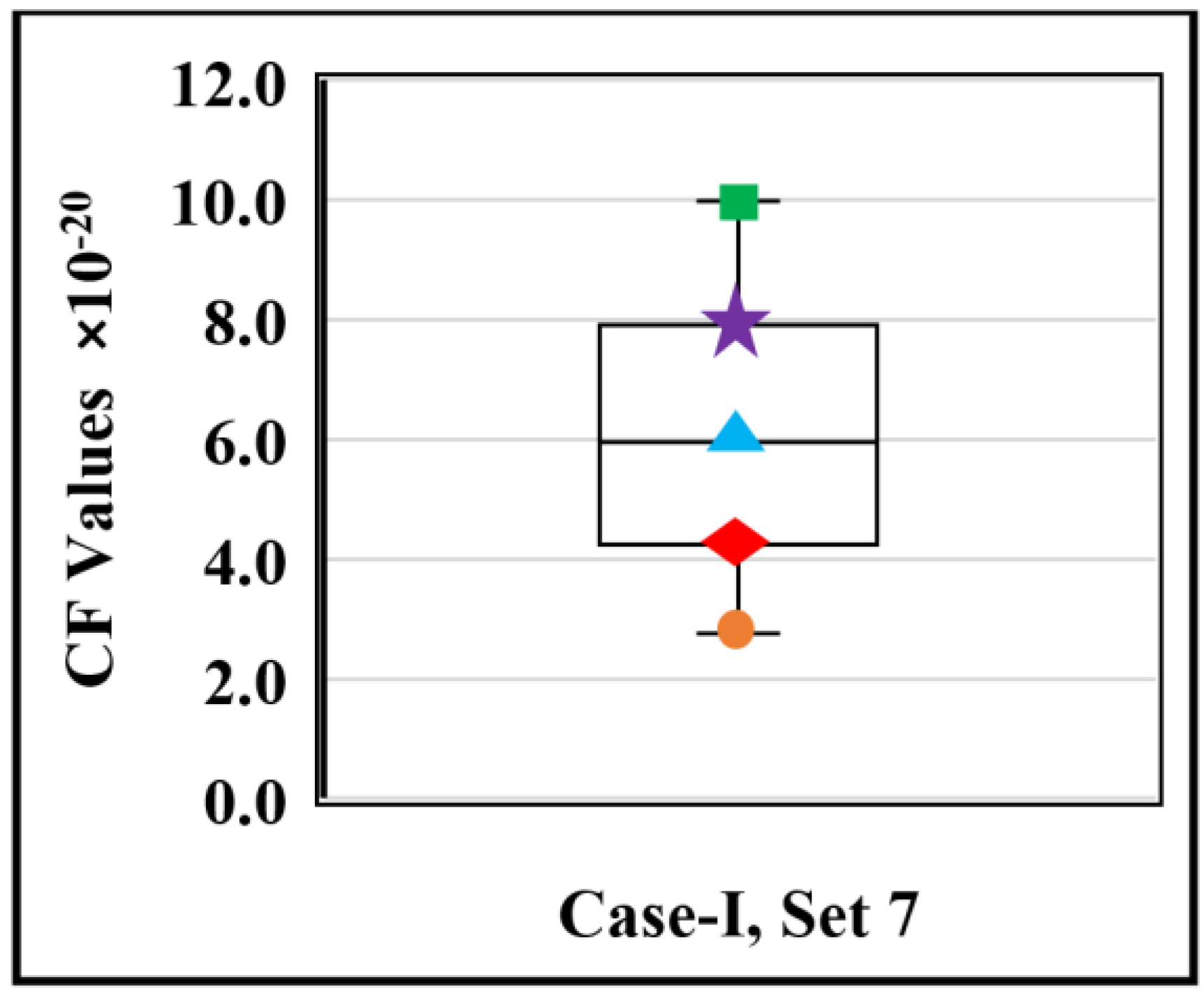

The MA is stochastic by its nature. Therefore, different simulation runs will give different design results. The MA has been run 50 times for the best design set of all the case studies and the resulting CF values have been utilized for the box and whisker plots.

Figure 8 shows the box and whisker plot for the seventh design set of the MA; the green square represents the maximum value, the purple star represents upper whisker, the blue triangle represents median value, the red diamond represents the lower whisker, and the orange circle represents the minimum value. The median value of the CF is found to be equal to 5.95 × 10

−20, the maximum value is 9.98 × 10

−20, and the minimum value is 2.75 × 10

−20, the lower whisker is 4.32594 × 10

−20 and the upper whisker is 7.8561 × 10

−20.

Table 5 shows the simulation results for each design set in case studies I. Spice simulation results show that the MA method is very accurate with small variations due to MOSFET junction capacitance.

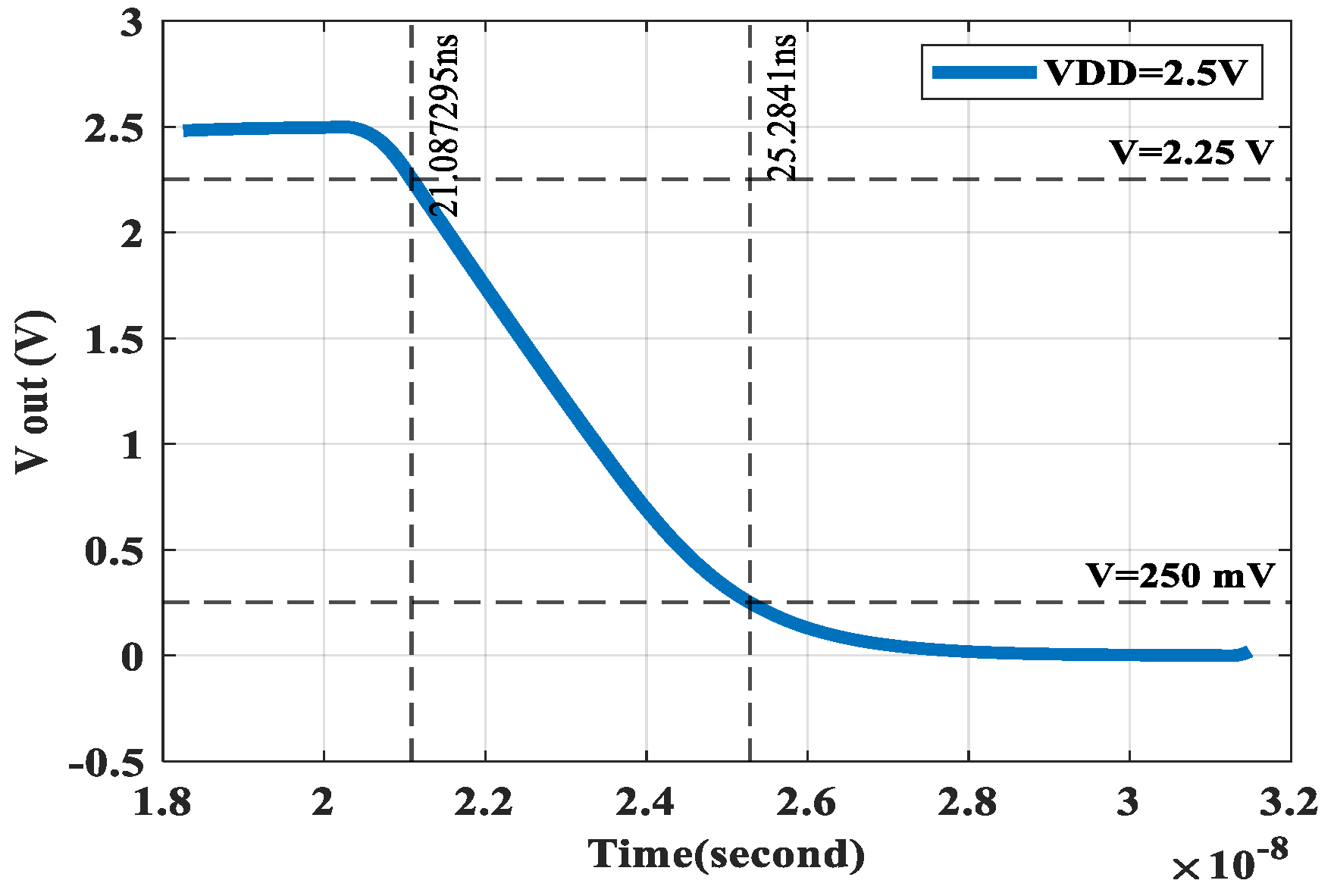

The fall time for the seventh design set of Case I using Spice simulation is shown in

Figure 9. As shown in

Figure 9, using the values obtained using the MA, an optimum value of the fall time equal to 4.1925571 ns is achieved.

For Case II, the optimal CMOS inverter design with symmetrical operation (fall time equals rise time) is found using the MA for the eight different design sets in

Table 2. The MA gives the optimal design parameters needed to minimize the cost function in 15.

Table 6 gives the optimal design parameters needed for the CMOS inverter with a symmetrical operation for the eight design sets of Case II. It is apparent that in

Table 6 the symmetry in the fall time and rise time has been achieved.

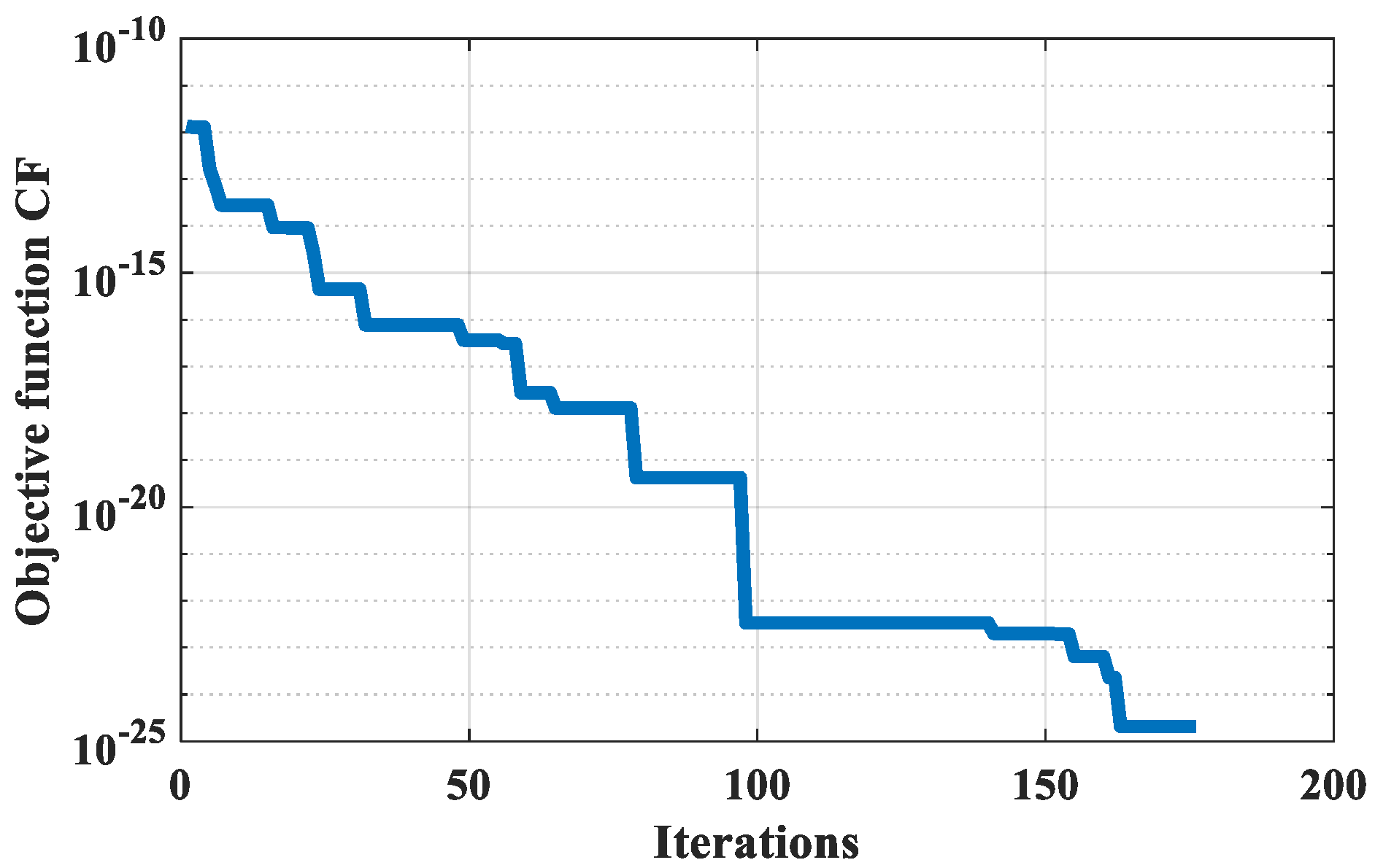

In

Figure 10, a plot of the objective function convergence with MA iteration for the fourth design set is shown; the objective function converges after 160 iterations.

Figure 10,

Figure 11 and

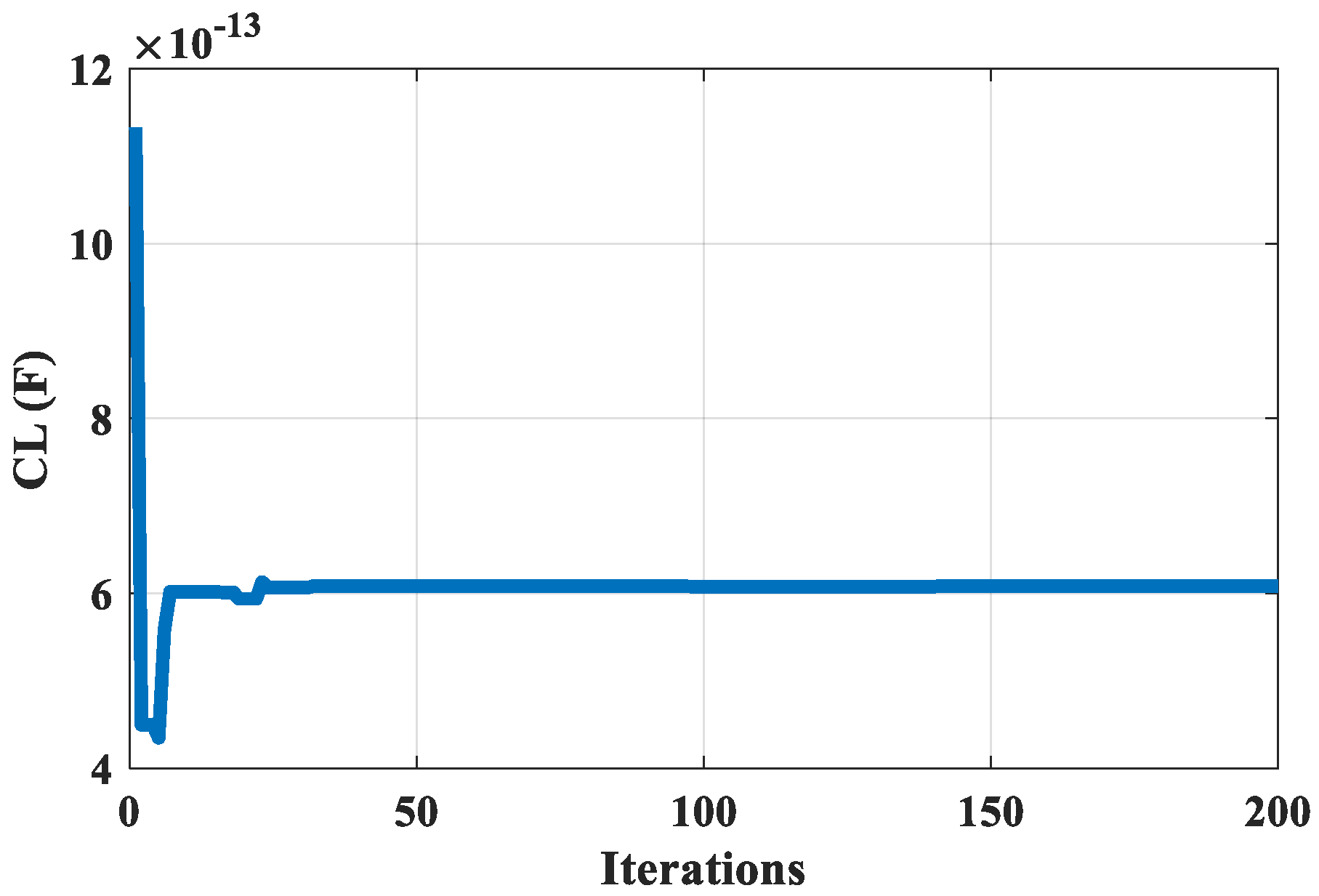

Figure 12 show the convergence plots of the inverter design parameters, CL, (W/L)n, and (W/L)p, for the same design set. In

Figure 11, convergence is achieved after the 25th iteration with an optimum value of 0.6085469 pF for the load capacitance.

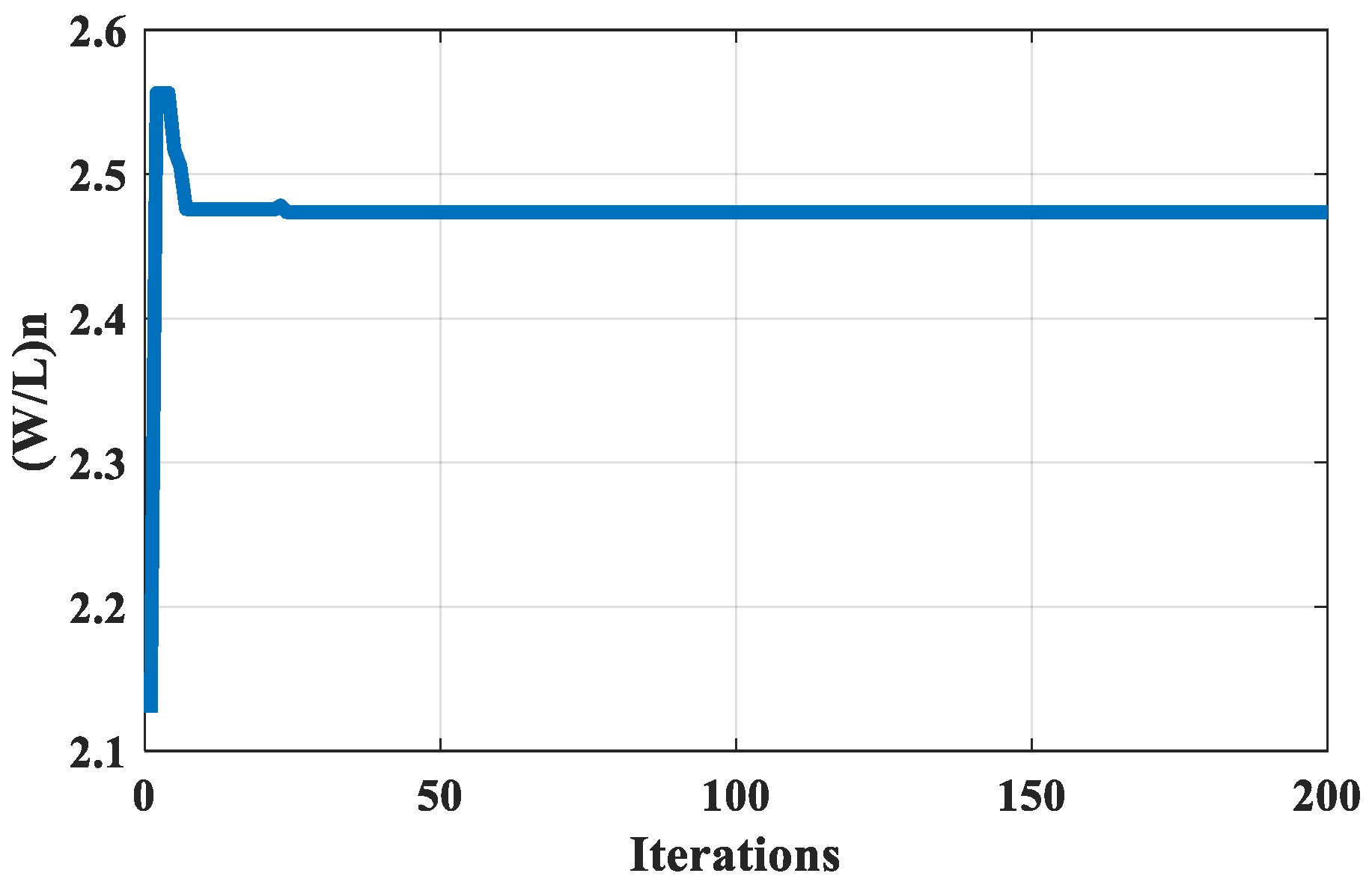

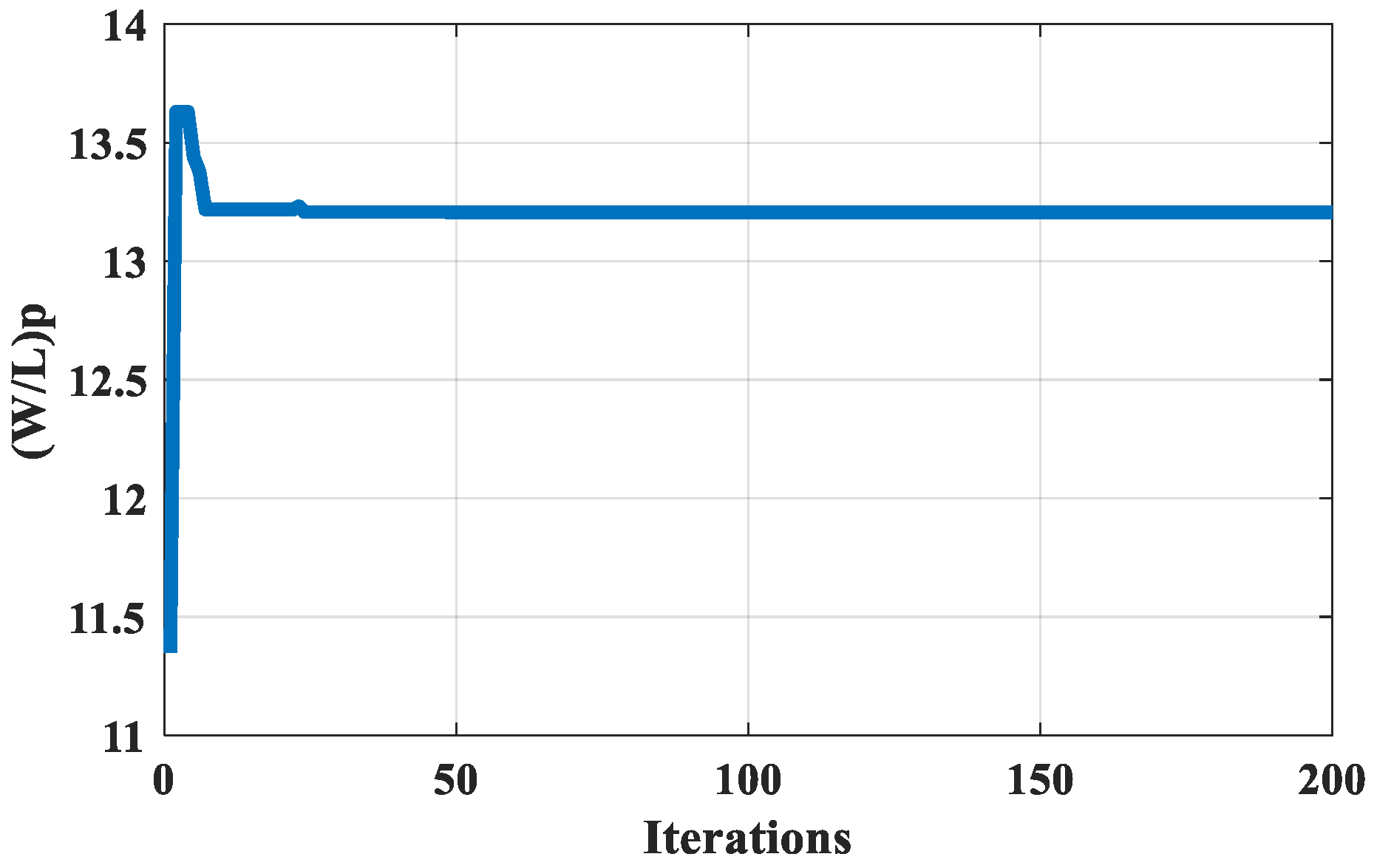

Figure 12 shows the convergence of the NMOS transistor aspect ratio for the fourth set which is equal to 2.4734372. On the other hand, the optimum value for PMOS aspect ratio is equal to 13.206141, as shown in

Figure 13.

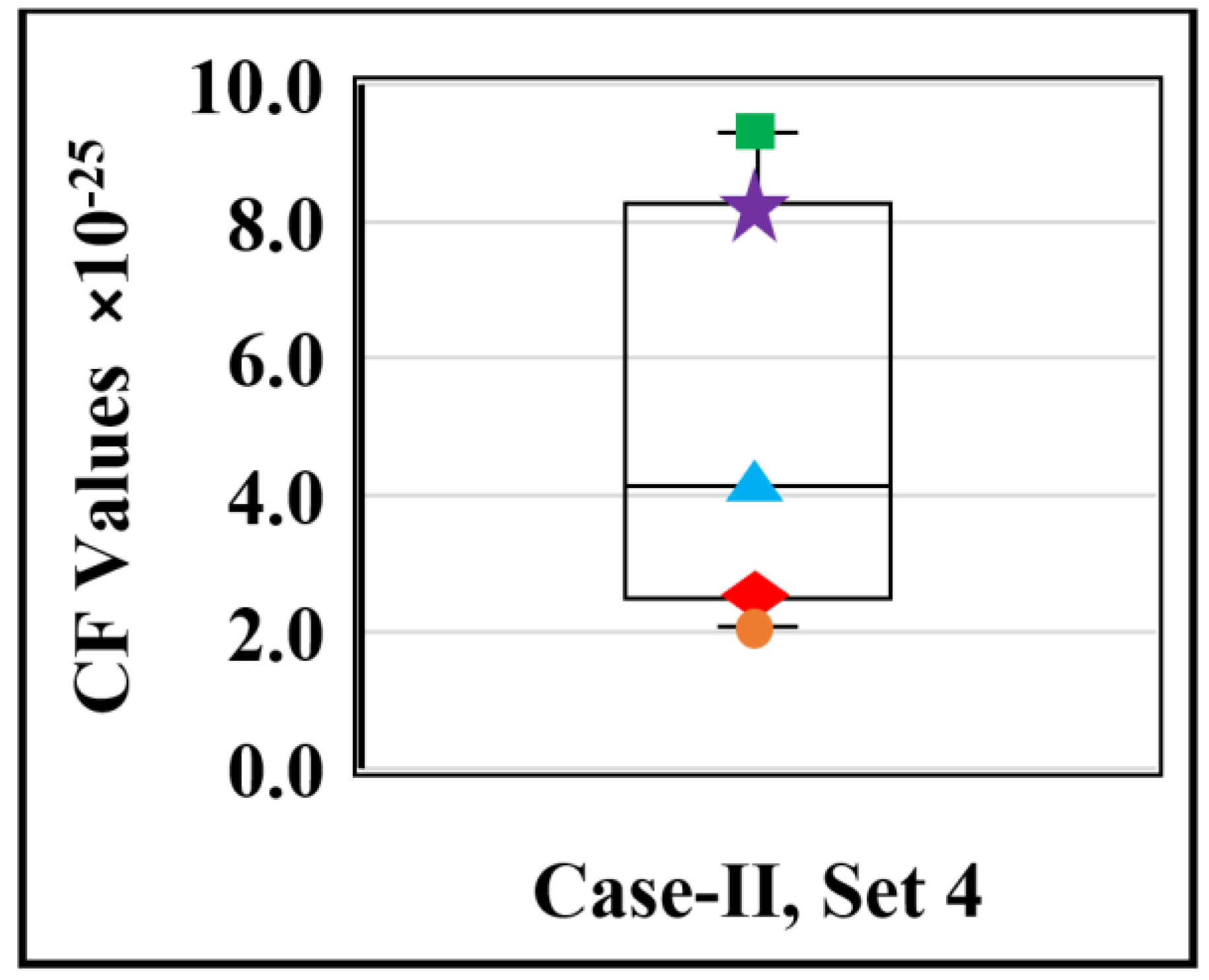

Figure 14 shows the box and whisker plot for the fourth design set of Case II. The green square represents the maximum value, the purple star represents upper whisker, the blue triangle represents median value, the red diamond represents the lower whisker, and the orange circle represents the minimum value. The median value is found to be 4.14 × 10

−25, the maximum value is 9.31 × 10

−25, the minimum value is 2.07 × 10

−25, the lower whisker is 2.6366 × 10

−25, and the upper whisker is 8.2718 × 10

−25.

Table 7 shows the simulation results for each design set in case studies II. Spice simulation results show that the MA method is very accurate with small variations due to MOSFET junction capacitance.

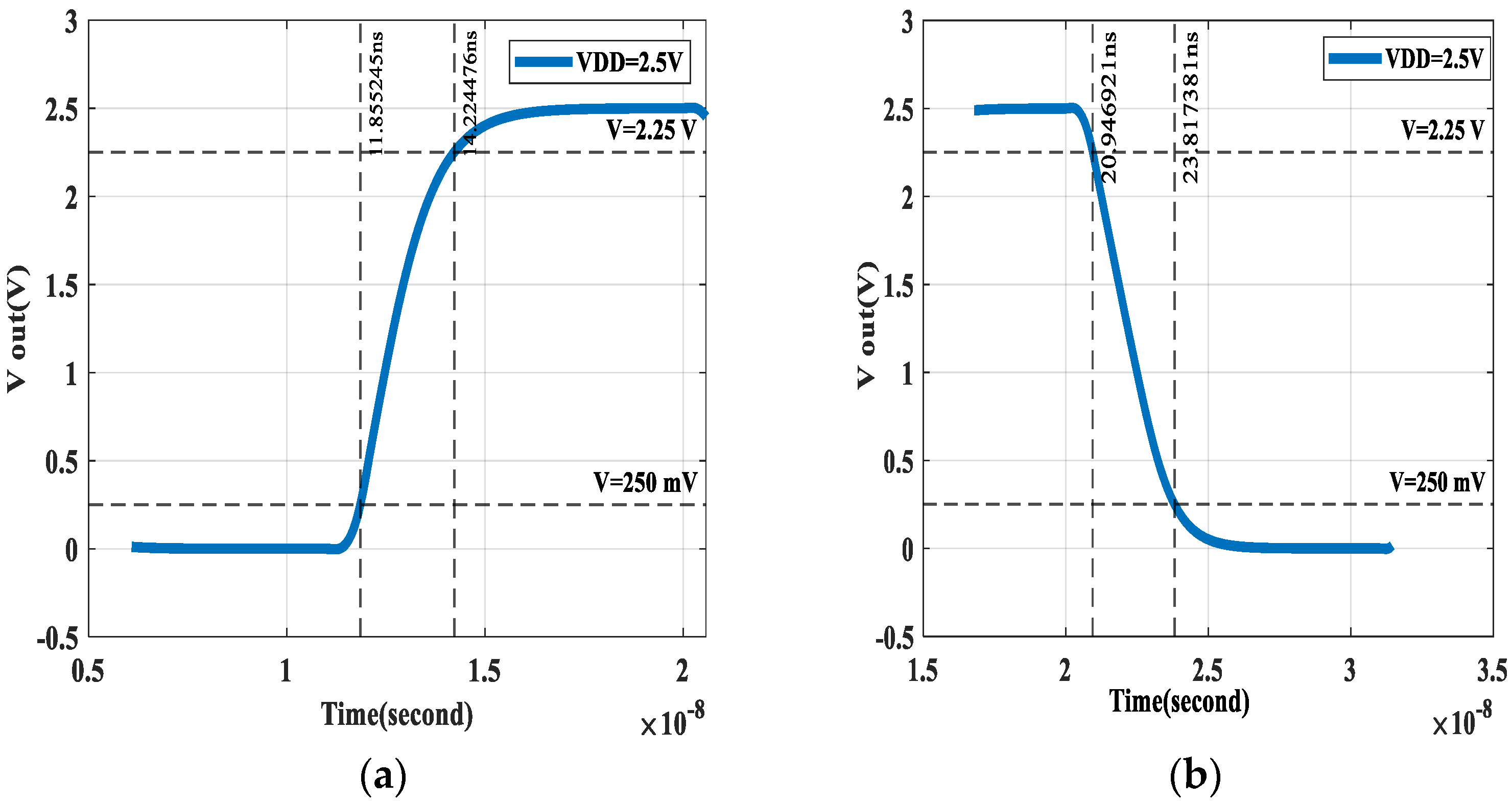

The rise and fall times for the fourth design set of Case II using Spice simulation are shown in

Figure 15. Spice simulations in

Figure 15 show that the designed inverter has a al fall time and rise time with only fractions of nano second difference.

In Case III, the optimal CMOS inverter design for each design set in

Table 3 is found using the MA with population size (males and females) equals 20 and 100 iterations. The results give the optimal design parameters. (W/L)

p, (W/L)

n, and C

L of the CMOS inverter, which minimizes the objective function given in Equation (21). Then, these optimal values of the CMOS inverter parameters are used to calculate the fall time (t

f), the rise time (t

r), and the propagation delay times (t

PHL and t

PLH).

Table 8 summarizes the results obtained using the MA for each design set in Case III, which satisfies the symmetrical output waveform with equal rise and fall times, and the symmetrical propagation delay time (t

PHL equal t

PLH).

Table 9 shows a comparison of the MA results with results obtained by different optimization algorithms. The optimal value of the CF (in ps) of the MA is compared to the optimal value of CF using PSOCFIWA [

25], DE [

26], ALC-PSO [

29], CRPSO [

27], PSO [

30], HS–DE [

32], and SOS [

32]. The results show that the suggested MA outperforms most of the widely used optimization methods in finding the optimal CMOS inverter design with the lowest CF value.

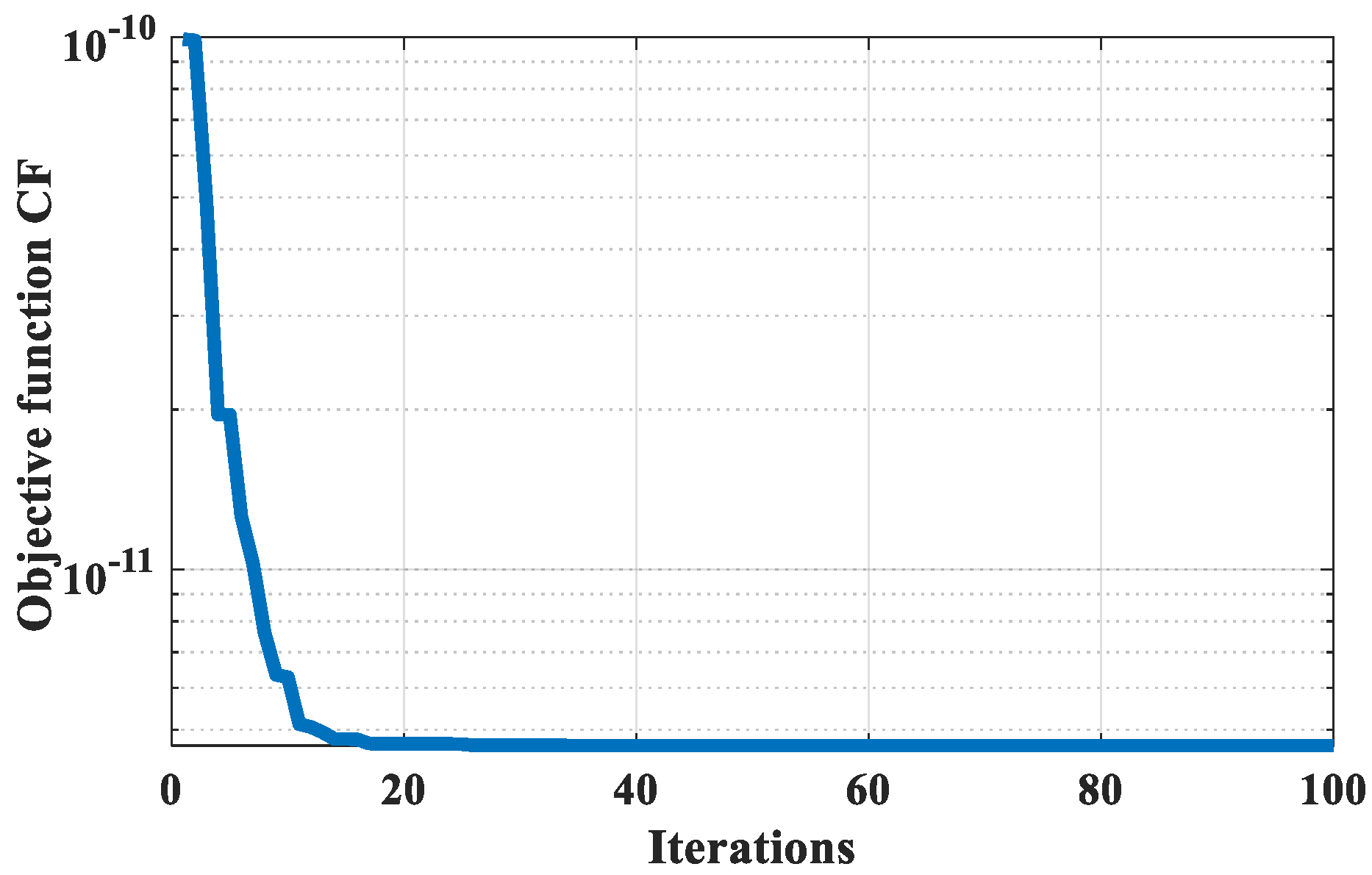

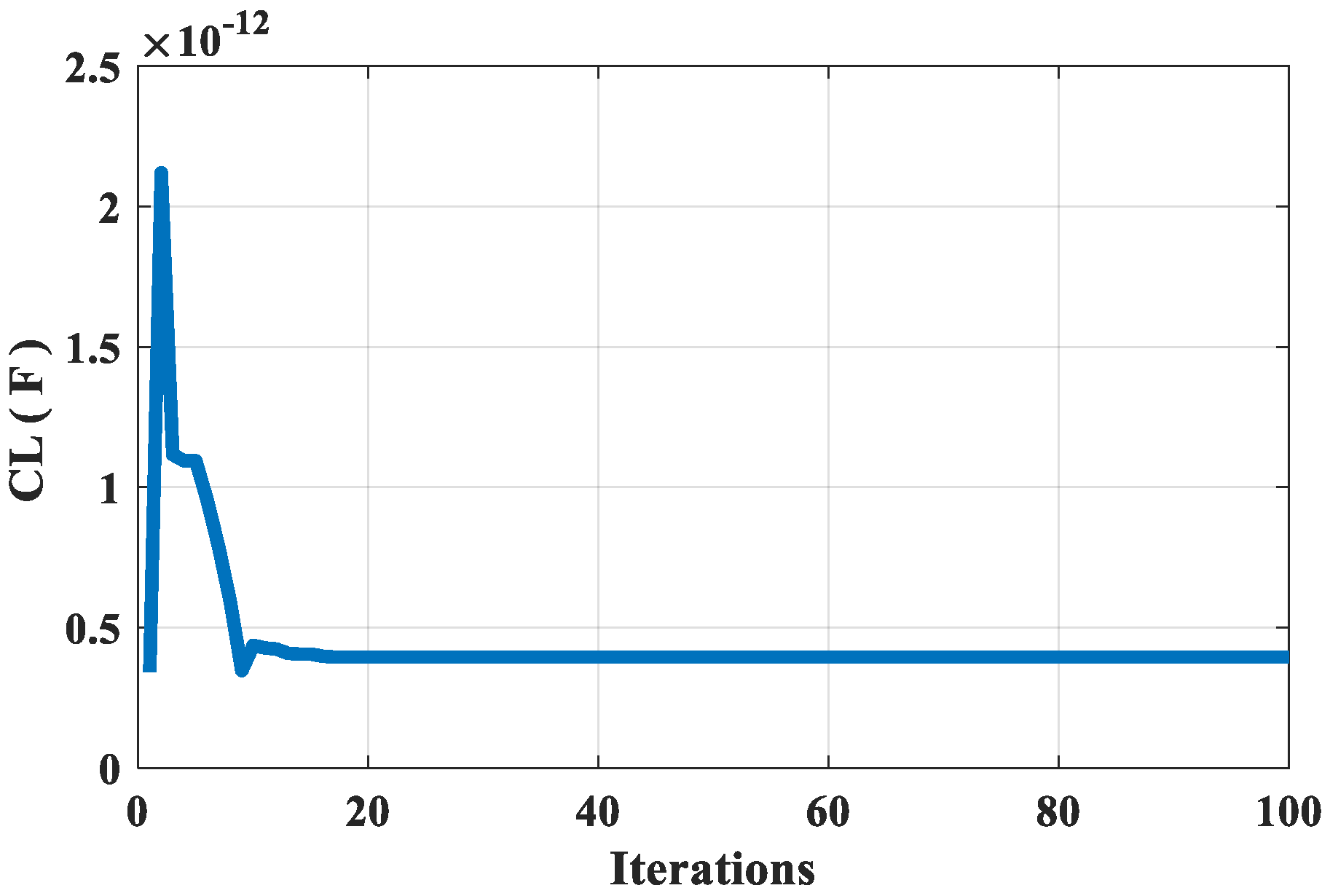

Figure 16 shows the convergence plot of the objective function for the eighth design set. The optimum value of the objective function is 4.67217 ps and it converges after 18 iterations.

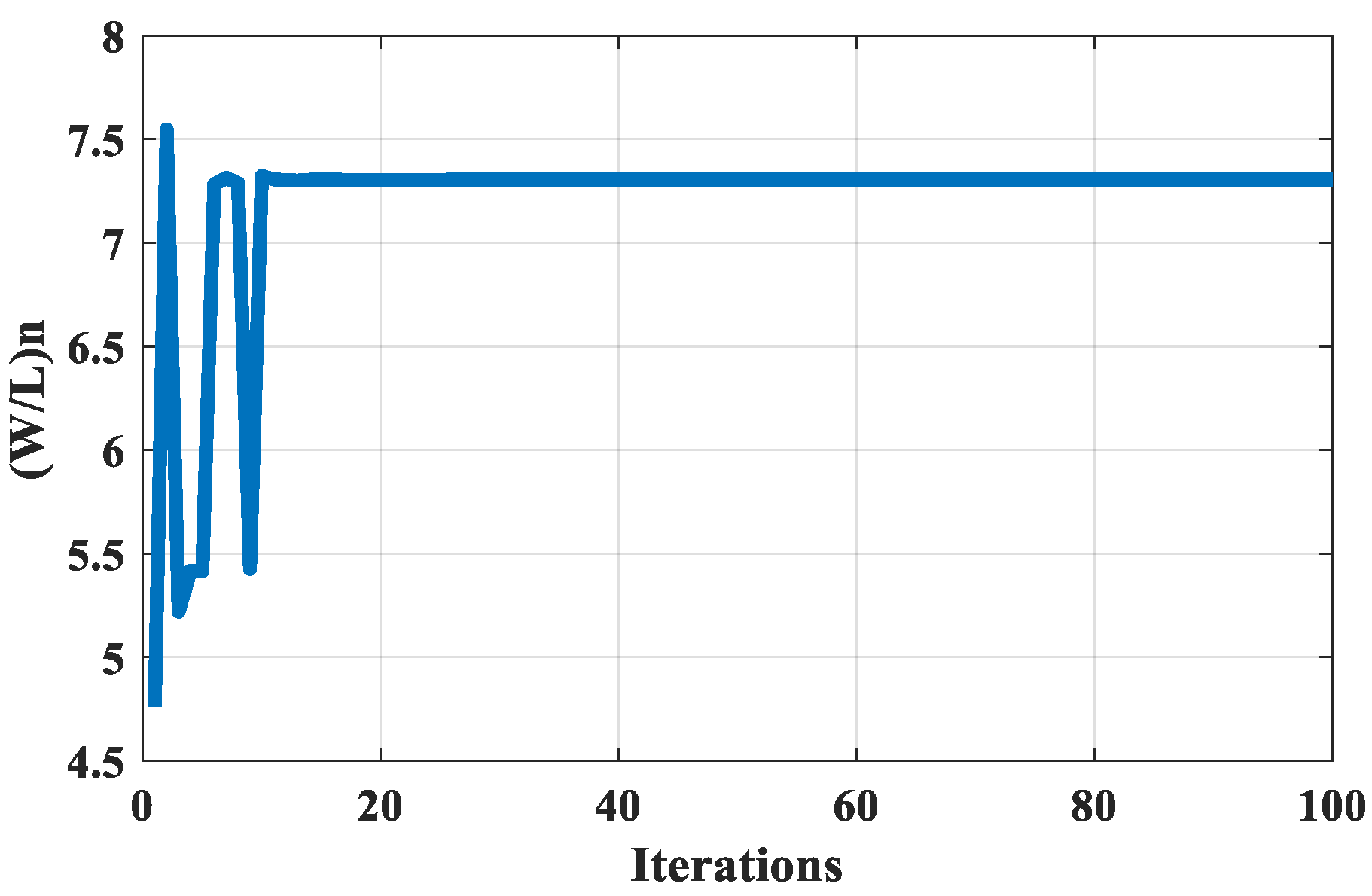

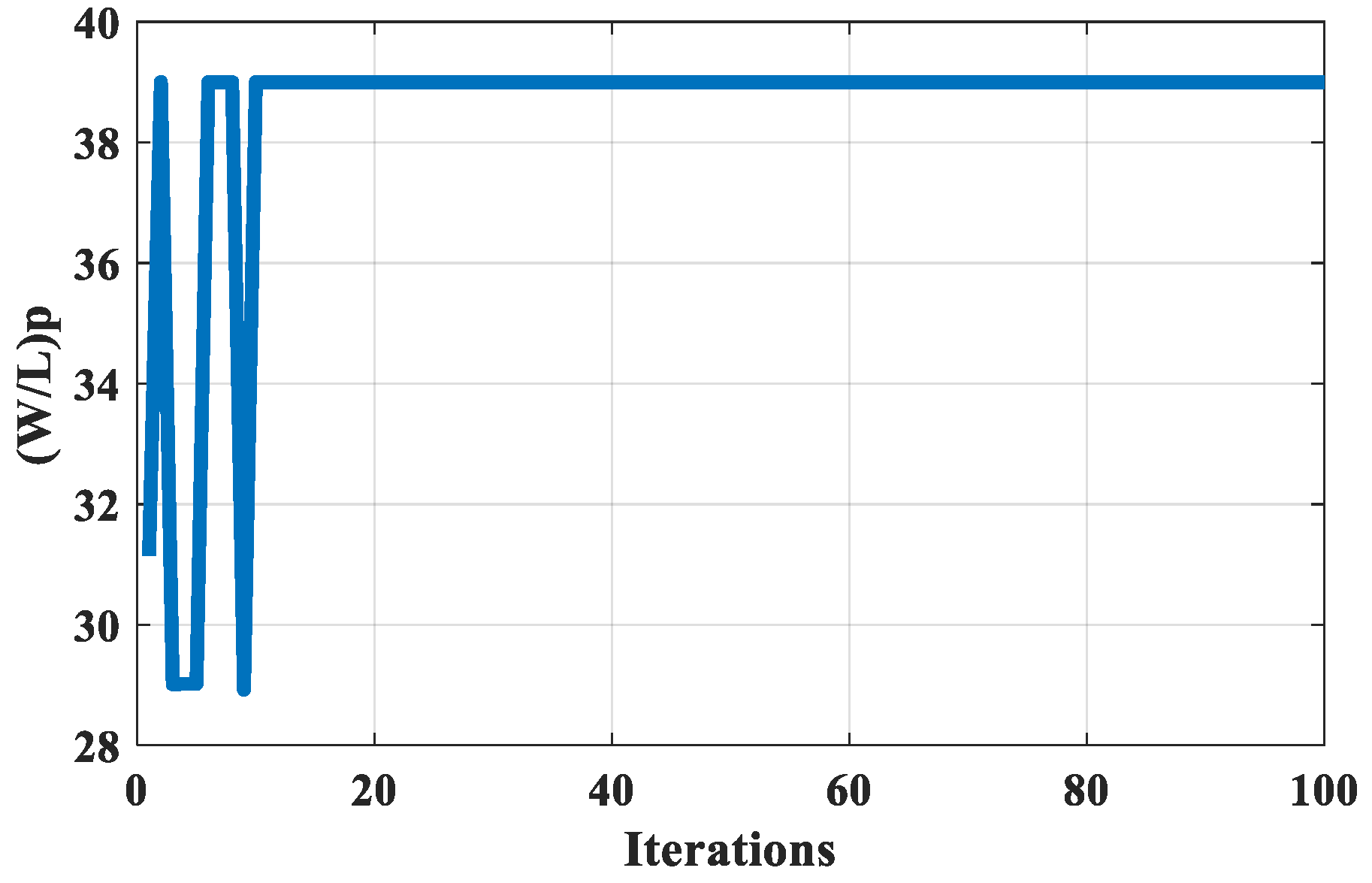

Figure 17,

Figure 18 and

Figure 19 show the convergence plots of the inverter design parameters: C

L, (W/L)

n and (W/L)

p for the same design set.

Figure 17 shows that the capacitance load optimum value for the eighth set is equal to 0.394871 pF. The aspect ratio for the NMOS transistor converges at a value of 7.30448 after 16 iterations as shown in

Figure 18. On the other hand,

Figure 19 shows that the optimum aspect ratio for the PMOS transistor is 39.

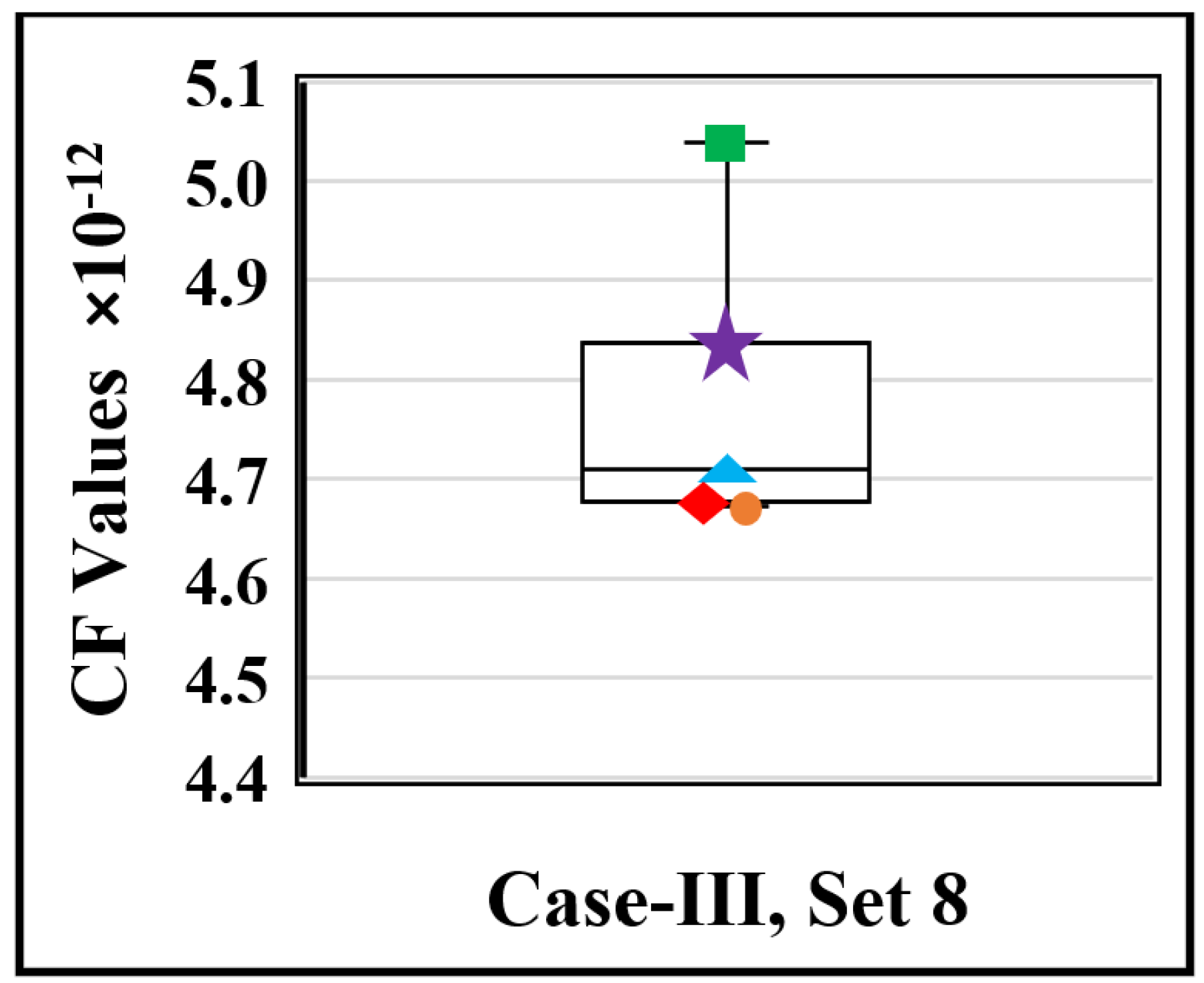

Figure 20 shows the box and whisker plot for the eighth design set of the MA. The green square represents the maximum value, the purple star represents upper whisker, the blue triangle represents median value, the red diamond represents the lower whisker, and the orange circle represents the minimum value.

The median value is found to be 4.71 × 10−12, the maximum value is 5.04 × 10−12, the minimum value is 4.67 × 10−12, the lower whisker is 4.67727 × 10−12, and the upper whisker is 4.81995 × 10−12.

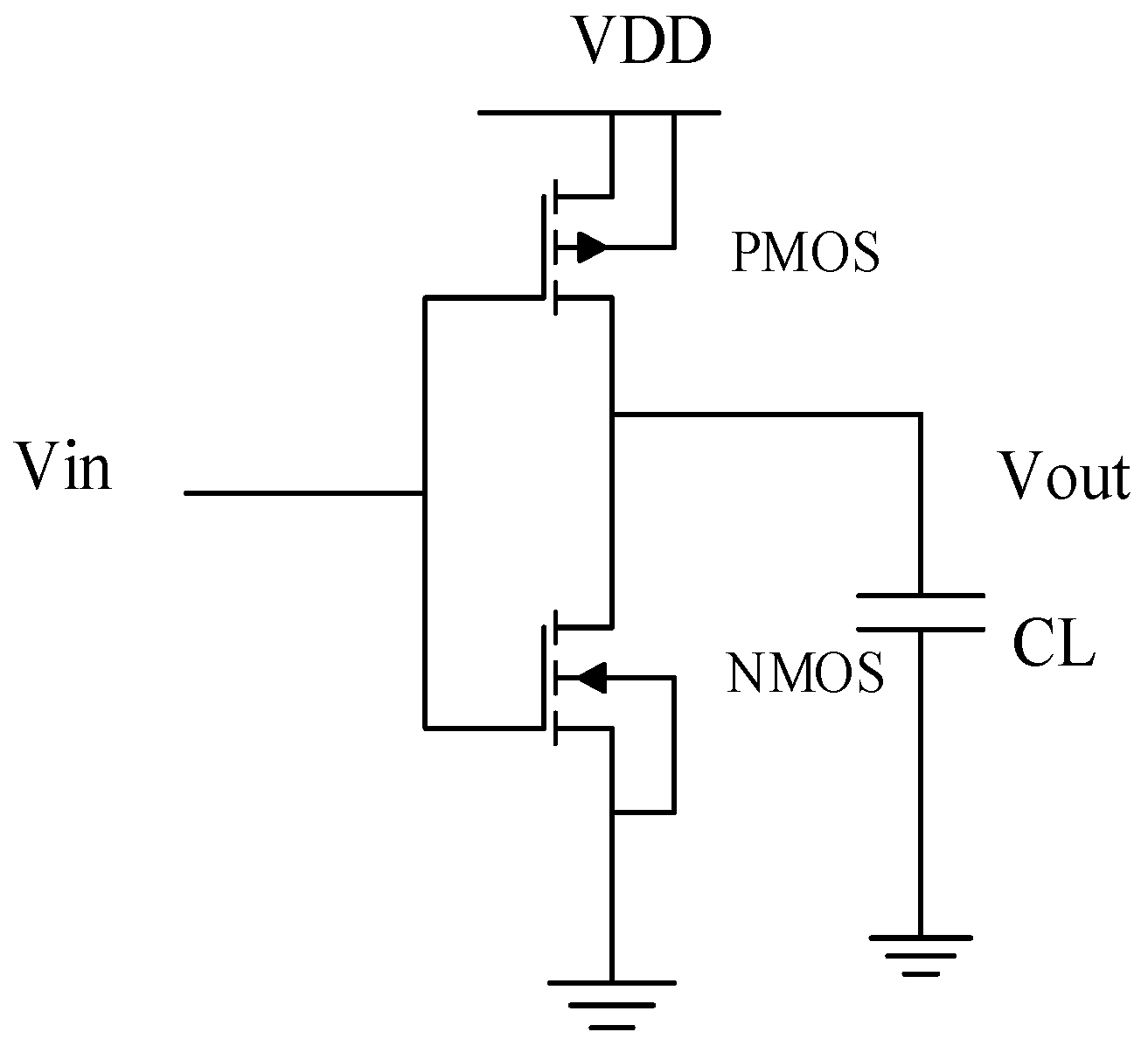

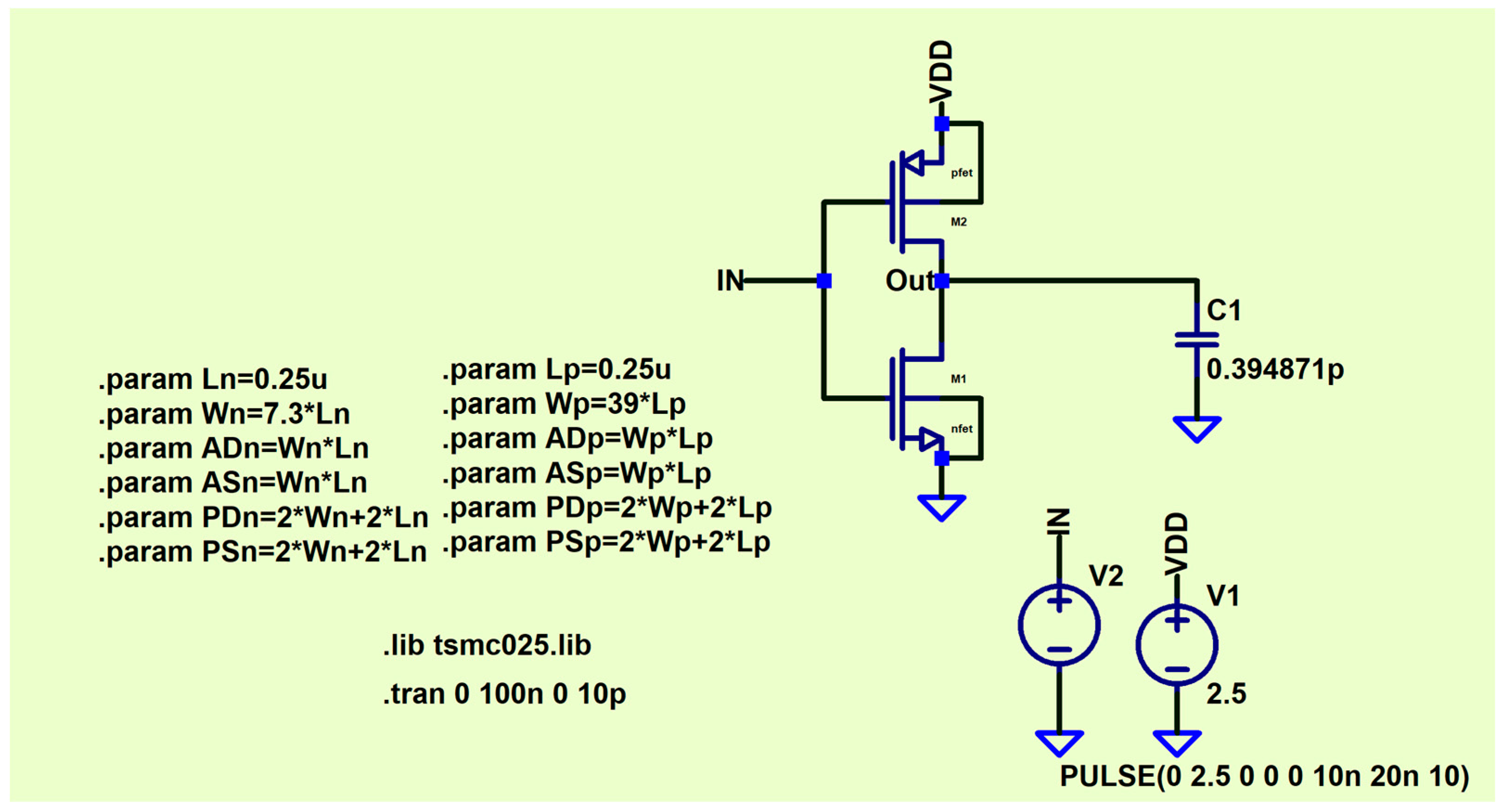

To verify the results obtained using MA optimization, the optimal values of the design parameters are used in the inverter Spice simulations. The simulated circuit is shown in

Figure 21.

Table 10 shows the simulation results for each design set in the three case studies. Spice simulation results show that the MA method is very accurate with small variations due to MOSFET junction capacitance.

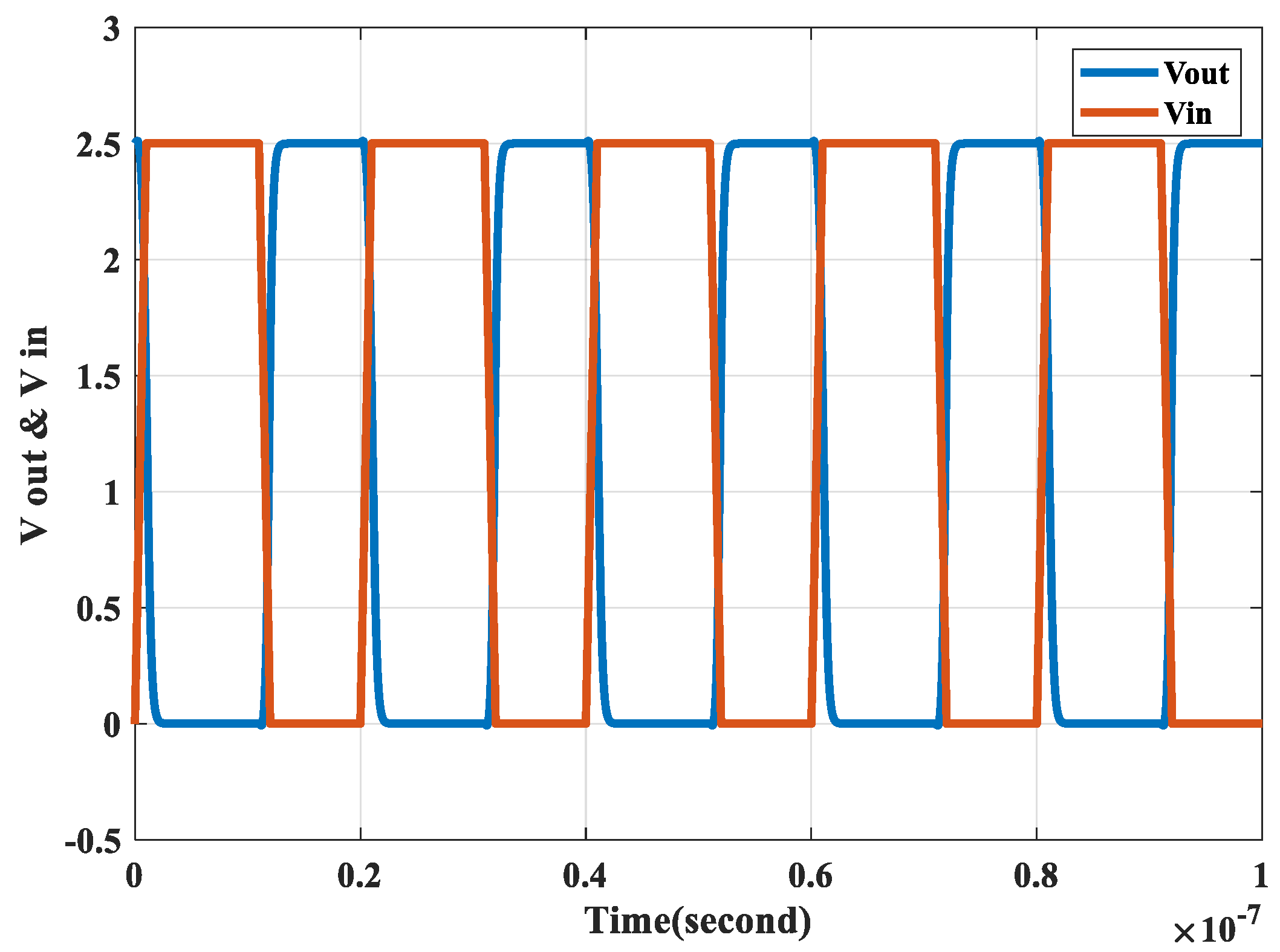

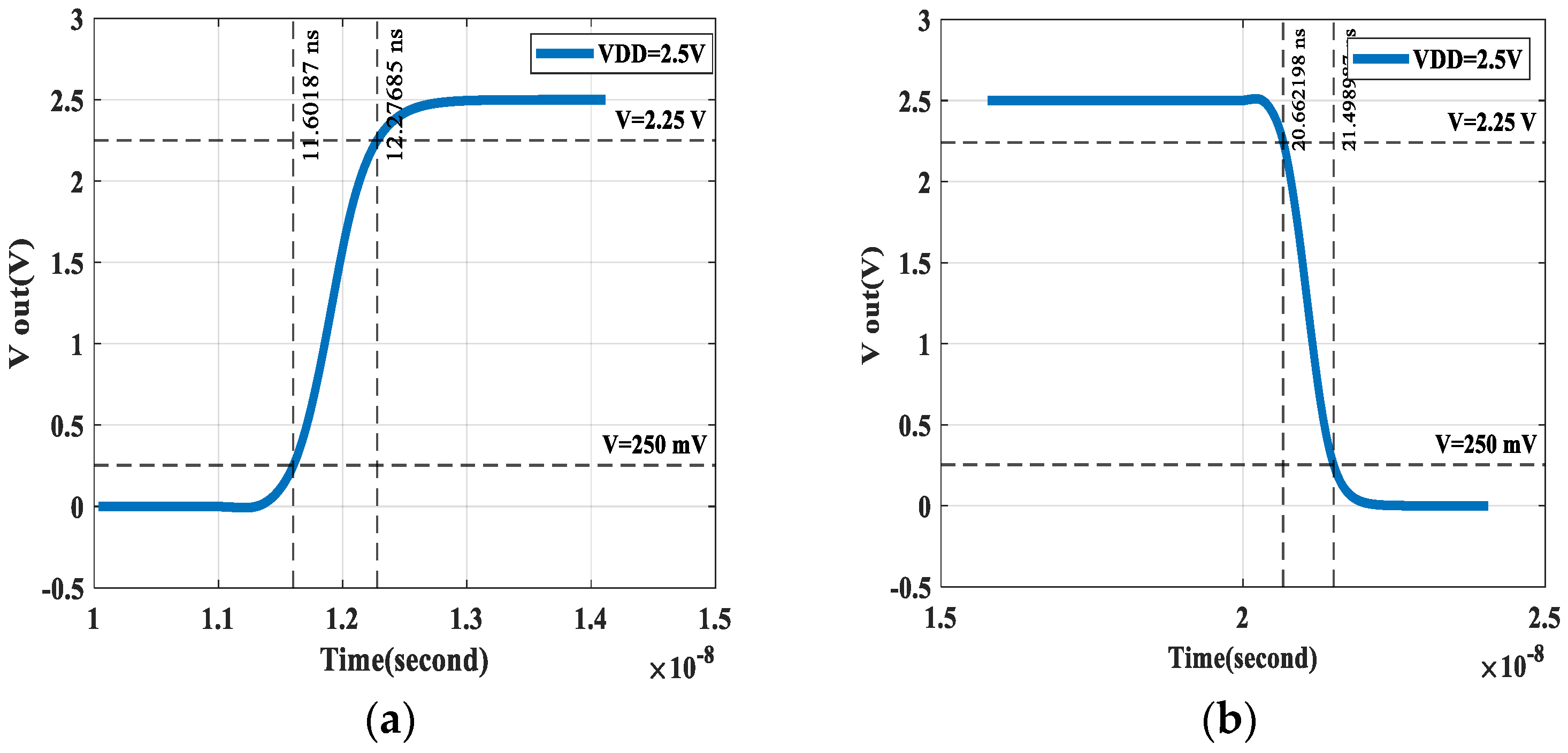

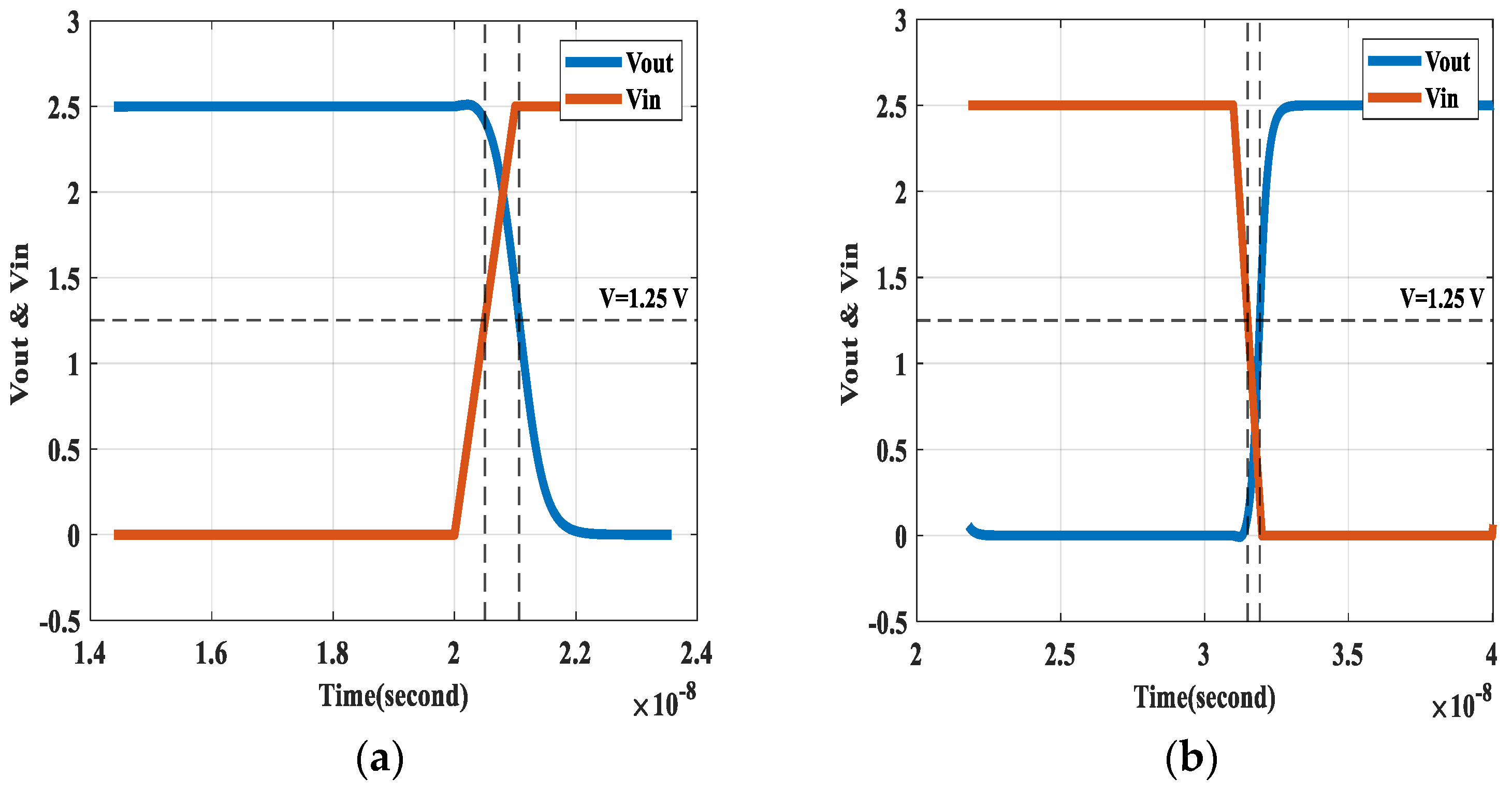

Spice simulations for the rise and fall times and the propagation delay times for the eighth design set of Case III are shown in

Figure 22 and

Figure 23, respectively. Rise time and fall time in

Figure 22 are 0.840474 ns and 0.6761915 ns with a difference less than 0.2 ns. propagation delay high to low and low to high for the eighth set are shown in

Figure 23 to be equal to 0.565393 ns and 0.416783 ns, respectively.