Carrier Trap Density Reduction at SiO2/4H-Silicon Carbide Interface with Annealing Processes in Phosphoryl Chloride and Nitride Oxide Atmospheres

Abstract

:1. Introduction

2. Experimental Data

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Nee, H.-P.; Kolar, J.; Friedrichs, P.; Rabkowski, J. Editorial: Special issue on wide bandgap power devices and their applications. IEEE Trans. Power Electron. 2014, 29, 2153–2154. [Google Scholar] [CrossRef]

- Gong, X.; Ferreira, J. Investigation of conducted EMI in SiC JFET inverters using separated heat sinks. IEEE Trans. Ind. Electron. 2014, 61, 115–125. [Google Scholar] [CrossRef]

- Alexandru, M.; Banu, V.; Jordà, X.; Montserrat, J.; Vellvehi, M.; Tournier, D.; Millán, J.; Godignon, P. SiC integrated circuit control electronics for high temperature operation. IEEE Trans. Ind. Electron. 2015, 62, 3182–3191. [Google Scholar] [CrossRef]

- Esteve, V.; Jordán, J.; Sanchis-Kilders, E.; Dede, E.J.; Maset, E.; Ejea, J.B.; Ferreres, A. Comparative study of a single inverter bridge for dual frequency induction heating using Si and SiC MOSFETs. IEEE Trans. Ind. Electron. 2015, 62, 1440–1450. [Google Scholar] [CrossRef]

- Chen, Z.; Yao, Y.; Boroyevich, D.; Ngo, K.; Mattavelli, P.; Rajashekara, K. A 1200 V, 60 A SiC MOSFET multichip phase-leg module for high-temperature, high-frequency applications. IEEE Trans. Power Electron. 2014, 29, 2307–2320. [Google Scholar] [CrossRef]

- Ning, P.; Zhang, D.; Lai, R.; Jiang, D.; Wang, F.; Boroyevich, D.; Burgos, R.; Karimi, K.; Immanuel, V.D. High-temperature hardware: Development of a 10-kW high-temperature, high-power-density three-phase AC-DC-AC SiC converter. IEEE Ind. Electron. Mag. 2013, 7, 6–17. [Google Scholar] [CrossRef]

- Zhao, B.; Song, Q.; Liu, W. Experimental comparison of isolated bidirectional DC/DC converters based on All-Si and All-SiC power devices for next-generation power conversion application. IEEE Trans. Ind. Electron. 2014, 61, 1389–1393. [Google Scholar] [CrossRef]

- Zhang, H.; Tolbert, L.M. Efficiency impact of silicon carbide power electronics for modern wind turbine full scale frequency converter. IEEE Trans. Ind. Electron. 2011, 58, 21–28. [Google Scholar] [CrossRef]

- Cabello, M.; Soler, V.; Gemma, R.; Montserrat, J.; Rebollo, J.; Godignon, P. Advanced processing for mobility improvement in 4H-SiC MOSFETs: A review. Mater. Sci. Semicond. Process. 2018, 78, 22–31. [Google Scholar] [CrossRef]

- Li, X.; Ermakov, A.; Amarasinghe, V.; Garfunkel, E.; Gustafsson, T.; Feldman, L.C. Oxidation induced stress in SiO2/SiC structures. Appl. Phys. Lett. 2017, 110, 141604. [Google Scholar] [CrossRef]

- Pérez-Tomás, A.; Godignon, P.; Mestres, N.; Millán, J. A field-effect electron mobility model for SiC MOSFETs including high density of traps at the interface. J. Microelectron. Eng. 2006, 83, 440–445. [Google Scholar] [CrossRef]

- Palmieri, R.; Radtke, C.; Silva, M.R., Jr. Trapping of majority carriers in SiO2/4H-SiC structures. J. Phys. D Appl. Phys. 2009, 42, 125301. [Google Scholar] [CrossRef]

- Pascu, R.; Romanitan, C.; Varesteanu, P.; Kusko, M. A Reliable Technology for Advanced SiC-MOS Devices Based on Fabrication of High Quality Silicon Oxide Layers by Converting a-Si. J. Electron. Devices Soc. 2019, 7, 158–167. [Google Scholar] [CrossRef]

- Kaminski, P.; Budzioch, R.; Gaca, J.; Michałowski, P.P.; Kozłowski, R.; Harmasz, A.; Ciuk, T.; Płocharski, J. Effect of oxidation temperature on the heterogeneity of chemical composition and density in SiO2 film grown on 4H-SiC. J. Mater. Chem. C 2021, 9, 4393. [Google Scholar] [CrossRef]

- Saito, M.; Li, H.; Inoue, K.; Matsuhata, H.; Ikuharaet, Y. Oxygen atom ordering on SiO2/4H-SiC(0001) polar interfaces formed by wet oxidation. Acta Mater. 2021, 221, 117360. [Google Scholar] [CrossRef]

- Kobayashi, T.; Matsushita, Y. Structure and energetics of carbon defects in SiC (0001)/SiO2 systems at realistic temperatures: Defects in SiC, SiO2, and at their interface. J. Appl. Phys. 2019, 126, 145302. [Google Scholar] [CrossRef] [Green Version]

- Matsushita, Y.; Oshiyama, A. Structural stability and energy levels of carbon-related defects in amorphous SiO2 and its interface with SiC. Jpn. J. Appl. Phys. 2018, 57, 125701. [Google Scholar] [CrossRef] [Green Version]

- Ólafsson, H.Ö.; Allerstam, F.; Sveinbjörnsson, E.Ö. On Shallow Interface States in n-Type 4H-SiC Metal-Oxide-Semiconductor Structures. Mater. Sci. Forum 2001, 389–393, 1005–1008. [Google Scholar] [CrossRef]

- Chanthaphan, A.; Hosoi, T.; Shimura, T.; Watanabe, H. Study of SiO2/4H-SiC interface nitridation by post-oxidation annealing in pure nitrogen gas. AIP Adv. 2015, 5, 097134. [Google Scholar] [CrossRef]

- Peng, Z.; Wang, Y.; Shen, H.; Li, C.; Wu, J.; Bai, Y.; Liu, K.; Liu, X. Effects of combined NO and forming gas annealing on interfacial properties and oxide reliability of 4H-SiC MOS structures. Microelectron. Reliab. 2016, 58, 192–196. [Google Scholar] [CrossRef]

- Krol, K.; Kalisz, M.; Sochacki, M.; Szmidt, J. The influence of post-oxidation annealing process in O2 and N2O on the quality of Al/SiO2/n-type 4H-SiC MOS interface. Mater. Sci. Forum 2013, 740–742, 753–756. [Google Scholar] [CrossRef]

- Fujihira, K.; Tarui, Y.; Imaizumi, M.; Ohtsuka, K.; Takami, T.; Shiramizu, T.; Kawase, K.; Tanimura, J.; Ozeki, T. Characteristics of 4H–SiC MOS interface annealed in N2O. Solid-State Electron. 2005, 49, 896–901. [Google Scholar] [CrossRef]

- Chowdhury, S.; Yamamoto, K.; Hitchcock, C.W.; Chow, T.P. Characteristics of MOS capacitors with NO and POCl3 annealed gate oxides on (0001), (11-20) and (000-1) 4H-SiC. Mater. Sci. Forum 2015, 821–823, 500–503. [Google Scholar] [CrossRef]

- Tsui, B.-Y.; Huang, Y.-T.; Wu, T.-L.; Chien, C.-H. Time-dependent dielectric breakdown of gate oxide on 4H-SiC with different oxidation processes. Microelectron. Reliab. 2021, 123, 114186. [Google Scholar] [CrossRef]

- Fiorenza, P.; Giannazzo, F.; Vivona, M.; La Magna, A.; Roccaforte, F. SiO2/4H-SiC interface doping during post-deposition-annealing of the oxide in N2O or POCl3. Appl. Phys. Lett. 2013, 103, 153508. [Google Scholar] [CrossRef]

- Okamoto, D.; Yano, H.; Hatayama, T.; Fuyuki, T. Development of 4H-SiC MOSFETs with Phosphorus-Doped Gate Oxide. Mater. Sci. Forum 2012, 717–720, 733–738. [Google Scholar] [CrossRef]

- Krol, K.B.; Sochacki, M.; Strupiński, W.; Racka, K.; Guziewicz, M.; Konarski, P.; Miśnik, M.; Szmidt, J. Chlorine-enhanced thermal oxides growth and significant trap density reduction at SiO2/SiC interface by incorporation of phosphorus. Thin Solid Films 2015, 591, 86–89. [Google Scholar] [CrossRef]

- Fiorenza, P.; Swanson, L.K.; Vivona, M.; Giannazzo, F.; Bongiorno, C.; Frazzetto, A.; Roccaforte, F. Comparative study of gate oxide in 4H-SiC lateral MOSFETs subjected to post-deposition-annealing in N2O and POCl3. Appl. Phys. A 2014, 115, 333–339. [Google Scholar] [CrossRef]

- Yano, H.; Araoka, T.; Hatayama, T.; Fuyuki, T. Improved stability of 4H-SiC MOS device properties by combination of NO and POCl3 annealing. Mater. Sci. Forum 2013, 740–742, 727–732. [Google Scholar] [CrossRef]

- Yano, H.; Kanafuji, N.; Osawa, A.; Hatayama, T.; Fuyuki, T. Threshold Voltage Instability in 4H-SiC MOSFETs with Phosphorus-Doped and Nitrided Gate Oxides. IEEE Trans. Electron. Devices 2015, 62, 324–332. [Google Scholar] [CrossRef]

- Fiorenza, P.; Giannazzo, F.; Roccaforte, F. Characterization of SiO2/4H-SiC Interfaces in 4H-SiC MOSFETs: A Review. Energies 2019, 12, 2310. [Google Scholar] [CrossRef] [Green Version]

- Tachiki, K.; Kaneko, M.; Kobayashi, T.; Kimoto, T. Formation of high-quality SiC(0001)/SiO2 structures by excluding oxidation process with H2 etching before SiO2 deposition and high temperature N2 annealing. Appl. Phys. Express 2020, 13, 121002. [Google Scholar] [CrossRef]

- Taube, A.; Guziewicz, M.; Kosiel, K.; Gołaszewska-Malec, K.; Król, K.; Kruszka, R.; Kaminska, E.; Piotrowska, A. Characterization of Al2O3/4H-SiC and Al2O3/SiO2/4H-SiC MOS structures. Bull. Pol. Acad. Sci. Tech. Sci. 2016, 64, 447–451. [Google Scholar] [CrossRef] [Green Version]

- Kim, Y.-J.; Baek, R.-H.; Chang, S.K.; Choi, K.K. Effect of hydrogen plasma treatment on the electrical properties for SiC-based power MOSFETs. Microelectron. Eng. 2022, 258, 111769. [Google Scholar] [CrossRef]

- Kobayashi, T.; Suda, J.; Kimoto, T. Reduction of interface state density in SiC (0001) MOS structures by post-oxidation Ar annealing at high temperature. AIP Adv. 2017, 7, 045008. [Google Scholar] [CrossRef] [Green Version]

- Yano, H.; Katafuchi, F.; Kimoto, T.; Matsunam, H. Effects of wet oxidation/anneal on interface properties of thermally oxidized SiO2/SiC MOS system and MOSFET’s. IEEE Trans. Electron. Devices 1999, 46, 504–510. [Google Scholar] [CrossRef]

- Godignon, P.; Montserrat, J.; Rebollo, J.; Planson, D. Edge Terminations for 4H-SiC Power Devices: A Critical Issue. Mater. Sci. Forum 2022, 1062, 570–575. [Google Scholar] [CrossRef]

- Nicollian, E.H.; Brews, J.R. MOS (Metal Oxide Semiconductor) Physics and Technology; John Willey and Sons: New York, NY, USA, 1982. [Google Scholar]

- Afanas’ev, V.V.; Stesmans, A.; Bassler, M.; Pensl, G.; Schulz, M.J. Shallow electron traps at the 4H-SiC/SiO2 interface. Appl. Phys. Lett. 2000, 76, 336–338. [Google Scholar] [CrossRef]

- Shroder, D. Oxide and interface trapped charges, oxide thickness. In Semiconductor Material and Device Characterization; John Wiley & Sons, Inc.: New York, NY, USA, 2006; pp. 319–387. [Google Scholar]

- Sze, S.M.; Kwok, K.N. Physics of Semiconductor Devices; Wiley Interscience, John Wiley & Sons: New York, NY, USA, 2006. [Google Scholar]

- Afanas’ev, V.V.; Bassler, M.; Pensl, G.; Schulz, M.J. Intrinsic SiC/SiO2 Interface States. Phys. Status Solidi A 1997, 162, 321–337. [Google Scholar] [CrossRef]

- Okamoto, M.; Tanaka, M.; Yatsuo, T.; Fukuda, K. Effect of the oxidation process on the electrical characteristics of 4H-SiC p-channel metal-oxide-semiconductor field-effect transistors. Appl. Phys. Lett. 2006, 89, 023502. [Google Scholar] [CrossRef]

- Hosoi, T.; Nagai, D.; Shimura, T.; Watanabe, H. Exact evaluation of interface reaction-limited growth in dry and wet thermal oxidation of 4HSiC (0001) Si-face surfaces. Jpn. J. Appl. Phys. 2015, 54, 098002. [Google Scholar] [CrossRef]

- Indari, E.D.; Yamashita, Y.; Hasunuma, R.; Oji, H.; Yamabe, K. Relationship between electrical properties and interface structures of SiO2/4H-SiC prepared by dry and wet oxidation. AIP Adv. 2019, 9, 105018. [Google Scholar] [CrossRef] [Green Version]

- Fukuda, K.; Kato, M.; Kojima, K.; Senzaki, J. Effect of gate oxidation method on electrical properties of metal-oxide-semiconductor field-effect transistors fabricated on 4H-SiC C(000-1) face. Appl. Phys. Lett. 2004, 84, 2088–2090. [Google Scholar] [CrossRef]

- Li, X.; Lee, S.S.; Li, M.; Ermakov, A.; Medina-Ramos, J.; Fister, T.T.; Amarasinghe, V.; Gustafsson, T.; Garfunkel, E.; Fenter, P.; et al. Effect of nitrogen passivation on interface composition and physical stress in SiO2/SiC(4H) structures. Appl. Phys. Lett. 2018, 113, 131601. [Google Scholar] [CrossRef]

- Wang, T.; Liu, G.; Li, Y.; Hou, H.; Xu, Z.; Wang, M.; Qiao, G. Native point defects on hydrogen-passivated 4H–SiC(0001) surface and the effects on metal adsorptions. J. Chem. Phys. 2017, 147, 024707. [Google Scholar] [CrossRef]

- Kil, T.-H.; Kita, K. Anomalous band alignment change of SiO2/4H–SiC (0001) and (000-1) MOS capacitors induced by NO-POA and its possible origin. Appl. Phys. Lett. 2020, 116, 122103. [Google Scholar] [CrossRef]

- Okamoto, D.; Yano, H.; Hirata, K.; Hatayama, T.; Fuyuki, T. Improved Inversion Channel Mobility in 4H-SiC MOSFETs on Si Face Utilizing Phosphorus-Doped Gate Oxide. IEEE Electron. Device Lett. 2010, 31, 710–712. [Google Scholar] [CrossRef]

- Pascu, R.; Craciunoiu, F.; Kusko, M.; Mihaila, M.; Pristavu, G.; Badila, M.; Brezeanu, G. SiO2/4H-SiC interface states reduction by POCl3 post-oxidation annealing. In Proceedings of the 2015 International Semiconductor Conference (CAS), Sinaia, Romania, 12–14 October 2015; pp. 255–258. [Google Scholar] [CrossRef]

- Yano, H.; Hatayama, T.; Fuyuki, T. POCl3 Annealing as a New Method for Improving 4H-SiC MOS Device Performance. ECS Trans. 2013, 50, 257. [Google Scholar] [CrossRef]

- Sharma, Y.K.; Ahyi, A.C.; Isaacs-Smith, T.; Modic, A.; Park, M.; Xu, Y.; Garfunkel, E.L.; Dhar, S.; Feldman, L.C.; Williams, J.R. High-mobility stable 4H-SiC MOSFETs using a thin PSG interfacial passivation layer. IEEE Electron. Device Lett. 2013, 34, 175–177. [Google Scholar] [CrossRef]

- Jayawardena, A.; Shen, X.; Mooney, P.M.; Dhar, S. Mechanism of phosphorus passivation of near-interface oxide traps in 4H–SiC MOS devices investigated by CCDLTS and DFT calculation. Semicond. Sci. Technol. 2018, 33, 065005. [Google Scholar] [CrossRef]

- Jiao, C.; Ahyi, A.C.; Xu, C.; Morisette, D.; Feldman, L.C.; Dhar, S. Phospho-silicate glass gated 4H-SiC metal-oxide-semiconductor devices: Phosphorus concentration dependence. J. Appl. Phys. 2016, 119, 155705. [Google Scholar] [CrossRef]

- Ju, Y.; Bouvet, D.; Stark, R.; Woerle, J.; Grossner, U. 4H-SiC Power VDMOSFET Manufacturing Utilizing POCl3 Post Oxidation Annealing. Mater. Sci. Forum 2020, 1004, 559–564. [Google Scholar] [CrossRef]

- Xu, Y.; Xu, C.; Liu, G.; Lee, H.D.; Shubeita, S.M.; Jiao, C.; Modic, A.; Ahyi, A.C.; Sharma, Y.; Wan, A.; et al. Concentration, chemical bonding, and etching behavior of P and N at the SiO2/SiC(0001) interface. J. Appl. Phys. 2018, 118, 235303. [Google Scholar] [CrossRef] [Green Version]

- Kobayashi, T.; Matsushita, Y.; Okuda, T.; Oshiyama, A. Microscopic mechanism of carbon annihilation upon SiC oxidation due to phosphorus treatment: Density functional calculations combined with ion mass spectrometry. Appl. Phys. Express 2018, 11, 121301. [Google Scholar] [CrossRef]

- Kimoto, T.; Watanabe, H. Defect engineering in SiC technology for high-voltage power devices. Appl. Phys. Express 2018, 13, 120101. [Google Scholar] [CrossRef]

- Devynck, F.; Alkauskas, A.; Broqvist, P.; Pasquarello, A. Defect levels of carbon-related defects at the SiC/SiO2 interface from hybrid functionals. Phys. Rev. B 2011, 83, 195319. [Google Scholar] [CrossRef] [Green Version]

- Kaneko, T.; Tajima, N.; Yamasaki, T.; Nara, J.; Schimizu, T.; Kato, K.; Ohno, T. Hybrid density functional analysis of distribution of carbon-related defect levels at 4H-SiC(0001)/SiO2 interface. Appl. Phys. Express 2018, 11, 011302. [Google Scholar] [CrossRef]

- Gavrikov, A.; Knizhnik, A.; Safonov, A.; Schebinin, A.; Bagatu’yants, A.; Potapkin, B.; Chatterjee, A.; Matocha, K. First-principles-based investigation of kinetic mechanism of SiC(0001) dry oxidation including defect generation and passivation. J. Appl. Phys. 2008, 104, 093508. [Google Scholar] [CrossRef]

- Deak, P.; Knaup, J.M.; Hornos, T.; Thill, C.; Gali, A.; Frauenheim, T. The mechanism of defect creation and passivation at the SiC/SiO2 interface. J. Phys. D Appl. Phys. 2007, 40, 6242–6253. [Google Scholar] [CrossRef]

- Salemi, S.; Goldsman, N.; Akturk, A.; Lelis, A. Density Functional Theory Based Investigation of Defects and Passivation of 4H-Silicon Carbide/SiO2 Interface. In Proceedings of the International Conference on Simulation of Semiconductor Process and Devices, SISPAD 2012, Denver, CO, US, 5–7 September 2012. [Google Scholar]

- Pennington, G.; Ashman, C. Nitrogen Passivation of (0001) 4H-SiC Dangling Bonds. Mater. Sci. Forum 2009, 600–603, 469–472. [Google Scholar] [CrossRef]

- Salemi, S.; Goldsman, N.; Ettisserry, D.P.; Akturk, A.; Lelis, A. The effect of defects and their passivation on the density of states of the 4H-silicon-carbide/silicon-dioxide interface. J. Appl. Phys. 2013, 113, 053703. [Google Scholar] [CrossRef]

- Wang, Z.; Zhang, Z.; Shao, C.; Robertson, J.; Liu, S.; Guo, Y. Defects and Passivation Mechanism of the Suboxide Layers at SiO₂/4H-SiC (0001) Interface: A First-Principles Calculation. IEEE Trans. Electron. Devices 2020, 68, 288–293. [Google Scholar] [CrossRef]

- Nakanuma, T.; Iwakata, Y.; Watanabe, A.; Hosoi, T.; Kobayashi, T.; Sometani, M.; Okamoto, M.; Yoshigoe, A.; Shimura, T.; Watanabe, H. Comprehensive physical and electrical characterizations of NO nitrided SiO2/4H-SiC(110) interfaces. Jpn. J. Appl. Phys. 2022, 61, SC1065. [Google Scholar] [CrossRef]

- Zheng, Z.; Tressler, R.E.; Spear, K.E. The effects of Cl2 on the oxidation of single crystal silicon carbide. Corros. Sci. 1992, 33, 557–567. [Google Scholar] [CrossRef]

- Pascu, R.; Craciunoiu, F.; Pristavu, G.; Brezeanu, G.; Kusko, M. Oxide trap states versus gas sensing in SiC-MOS capacitors—The effect of N- and P- based post oxidation processes. Sens. Actuators B 2017, 245, 911–922. [Google Scholar] [CrossRef]

- Zhang, Z.; Guo, Y.; Robertson, J. Mobility degradation in 4H-SiC MOSFETs and interfacial formation of carbon clusters. Solid-State Electron. 2021, 183, 108051. [Google Scholar] [CrossRef]

| Process Type, Parameter | Values | ||||||

|---|---|---|---|---|---|---|---|

| Oxidation, Time t (min) | Dry | Dry | Dry | Wet | Wet | Wet | Wet |

| 360 | 180 | 360 | 80 | 80 | 80 | 80 | |

| POCl3 T (°C) | - | - | 1000 | - | 1000 | 1000 | 1000 |

| N2 T (°C) | 1000 | - | 1000 | - | 1000 | 1000 | 1000 |

| NO T (°C) | - | 1000 | - | 1000 | 1000 | 1100 | 1175 |

| sample identification, ID | d-N2 | d-NO | d-POC | w-NO | w-POC-NO-1 | w-POC-NO-2 | w-POC-NO-3 |

| Parameter | Sample Identification, ID | ||||||

|---|---|---|---|---|---|---|---|

| d-N2 | d-NO | d-POC | w-NO | w-POC-NO-1 | w-POC-NO-2 | w-POC-NO-3 | |

| tox (nm) | 80 | 50 | 78 | 53 | 58 | 73 | 73 |

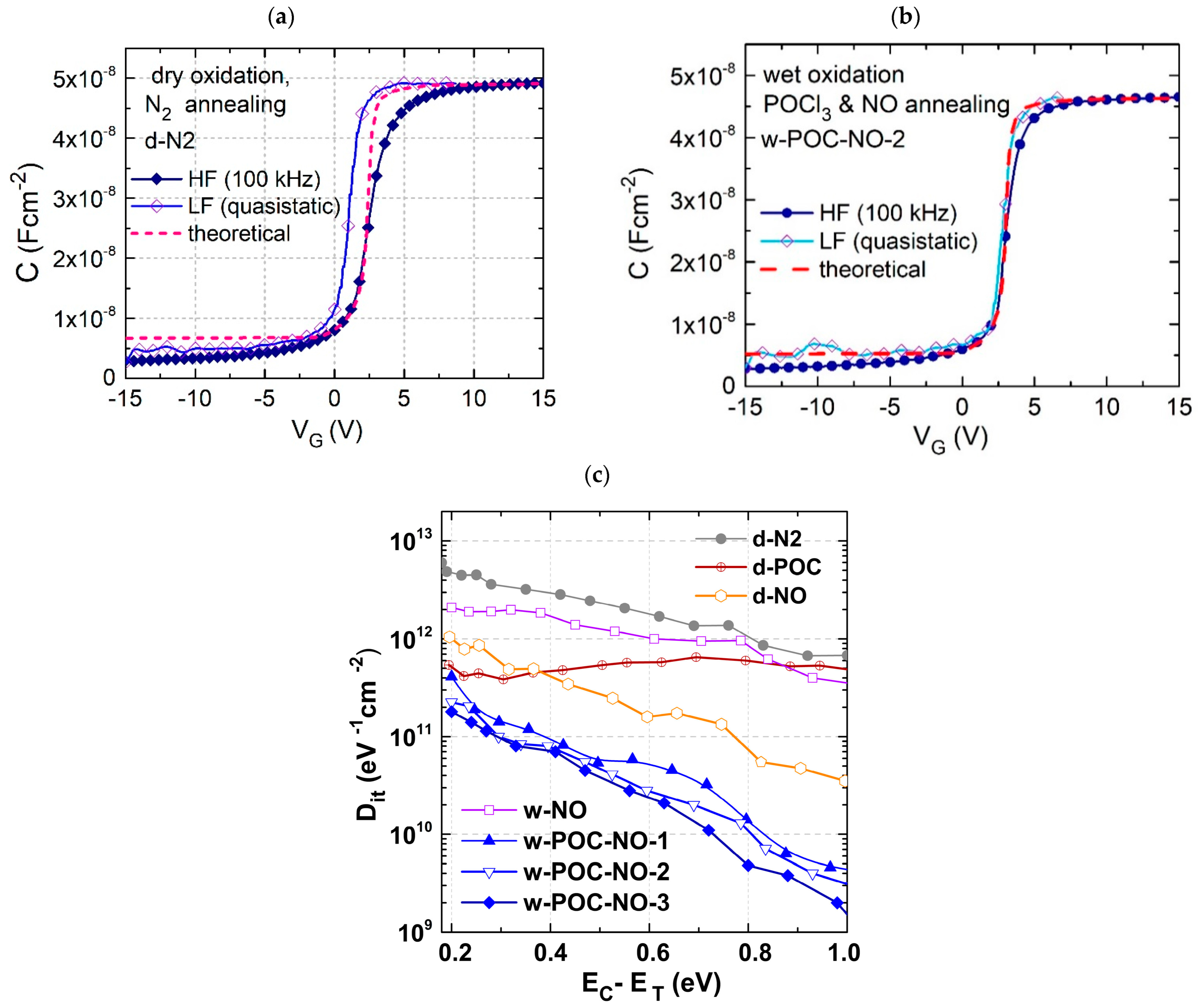

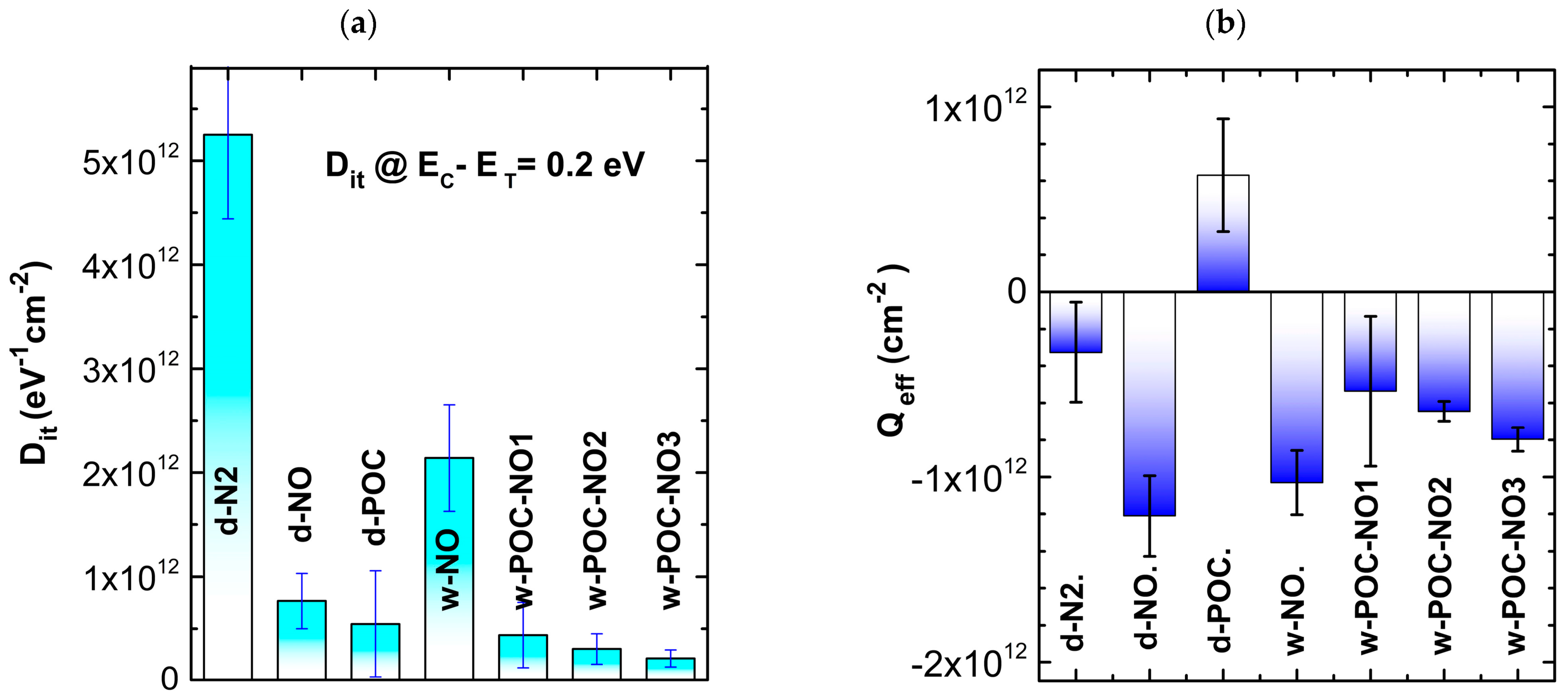

| Dit × 1011 (eV−1cm−2) (EC − ET = 0.2 eV) | 48 | 7.6 | 5.4 | 22 | 4.5 | 3.1 | 2.0 |

| VFB (V) | 2.37 | 3.97 | −1.15 | 3.52 | 2.47 | 3.32 | 3.82 |

| Qeff × 1011 (cm−2) | −3.2 | −12 | 6.3 | −10 | −5.4 | −6.5 | −7.9 |

| Before NO | Temperature | After NO | ||

|---|---|---|---|---|

| tox (nm) | TNO (°C) | tox (nm) | η (λ = 650 nm) | Δtox (nm) |

| 75 | 1000 | 66.4 | 1.472 | −8.6 |

| 75 | 1100 | 62.1 | 1.487 | −12.7 |

| 86 | 1175 | 72.6 | 1.488 | −13.4 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Brzozowski, E.; Kaminski, M.; Taube, A.; Sadowski, O.; Krol, K.; Guziewicz, M. Carrier Trap Density Reduction at SiO2/4H-Silicon Carbide Interface with Annealing Processes in Phosphoryl Chloride and Nitride Oxide Atmospheres. Materials 2023, 16, 4381. https://doi.org/10.3390/ma16124381

Brzozowski E, Kaminski M, Taube A, Sadowski O, Krol K, Guziewicz M. Carrier Trap Density Reduction at SiO2/4H-Silicon Carbide Interface with Annealing Processes in Phosphoryl Chloride and Nitride Oxide Atmospheres. Materials. 2023; 16(12):4381. https://doi.org/10.3390/ma16124381

Chicago/Turabian StyleBrzozowski, Ernest, Maciej Kaminski, Andrzej Taube, Oskar Sadowski, Krystian Krol, and Marek Guziewicz. 2023. "Carrier Trap Density Reduction at SiO2/4H-Silicon Carbide Interface with Annealing Processes in Phosphoryl Chloride and Nitride Oxide Atmospheres" Materials 16, no. 12: 4381. https://doi.org/10.3390/ma16124381

APA StyleBrzozowski, E., Kaminski, M., Taube, A., Sadowski, O., Krol, K., & Guziewicz, M. (2023). Carrier Trap Density Reduction at SiO2/4H-Silicon Carbide Interface with Annealing Processes in Phosphoryl Chloride and Nitride Oxide Atmospheres. Materials, 16(12), 4381. https://doi.org/10.3390/ma16124381