Investigation of Electrical Properties of the Al/SiO2/n++-Si Resistive Switching Structures by Means of Static, Admittance, and Impedance Spectroscopy Measurements

Abstract

:1. Introduction

2. Materials and Methods

3. Results and Discussion

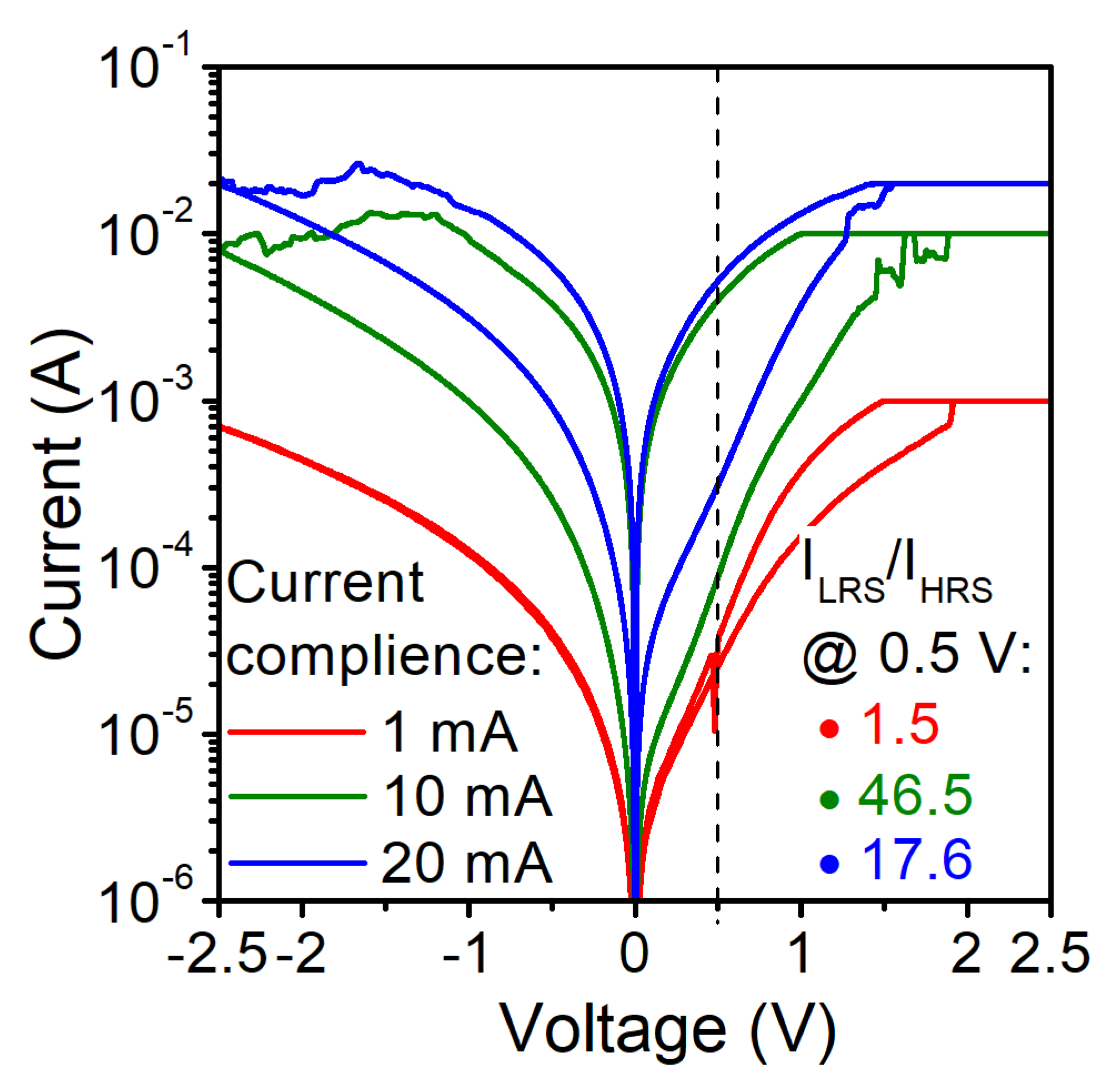

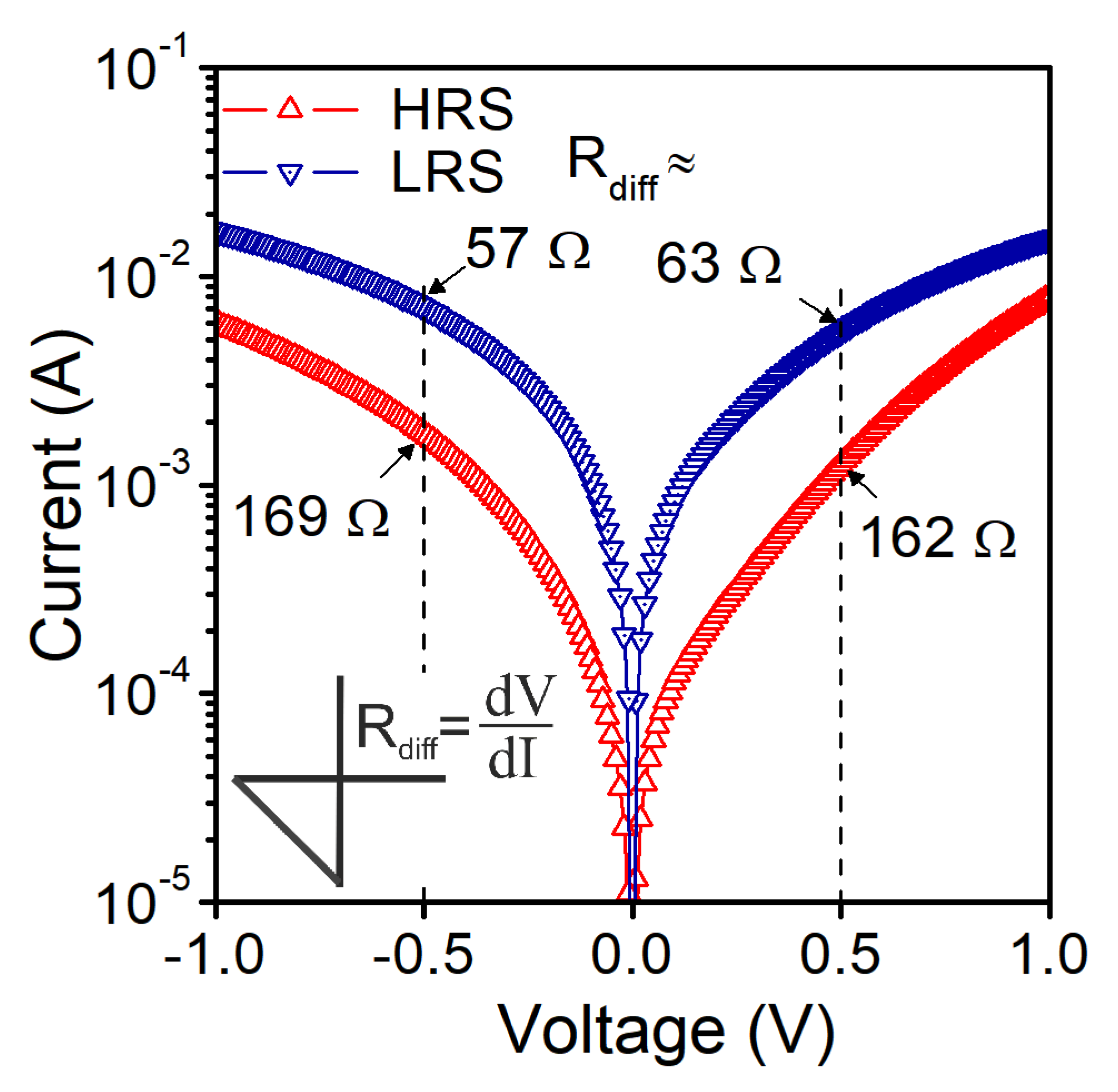

3.1. DC Measurements

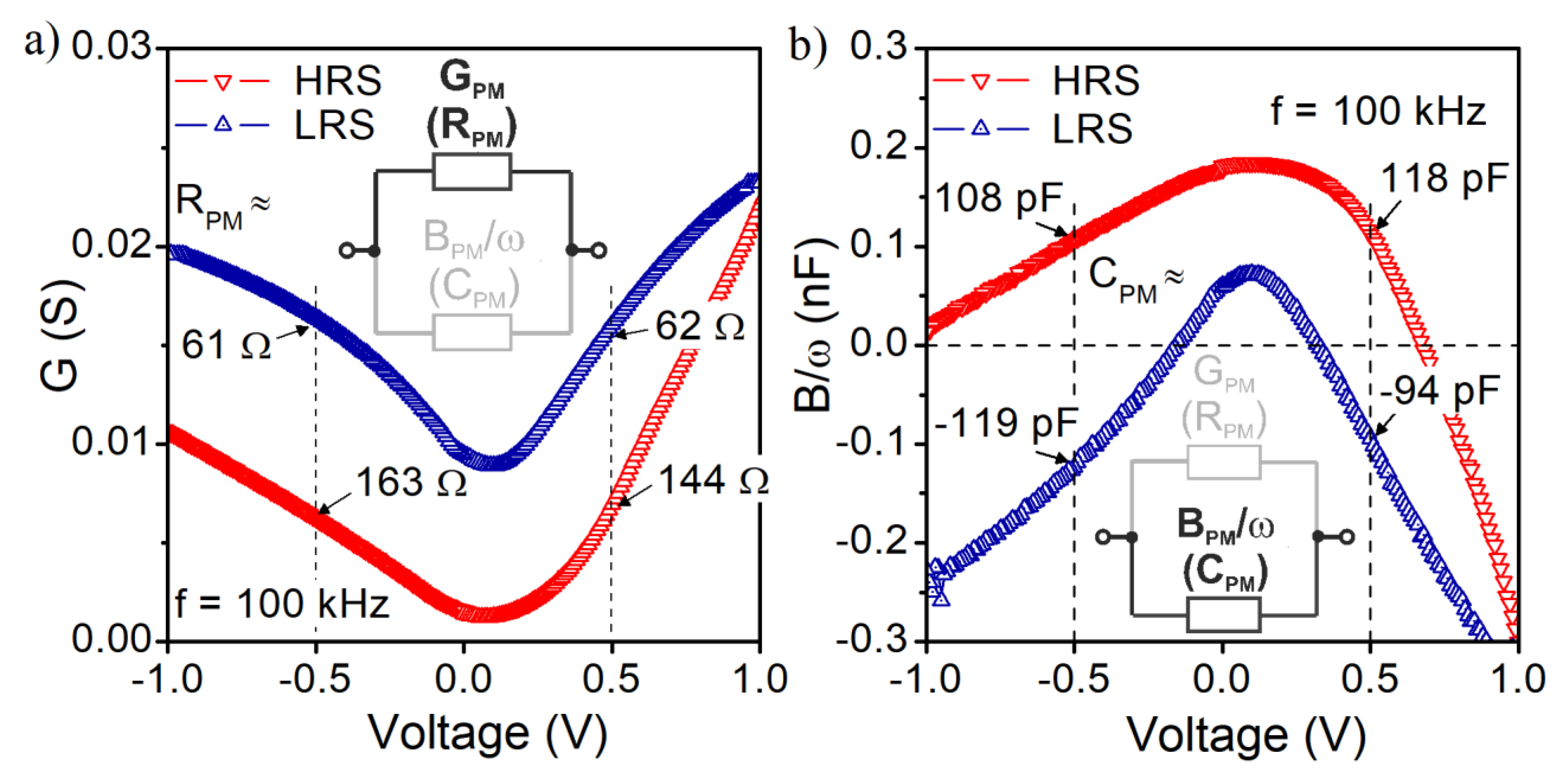

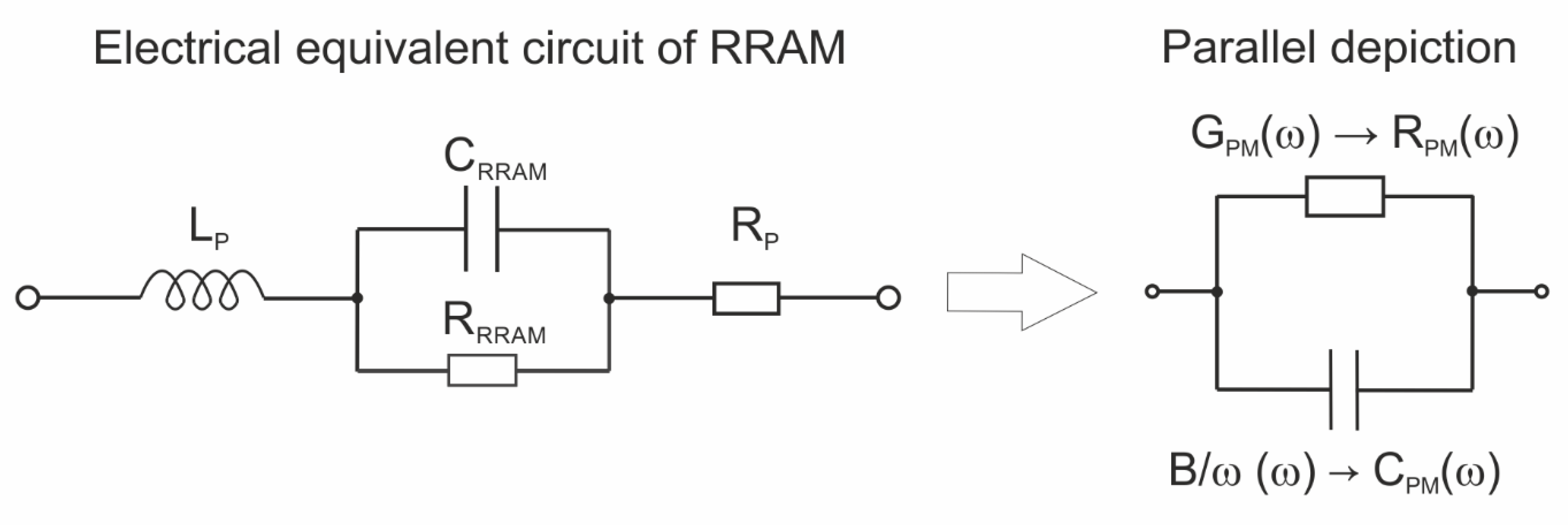

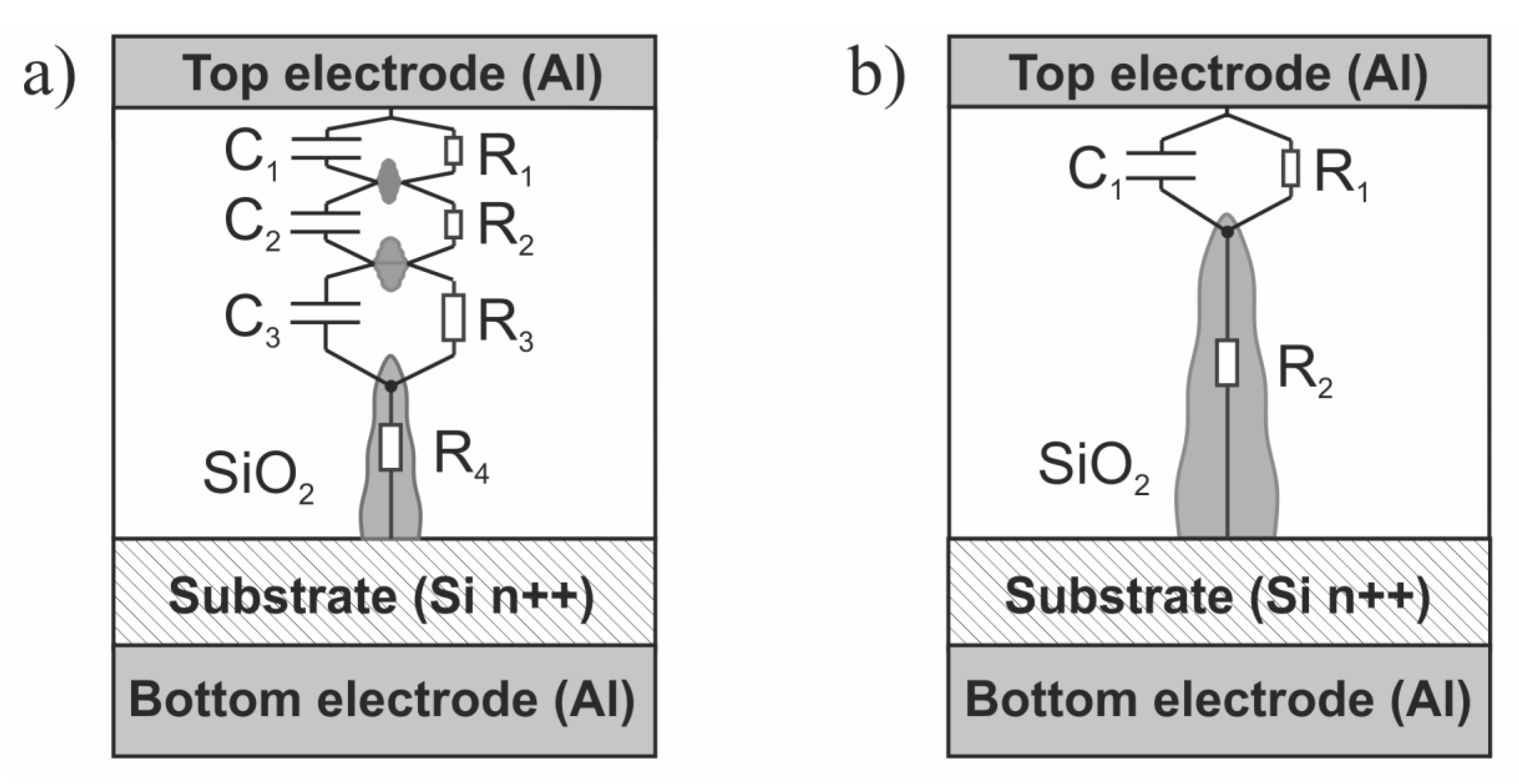

3.2. Small-Signal Measurements

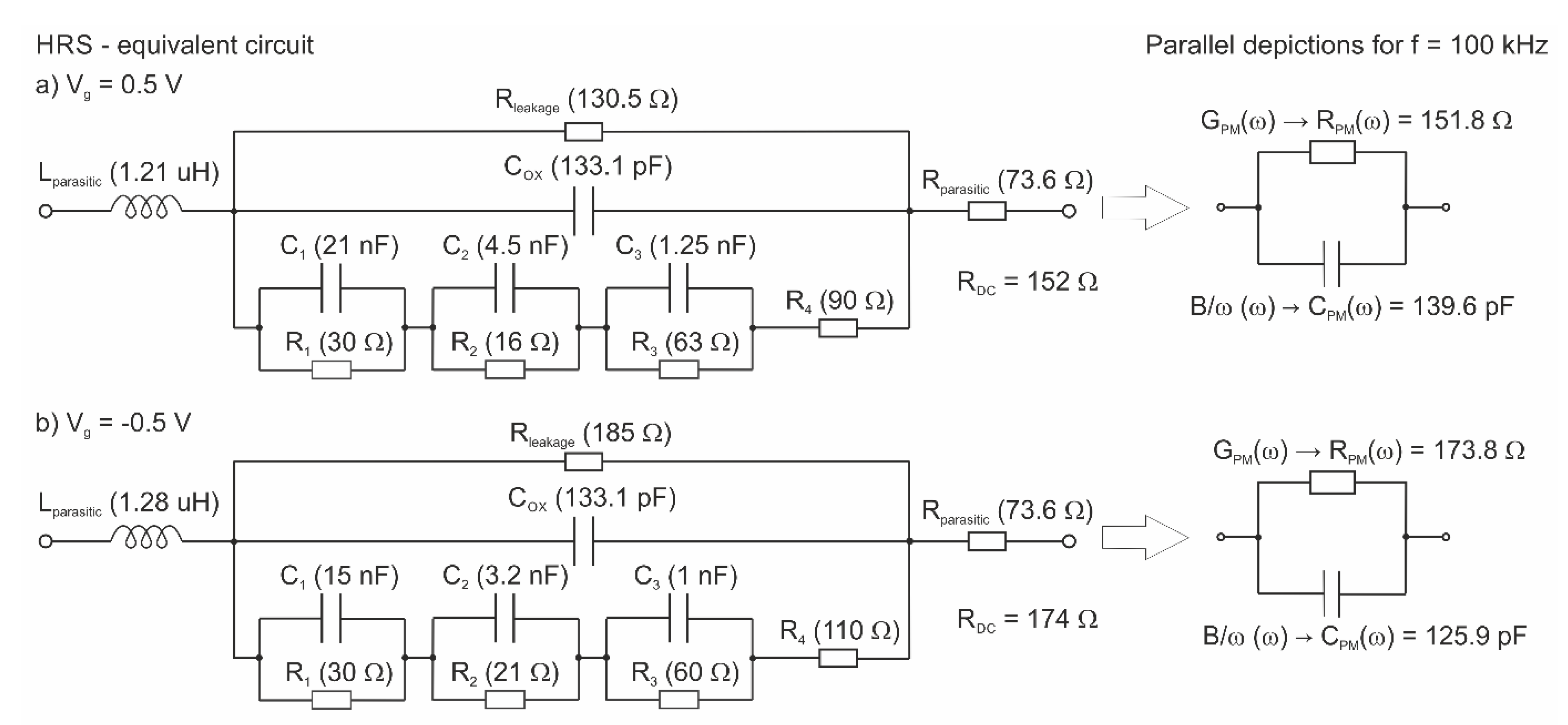

3.3. Complex Impedance Spectroscopy

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Chang, T.C.; Chang, K.C.; Tsai, T.M.; Chu, T.J.; Sze, S.M. Resistance random access memory. Mater. Today 2016, 19, 254–264. [Google Scholar] [CrossRef]

- Wong, H.S.P.; Lee, H.Y.; Yu, S.; Chen, Y.S.; Wu, Y.; Chen, P.S.; Lee, B.; Chen, F.T.; Tsai, M.J. Metal-oxide RRAM. Proc. IEEE 2012, 100, 1951–1970. [Google Scholar] [CrossRef]

- Shen, Z.; Zhao, C.; Qi, Y.; Xu, W.; Liu, Y.; Mitrovic, I.Z.; Yang, L.; Zhao, C. Advances of RRAM devices: Resistive switching mechanisms, materials and bionic synaptic application. Nanomaterials 2020, 10, 1437. [Google Scholar] [CrossRef] [PubMed]

- Boybat, I.; Le Gallo, M.; Nandakumar, S.R.; Moraitis, T.; Parnell, T.; Tuma, T.; Rajendran, B.; Leblebici, Y.; Sebastian, A.; Eleftheriou, E. Neuromorphic computing with multi-memristive synapses. Nat. Commun. 2018, 9, 1–12. [Google Scholar] [CrossRef]

- Sarkar, B.; Lee, B.; Misra, V. Understanding the gradual reset in Pt/Al2O3/Ni RRAM for synaptic applications. Semicond. Sci. Technol. 2015, 30. [Google Scholar] [CrossRef]

- Ielmini, D. Brain-inspired computing with resistive switching memory (RRAM): Devices, synapses and neural networks. Microelectron. Eng. 2018, 190, 44–53. [Google Scholar] [CrossRef]

- Jiang, Z.; Wang, Z.; Zheng, X.; Fong, S.W.; Qin, S.; Chen, H.Y.; Ahn, E.C.; Cao, J.; Nishi, Y.; Wong, S.S.; et al. Bidirectional Analog Conductance Modulation for RRAM-Based Neural Networks. IEEE Trans. Electron Devices 2020, 67, 4904–4910. [Google Scholar] [CrossRef]

- Wang, H.; Yan, X. Overview of Resistive Random Access Memory (RRAM): Materials, Filament Mechanisms, Performance Optimization, and Prospects. Phys. Status Solidi Rapid Res. Lett. 2019, 13, 1900073. [Google Scholar] [CrossRef]

- Lim, E.W.; Ismail, R. Conduction Mechanism of Valence Change Resistive Switching Memory: A Survey. Electronics 2015, 4, 586–613. [Google Scholar] [CrossRef]

- Yuan, F.-Y.; Deng, N.; Shih, C.-C.; Tseng, Y.-T.; Chang, T.-C.; Chang, K.-C.; Wang, M.-H.; Chen, W.-C.; Zheng, H.-X.; Wu, H.; et al. Conduction Mechanism and Improved Endurance in HfO 2 -Based RRAM with Nitridation Treatment. Nanoscale Res. Lett. 2017, 12, 1–6. [Google Scholar] [CrossRef]

- Yu, S.; Guan, X.; Wong, H.-S.P. Conduction mechanism of TiN/HfOx/Pt resistive switching memory: A trap-assisted-tunneling model. Appl. Phys. Lett. 2011, 99, 063507. [Google Scholar] [CrossRef]

- Gul, F. Carrier transport mechanism and bipolar resistive switching behavior of a nano-scale thin film TiO2 memristor. Ceram. Int. 2018, 44, 11417–11423. [Google Scholar] [CrossRef]

- Chai, Z.; Zhang, W.; Freitas, P.; Hatem, F.; Zhang, J.F.; Marsland, J.; Govoreanu, B.; Goux, L.; Kar, G.S.; Hall, S.; et al. The Over-Reset Phenomenon in Ta2O5 RRAM Device Investigated by the RTN-Based Defect Probing Technique. IEEE Electron Device Lett. 2018, 39, 955–958. [Google Scholar] [CrossRef] [Green Version]

- Traore, B.; Blaise, P.; Vianello, E.; Grampeix, H.; Jeannot, S.; Perniola, L.; De Salvo, B.; Nishi, Y. On the Origin of Low-Resistance State Retention Failure in HfO2-Based RRAM and Impact of Doping/Alloying. IEEE Trans. Electron Devices 2015, 62, 4029–4036. [Google Scholar] [CrossRef]

- Liu, T.; Verma, M.; Kang, Y.; Orlowski, M.K. I-V characteristics of antiparallel resistive switches observed in a single Cu/TaOx/Pt cell. IEEE Electron Device Lett. 2013, 34, 108–110. [Google Scholar] [CrossRef]

- Jung, P.Y.; Panda, D.; Chandrasekaran, S.; Rajasekaran, S.; Tseng, T.Y. Enhanced Switching Properties in TaOx Memristors Using Diffusion Limiting Layer for Synaptic Learning. IEEE J. Electron Devices Soc. 2020, 8, 110–115. [Google Scholar] [CrossRef]

- Mazurak, A.; Mroczyński, R.; Beke, D.; Gali, A. Silicon-Carbide (SiC) Nanocrystal Technology and Characterization and Its Applications in Memory Structures. Nanomaterials 2020, 10, 2387. [Google Scholar] [CrossRef]

- Fan, Y.S.; Zhang, L.; Crotti, D.; Witters, T.; Jurczak, M.; Govoreanu, B. Direct Evidence of the Overshoot Suppression in Ta2O5-Based Resistive Switching Memory with an Integrated Access Resistor. IEEE Electron Device Lett. 2015, 36, 1027–1029. [Google Scholar] [CrossRef]

- Wang, S.; Dang, B.; Sun, J.; Song, F.; Zhao, M.; Yang, M.; Ma, X.; Wang, H.; Hao, Y. Physically Transient Resistive Memory with Programmable Switching Behaviors in MgO-Mo Based Devices. IEEE Electron Device Lett. 2020, 41, 553–556. [Google Scholar] [CrossRef]

- Chang, Y.-F.; Chen, P.-Y.; Chen, Y.-T.; Xue, F.; Wang, Y.; Zhou, F.; Fowler, B.; Lee, J.C. Study of polarity effect in SiOx -based resistive switching memory. Appl. Phys. Lett. 2012, 101, 52111. [Google Scholar] [CrossRef]

- Chang, Y.-F.; Chen, P.-Y.; Fowler, B.; Chen, Y.-T.; Xue, F.; Wang, Y.; Zhou, F.; Lee, J.C. Understanding the resistive switching characteristics and mechanism in active SiO x-based resistive switching memory. J. Appl. Phys. 2012, 112, 123702. [Google Scholar] [CrossRef]

- Chang, Y.-F.; Fowler, B.; Chen, Y.-C.; Chen, Y.-T.; Wang, Y.; Xue, F.; Zhou, F.; Lee, J.C. Intrinsic SiO x-based unipolar resistive switching memory. I. Oxide stoichiometry effects on reversible switching and program window optimization. J. Appl. Phys. 2014, 116, 043708. [Google Scholar] [CrossRef]

- Chang, Y.-F.; Fowler, B.; Chen, Y.-C.; Chen, Y.-T.; Wang, Y.; Xue, F.; Zhou, F.; Lee, J.C. Intrinsic SiO x-based unipolar resistive switching memory. II. Thermal effects on charge transport and characterization of multilevel programing. J. Appl. Phys. 2014, 116, 043709. [Google Scholar] [CrossRef]

- Li, C.; Jiang, H.; Xia, Q. Low voltage resistive switching devices based on chemically produced silicon oxide. Appl. Phys. Lett. 2013, 103, 62104. [Google Scholar] [CrossRef] [Green Version]

- Mehonic, A.; Cueff, S.; Wojdak, M.; Hudziak, S.; Jambois, O.; Labbe, C.; Garrido, B.; Rizk, R.; Kenyon, A.J.; Cueff, S.; et al. Resistive switching in silicon suboxide films. J. Appl. Phys. 2012, 111. [Google Scholar] [CrossRef]

- Yoon, S.J.; Ryu, J.-H.; Ismail, M.; Chen, Y.-C.; Chang, Y.-F.; Yun, M.J.; Kim, H.-D.; Kim, S. Compliance current and temperature effects on non-volatile memory switching and volatile switching dynamics in a Cu/SiOx/p++—Si device. Appl. Phys. Lett 2019, 115, 212102. [Google Scholar] [CrossRef]

- Yao, J.; Sun, Z.; Zhong, L.; Natelson, D.; Tour, J.M. Resistive Switches and Memories from Silicon Oxide. Nano Lett. 2010, 10, 4105–4110. [Google Scholar] [CrossRef]

- Mehonic, A.; Shluger, A.L.; Gao, D.; Valov, I.; Miranda, E.; Ielmini, D.; Bricalli, A.; Ambrosi, E.; Li, C.; Yang, J.J.; et al. Silicon Oxide (SiOx): A Promising Material for Resistance Switching? Adv. Mater. 2018, 30, e1801187. [Google Scholar] [CrossRef] [Green Version]

- Ambrosi, E.; Bricalli, A.; Laudato, M.; Ielmini, D. Impact of oxide and electrode materials on the switching characteristics of oxide ReRAM devices. Faraday Discuss. 2019, 213, 87–98. [Google Scholar] [CrossRef] [Green Version]

- Tseng, Y.H.; Shen, W.C.; Lin, C.J. Modeling of electron conduction in contact resistive random access memory devices as random telegraph noise. J. Appl. Phys. 2012, 111, 073701. [Google Scholar] [CrossRef] [Green Version]

- Shen, W.C.; Mei, C.Y.; Chih, Y.D.; Sheu, S.S.; Tsai, M.J.; King, Y.C.; Lin, C.J. High-K metal gate contact RRAM (CRRAM) in pure 28nm CMOS logic process. Tech. Dig. Int. Electron Devices Meet. IEDM 2012, 745–748. [Google Scholar] [CrossRef]

- Tseng, Y.H.; Huang, C.E.; Kuo, C.H.; Chih, Y.D.; King, Y.C.; Lin, C.J. A new high-density and ultrasmall-cell-size contact RRAM (CR-RAM) with fully CMOS-logic-compatible technology and circuits. IEEE Trans. Electron Devices 2011, 58, 53–58. [Google Scholar] [CrossRef]

- Wang, Y.; Fowler, B.; Zhou, F.; Chang, Y.-F.; Chen, Y.-T.; Xue, F.; Lee, J.C. Effects of sidewall etching on electrical properties of SiOx resistive random access memory. Appl. Phys. Lett. 2013, 103, 213505. [Google Scholar] [CrossRef]

- Yan, X.; Zhou, Z.; Ding, B.; Zhao, J.; Zhang, Y. Superior resistive switching memory and biological synapse properties based on a simple TiN/SiO2/p-Si tunneling junction structure. J. Mater. Chem. C 2017, 5, 2259–2267. [Google Scholar] [CrossRef]

- Niu, G.; Calka, P.; der Maur, M.A.; Santoni, F.; Guha, S.; Fraschke, M.; Hamoumou, P.; Gautier, B.; Perez, E.; Walczyk, C.; et al. Geometric conductive filament confinement by nanotips for resistive switching of HfO2-RRAM devices with high performance. Sci. Rep. 2016, 6, 1–9. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Tran, X.A.; Zhu, W.; Liu, W.J.; Yeo, Y.C.; Nguyen, B.Y.; Yu, H.Y. Self-Selection Unipolar HfOx-Based RRAM. IEEE Trans. Electron Dev. 2012, 60, 391–395. [Google Scholar] [CrossRef]

- Kim, H.D.; Yun, M.; Kim, S. Self-rectifying resistive switching behavior observed in Si3N4-based resistive random access memory devices. J. Alloy. Compd. 2015, 651, 340–343. [Google Scholar] [CrossRef]

- Kim, S.; Chang, Y.-F.; Kim, M.-H.; Kim, T.-H.; Kim, Y.; Park, B.-G. Self-Compliant Bipolar Resistive Switching in SiN-Based Resistive Switching Memory. Materials 2017, 10, 459. [Google Scholar] [CrossRef] [Green Version]

- Maji, S.; Samanta, S.; Das, P.; Maikap, S.; Dhanak, V.R.; Mitrovic, I.Z.; Mahapatra, R. Set compliance current induced resistive memory characteristics of W/Hf/HfOx/TiN devices. J. Vac. Sci. Technol. B 2019, 37, 021204. [Google Scholar] [CrossRef]

- Lee, T.S.; Lee, N.J.; Abbas, H.; Lee, H.H.; Yoon, T.-S.; Kang, C.J. Compliance Current-Controlled Conducting Filament Formation in Tantalum Oxide-Based RRAM Devices with Different Top Electrodes. ACS Appl. Electron. Mater. 2020, 2, 1154–1161. [Google Scholar] [CrossRef]

- Chiu, F.C. A review on conduction mechanisms in dielectric films. Adv. Mater. Sci. Eng. 2014, 2014, 1–18. [Google Scholar] [CrossRef] [Green Version]

- Zhu, J.; Zhang, T.; Yang, Y.; Huang, R. A comprehensive review on emerging artificial neuromorphic devices. Appl. Phys. Rev. 2020, 7. [Google Scholar] [CrossRef]

- Napolean, A.; Sivamangai, N.M.; Samuel, J.; John, V. Overview of Current Compliance Effect on Reliability of Nano Scaled Metal Oxide Resistive Random Access Memory Device. In Proceedings of the 4th International Conference on Devices, Circuits and Systems (ICDCS), Coimbatore, India, 16–17 March 2018. [Google Scholar] [CrossRef]

- Jiang, X.L.; Zhao, Y.G.; Chen, Y.S.; Li, D.; Luo, Y.X.; Zhao, D.Y.; Sun, Z.; Sun, J.R.; Zhao, H.W. Characteristics of different types of filaments in resistive switching memories investigated by complex impedance spectroscopy. Appl. Phys. Lett. 2013, 102, 253507. [Google Scholar] [CrossRef]

- Jeong, D.S.; Schroeder, H.; Waser, R. Impedance spectroscopy of TiO2 thin films showing resistive switching. Appl. Phys. Lett. 2006, 89, 082909. [Google Scholar] [CrossRef] [Green Version]

- Shen, Y.-S.; Ho, C.-C.; Chiou, B.-S. Impedance Spectroscopy of CaCu3Ti4O12 Films Showing Resistive Switching. J. Electrochem. Soc. 2009, 156, H466–H470. [Google Scholar] [CrossRef]

- Dueñas, S.; Castán, H.; García, H.; Miranda, E.; Gonzalez, M.B.; Campabadal, F. Study of the admittance hysteresis cycles in TiN/Ti/HfO2/W-based RRAM devices. Microelectron. Eng. 2017, 178, 30–33. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wiśniewski, P.; Jasiński, J.; Mazurak, A.; Stonio, B.; Majkusiak, B. Investigation of Electrical Properties of the Al/SiO2/n++-Si Resistive Switching Structures by Means of Static, Admittance, and Impedance Spectroscopy Measurements. Materials 2021, 14, 6042. https://doi.org/10.3390/ma14206042

Wiśniewski P, Jasiński J, Mazurak A, Stonio B, Majkusiak B. Investigation of Electrical Properties of the Al/SiO2/n++-Si Resistive Switching Structures by Means of Static, Admittance, and Impedance Spectroscopy Measurements. Materials. 2021; 14(20):6042. https://doi.org/10.3390/ma14206042

Chicago/Turabian StyleWiśniewski, Piotr, Jakub Jasiński, Andrzej Mazurak, Bartłomiej Stonio, and Bogdan Majkusiak. 2021. "Investigation of Electrical Properties of the Al/SiO2/n++-Si Resistive Switching Structures by Means of Static, Admittance, and Impedance Spectroscopy Measurements" Materials 14, no. 20: 6042. https://doi.org/10.3390/ma14206042

APA StyleWiśniewski, P., Jasiński, J., Mazurak, A., Stonio, B., & Majkusiak, B. (2021). Investigation of Electrical Properties of the Al/SiO2/n++-Si Resistive Switching Structures by Means of Static, Admittance, and Impedance Spectroscopy Measurements. Materials, 14(20), 6042. https://doi.org/10.3390/ma14206042