A Feasible Alternative to FDSOI and FinFET: Optimization of W/La2O3/Si Planar PMOS with 14 nm Gate-Length

Abstract

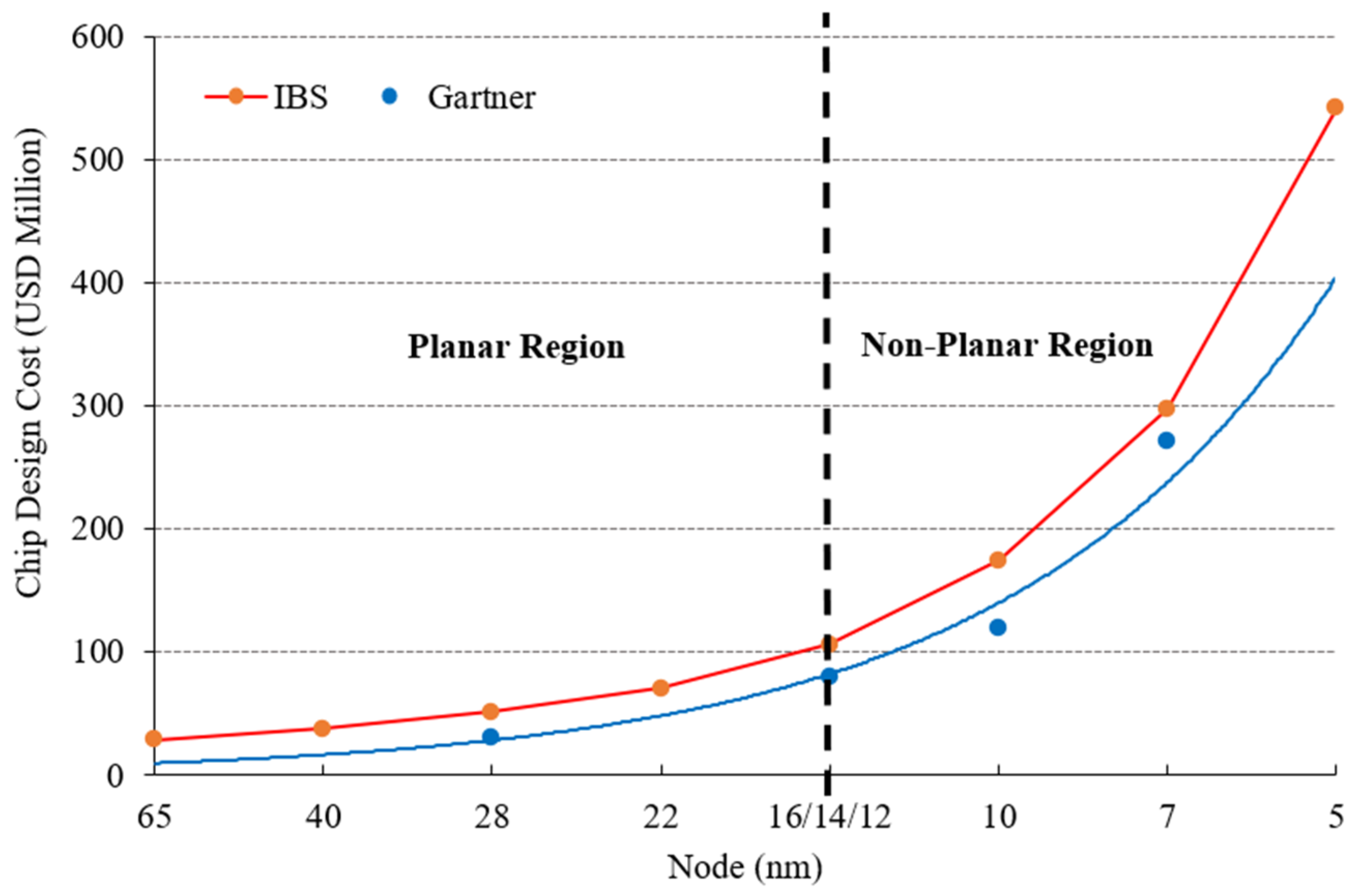

:1. Introduction

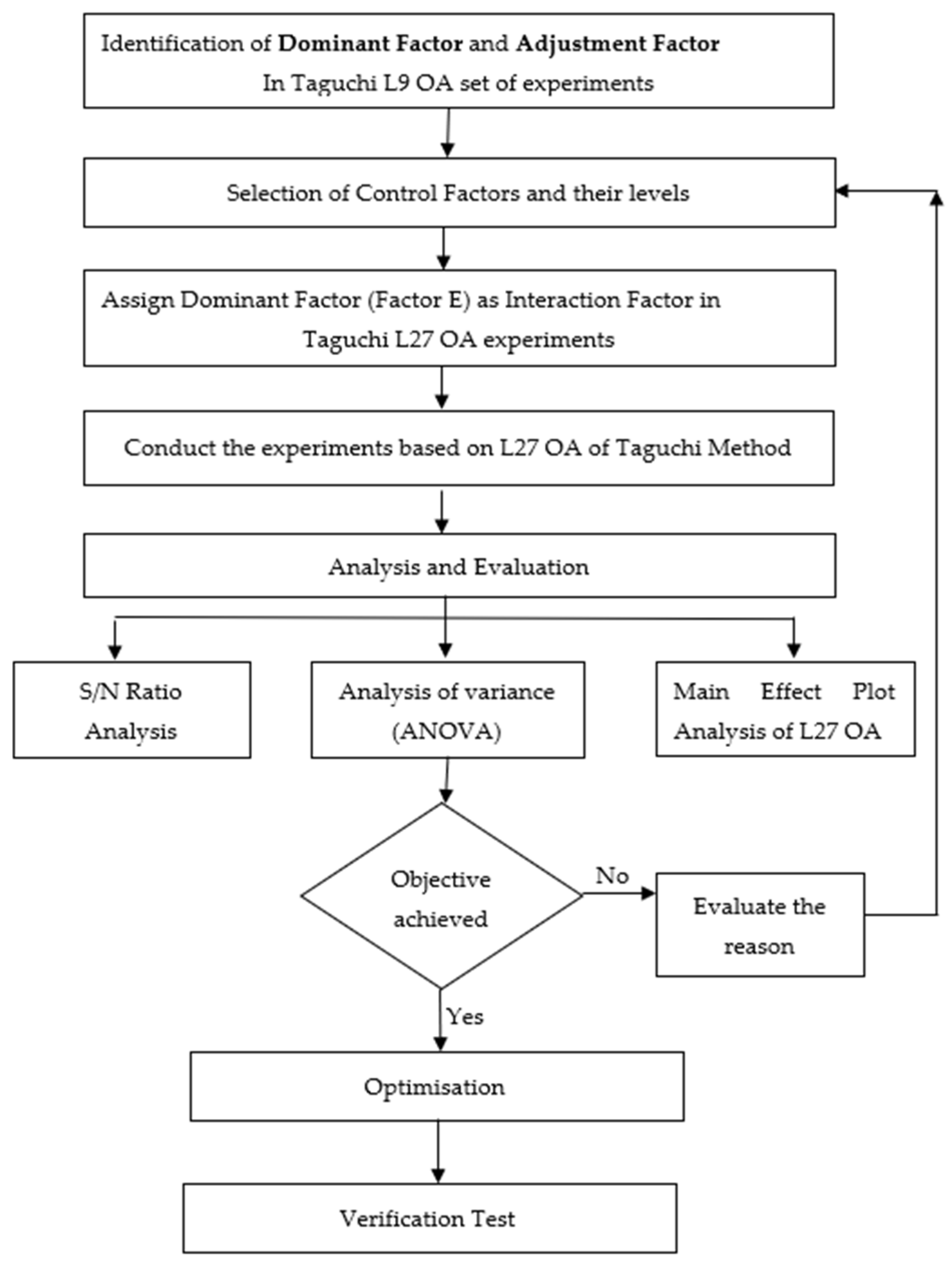

2. Materials and Methods

3. Results

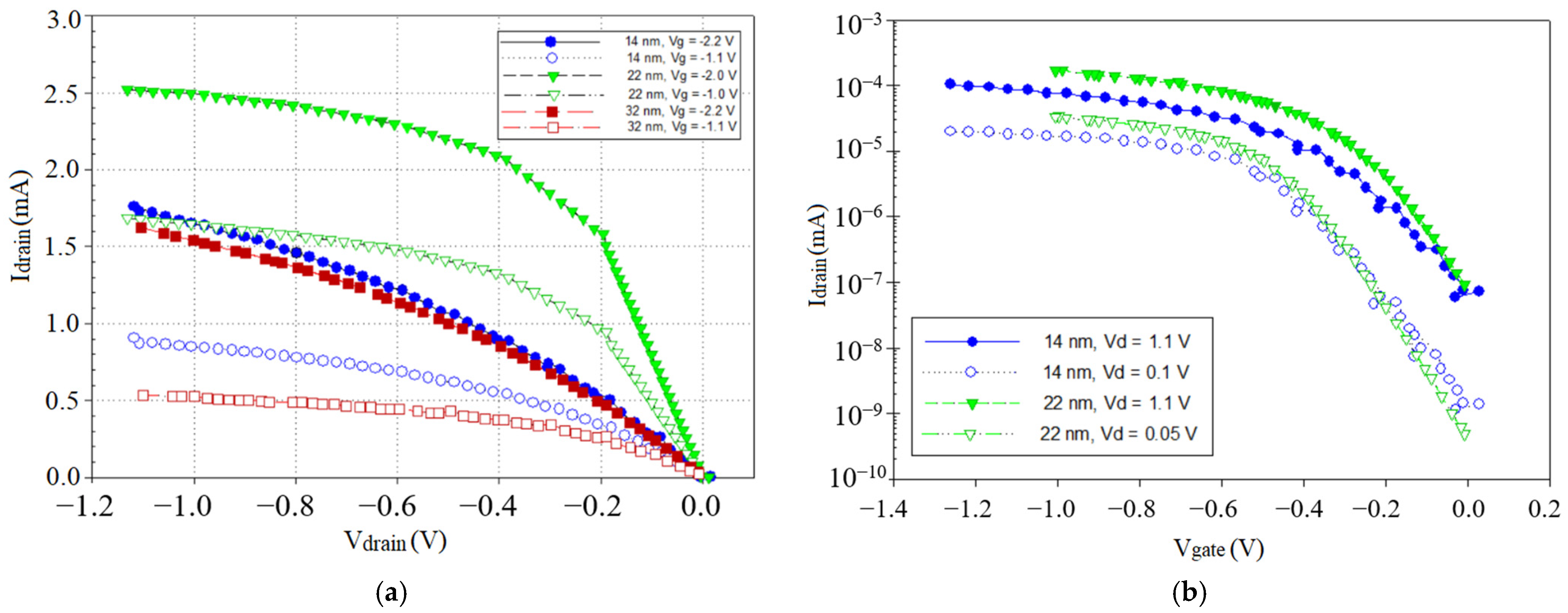

3.1. Virtual Fabrication of 14-nm-Gate-Length PMOS

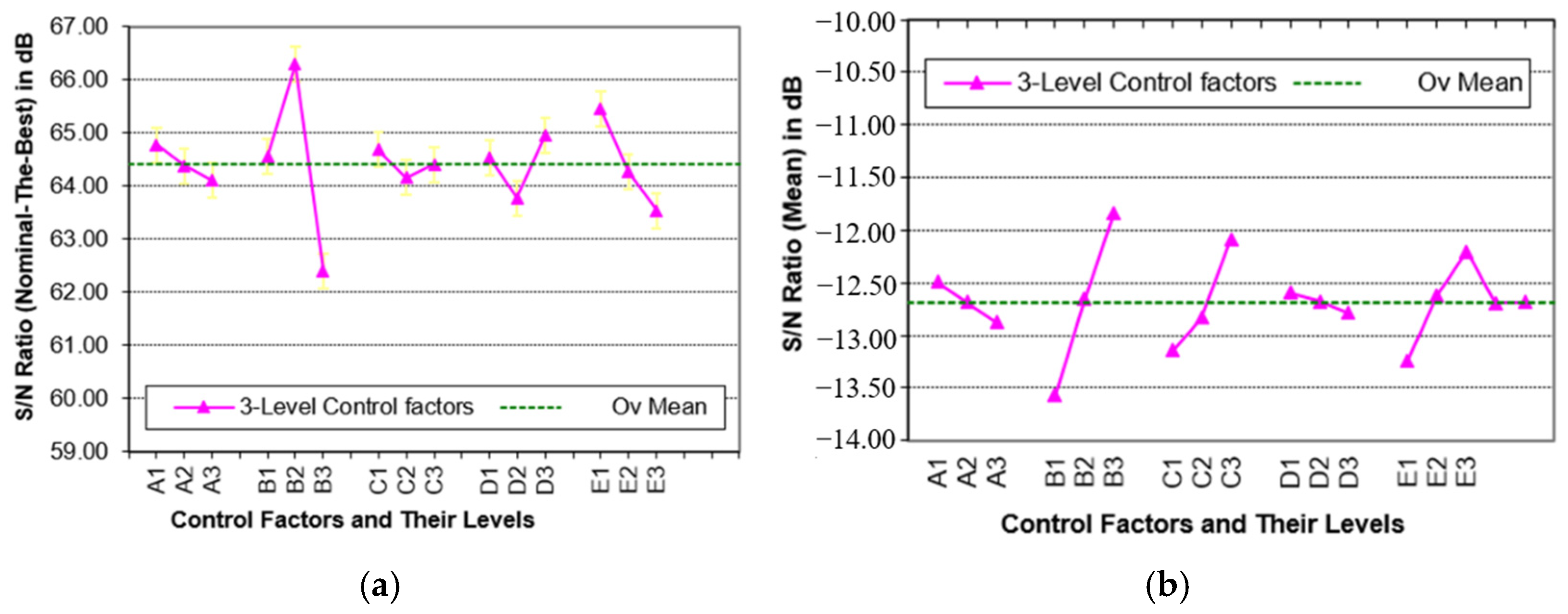

3.2. Taguchi L9 and L27 Orthogonal Array Method

4. Discussion

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Weber, O. FDSOI vs. FinFET: Differentiating device features for ultra low power & IoT applications. In Proceedings of the IC Design and Technology (ICICDT), 2017 IEEE International Conference, Austin, TX, USA, 23–25 May 2017; pp. 1–3. [Google Scholar]

- Skotnicki, T.; Hutchby, J.A.; Tsu-Jae, K.; Wong, H.P.; Boeuf, F. The end of CMOS scaling: Toward the introduction of new materials and structural changes to improve MOSFET performance. IEEE Circuits Devices Mag. 2005, 21, 16–26. [Google Scholar] [CrossRef]

- Kuhn, K.J. CMOS scaling for the 22nm node and beyond: Device physics and technology. In Proceedings of the 2011 International Symposium on VLSI Technology, Systems and Applications, Hsinchu, Taiwan, 25–27 April 2011; pp. 1–2. [Google Scholar]

- Ando, T. Ultimate scaling of high-κ gate dielectrics: Higher-κ or interfacial layer scavenging? Materials 2012, 5, 478–500. [Google Scholar] [CrossRef] [Green Version]

- Vashishtha, V.; Clark, L.T. Comparing bulk-Si FinFET and gate-all-around FETs for the 5 nm technology node. Microelectron. J. 2021, 107, 104942. [Google Scholar] [CrossRef]

- Mounir Mahmoud, M.; Soin, N. A comparative study of lifetime reliability of planar MOSFET and FinFET due to BTI for the 16 nm CMOS technology node based on reaction-diffusion model. Microelectron. Reliab. 2019, 97, 53–65. [Google Scholar] [CrossRef]

- Xinlin, W.; Shahidi, G.; Oldiges, P.; Khare, M. Device scaling of high performance MOSFET with metal gate high-k at 32nm technology node and beyond. In Proceedings of the 2008 International Conference on Simulation of Semiconductor Processes and Devices, Kanagawa, Japan, 9–11 September 2008; pp. 309–312. [Google Scholar]

- Kotlyar, R.; Giles, M.D.; Matagne, P.; Obradovic, B.; Shifren, L.; Stettler, M.; Wang, E. Inversion mobility and gate leakage in high-k/metal gate MOSFETs. In Proceedings of the IEDM Technical Digest, IEEE International Electron Devices Meeting, San Francisco, CA, USA, 13–15 December 2004; pp. 391–394. [Google Scholar]

- Pan, C.; Naeemi, A. A Paradigm Shift in Local Interconnect Technology Design in the Era of Nanoscale Multigate and Gate-All-Around Devices. IEEE Electron Device Lett. 2015, 36, 274–276. [Google Scholar] [CrossRef]

- Monfray, S.; Skotnicki, T. UTBB FDSOI: Evolution and opportunities. Solid-State Electron. 2016, 125, 63–72. [Google Scholar] [CrossRef]

- Triyoso, D.H.; Carter, R.; Kluth, J.; Hempel, K.; Gribelyuk, M.; Kang, L.; Kumar, A.; Mulfinger, B.; Javorka, P.; Punchihewa, K.; et al. Extending HKMG scaling on CMOS with FDSOI: Advantages and integration challenges. In Proceedings of the 2016 International Conference on IC Design and Technology (ICICDT), Ho Chi Minh City, Vietnam, 27–29 June 2016; pp. 1–4. [Google Scholar]

- Radamson, H.H.; He, X.; Zhang, Q.; Liu, J.; Cui, H.; Xiang, J.; Kong, Z.; Xiong, W.; Li, J.; Gao, J. Miniaturization of CMOS. Micromachines 2019, 10, 293. [Google Scholar] [CrossRef] [Green Version]

- Yang, L.; Zhang, Q.; Huang, Y.; Zheng, Z.; Li, B.; Li, B.; Zhang, X.; Zhu, H.; Yin, H.; Guo, Q.; et al. Total Ionizing Dose Response and Annealing Behavior of Bulk nFinFETs with ON-State Bias Irradiation. IEEE Trans. Nucl. Sci. 2018, 65, 1503–1510. [Google Scholar] [CrossRef]

- Khan, S.M. Securing Semiconductor Supply Chains; Center for Security and Emerging Technology (CSET): Washington, DC, USA, 2021. [Google Scholar]

- Khan, S.M.; Mann, A. AI Chips: What They Are and Why They Matter; Center for Security and Emerging Technology: Washington, DC, USA, 2020. [Google Scholar]

- Brewer, R.M.; Zhang, E.X.; Gorchichko, M.; Wang, P.F.; Cox, J.; Moran, S.L.; Ball, D.R.; Sierawski, B.D.; Fleetwood, D.M.; Schrimpf, R.D.; et al. Total Ionizing Dose Responses of 22-nm FDSOI and 14-nm Bulk FinFET Charge-Trap Transistors. IEEE Trans. Nucl. Sci. 2021, 68, 677–686. [Google Scholar] [CrossRef]

- He, H. 28nm to be a Long-Lived Node for Semiconductor Applications in the Next Five Years; Omdia: London, UK, 2020. [Google Scholar]

- Iwai, H. Roadmap for 22nm and beyond (Invited Paper). Microelectron. Eng. 2009, 86, 1520–1528. [Google Scholar] [CrossRef]

- Chen, X.; Samavedam, S.; Narayanan, V.; Stein, K.; Hobbs, C.; Baiocco, C.; Li, W.; Jaeger, D.; Zaleski, M.; Yang, H.S.; et al. A cost effective 32nm high-K/ metal gate CMOS technology for low power applications with single-metal/gate-first process. In Proceedings of the 2008 Symposium on VLSI Technology, Honolulu, HI, USA, 17–19 June 2008; pp. 88–89. [Google Scholar]

- Godara, M.; Madhu, C.; Joshi, G. Comparison of Electrical Characteristics of 28 Nm Bulk MOSFET and FDSOI MOSFET. In Proceedings of the 2018 IEEE Electron Devices Kolkata Conference (EDKCON), Kolkata, India, 24–25 November 2018; pp. 413–418. [Google Scholar]

- Fahim, A. Challenges in low-power analog circuit design for sub-28nm CMOS technologies. In Proceedings of the 2014 IEEE/ACM International Symposium on Low Power Electronics and Design (ISLPED), La Jolla, CA, USA, 11–13 August 2014; pp. 123–126. [Google Scholar]

- Wang, M.; Du, C.; Peng, M.; Wang, S.; Chen, S.; Liu, C.; Cheng, O.; Huang, L.S.; Lee, S.C. Trend of subthreshold swing with DPN process for 28nm N/PMOSFETs. In Proceedings of the 2013 International Symposium on Next-Generation Electronics, Kaohsiung, Taiwan, 25–26 February 2013; pp. 389–392. [Google Scholar]

- Elgomati, H.; Majlis, B.Y.; Hamid, A.A.; Susthitha, P.; Ahmad, I. Modelling of process parameters for 32nm PMOS transistor using Taguchi method. In Proceedings of the 2012 Sixth Asia Modelling Symposium, Bali, Indonesia, 29–31 May 2012; pp. 40–45. [Google Scholar]

- Maheran, A.H.A.; Menon, P.S.; Shaari, S.; Ahmad, I.; Faizah, Z.A.N. Statistical optimization of process parameters for threshold voltage in 22 nm p-Type MOSFET using Taguchi method. In Proceedings of the 2015 IEEE Regional Symposium on Micro and Nanoelectronics (RSM), Kuala Terengganu, Malaysia, 19–21 August 2015; pp. 1–4. [Google Scholar]

- Daneshgar, S.; Dasgupta, K.; Thakkar, C.; Chakrabarti, A.; Levy, C.S.; Jaussi, J.E.; Casper, B. High-Power Generation for mm-Wave 5G Power Amplifiers in Deep Submicrometer Planar and FinFET Bulk CMOS. IEEE Trans. Microw. Theory Tech. 2020, 68, 2041–2056. [Google Scholar] [CrossRef]

- Callender, S.; Shin, W.; Lee, H.; Pellerano, S.; Hull, C. FinFET for mm Wave-Technology and Circuit Design Challenges. In Proceedings of the 2018 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS), San Diego, CA, USA, 15–17 October 2018; pp. 168–173. [Google Scholar]

- Wakabayashi, H.; Ezaki, T.; Sakamoto, T.; Kawaura, H.; Ikarashi, N.; Ikezawa, N.; Narihiro, M.; Ochiai, Y.; Ikezawa, T.; Takeuchi, K.; et al. Characteristics and Modeling of Sub-10-nm Planar Bulk CMOS Devices Fabricated by Lateral Source/Drain Junction Control. IEEE Trans. Electron Devices 2006, 53, 1961–1970. [Google Scholar] [CrossRef]

- Swami, Y.; Rai, S. Modeling and analysis of sub-surface leakage current in nano-MOSFET under cutoff regime. Superlattices Microstruct. 2017, 102, 259–272. [Google Scholar] [CrossRef]

- Ablat, A.; Mamat, M.; Ghupur, Y.; Aimidula, A.; Wu, R.; Ali Baqi, M.; Gholam, T.; Wang, J.; Qian, H.; Wu, R.; et al. Electronic structure of La2O3/Si interface by in situ photoemission spectroscopy. Mater. Lett. 2017, 191, 97–100. [Google Scholar] [CrossRef]

- Fei, C.; Liu, H.; Wang, X.; Zhao, L.; Zhao, D.; Feng, X. Effects of Rapid Thermal Annealing and Different Oxidants on the Properties of LaxAlyO Nanolaminate Films Deposited by Atomic Layer Deposition. Nanoscale Res. Lett. 2017, 12, 218. [Google Scholar] [CrossRef] [Green Version]

- Jun, J.-H.; Wang, C.-H.; Won, D.-J.; Choi, D.-J. Structural and electrical properties of a La2O3 thin film as a gate dielectric. J. Kor. Phys. Soc 2002, 41, 998–1002. [Google Scholar]

- Cheng, J.-B.; Li, A.-D.; Shao, Q.-Y.; Ling, H.-Q.; Wu, D.; Wang, Y.; Bao, Y.-J.; Wang, M.; Liu, Z.-G.; Ming, N.-B. Growth and characteristics of La2O3 gate dielectric prepared by low pressure metalorganic chemical vapor deposition. Appl. Surf. Sci. 2004, 233, 91–98. [Google Scholar] [CrossRef]

- Wang, X.; Liu, H.; Zhao, L.; Fei, C.; Feng, X.; Chen, S.; Wang, Y. Structural Properties Characterized by the Film Thickness and Annealing Temperature for La2O3 Films Grown by Atomic Layer Deposition. Nanoscale Res. Lett. 2017, 12, 233. [Google Scholar] [CrossRef] [Green Version]

- Zhang, X.; Tu, H.; Zhao, H.; Yang, M.; Wang, X.; Xiong, Y.; Yang, Z.; Du, J.; Wang, W.; Chen, D. Band structure and electronic characteristics of cubic La2O3 gate dielectrics epitaxially grown on InP substrates. Appl. Phys. Lett. 2011, 99, 132902. [Google Scholar] [CrossRef]

- Maheran, A.H.A.; Faizah, Z.A.N.; Menon, P.S.; Ahmad, I.; Apte, P.R.; Kalaivani, T.; Salehuddin, F. Statistical process modelling for 32nm high-K/metal gate PMOS device. In Proceedings of the 2014 IEEE International Conference on Semiconductor Electronics (ICSE2014), Kuala Lumpur, Malaysia, 27–29 August 2014; pp. 232–235. [Google Scholar]

- Maheran, A.A.; Menon, P.; Ahmad, I.; Yusoff, Z. Threshold voltage optimization in a 22nm High-k/Salicide PMOS device. In Proceedings of the Micro and Nanoelectronics (RSM), 2013 IEEE Regional Symposium, Daerah Langkawi, Malaysia, 25–27 September 2013; pp. 126–129. [Google Scholar]

- Silvaco, T. Manuals, ATLAS, ATHENA; Silvaco International Co.: Santa Clara, CA, USA, 2018. [Google Scholar]

- Mah, S.; Ahmad, I.; Ker, P.J.; ZA, N.F. Modelling of 14NM Gate Length La2O3 -based n-Type MOSFET. J. Telecommun. Electron. Comput. Eng. (JTEC) 2016, 8, 107–110. [Google Scholar]

- Mah, S.; Ahmad, I.; Ker, P.J.; ZA, N.F. High-k Dielectric Thickness and Halo Implant on Threshold Voltage Control. J. Telecommun. Electron. Comput. Eng. (JTEC) 2018, 10, 1–5. [Google Scholar]

- Abbasi, S.A.; Busnaina, A.; Isaacs, J.A. Cumulative Energy Demand for Printing Nanoscale Electronics. Procedia CIRP 2019, 80, 298–303. [Google Scholar] [CrossRef]

- Kuhn, K.J. CMOS transistor scaling past 32nm and implications on variation. In Proceedings of the 2010 IEEE/SEMI Advanced Semiconductor Manufacturing Conference (ASMC), San Francisco, CA, USA, 11–13 July 2010; pp. 241–246. [Google Scholar]

- Maheran, A.A.; Menon, P.; Shaari, S.; Kalaivani, T.; Ahmad, I.; Faizah, Z.N.; Apte, P. Effect of process parameter variability on the threshold voltage of downscaled 22nm PMOS using taguchi method. In Proceedings of the Semiconductor Electronics (ICSE), 2014 IEEE International Conference, Kuala Lumpur, Malaysia, 27–29 August 2014; pp. 178–181. [Google Scholar]

- Weste, N.H.; Harris, D. CMOS VLSI Design: A Circuits and Systems Perspective; Pearson Education Inc.: London, UK, 2011. [Google Scholar]

- Taur, Y.; Ning, T.H. Fundamentals of Modern VLSI Devices; Cambridge University Press: Cambridge, UK, 2013. [Google Scholar]

- Anantha, C.; William, J.B.; Frank, F. Techniques for Leakage Power Reduction. In Design of High-Performance Microprocessor Circuits; IEEE: New York, NY, USA, 2001; pp. 46–62. [Google Scholar]

- Phadke, M. Quality Engineering Using Robust Design; Prentice Hall PTR: Hoboken, NJ, USA, 1989; pp. 108–112. [Google Scholar]

- Ah, A.M.; Menon, P.; Ahmad, I.; Salehuddin, F.; Zain, A.M. Process parameter optimisation for minimum leakage current in a 22nm p-type MOSFET using Taguchi method. J. Telecommun. Electron. Comput. Eng. (JTEC) 2016, 8, 19–23. [Google Scholar]

- Lemme, M.C.; Efavi, J.K.; Gottlob, H.D.B.; Mollenhauer, T.; Wahlbrink, T.; Kurz, H. Comparison of metal gate electrodes on MOCVD HfO2. Microelectron. Reliab. 2005, 45, 953–956. [Google Scholar] [CrossRef]

- Lin, R.; Qiang, L.; Ranade, P.; Tsu-Jae, K.; Chenming, H. An adjustable work function technology using Mo gate for CMOS devices. IEEE Electron Device Lett. 2002, 23, 49–51. [Google Scholar] [CrossRef]

- Weber, O.; Josse, E.; Andrieu, F.; Cros, A.; Richard, E.; Perreau, P.; Baylac, E.; Degors, N.; Gallon, C.; Perrin, E.; et al. 14nm FDSOI technology for high speed and energy efficient applications. In Proceedings of the 2014 Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Papers, Honolulu, HI, USA, 9–12 June 2014; pp. 1–2. [Google Scholar]

- Mäkipää, J.; Billoint, O. FDSOI versus BULK CMOS at 28 nm node which technology for ultra-low power design? In Proceedings of the 2013 IEEE International Symposium on Circuits and Systems (ISCAS), Beijing, China, 19–23 May 2013; pp. 554–557. [Google Scholar]

- Wang, G.; Luo, J.; Qin, C.; Liang, R.; Xu, Y.; Liu, J.; Li, J.; Yin, H.; Yan, J.; Zhu, H. Integration of Highly Strained SiGe in Source and Drain with HK and MG for 22 nm Bulk PMOS Transistors. Nanoscale Res. Lett. 2017, 12, 123. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Chau, R.; Kavalieros, J.; Roberds, B.; Schenker, R.; Lionberger, D.; Barlage, D.; Doyle, B.; Arghavani, R.; Murthy, A.; Dewey, G. 30 nm physical gate length CMOS transistors with 1.0 ps n-MOS and 1.7 ps p-MOS gate delays. In Proceedings of the International Electron Devices Meeting 2000. Technical Digest. IEDM (Cat. No.00CH37138), San Francisco, CA, USA, 10–13 December 2000; pp. 45–48. [Google Scholar]

- Wakabayashi, H.; Ueki, M.; Narihiro, M.; Fukai, T.; Ikezawa, N.; Matsuda, T.; Yoshida, K.; Takeuchi, K.; Ochiai, Y.; Mogami, T.; et al. Sub-50-nm physical gate length CMOS technology and beyond using steep halo. IEEE Trans. Electron Devices 2002, 49, 89–95. [Google Scholar] [CrossRef]

- Inaba, S.; Okano, K.; Matsuda, S.; Fujiwara, M.; Hokazono, A.; Adachi, K.; Ohuchi, K.; Suto, H.; Fukui, H.; Shimizu, T.; et al. High performance 35 nm gate length CMOS with NO oxynitride gate dielectric and Ni salicide. IEEE Trans. Electron Devices 2002, 49, 2263–2270. [Google Scholar] [CrossRef]

- Mistry, K.; Allen, C.; Auth, C.; Beattie, B.; Bergstrom, D.; Bost, M.; Brazier, M.; Buehler, M.; Cappellani, A.; Chau, R.; et al. A 45nm Logic Technology with High-k+Metal Gate Transistors, Strained Silicon, 9 Cu Interconnect Layers, 193nm Dry Patterning, and 100% Pb-free Packaging. In Proceedings of the 2007 IEEE International Electron Devices Meeting, Washington, DC, USA, 10–12 December 2007; pp. 247–250. [Google Scholar]

- Ghani, T.; Armstrong, M.; Auth, C.; Bost, M.; Charvat, P.; Glass, G.; Hoffmann, T.; Johnson, K.; Kenyon, C.; Klaus, J.; et al. A 90nm high volume manufacturing logic technology featuring novel 45nm gate length strained silicon CMOS transistors. In Proceedings of the IEEE International Electron Devices Meeting 2003, Washington, DC, USA, 8–10 December 2003; pp. 11.16.11–11.16.13. [Google Scholar]

- International Technology Roadmap for Semiconductors (ITRS) 2013 Edition. Available online: http://www.itrs2.net/2013-itrs.html (accessed on 8 March 2021).

- Morvan, S.; Andrieu, F.; Cassé, M.; Weber, O.; Xu, N.; Perreau, P.; Hartmann, J.M.; Barbé, J.C.; Mazurier, J.; Nguyen, P.; et al. Efficiency of mechanical stressors in Planar FDSOI n and p MOSFETs down to 14nm gate length. In Proceedings of the 2012 Symposium on VLSI Technology (VLSIT), Honolulu, HI, USA, 12–14 June 2012; pp. 111–112. [Google Scholar]

- Barral, V.; Poiroux, T.; Andrieu, F.; Buj-Dufournet, C.; Faynot, O.; Ernst, T.; Brevard, L.; Fenouillet-Beranger, C.; Lafond, D.; Hartmann, J.M.; et al. Strained FDSOI CMOS technology scalability down to 2.5nm film thickness and 18nm gate length with a TiN/HfO2 gate stack. In Proceedings of the 2007 IEEE International Electron Devices Meeting, Washington, DC, USA, 10–12 December 2007; pp. 61–64. [Google Scholar]

- Cheng, K.; Khakifirooz, A.; Kulkarni, P.; Kanakasabapathy, S.; Schmitz, S.; Reznicek, A.; Adam, T.; Zhu, Y.; Li, J.; Faltermeier, J.; et al. Fully depleted extremely thin SOI technology fabricated by a novel integration scheme featuring implant-free, zero-silicon-loss, and faceted raised source/drain. In Proceedings of the 2009 Symposium on VLSI Technology, Kyoto, Japan, 15–17 June 2009; pp. 212–213. [Google Scholar]

- International Roadmap for Devices and Systems (IRDS™) 2017 Edition. Available online: https://irds.ieee.org/editions/2017 (accessed on 8 March 2021).

- Sicard, E. Introducing 7-nm FinFET technology in Microwind; Application Note hal-01558775; Institut National des Sciences Appliquées: Toulouse, France, 2017. [Google Scholar]

- Zhang, J.; Niu, G.; Cai, W.; Imura, K. Comparison of PMOS and NMOS in a 14-nm RF FinFET technology: RF Characteristics and Compact Modeling. In Proceedings of the 2020 IEEE 20th Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems (SiRF), San Antonio, TX, USA, 26–29 January 2020; pp. 47–49. [Google Scholar]

- Wang, G.; Qin, C.; Yin, H.; Luo, J.; Duan, N.; Yang, P.; Gao, X.; Yang, T.; Li, J.; Yan, J.; et al. Study of SiGe selective epitaxial process integration with high-k and metal gate for 16/14nm nodes FinFET technology. Microelectron. Eng. 2016, 163, 49–54. [Google Scholar] [CrossRef]

- International Roadmap for Devices and Systems (IRDS™) 2020 Edition. Available online: https://irds.ieee.org/editions/2020 (accessed on 8 March 2021).

| Process Step | PMOS Parameters | Process Environment |

|---|---|---|

| Silicon substrate | <100> orientation | |

| Retrograde well implantation | 200 Å oxide screen | 970 °C, 20 min of dry O2 |

| 4.5 × 1011 cm−3 phosphorus | ||

| 30 min, 900 °C diffused in nitrogen | ||

| 36 min, dry O2 | ||

| STI isolation | 130 Å stress buffer | 900 °C, 25 min of dry O2 |

| 1500 Å Si3N4, applying LPCVD | ||

| 1.0 μm photoresist deposition | ||

| 15 min annealing at 900 °C | ||

| Gate oxide | Diffused dry O2 | 0.1 min, 815 °C |

| Vth adjust implant | 1.8 × 1011 cm−2 BF2 | 5 keV implant energy, 7° tilt |

| 20 min annealing at 800 °C | ||

| High-k/metal gate deposition | 0.002 μm La2O3 | 17 min, 900 °C annealing |

| 0.0038 μm W | ||

| LDD implantation | 3 × 1013 cm−3 phosphor | 20° tilt |

| Sidewall spacer deposition | 0.008 μm Si3N4 | |

| S/D implantation | 1.4 × 1013 cm−3 Boron | 10 keV implant energy |

| 7° tilt | ||

| PMD deposition | 0.3 μm BPSG | 25 min, 850 °C annealing |

| Metal 1 | 0.04 μm aluminum | |

| IMD deposition | 0.04 μm BPSG | 15 min, 950 °C annealing |

| Metal 2 | 0.12 μm aluminum |

| Sym. | Control Factor | Units | Level 1 | Level 2 | Level 3 |

|---|---|---|---|---|---|

| A | Halo Implantation Dose | atom/cm3 | 5.35 × 1013 | 5.40 × 1013 | 5.45 × 1013 |

| B | Halo Implantation Energy | keV | 158 | 160 | 162 |

| C | Source/Drain Implantation Tilt | ° | 6.5 | 7.0 | 7.5 |

| D | Compensation Implantation | atom/cm3 | 1.0 × 1012 | 1.1 × 1012 | 1.2 × 1012 |

| E | Source/Drain Implantation Dose | atom/cm3 | 1.38 × 1013 | 1.41 × 1013 | 1.43 × 1013 |

| Sym. | Level 1 | Level 2 | Level 3 | Factor Effect Nominal (%) | Factor Effect Mean (%) |

|---|---|---|---|---|---|

| A | 64.77 | 64.38 | 64.10 | 2.10 | 2.76 |

| B | 64.54 | 66.29 | 62.41 | 69.72 | 55.00 |

| C | 64.68 | 64.16 | 64.40 | 1.28 | 21.60 |

| D | 64.52 | 63.77 | 64.95 | 6.52 | 0.69 |

| E | 65.45 | 64.26 | 63.53 | 17.18 | 19.95 |

| A1B2C3D3E1 | X1, Y1 | X1, Y2 | X2, Y1 | X2, Y2 | Mean |

|---|---|---|---|---|---|

| Vth (V) | −0.233449 | −0.233613 | −0.233489 | −0.233653 | −0.233551 |

| Ion(µA/µm) | 10,900 | 10,900 | 10,860 | 10,900 | 10,900 |

| Ioff(nA/µm) | 107 | 108 | 107 | 108 | 80.6 |

| Planar Bulk PMOS (Experimental) | Planar Bulk (ITRS2013) | This Result | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| Node Range | 32 | 65 | 65 | 90 | 100 | 100 | “8/7” | “16/14” | Before Optimisation | Optimised Results |

| Lg | 25 nm | 30 nm | 33 nm | 35 nm | 45 nm | 50 nm | 14 nm | 20 nm | 14 nm | 14 nm |

| Vth (V) | N/A | N/A | −0.2 | N/A | −0.25 | −0.2 | 0.230 | 0.190 | −0.230781 | −0.23355 |

| Ion(µA/µm) | 488 | 285 at 0.85 V | 400 at 1.2 V | 272 at 0.85 V | 1070 at 1 V | 700 at 1.2 V | >1267 | >1348 | 10,900 | 10,900 |

| Ioff(nA/µm) | 0.83 | <83 at 0.85 V | 300 at 1.2 V | 100 at 0.85 V | 100 at 1 V | 40 at 1.2 V | <100 | <100 | 100 | 80.6 |

| Ion/Ioff | 587,951 | 3433.735 | 1333.333 | 2720 | 10,700 | 17,500 | 12,670 | 134,800 | 109,000 | 135,236 |

| SS (mV/dec) | 85 | 100 at 0.85 V | N/A | 92.3 at 0.85 V | N/A | N/A | N/A | N/A | 98.43 | 76.98 |

| DIBL (mV/V) | 77 | 100 | N/A | N/A | N/A | N/A | N/A | N/A | 71.2 | 68.57 |

| Ref | [52] | [53] | [54] | [55] | [56] | [57] | [58] | |||

| FDSOI | FDSOI (IRDS 2017) | FinFET | FinFET (IRDS 2020) | ||||||

|---|---|---|---|---|---|---|---|---|---|

| Node Range | “9/8” | “11/10” | “16/14” | “10” | “3” | “3” | “16/14” | “5” | “3” |

| Lg | 14 nm 1 | 18 nm | 25 nm | 20 nm | 12 nm 1 | 14 nm | 30 nm | 18 nm | 16 nm |

| Vth (V) | N/A | −0.2 | −0.3 | 0.190 | −0.28 | N/A | −0.24 | 0.222 | 0.237 |

| Ion(µA/µm) | 1014 at 1.0 V | 350 at 1.0 V | 550 at 0.9 V | >972 | 1500 at 0.6 V | N/A | 292 at 0.8 V | >854 | >912 |

| Ioff(nA/um) | 16 at 1.0 V | 100 at 1.0 V | 3 at 0.9 V | <10 | 10 at 0.6 V | N/A | 7.5 at 0.8 V | <10 | <10 |

| Ion/Ioff | 63,375 | 3500 | 183,333 | N/A | 150,000 | N/A | 38,933 | N/A | N/A |

| SS (mV/dec) | N/A | 75 at 1.0 V | 80 at 0.9 V | 68 | 70 at 0.6 V | 80 at 0.3 V | 72 at 0.8 V | 78 | 82 |

| DIBL (mV/V) | N/A | 75 | 85 | N/A | N/A | 75 | 50 | N/A | N/A |

| Ref | [59] | [60] | [61] | [62] | [63] | [64] | [65] | [66] | |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Mah, S.K.; Ker, P.J.; Ahmad, I.; Zainul Abidin, N.F.; Ali Gamel, M.M. A Feasible Alternative to FDSOI and FinFET: Optimization of W/La2O3/Si Planar PMOS with 14 nm Gate-Length. Materials 2021, 14, 5721. https://doi.org/10.3390/ma14195721

Mah SK, Ker PJ, Ahmad I, Zainul Abidin NF, Ali Gamel MM. A Feasible Alternative to FDSOI and FinFET: Optimization of W/La2O3/Si Planar PMOS with 14 nm Gate-Length. Materials. 2021; 14(19):5721. https://doi.org/10.3390/ma14195721

Chicago/Turabian StyleMah, Siew Kien, Pin Jern Ker, Ibrahim Ahmad, Noor Faizah Zainul Abidin, and Mansur Mohammed Ali Gamel. 2021. "A Feasible Alternative to FDSOI and FinFET: Optimization of W/La2O3/Si Planar PMOS with 14 nm Gate-Length" Materials 14, no. 19: 5721. https://doi.org/10.3390/ma14195721

APA StyleMah, S. K., Ker, P. J., Ahmad, I., Zainul Abidin, N. F., & Ali Gamel, M. M. (2021). A Feasible Alternative to FDSOI and FinFET: Optimization of W/La2O3/Si Planar PMOS with 14 nm Gate-Length. Materials, 14(19), 5721. https://doi.org/10.3390/ma14195721