Impact of Line Edge Roughness on ReRAM Uniformity and Scaling

Abstract

:1. Introduction

2. Modeling Methodology

2.1. Background of Modeling: LER Characterization in Different Lithography Techniques

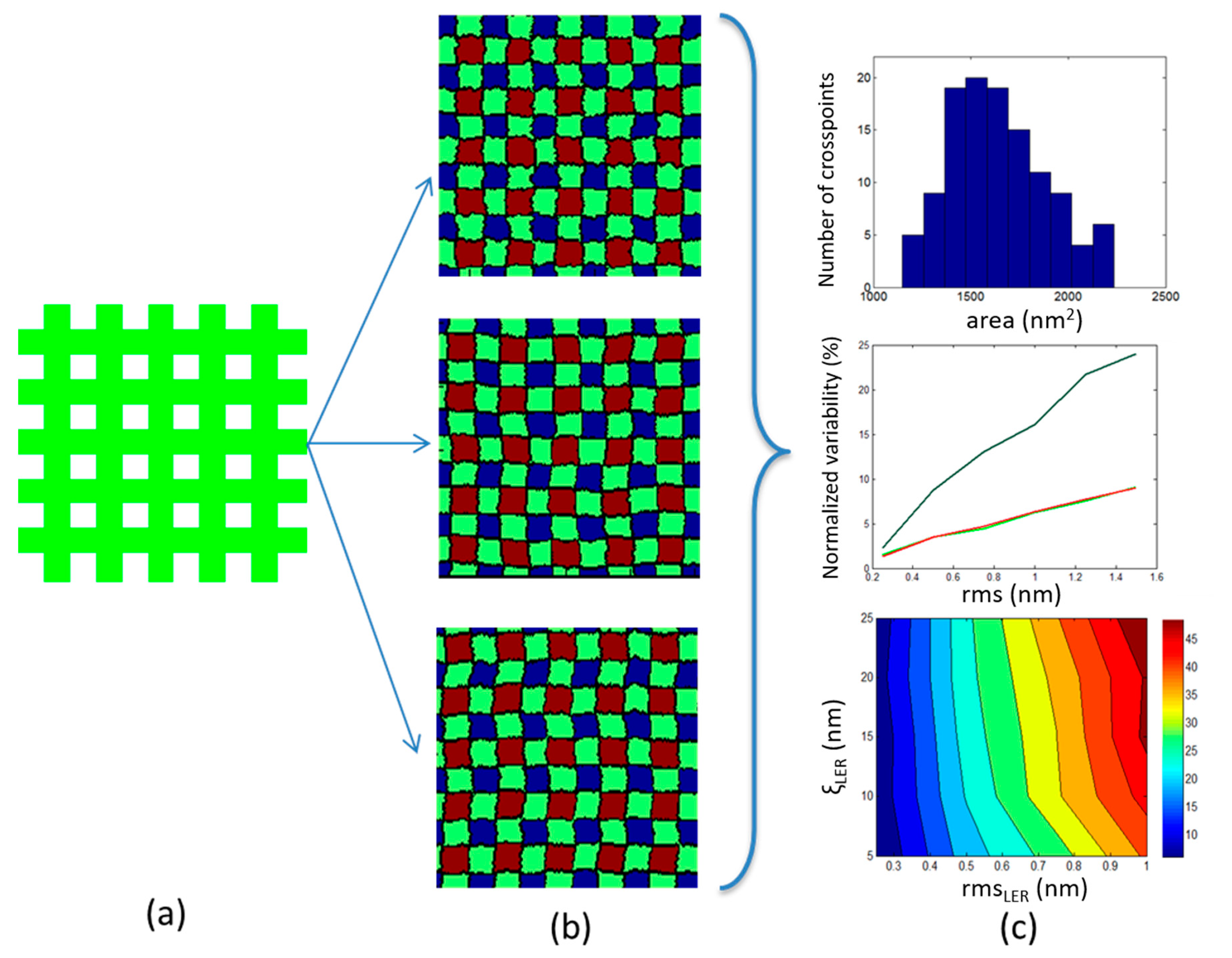

2.2. Implementation of Modeling

3. Results and Discussion

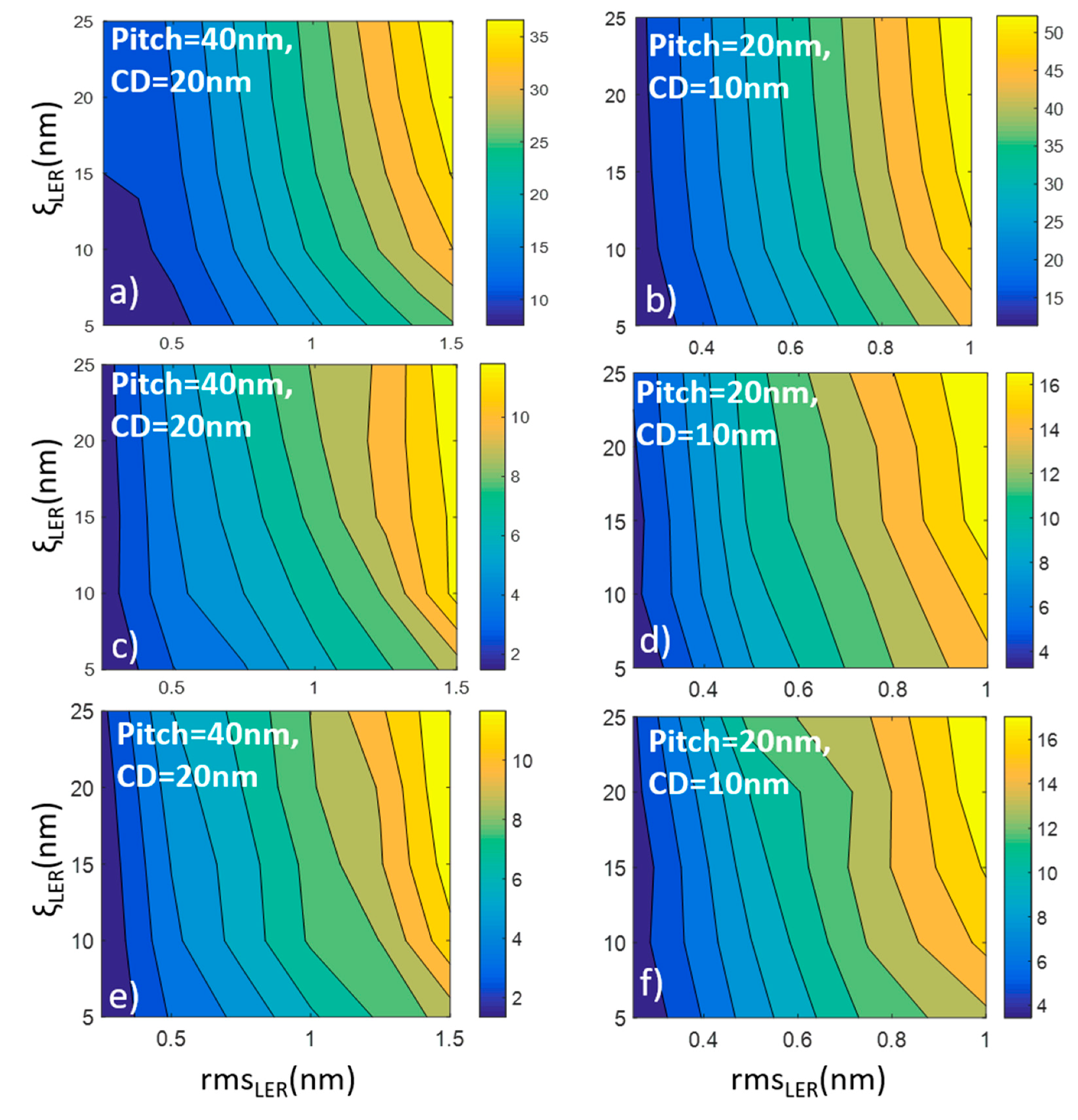

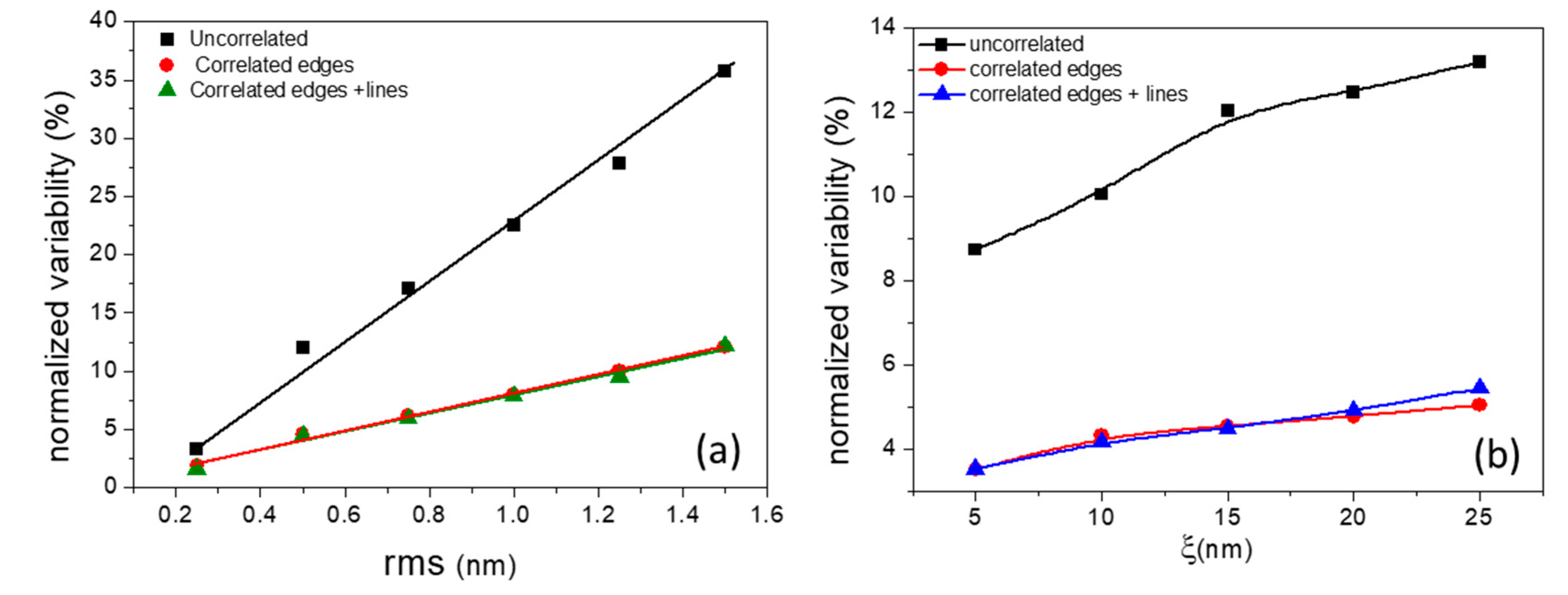

3.1. The Impact of LER Parameters Rms, ξ

3.2. The Impact of Scaling Device Size

3.3. The Impact of Edge and Line Correlations

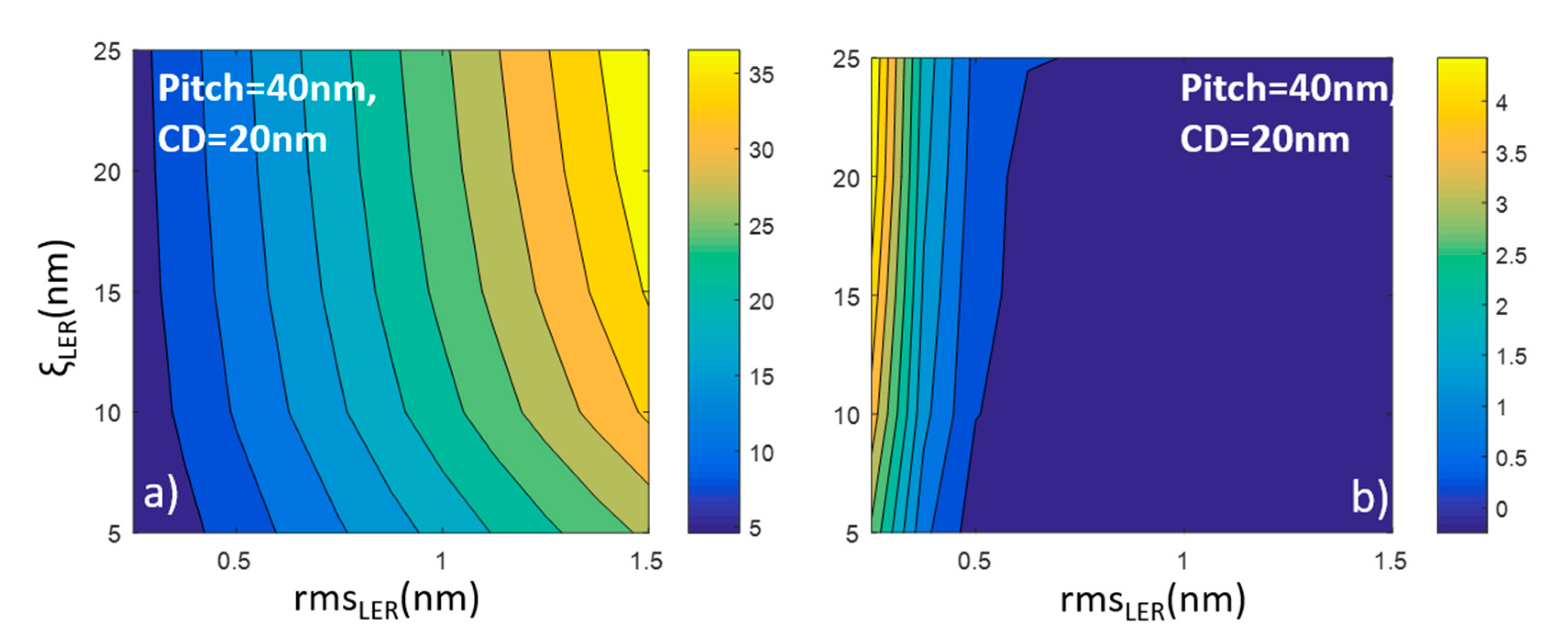

3.4. Analytical Formula for LER Effects on Area Variability

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Stathopoulos, S.; Khiat, A.; Trapatseli, M.; Cortese, S.; Serb, A.; Valov, I.; Prodromakis, T. Multibit memory operation of metal-oxide bi-layer memristors. Sci. Rep. 2017, 7, 17532. [Google Scholar] [CrossRef] [PubMed]

- Khiat, A.; Ayliffe, P.; Prodromakis, T. High Density Crossbar Arrays with Sub-15 nm Single Cells via Liftoff Process Only. Sci. Rep. 2016, 6, 32614. [Google Scholar] [CrossRef]

- Wu, H.; Yao, P.; Gao, B.; Wu, W.; Zhang, Q.; Zhang, W.; Deng, N.; Wu, D.; Wong, H.-S.P.; Yu, S.; et al. Device and circuit optimization of RRAM for Neuromorphic computing. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 11.5.1–11.5.4. [Google Scholar]

- Lv, H.; Xu, X.; Yuan, P.; Dong, D.; Gong, T.; Liu, J.; Yu, Z.; Huang, P.; Zhang, K.; Huo, C.; et al. BEOL Based RRAM with One Extra-mask for Low Cost, Highly Reliable Embedded Application in 28 nm Node and Beyond. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 2.4.1–2.4.4. [Google Scholar]

- Fujitsu Semiconductor Launches World’s Largest Density 4 Mbit ReRAM Product for Mass Production. 2016. Available online: https://phys.org/news/2016-10-fujitsu-semiconductor-world-largest-density.html (accessed on 10 December 2017).

- Govoreanu, B.; Kar, G.S.; Chen, Y.-Y.; Paraschiv, V.; Kubicek, S.; Fantini, A.; Radu, I.; Goux, L.; Clima, S.; Degraeve, R.; et al. 10 × 10 nm2 Hf/HfOx cross-point resistive RAM with excellent performance, reliability and low-energy operation. In Proceedings of the International Electron Devices Meeting, Washington, DC, USA, 5–7 December 2011; pp. 31.6.1–31.6.4. [Google Scholar] [CrossRef]

- Wedig, A.; Luebben, M.; Cho, D.-Y.; Moors, M.; Skaja, K.; Rana, V.; Hasegawa, T.; Adepalli, K.K.; Yildiz, B.; Waser, R.; et al. Nanoscale cation motion in TaOx, HfOx and TiOx memristive systems. Nat. Nanotechnol. 2016, 11, 67–74. [Google Scholar] [CrossRef] [PubMed]

- Luo, Q.; Xu, X.; Gong, T.; Lv, H.; Dong, D.; Ma, H.; Yuan, P.; Gao, J.; Liu, J.; Yu, Z.; et al. 8-layers 3D Vertical RRAM with Excellent Scalability towards Storage Class Memory Applications. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 2.7.1–2.7.4. [Google Scholar]

- Serb, A.; Bill, J.; Khiat, A.; Berdan, R.; Legenstein, R.; Prodromakis, T. Unsupervised learning in probabilistic neural networks with multi-state metal-oxide memristive synapses. Nat. Commun. 2016, 7, 12611. [Google Scholar] [CrossRef] [PubMed]

- Serb, A.; Khiat, A.; Prodromakis, T. Seamlessly Fused Digital-Analogue Reconfigurable Computing using Memristors. Nat. Commun. 2018, 9, 2170. [Google Scholar] [CrossRef]

- Chen, W.-H.; Lin, W.-J.; Lai, L.-Y.; Li, S.; Hsu, C.-H.; Lin, H.-T.; Lee, H.-Y.; Su, J.-W.; Xie, Y.; Sheu, S.-S.; et al. A 16Mb Dual-Mode ReRAM Macro with Sub-14ns Computing-In-Memory and Memory Functions Enabled by Self-Write Termination Scheme. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 28.2.1–28.2.4. [Google Scholar]

- Lübben, M.; Karakolis, P.; Ioannou-Sougleridis, V.; Normand, P.; Dimitrakis, P.; Valov, I. Graphene-Modified Interface Controls Transition from VCM to ECM Switching Modes in Ta/TaOx Based Memristive Devices. Adv. Mater. 2015, 27, 6202–6207. [Google Scholar] [CrossRef]

- Tsigkourakos, M.; Bousoulas, P.; Aslanidis, V.; Skotadis, E.; Tsoukalas, D. Ultra-Low Power Multilevel Switching with Enhanced Uniformity in Forming Free TiO2−x-Based RRAM with Embedded Pt Nanocrystals. Phys. Status Solidi (a) 2017, 214, 1700570. [Google Scholar] [CrossRef]

- Chen, A. Area and Thickness Scaling of Forming Voltage of Resistive Switching Memories. IEEE Trans. Electron Devices 2014, 35, 57–59. [Google Scholar] [CrossRef]

- Wong, H.-S.P.; Lee, H.-Y.; Yu, S.; Chen, Y.-S.; Wu, Y.; Chen, P.-S.; Lee, B.; Chen, F.T.; Tsai, M.-J. Metal Oxide ReRAM. Proc. IEEE 2012, 100, 1951–1970. [Google Scholar] [CrossRef]

- Fang, Z.; Li, X.; Wang, X.; Lo, P. Area Dependent Low Frequency Noise in Metal Oxide Based Resistive Random Access Memory. Int. J. Inf. Electron. Eng. 2012, 2, 882–884. [Google Scholar] [CrossRef]

- Lee, J.; Park, J.; Jung, S.; Hwang, H. Scaling Effect of Device Area and Film Thickness on Electrical and Reliability Characteristics of RRAM. In Proceedings of the IEEE International Interconnect Technology Conference and Materials for Advanced Metallization (IITC/MAM), Dresden, Germany, 8–12 May 2011. [Google Scholar] [CrossRef]

- Hayakawa, Y.; Himeno, A.; Yasuhara, R.; Boullart, W.; Vecchio, E.; Vandeweyer, T.; Witters, T.; Crotti, D.; Jurczak, M.; Fujii, S.; et al. Highly reliable TaOx ReRAM with centralized filament for 28-nm embedded application. In Proceedings of the Symposium on VLSI Technology Digest of Technical Papers, T14–T15, Kyoto, Japan, 17–19 June 2015. [Google Scholar] [CrossRef]

- Choi, B.J.; Chen, A.B.K.; Yang, X.; Chen, I.-W. Purely Electronic Switching with High Uniformity, Resistance Tunability, and Good Retention in Pt-Dispersed SiO2 Thin Films for ReRAM. Adv. Mater. 2011, 23, 3847–3852. [Google Scholar] [CrossRef]

- Guan, W.; Long, S.; Liu, Q.; Liu, M.; Wang, W. Nonpolar Nonvolatile Resistive Switching in Cu Doped ZrO2. IEEE Electron Device Lett. 2008, 29, 434–437. [Google Scholar] [CrossRef]

- Kim, M.; Choi, K.C. Transparent and flexible resistive random access memory based on Al2O3 film with multilayer electrodes. IEEE Trans. Electron Devices 2017, 64, 3508–3510. [Google Scholar] [CrossRef]

- Yoon, K.J.; Kim, G.H.; Yoo, S.; Bae, W.; Yoon, J.H.; Park, T.H.; Kwon, D.E.; Kwon, Y.J.; Kim, H.J.; Kim, Y.M.; et al. Double-Layer-Stacked One Diode-One Resistive Switching Memory Cross-point Array with an Extremely High Rectification Ratio of 109. Adv. Electron. Mater. 2017, 3, 1700152. [Google Scholar] [CrossRef]

- Sawa, A. Resistive switching in transition metal oxides. Mater. Today 2008, 11, 28–36. [Google Scholar] [CrossRef]

- Kim, H.-D.; An, H.-M.; Lee, E.B.; Kim, T.G. Stable Bipolar Resistive Switching Characteristics and Resistive Switching Mechanisms Observed in Aluminum Nitride-based ReRAM Devices. IEEE Trans. Electron Devices 2011, 58, 3566–3573. [Google Scholar] [CrossRef]

- Kim, H.-D.; Yun, M.J.; Hong, S.M.; Kim, T.G. Size-dependent resistive switching properties of the active region in nickel nitride-based crossbar array resistive random access memory. J. Nanosci. Nanotechnol. 2014, 14, 9088–9091. [Google Scholar] [CrossRef]

- Constantoudis, V.; Gogolides, E.; Patsis, G.P. Sidewall roughness in nanolithography: Origins, metrology and device effects, Nanolithography. In The Art of Fabricating Nanoelectronic and Nanophotonic Devices and Systems; Feldman, M.E., Ed.; Woodhead publishing: Cambridge, UK, 2013; pp. 503–537. [Google Scholar]

- Xiong, S.; Bokor, J. A Simulation Study of Gate Line Edge Roughness Effects on Doping Profiles of Short-Channel MOSFET Devices. IEEE Trans. Electron Devices 2004, 51, 228–232. [Google Scholar] [CrossRef]

- Shibata, K.; Izumi, N.; Tsujita, K. Influence of line-edge roughness on MOSFET devices with sub-50-nm gates. Microlithography 2004, 5375, 865–873. [Google Scholar] [CrossRef]

- Kaya, S.; Brown, A.R.; Asenov, A.; Magot, D.; LintonI, T. Analysis of Statistical Fluctuations due to Line Edge Roughness in sub-0.1μm MOSFETs. In Simulation of Semiconductor Processes and Devices 2001; Springer Science and Business Media LL: Berlin, Germany, 2001; pp. 78–81. [Google Scholar]

- Son, D.; Ko, K.; Woo, C.; Kang, M.; Shin, H. Line Edge Roughness and Process Variation Effect of Three Stacked Gate-All-Around Silicon MOSFET Devices. J. Nanosci. Nanotechnol. 2017, 17, 7130–7133. [Google Scholar] [CrossRef]

- Baraveli, E.; Jurczak, M.; Speciale, N.; De Meyer, K.; Dixit, A. Impact of LER and Random Dopant Fluctuations on FinFET Matching Performance. IEEE Trans. Nanotechnol. 2008, 7, 291–298. [Google Scholar] [CrossRef]

- Patel, K.; Liu, T.-J.K.; Spanos, C.J. Gate Line Edge Roughness Model for Estimation of FinFET Performance Variability. IEEE Trans. Electron Devices 2009, 56, 3055–3063. [Google Scholar] [CrossRef]

- Constantoudis, V.; Papavieros, G.; Gogolides, E.; Pret, A.V.; Pathangi, H.; Gronheid, R. Challenges in line edge roughness metrology in directed self-assembly lithography: placement errors and cross-line correlations. J. Micro/Nanolithogr. MEMS MOEMS 2017, 16, 24001. [Google Scholar] [CrossRef]

- Constantoudis, V.; Gogolides, E.; Roberts, J.; Stowers, J.K. Characterization and modeling of line width roughness (LWR). Microlithography 2005, 5752, 1227–1237. [Google Scholar]

- Mack, C.A. Generating random rough edges, surfaces, and volumes. Appl. Opt. 2013, 52, 1472–1480. [Google Scholar] [CrossRef] [PubMed]

- Constantoudis, V.; Patsis, G.P.; Leunissen, L.H.A.; Gogolides, E. Line edge roughness and critical dimension variation: Fractal characterization and comparison using model functions. J. Vac. Sci. Technol. B Microelectron. Nanometer Struct. 2004, 22, 1974. [Google Scholar] [CrossRef]

- Constantoudis, V.; Kokkoris, G.; Gogolides, E.; Pargon, E.; Martin, M. Effects of resist sidewall morphology on line-edge roughness reduction and transfer during etching: is the resist sidewall after development isotropic or anisotropic? J. Micro/Nanolithogr. MEMS MOEMS 2010, 9, 41209. [Google Scholar] [CrossRef]

- Palasantzas, G.; Krim, J. Effect of the form of the height-height correlation function on diffuse x-ray scattering from a self-affine surface. Phys. Rev. B 1993, 48, 2873–2877. [Google Scholar] [CrossRef]

- 2013 ITRS-International Technology Roadmap for Semiconductors. Available online: http://www.itrs2.net/2013-itrs.html (accessed on 10 December 2017).

- Papavieros, G.; Constantoudis, V. Line edge roughness measurement through SEM images: Effects of image digitization and their mitigation. Proc. SPIE 2017, 10446. [Google Scholar] [CrossRef]

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Constantoudis, V.; Papavieros, G.; Karakolis, P.; Khiat, A.; Prodromakis, T.; Dimitrakis, P. Impact of Line Edge Roughness on ReRAM Uniformity and Scaling. Materials 2019, 12, 3972. https://doi.org/10.3390/ma12233972

Constantoudis V, Papavieros G, Karakolis P, Khiat A, Prodromakis T, Dimitrakis P. Impact of Line Edge Roughness on ReRAM Uniformity and Scaling. Materials. 2019; 12(23):3972. https://doi.org/10.3390/ma12233972

Chicago/Turabian StyleConstantoudis, Vassilios, George Papavieros, Panagiotis Karakolis, Ali Khiat, Themistoklis Prodromakis, and Panagiotis Dimitrakis. 2019. "Impact of Line Edge Roughness on ReRAM Uniformity and Scaling" Materials 12, no. 23: 3972. https://doi.org/10.3390/ma12233972

APA StyleConstantoudis, V., Papavieros, G., Karakolis, P., Khiat, A., Prodromakis, T., & Dimitrakis, P. (2019). Impact of Line Edge Roughness on ReRAM Uniformity and Scaling. Materials, 12(23), 3972. https://doi.org/10.3390/ma12233972