Enhanced Electrical Properties of Atomic Layer Deposited LaxAlyO Thin Films with Stress Relieved Preoxide Pretreatment

Abstract

1. Introduction

2. Experimental

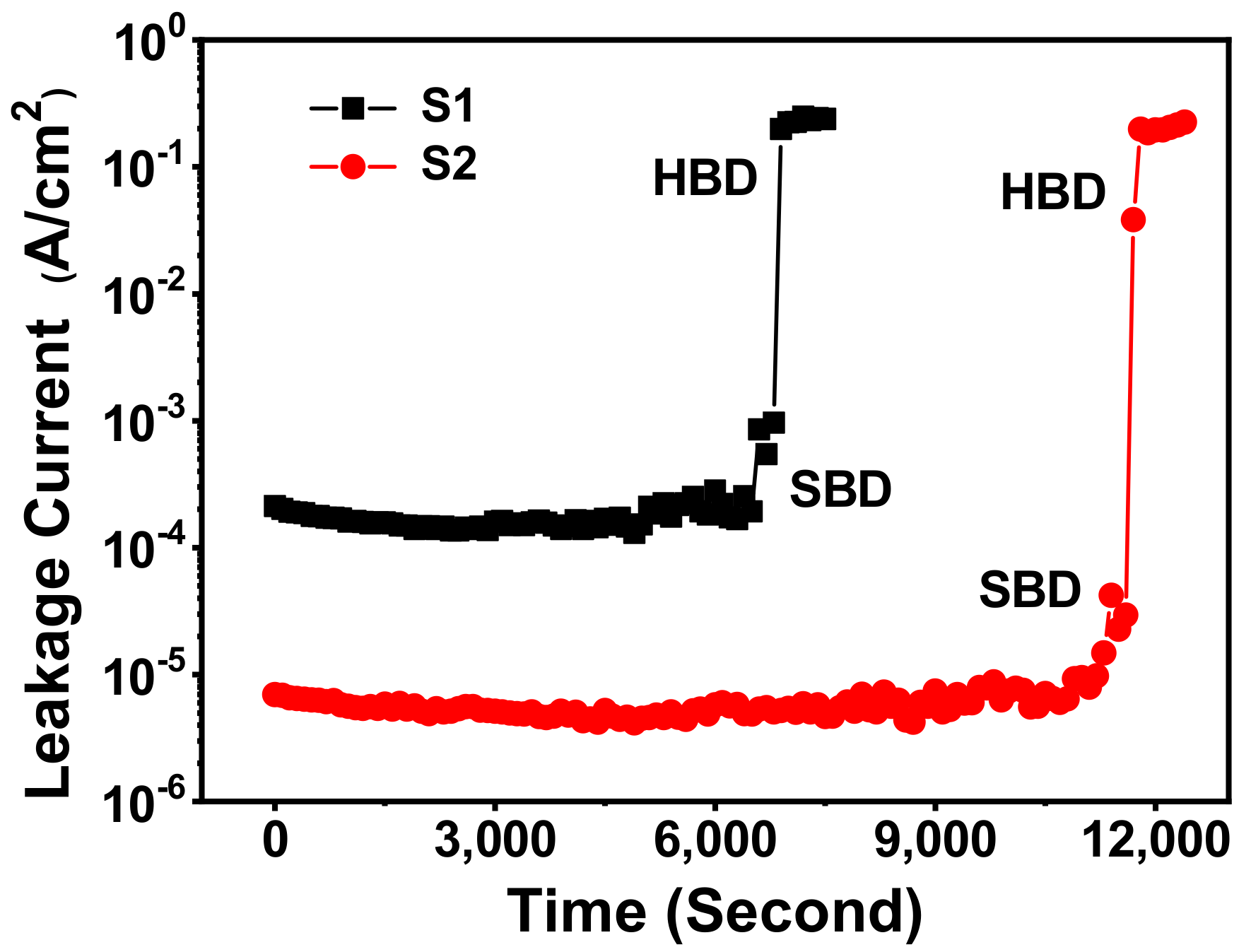

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Ieong, M.; Narayanan, V.; Singh, D.; Topol, A.; Chan, V.; Ren, Z. Transistor scaling with novel materials. Mater. Today 2006, 9, 26–31. [Google Scholar] [CrossRef]

- He, G.; Sun, Z.Q.; Li, G.; Zhang, L.D. Review and perspective of Hf-based high-k gate dielectrics on silicon. Crit. Rev. Solid State Mater. Sci. 2012, 37, 131–157. [Google Scholar] [CrossRef]

- Robertson, J.; Wallace, R.M. High-k materials and metal gates for CMOS applications. Mater. Sci. Eng. R Rep. 2015, 88, 1–41. [Google Scholar] [CrossRef]

- Li, X.; Yajima, T.; Nishimura, T.; Toriumi, A. Study of Si kinetics in interfacial SiO2 scavenging in HfO2 gate stacks. Appl. Phys. Express 2015, 8, 061304. [Google Scholar] [CrossRef]

- Deng, J.; Cheng, J.; Chen, X.B. An improved SOI p-channel LDMOS with high-k gate dielectric and dual hole-conductive paths. IEEE Electron Device Lett. 2017, 38, 1712–1715. [Google Scholar] [CrossRef]

- Mistry, K.; Allen, C.; Auth, C.; Beattie, B.; Bergstrom, D.; Bost, M.; Brazier, M.; Buehler, M.; Cappellani, A.; Chau, R.; et al. A 45 nm logic technology with high-k+metal gate transistors, strained silicon, 9 Cu interconnect layers, 193 nm dry patterning, and 100% Pb-free packaging. In Proceedings of the 2007 IEEE International Electron Devices Meeting, Washington, DC, USA, 10–12 December 2007; pp. 247–250. [Google Scholar]

- Pelloquin, S.; Saint-Girons, G.; Baboux, N.; Albertini, D.; Hourani, W.; Penuelas, J.; Grenet, G.; Plossu, C.; Hollinger, G. LaAlO3/Si capacitors: Comparison of different molecular beam deposition conditions and their impact on electrical properties. J. Appl. Phys. 2013, 113, 034106. [Google Scholar] [CrossRef]

- Breckenfeld, E.; Wilson, R.B.; Martin, L.W. Effect of growth induced (non)stoichiometry on the thermal conductivity, permittivity, and dielectric loss of LaAlO3 films. Appl. Phys. Lett. 2013, 103, 082901. [Google Scholar] [CrossRef]

- Couso, C.; Porti, M.; Martin-Martinez, J.; Garcia-Loureiro, A.J.; Seoane, N.; Nafria, M. Local defect density in polycrystalline high-k dielectrics cafm-based evaluation methodology and impact on MOSFET variability. IEEE Electron Device Lett. 2017, 38, 637–640. [Google Scholar] [CrossRef]

- Suzuki, M. Comprehensive study of lanthanum aluminate high-dielectric-constant gate oxides for advanced CMOS devices. Materials 2012, 5, 443–477. [Google Scholar] [CrossRef] [PubMed]

- Cerbu, F.; Madia, O.; Andreev, D.V.; Fadida, S.; Eizenberg, M.; Breuil, L.; Lisoni, J.G.; Kittl, J.A.; Strand, J.; Shluger, A.L.; et al. Intrinsic electron traps in atomic-layer deposited HfO2 insulators. Appl. Phys. Lett. 2016, 108, 222901. [Google Scholar] [CrossRef]

- Tseng, H.H.; Tobin, P.J.; Kalpat, S.; Schaeffer, J.K.; Ramón, M.E.; Fonseca, L.R.C.; Jiang, Z.X.; Hegde, R.I.; Triyoso, D.H.; Semavedam, S. Defect passivation with fluorine and interface engineering for Hf-based high-k metal gate stack device reliability and performance enhancement. IEEE Trans. Electron Device 2007, 54, 3267–3275. [Google Scholar] [CrossRef]

- Clik-Butler, Z.; Devireddy, S.P.; Tseng, H.H.; Tobin, P.; Zlotnicka, A. A low-frequency noise model for advanced gate-stack MOSFETs. Microelectron. Reliab. 2009, 49, 103–112. [Google Scholar] [CrossRef]

- Li, F.; Tseng, H.H.; Register, L.F.; Tobin, P.J.; Banerjee, S.K. Asymmetry in Gate Capacitance-Voltage (C-V) Behavior of ultrathin metal gate MOSFETs with HfO2 gate dielectrics. IEEE Trans. Electron Devices 2006, 53, 1943–1946. [Google Scholar] [CrossRef]

- Schaefer, A.; Zielasek, V.; Schmidt, T.; Sandell, A.; Schowalter, M.; Seifarth, O.; Walle, L.E.; Schulz, C.; Wollschläger, J.; Schroeder, T.; et al. Growth of praseodymium oxide on Si(111) under oxygen-deficient conditions. Phys. Rev. B 2009, 80, 045414. [Google Scholar] [CrossRef]

- Johnson, R.W.; Hultqvist, A.; Bent, S.F. A brief review of atomic layer deposition from fundamentals to applications. Mater. Today 2014, 17, 236–246. [Google Scholar] [CrossRef]

- Xiong, Y.H.; Tu, H.L.; Du, J.; Wei, F.; Zhang, X.Q.; Yang, M.M.; Zhao, H.B.; Chen, D.P.; Wang, W.W. Epitaxial growth and electrical properties of ultrathin La2Hf2O7 high-k gate dielectric films. Appl. Surf. Sci. 2013, 283, 554–558. [Google Scholar] [CrossRef]

- Kim, J.; Kim, H.C.; Wallace, R.M.; Park, T.J. In-Situ XPS Study on ALD (Atomic Layer Deposition) of High-k Dielectrics La2O3 using La-formidinate and Ozone. ECS Trans. 2012, 45, 95–101. [Google Scholar] [CrossRef]

- Gao, L.G.; Yin, K.B.; Chen, L.; Guo, H.X.; Xia, Y.D.; Yin, J.; Liu, Z.G. The effect of Si surface nitridation on the interfacial structure and electrical properties of (La2O3)0.5(SiO2)0.5 high-k gate dielectric films. Appl. Surf. Sci. 2009, 256, 90–95. [Google Scholar] [CrossRef]

- Hauser, J.R.; Ahmed, K. Characterization of ultra-thin oxides using electrical C-V and I-V measurements. AIP Conf. Proc. 1998, 449, 235–239. [Google Scholar]

- Kim, H.; Woo, S.; Lee, J.; Kim, H.; Kim, Y.; Lee, H.; Jeon, H. The Effects of Annealing Ambient on the Characteristics of La2O3 Films Deposited by RPALD. J. Electrochem. Soc. 2010, 157, H479–H482. [Google Scholar] [CrossRef]

- Neamen, D.A. Semiconductor Physics and Devices, 3rd ed.; McGraw-Hill: New York, NY, USA, 2003; p. 328. [Google Scholar]

- Shekhter, P.; Chaudhuri, A.R.; Laha, A.; Yehezkel, S.; Shriki, A.; Osten, H.J.; Eizenberg, M. The influence of carbon doping on the performance of Gd2O3 as high-k gate dielectric. Appl. Phys. Lett. 2014, 105, 262901. [Google Scholar] [CrossRef]

- Kang, H.S.; Reddy, M.S.P.; Kim, D.S.; Kim, K.W.; Ha, J.B.; Lee, Y.S.; Choi, H.C.; Lee, J.H. Effect of oxygen species on the positive flat-band voltage shift in Al2O3/GaN metal-insulator-semiconductor capacitors with post-deposition annealing. J. Phys. D Appl. Phys. 2013, 46, 155101. [Google Scholar] [CrossRef]

- Daus, A.; Vogt, C.; Münzenrieder, N.; Petti, L.; Knobelspies, S.; Cantarella, G.; Luisier, M.; Salvatore, G.A.; Tröster, G. Positive charge trapping phenomenon in n-channel thin-film transistors with amorphous alumina gate insulators. J. Appl. Phys. 2016, 120, 244501. [Google Scholar] [CrossRef]

- Sze, S.M.; Ng, K.K. Physics of Semiconductor Devices, 3rd ed.; John Wiley & Sons, Inc.: Hoboken, NJ, USA, 2006; p. 225. [Google Scholar]

- Nicollian, E.H.; Brews, J.R. MOS Physics and Technology; John Wiley & Sons, Inc.: New York, NY, USA, 1982; p. 223. [Google Scholar]

- Sahu, B.S.; Ahn, J.K.; Xian, C.J.; Yoon, S.G.; Srivastava, P. Experimental investigation of interfacial and electrical properties of post-deposition annealed Bi2Mg2/3Nb4/3O7 (BMN) dielectric filmson silicon. J. Phys. D Appl. Phys. 2008, 41, 135311. [Google Scholar] [CrossRef]

- Hill, W.A.; Coleman, C.C. A single-frequency approximation for interface-state density determination. Solid State Electron. 1980, 23, 987–993. [Google Scholar] [CrossRef]

- Spahr, H.; Bülow, T.; Nowak, C.; Hirschberg, F.; Reinker, J.; Hamwi, S.; Johannes, H.H.; Kowalsky, W. Impact of morphological defects on the electrical breakdown of ultra thin atomic layer deposition processed Al2O3 layers. Thin Solid Films 2013, 534, 172–176. [Google Scholar] [CrossRef]

- Jinesh, K.B.; Klootwijk, J.H.; Lamy, Y.; Wolters, R.; Tois, E.; Tuominen, M.; Roozeboom, F.; Besling, W.F.A. Enhanced electrical properties of atomic layer deposited La2O3 thin films with embedded ZrO2 nanocrystals. Appl. Phys. Lett. 2008, 93, 172904. [Google Scholar] [CrossRef]

- Ho, C.H.; Kim, S.Y.; Roy, K. Ultra-thin dielectric breakdown in devices and circuits: A brief review. Microelectron. Reliab. 2015, 55, 308–317. [Google Scholar] [CrossRef]

- Hassan, M.K.; Roy, K. Investigation of dependence between time-zero and time-dependent variability in high-k NMOS transistors. Microelectron. Reliab. 2017, 70, 22–31. [Google Scholar] [CrossRef]

- Hsieh, E.R.; Chung, S.S. The understanding on the evolution of stress-induced gate leakage in high-k dielectric metal-oxide-field-effect transistor by random-telegraph-noise measurement. Appl. Phys. Lett. 2015, 107, 243506. [Google Scholar] [CrossRef]

- Chu, C.M.; Lin, Y.C.; Lee, W.I.; Dee, C.F.; Wong, Y.Y.; Majlis, B.Y.; Salleh, M.M.; Yap, S.L.; Chang, E.Y. Reliability study of high-k La2O3/HfO2 and HfO2/La2O3 stacking layers on n-In0.53Ga0.47As metal-oxide-semiconductor capacitor. Appl. Phys. Express 2016, 9, 021203. [Google Scholar] [CrossRef]

- Okada, K.; Kurimoto, K.; Suzuki, M. Anomalous TDDB statistics of gate dielectrics caused by charging-induced dynamic stress relaxation under constant-voltage stress. IEEE Trans. Electron Devices 2016, 63, 2268–2274. [Google Scholar] [CrossRef]

| Process Step | Average Thickness (nm) | 95% Confidence Interval (nm) |

|---|---|---|

| Pre-RCA cleaning | 2.31 | (2.211, 2.409) |

| Post-RCA cleaning | 0.67 | (0.596, 0.744) |

| Post-thermal oxidation | 4.04 | (3.764, 4.316) |

| Post-diluted HF solution dipping | 0.65 | (0.537, 0.763) |

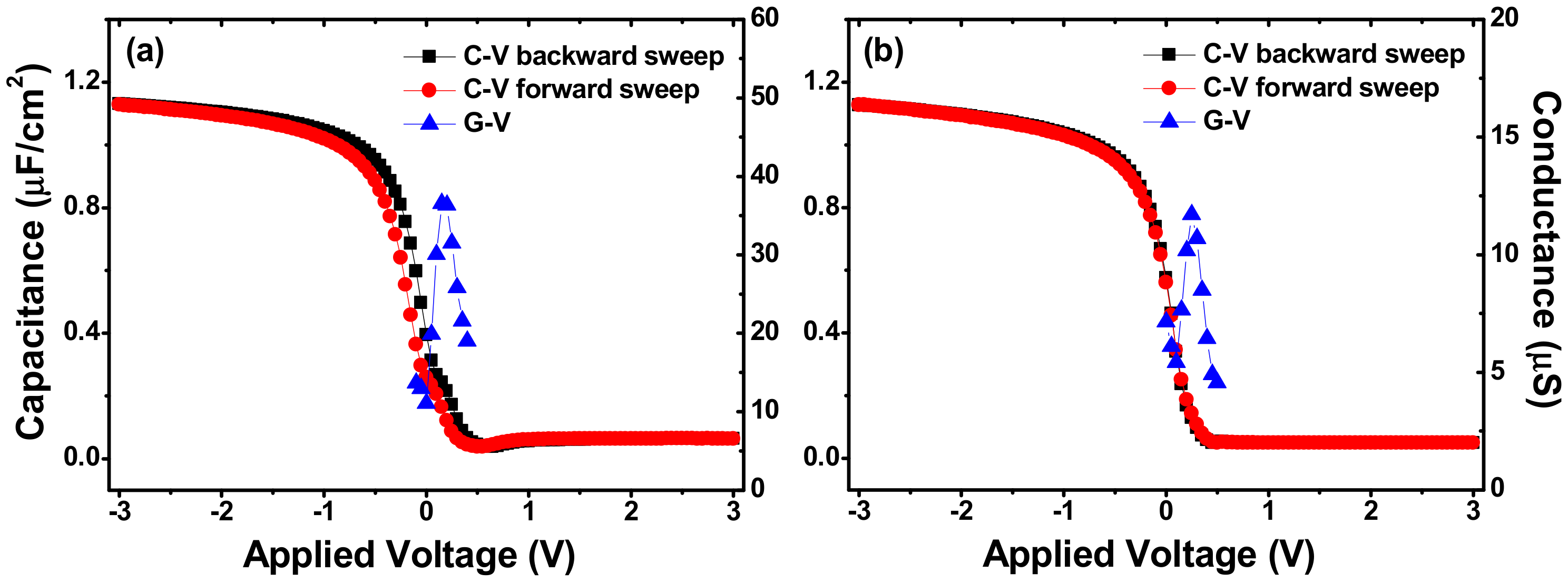

| Sample | Cox (μF/cm2) | VFB (V) Backward | ΔVFB (V) | Not (cm−2) | Dit (eV−1 cm−2) |

|---|---|---|---|---|---|

| S1 | 1.18 | 0.005 | 0.131 | 9.65 × 1011 | 1.62 × 1012 |

| S2 | 1.13 | 0.142 | 0.015 | 1.06 × 1011 | 4.19 × 1011 |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, X.; Liu, H.; Zhao, L.; Wang, Y. Enhanced Electrical Properties of Atomic Layer Deposited LaxAlyO Thin Films with Stress Relieved Preoxide Pretreatment. Materials 2018, 11, 1601. https://doi.org/10.3390/ma11091601

Wang X, Liu H, Zhao L, Wang Y. Enhanced Electrical Properties of Atomic Layer Deposited LaxAlyO Thin Films with Stress Relieved Preoxide Pretreatment. Materials. 2018; 11(9):1601. https://doi.org/10.3390/ma11091601

Chicago/Turabian StyleWang, Xing, Hongxia Liu, Lu Zhao, and Yongte Wang. 2018. "Enhanced Electrical Properties of Atomic Layer Deposited LaxAlyO Thin Films with Stress Relieved Preoxide Pretreatment" Materials 11, no. 9: 1601. https://doi.org/10.3390/ma11091601

APA StyleWang, X., Liu, H., Zhao, L., & Wang, Y. (2018). Enhanced Electrical Properties of Atomic Layer Deposited LaxAlyO Thin Films with Stress Relieved Preoxide Pretreatment. Materials, 11(9), 1601. https://doi.org/10.3390/ma11091601