1. Introduction

Traditional distribution networks are constrained by planned capacity and topology. In scenarios with a high proportion of large-scale distributed generation (DG) access, due to the fluctuation of DG output and insufficient absorption capacity at the distribution network voltage level, excess power needs to be transmitted to the higher-level grid. It is prone to problems such as reverse overloading of distribution transformers and overvoltage at nodes [

1,

2,

3]. Building an intelligent, flexible, and reliable distribution network and creating an intelligent regulated power supply network framework have become urgent problems to be solved at present [

4,

5,

6,

7,

8].

In modern power system, the unified power flow controller (UPFC) [

9,

10,

11,

12,

13], as one of the core devices of a flexible AC transmission system, has been applied on a large scale in the transmission field with its fast dynamic response characteristics and all-around power flow regulation capabilities, and has achieved remarkable results. It has demonstrated strong capabilities in flexible power flow control and has a significant optimization effect on power quality. The UPFC also has great application potential in distribution network scenarios. When applied to distribution network scenarios, it can effectively reduce the risk of inrush current during distribution loop closure operations, avoid power supply interruption caused by “power-off switching” during maintenance operations, optimize line load distribution to improve operational economy, and provide key technical support for flexible interconnection of distribution networks [

14,

15,

16]. In weak networks with high PV penetration, the coordination of UPFC with PV inverters and energy storage systems has become a key direction to mitigate voltage fluctuations and fault risks, but existing research rarely integrates such coordination requirements into UPFC fault protection design [

17].

However, the existing UPFC-related research mostly focuses on the field of transmission grids, with the core directions concentrating on device topology innovation, power flow control strategy optimization, and mathematical modeling analysis [

18,

19,

20]. Reference [

21] established a coordinated optimization planning model for transmission networks, including energy storage devices and UPFCs, and verified through case studies that the proposed indicators could quantitatively reflect the dynamic changes of network transmission. Regarding fault protection, it also focuses on UPFC body fault ride-through. Reference [

22] proposes a UPFC series unit restart strategy based on fault identification to improve fault ride-through capability. Reference [

23] designs protection for a single fault type in specific topologies such as modular multilevel converters (MMCs), such as open-circuit and control pulse loss. Reference [

24] analyzed the topology and working principle of MMC-UPFC and investigated the operational characteristics in the case of single-phase ground fault and two-phase short-circuit fault.

It can be seen that the current research direction is mainly focused on how the device achieves rapid fault ride-through after the fault occurs. Meanwhile, the proposed methods, in terms of fault protection methods, only target a single overvoltage or overcurrent fault and cannot simultaneously meet the requirements for monitoring and protecting multiple types of faults. Among the existing fault protection methods, the protection scenarios discussed are all in high-voltage and ultra-high-voltage transmission fields, and there is a lack of research in distribution protection scenarios.

To address these research gaps, this paper designs a fault protection device for D-UPFC, which takes the distribution thyristor bypass switch (D-TBS) as the core and is supplemented by a cooperative control system. At the same time, a three-level linkage protection strategy of the main controller, thyristor controller, and thyristor control unit (TCU) is proposed, aiming to quickly bypass the low-voltage converters when the high-voltage primary side system fails, to achieve reliable isolation and protection of the main equipment of the D-UPFC and to lay the foundation for the engineering application of the D-UPFC.

2. Principle of the Fault Protection Device

Figure 1 shows the topology of a medium-voltage flexible interconnect system based on a D-UPFC. This set of the flexible system includes the parallel transformer T1, the series transformer T2 and the low-voltage converter, which are connected to the 10 kV line to achieve flexible interconnection between the two transformer areas. The output end of the low-voltage converter is connected to the high-voltage AC system via the series transformer. When a short-circuit fault occurs in the high-voltage system, the system short-circuit current is conducted to the low-voltage side through the coupling effect of the transformer, thereby causing severe overvoltage and overcurrent conditions on the low-voltage side. In view of this, protective measures must be taken for the converter to prevent it from being damaged.

In the traditional UPFC protection system, mechanical bypass switches, metal oxide arresters, and thyristor bypass switches are usually connected in parallel on the secondary side of the series transformer. The thyristor bypass switch works in conjunction with the mechanical bypass switch to transfer the fault current [

25,

26]. However, in distribution network scenarios, once a short-circuit fault occurs in the system, the D-UPFC often disconnects directly. A fault protection device for D-UPFCs, D-TBS, has been developed, taking into account the economy and the strict requirements for device size. This device innovatively replaces the traditional mechanical bypass switch, metal oxide arrester, and TBS functions. The device volume can be reduced to 20–30% of traditional applications, and costs are lowered by over one-third. It directly coordinates with the circuit breaker on the primary side of the series transformer, enabling efficient and reliable system protection, thereby improving system stability and safety under fault conditions.

The D-TBS protection strategy must fulfill the following requirements: fast system response speed, high and low-voltage side control coordination, consistent fault clearance across all phases, and correct response and simultaneous triggering of the three-phase protection devices on the low-voltage side when multiple types of faults occur on the high-voltage side of the system. A double sampling method is employed to ensure high reliability. Fault current and fault voltage can be sampled simultaneously on the secondary side of the serial transformer.

The basic topology of the D-TBS is composed of three anti-parallel thyristors connected in a triangular pattern, and this structure is installed in parallel between the D-UPFC series transformer and the converter. To achieve rapid and accurate protection, three levels of control protection detection devices are set up: the main control level, the valve control level, and the thyristor level.

The control protection of the master level is integrated with the master control device of the D-UPFC to achieve a state detection summary in non-fault conditions and coordinated action with other protection devices in case of fault.

The valve-regulated stage control and protection device realizes the unified pulse distribution of each thyristor control unit (TCU) within the topology and the secondary side current monitoring of the D-UPFC series transformer. As shown in

Figure 2, the system mainly consists of the upper computer data interaction module, overcurrent fault-monitoring and protection module, power supply module, FPGA, and TCU device-monitoring and triggering module. Among them, the upper computer data interaction module has three uplink 50 MHz optical communication channels, which are used to conduct information interaction with the main controller and also transmit the main control information to the FPGA inside the controller to achieve interaction between the two. The overcurrent fault-monitoring and protection module has three analog channel interfaces connected to three hall current sensors to measure the three-phase current in real time and to cause the sampling results to interact with the FPGA inside the controller; The function of the power module is to supply stable voltage and current to all other parts of the system. The TCU device-monitoring and triggering module has six pairs of downlink 5 MHz fiber control channels, each corresponding to three anti-parallel thyristor TCUs. It achieves real-time triggering control and status feedback of the TCUs based on established logic requirements and also interacts with the FPGA.

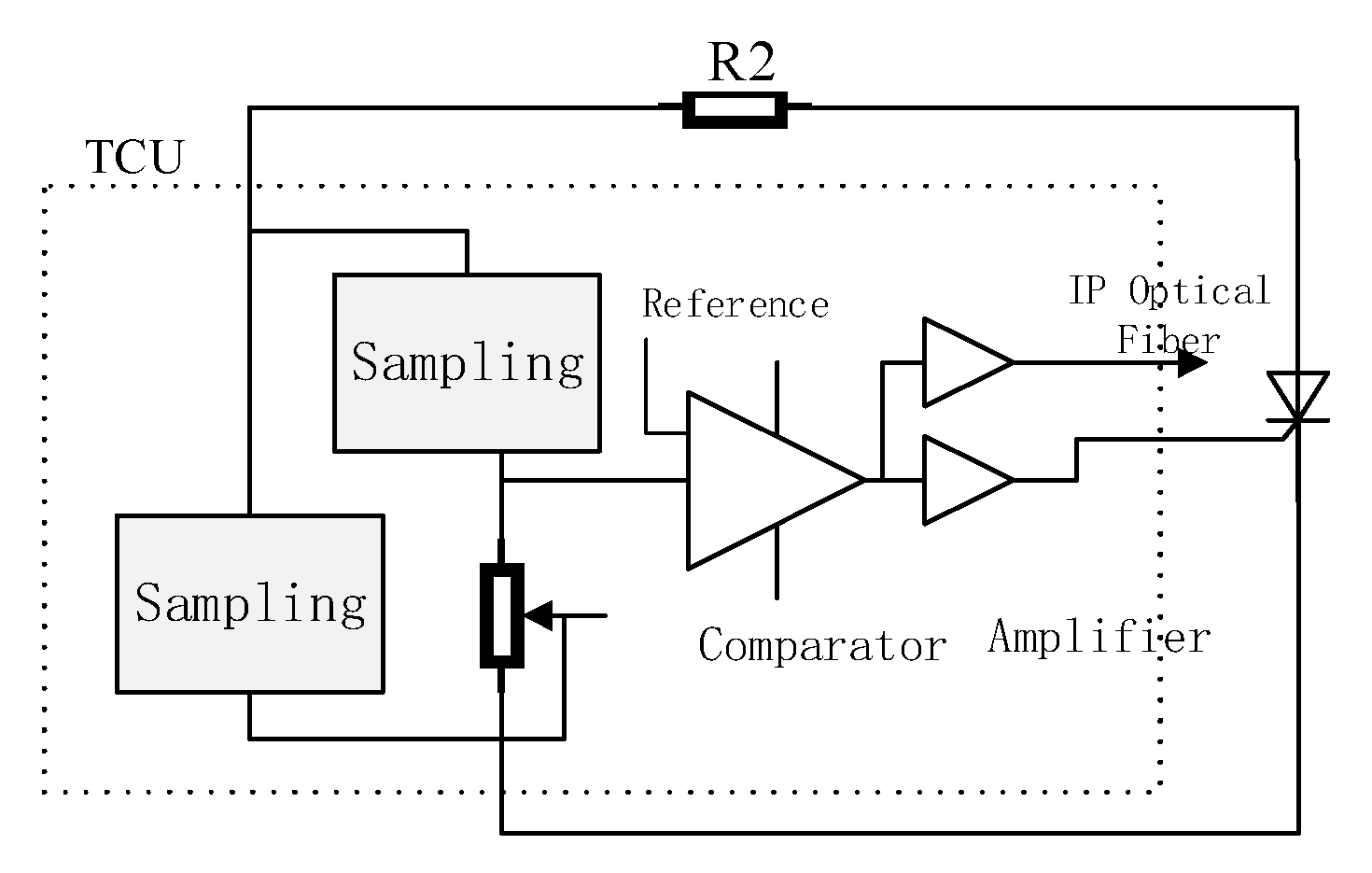

The thyristor-level control device directly performs control and protection monitoring on the thyristors, including the TCU corresponding to each thyristor, as well as the energy retrieval circuit and overvoltage-monitoring circuit that maintain the normal operation of the TCU. The principle of the TCU is shown in

Figure 3, which covers the self-energy-harvesting module, voltage stabilization module, self-energy-harvesting voltage-monitoring module, overvoltage fault-monitoring module, electro-optic/photoelectric conversion module, and trigger module. The self-harvesting module achieves wideband wide-voltage harvesting by combining with an external energy-harvesting RC circuit. The voltage regulator is responsible for stabilizing the voltage output by the self-powered module, and after the voltage regulator operation is completed, it supplies power to the other logic modules and trigger modules. The main function of the self-powered voltage-monitoring module is to monitor the power voltage and, through the electro-optical conversion module, transmit the current power status information of the TCU to the D-TBS. The overvoltage fault-monitoring module monitors the secondary voltage of the D-UPFC series transformer through the thyristor voltage equalization circuit and makes an overvoltage judgment, and then transmits the judgment result through the electro-optical conversion module to the D-TBS and the TCU trigger module. The trigger module receives the trigger command through the photoelectric conversion module and then triggers the thyristor.

Meanwhile, after the D-TBS operates, system recovery is not an automatic reset process but rather requires careful manual intervention. The general procedure is as follows: First, system-level protection isolates the fault zone, and maintenance personnel must confirm that the primary-side fault has been completely cleared. Next, a status check is performed via the monitoring system for all modules of the D-UPFC, the D-TBS itself, and the relevant circuit breakers to ensure the equipment is intact. Then, after the bypass is established, it is ensured that the thyristors are completely de-energized at both ends, at which point the thyristors automatically turn off and reset. Finally, after confirming that all equipment has returned to normal, the D-UPFC system is restarted according to the established procedure.

4. Fault Protection Device Protection Strategy

Depending on the application scenarios of the D-UPFC, the D-TBS, as an emergency protection device, is in a hot standby state under normal circumstances and is unlocked and turned on only in the event of a system failure. Due to the protection requirements of the D-UPFC, the interval from the occurrence of faults such as overvoltage and overcurrent in the system to the conduction of the thyristor should be controlled within a few milliseconds, and the thyristor’s own response time is also around the millisecond level. Therefore, the delay of the sampling and control protection action time of the D-TBS control device should not exceed 1 ms (comprehensive consideration of semiconductor safety, grid fault ride-through standards, and control system performance).

A three-level fault protection architecture was designed in this study, and the system composition is shown in

Figure 6. The architecture consists of three layers: the main controller layer, the D-TBS controller layer, and the TCU layer. Signal transmission and trigger control are achieved between these layers through an optical fiber communication network. At the main controller layer, the system collects the primary side current signal of the D-UPFC series transformer in real time, with a protection response time of no more than 1 ms. The D-TBS controller layer is responsible for monitoring the secondary current parameters of the D-UPFC series transformer, and the protection action delay is controlled to within 100 μs. The TCU layer works in conjunction with the D-TBS controller layer to monitor the voltage on the secondary side of the D-UPFC series transformer in real time, with a protection execution time of less than 2 μs. The protection system uses fiber optic communication technology, which not only significantly enhances anti-electromagnetic interference performance but also enables reliable transmission over long distances, providing convenience for the layout and control of field equipment.

4.1. TCU Level Protection

In the hierarchical architecture of the protection system, the TCU monitoring unit serves as the primary protection mechanism, with optimal response characteristics. It works as follows: When the current in the RC energy-harvesting loop is in the positive half-cycle, the self-harvesting module of the TCU initiates energy harvesting. During the forward alternating period of the voltage signal, the voltage monitoring unit of the TCU detects the forward voltage signal and immediately sends a pulse signal to the D-TBS through the electro-optical conversion unit. At the same time, the overvoltage-monitoring unit collects the voltage parameters of the thyristor voltage-equalizing resistor loop in real time and compares them with the preset overvoltage protection threshold. When it detects that the sampled voltage exceeds the threshold voltage, the overvoltage monitoring unit simultaneously performs two operations: On the one hand, it transmits a pulse signal to the D-TBS through the electro-optical conversion unit, and on the other hand, it sends a trigger command to the trigger unit, thereby driving the thyristor into the conduction state.

4.2. D-TBS Class Protection

In the hierarchical architecture of the protection system, the D-TBS control unit undertakes secondary protection functions, and its response time is also maintained at the microsecond level. As the core control unit of the protection system, this unit mainly undertakes the following functions: First, it is responsible for collecting, processing, and uploading the full-state operation information of the switchgear. Secondly, it monitors the IP signals sent by the TCU in real time and adjusts the conduction status of the thyristors accordingly to ensure that the main equipment can achieve rapid isolation and protection in the event of a fault.

When an overcurrent fault occurs in the system, the D-TBS control unit, after confirming that each TCU module has completed energy acquisition, sends thyristor trigger instructions in sequence and simultaneously integrates and transmits the fault data to the main control unit. The specific implementation process of its protection mechanism is as follows: The system first performs analog-to-digital conversion sampling on the three-phase current signal, and the FPGA processor acquires the current data at the preset sampling frequency. The D-TBS control unit performs sliding window processing on the collected discrete signal based on the current protection threshold set by the main control unit. Calculating the root mean square (RMS) current within a specific time window can ensure rapid response while effectively avoiding spike interference, thereby achieving accurate identification of overcurrent faults and TCU trigger control. The proposed overcurrent detection algorithm effectively suppresses random interference while significantly accelerating the system’s response to faults. The specific process is illustrated on the left side of

Figure 7.

When the D-TBS control unit detects overvoltage in a specific TCU module, the system will perform a fault-marking operation and simultaneously activate the trigger mechanism of the remaining TCU modules, thereby achieving rapid bypass protection for the main equipment. The implementation process of the protection logic is as follows: The FPGA processor first parses and judges the IP signal feedback from the TCU. When the first valid IP signal is captured, the system confirms that the TCU module has completed external energy harvesting and entered the normal working state, and then initiates the overvoltage monitoring program. If a second valid IP signal is detected during the monitoring cycle, an overvoltage fault is determined and the system marks the fault and sends an FP trigger instruction to the other TCU modules. Due to the adoption of an optical triggering method for controlling the TCU module by the D-TBS control unit, mis-operations of the TCU caused by external interference are essentially eliminated. Furthermore, during operation, the D-TBS control unit periodically reports its status to the main controller. This enables the system to promptly detect internal faults within the D-TBS control unit and execute predefined countermeasures. In addition, when the D-TBS control unit fails to receive a valid IP feedback signal from a certain TCU module for five consecutive power frequency cycles, it will be determined that the TCU module has failed. The system will perform the fault marking and notify the main control unit to initiate the equipment disconnection operation. The specific process is illustrated on the right side of

Figure 7.

4.3. Primary Control-Level Protection

As the third-level control unit of the protection system, the main controller has a relatively long response time due to factors such as control cycle and fiber optic transmission delay but still completes the protection action within 1 ms. The control unit not only monitors the voltage and current parameters on the secondary side of the series transformer in real time but also collects the current signal on the primary side as a protection criterion. When a fault occurs, the main controller sends status instructions to the D-TBS control unit via the optical fiber communication network, thereby triggering control of the TCU module. The specific implementation process of its protection mechanism is as follows: The system first performs real-time sampling of the 10 kV bus current, and the sampling signal is converted to a voltage signal through a parallel resistor network and then input into the AD sampling channel of the main controller. The DSP processor reads the voltage signal according to the preset interrupt period and calculates the RMS value of the current. The main controller compares the calculated current value with the preset threshold. When an overcurrent state is detected, the system performs a fault-marking operation and sends corresponding control instructions via the communication network.

4.4. Technical Advantages of Three-Level Protection

The determination of system protection thresholds is primarily governed by the parameters of key converter components (such as IGBTs and capacitors). Furthermore, the setting of protection boundary conditions must also consider factors like the system operation mode and redundancy configuration. Therefore, the threshold settings for overcurrent and overvoltage are not completely uniform in different application scenarios. The implementation of the three-level protection strategy helps the device meet diverse field requirements. Meanwhile, the three-level protection design enables simultaneous monitoring and protection of both high-side and low-side current and voltage. The fault response time can be as fast as 10 µs, meeting the requirements for systematic protection.

Since it is difficult to monitor the online operating status of the TCU in real time, it is difficult for the system to respond quickly when hardware problems occur. If an overvoltage fault happens to occur in that phase, it cannot be identified immediately, and at least half a cycle will have to pass before protection by another TCU unit. Adding a D-TBS protection level can respond to system failures in a shorter amount of time and enable synchronous trigger control of multiple TCU modules to suppress overvoltage and overcurrent damage to the converter.

5. Tests and Results

5.1. Functional Testing

The protection function of the fault protection device is tested through trigger tests, overcurrent fault tests, and overvoltage fault tests.

The trigger test is to test the basic functions of the TCU unit and the communication between the D-TBS control board and the TCU. The test schematic diagram, test diagram, and test results are shown in

Figure 8 below. The TBS controller is connected to the TCU via optical fiber, and the TCU can be effectively triggered after a command is issued under the controller.

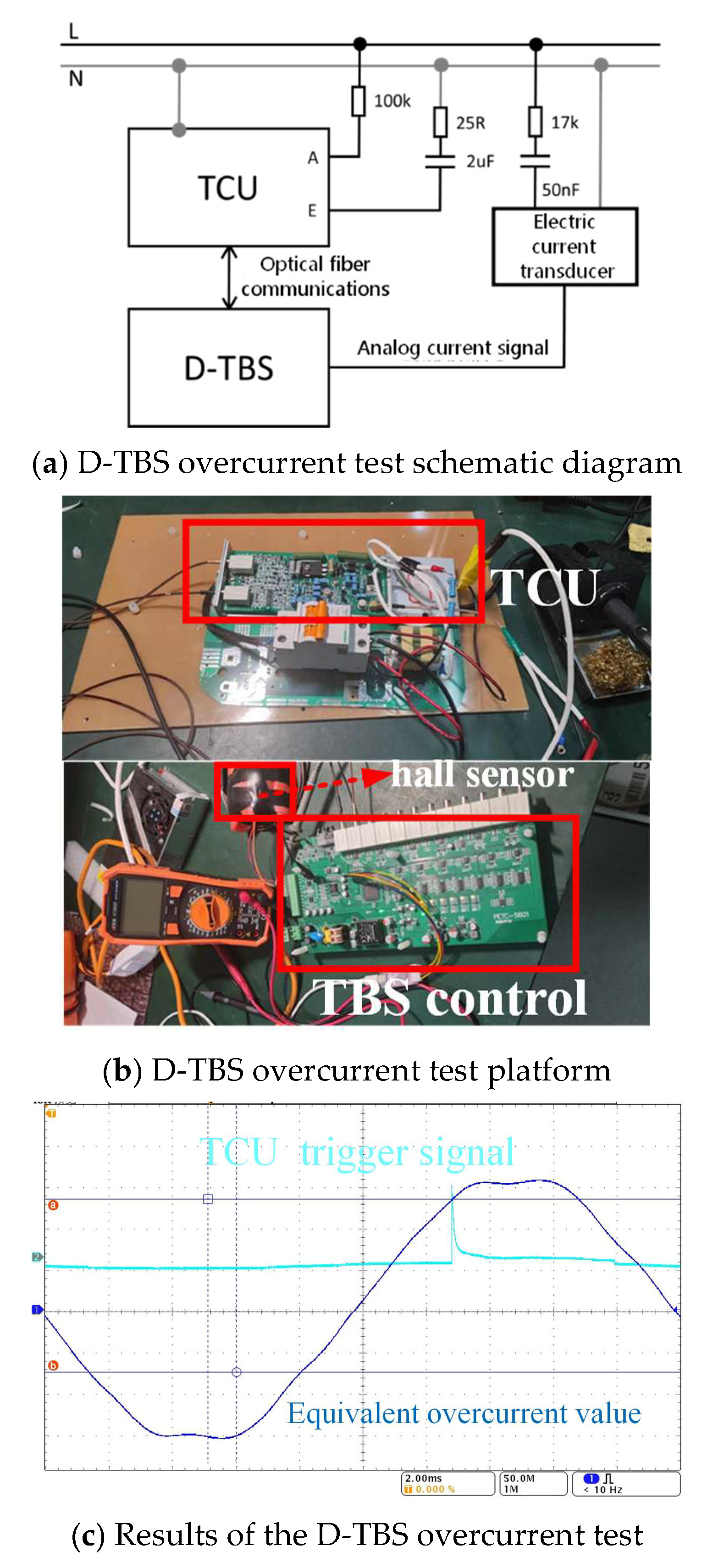

An overcurrent fault test is a test of the overcurrent protection function of a protection device. The testing principle and results are shown in

Figure 9. The TBS controller sends a trigger signal to the TCU when the simulated test current exceeds the set value by connecting an external power supply to the TBS controller, as shown in the following figure.

The overvoltage fault test is to test the overvoltage protection function of the protection device and the speed of response to overvoltage faults, as shown in

Figure 10.

The principle is to connect a small resistance-value resistor in parallel to a normal external large resistor to obtain a large current through short-term conduction so that the TCU simulates an overvoltage fault at low voltage. The D-TBS controller determines whether there is an overvoltage fault in the TCU unit by monitoring the number of indication pulses (IPs) per cycle of the TCU. The TCU IP signal indication waveform and test results are shown in

Figure 11.

In the

Figure 12, line 1 represents the overvoltage fault signal (low effective) received by the D-TBS, and line 2 is the unlock signal output by the D-TBS controller in response to the fault, with a delay of 920 ns measured by the oscilloscope (of which 800 ns is the filter delay). Line 3 is the output of the TCU thyristor unlock signal, with a total delay of 1.08 μs. The device’s extremely fast response speed ensures effective protection can be achieved during the initial stage of a voltage surge, significantly reducing the risk of damage to power components. The design functionality meets the intended requirements.

5.2. System Test

The fault protection strategy was tested by setting up the D-UPFC flexible loop closure device and control system. The system test parameters are shown in the

Table 2:

As shown in

Figure 13, taking a three-phase short-circuit fault in an AC system as an example, the short-circuit capacity of the AC distribution network is set to 20 MVA to verify the system fault protection device and its protection strategy. The simulated waveforms are:

When testing, consider the most serious external faults of the D-UPFC system, namely three-phase short-circuit faults occurring on the outlet side of the series transformer.

The action logic settings of D-UPFC after an AC system failure are as follows:

A three-phase short-circuit fault occurs at 1.0 s;

Five ms after the fault occurs, the D-UPFC inverter side initiates converter lockout pulse;

Fifty ms after the failure, switch the D-TBS loop (in actual protection devices, the response speed of the D-TBS itself can be at the ms level, and this simulation mainly verifies the protective effect of the D-TBS loop in the event of a failure).

After the fault occurs, the D-UPFC will experience transient overcurrent and lock, and the series transformer may experience overexcitation, resulting in an increase in voltage across the transformer (as shown in the above figure, the peak voltage on the secondary side of the series transformer can reach about 2.5 kV). After the D-TBS is put into operation, since the impedance of the D-TBS circuit is very small, the secondary side of the series transformer is approximately short-circuited after the TBS is closed, resulting in a large current in the D-TBS circuit (as shown above, the peak current in the D-TBS circuit can reach about 47 kA), thereby reducing the voltage on the secondary side of the series transformer and completing the fault protection mechanism of the secondary circuit.