Topology Analysis and Modeling Comparison of SI-SIMO Boost Converter Used in Multiple Output Applications

Abstract

1. Introduction

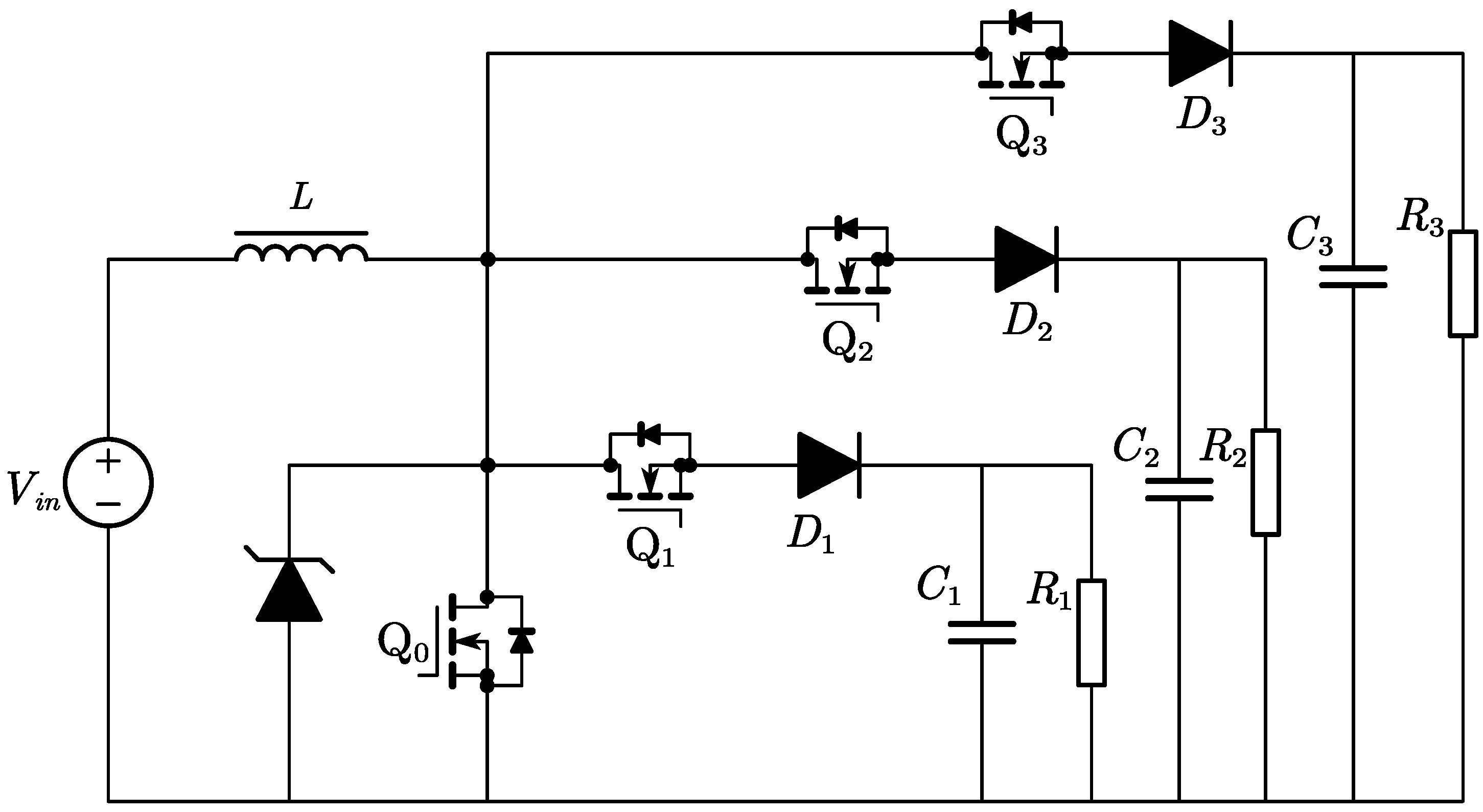

2. SI-SIMO Boost Converter

2.1. Topology

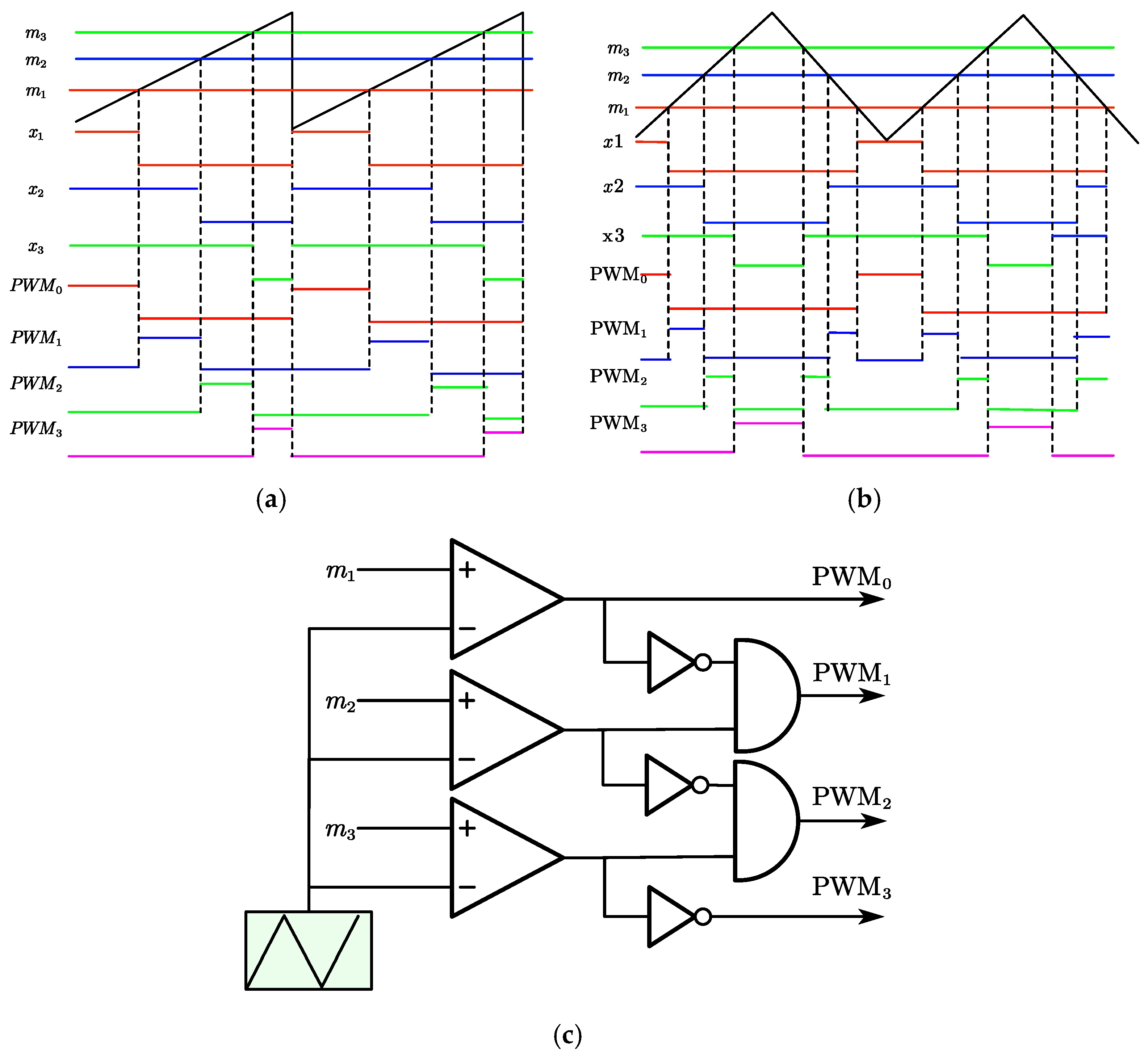

2.2. Modulation Scheme

2.3. Overlap PWM Logic to Avoid Overvoltage

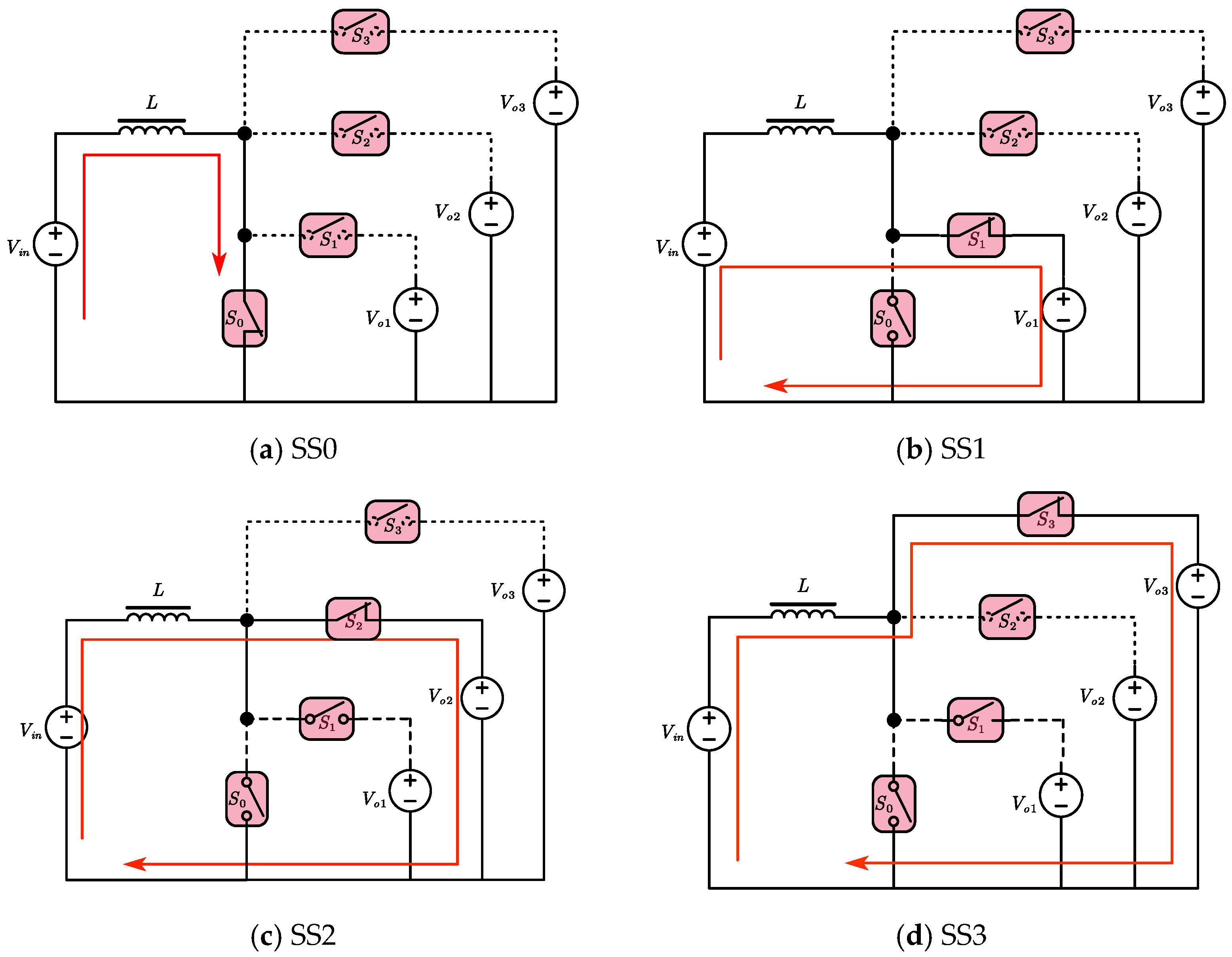

3. Switching-State Analysis

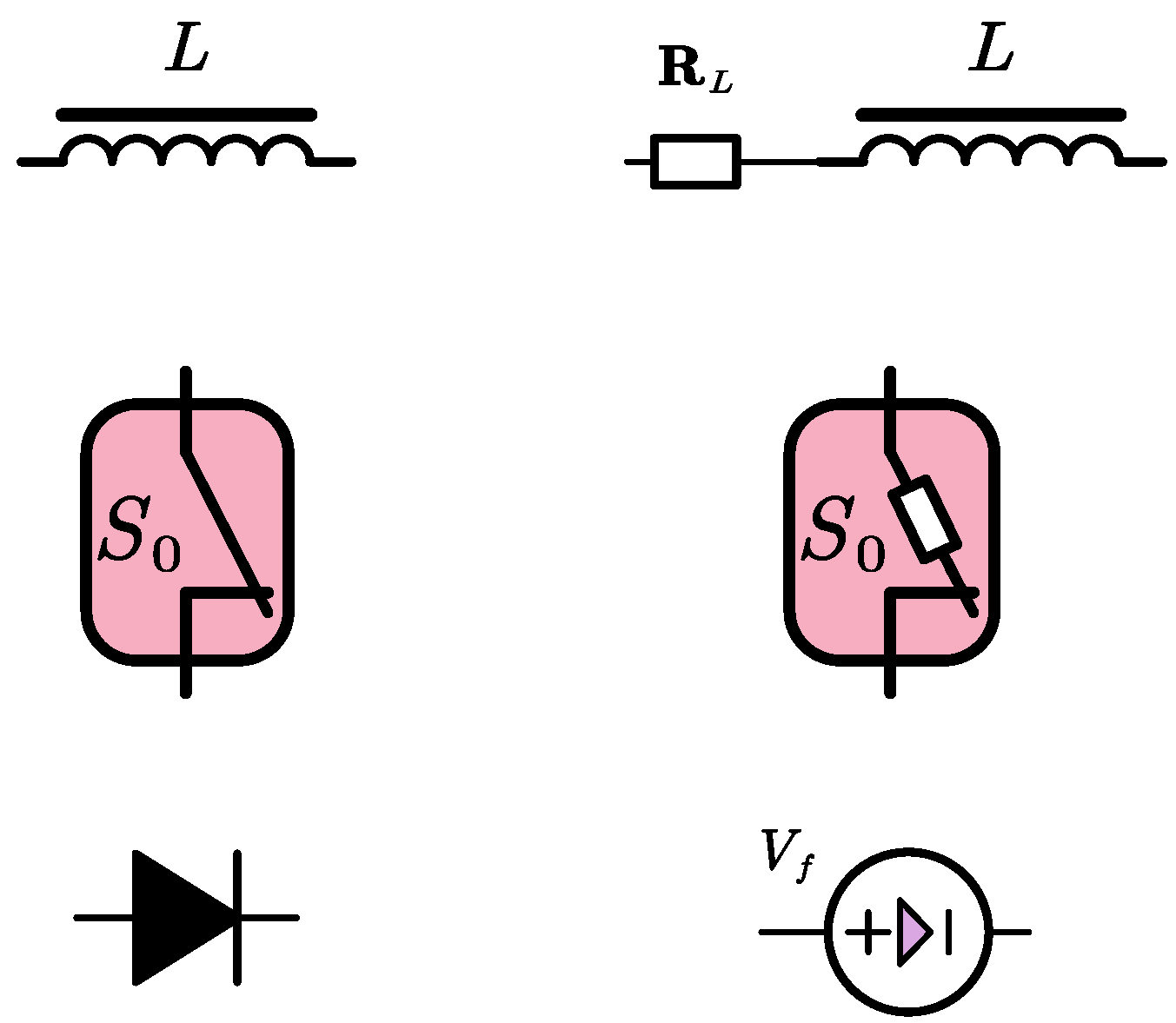

- Inductor model enhancement: The conventional inductor is replaced with a composite structure comprising an inductor in series with a resistor. This modification explicitly accounts for the parasitic resistance inherent in practical inductors.

- MOSFET parasitic resistance incorporation: The MOSFET device is represented by an equivalent model incorporating series resistance, graphically depicted as a switch–resistor combination. This refinement quantitatively captures the influence of the MOSFET’s on-state resistance.

- Diode forward voltage characterization: The ideal diode model is substituted with a unidirectional voltage source element. This substitution effectively models the non-negligible forward voltage drop characteristic of semiconductor diodes during conduction.

3.1. Switching-State 0 (Figure 5a SS0)

3.2. Switching-State 1 (Figure 5b SS1)

3.3. Switching State 2 (Figure 5c SS2)

3.4. Switching State 3 (Figure 5d SS3)

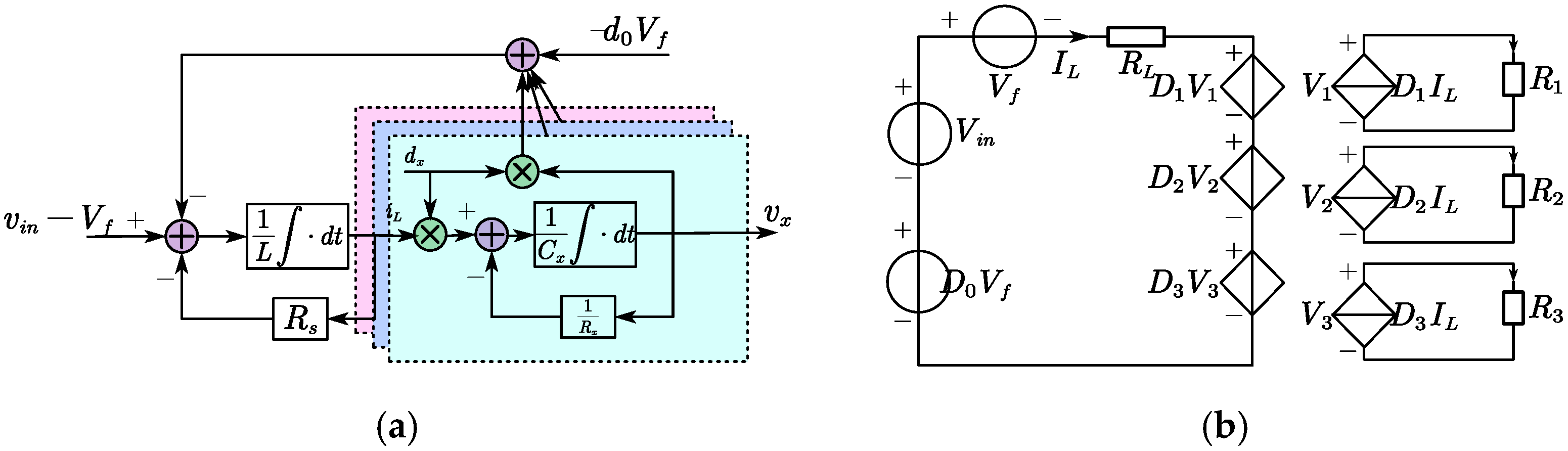

4. SIMO Boost Modeling and Analysis

4.1. Complete Nonlinear Dynamic Model

4.2. Steady-State Equivalent Circuit

4.3. Small-Signal Model

4.4. CCM/DCM Analysis

4.4.1. CCM Criteria

4.4.2. Critical Inductor Value

5. Simulation and Experimental Validation

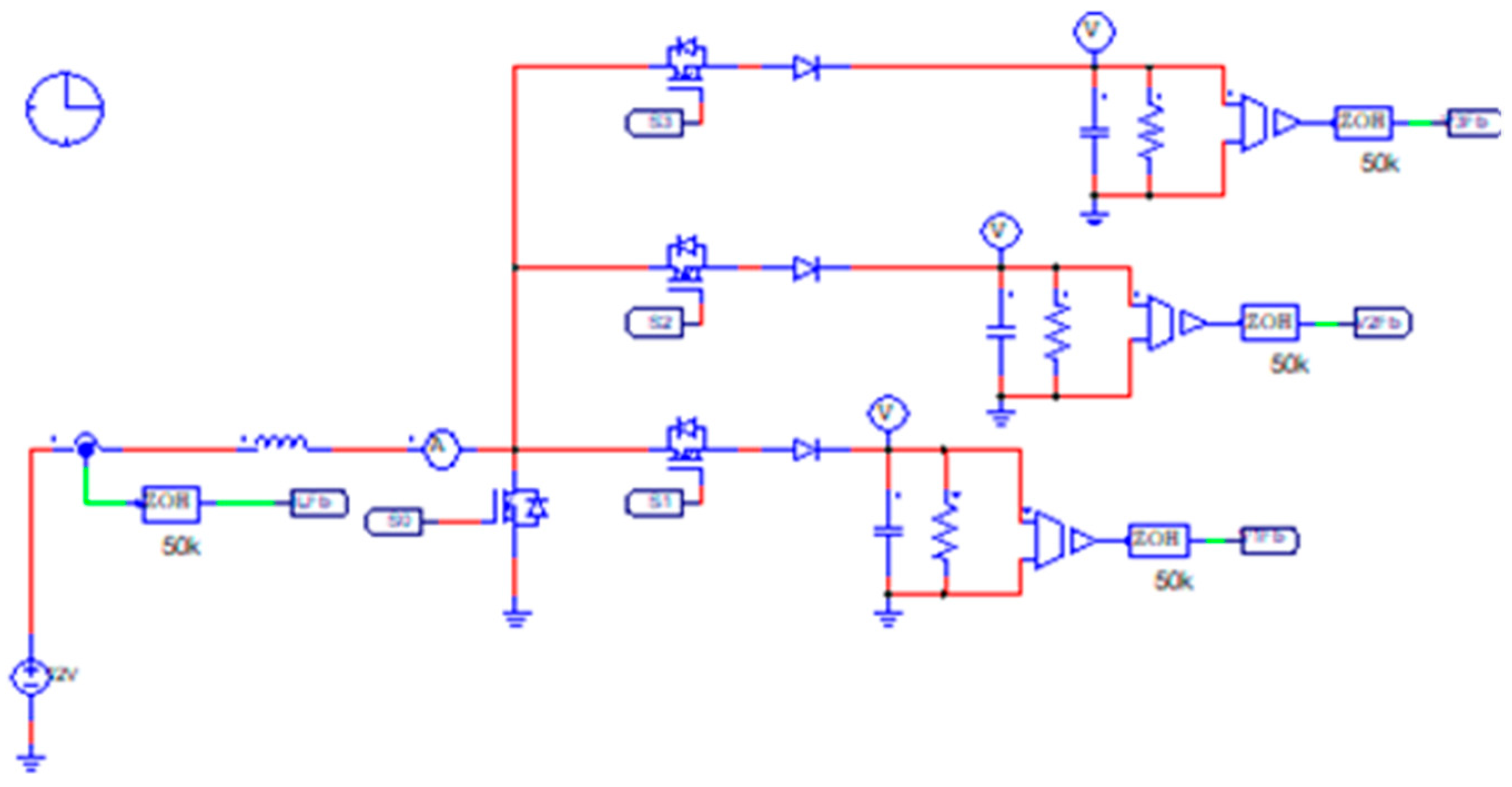

5.1. SI_SIMO Circuit Validation

5.1.1. Circuit Model and Experiment Parameters

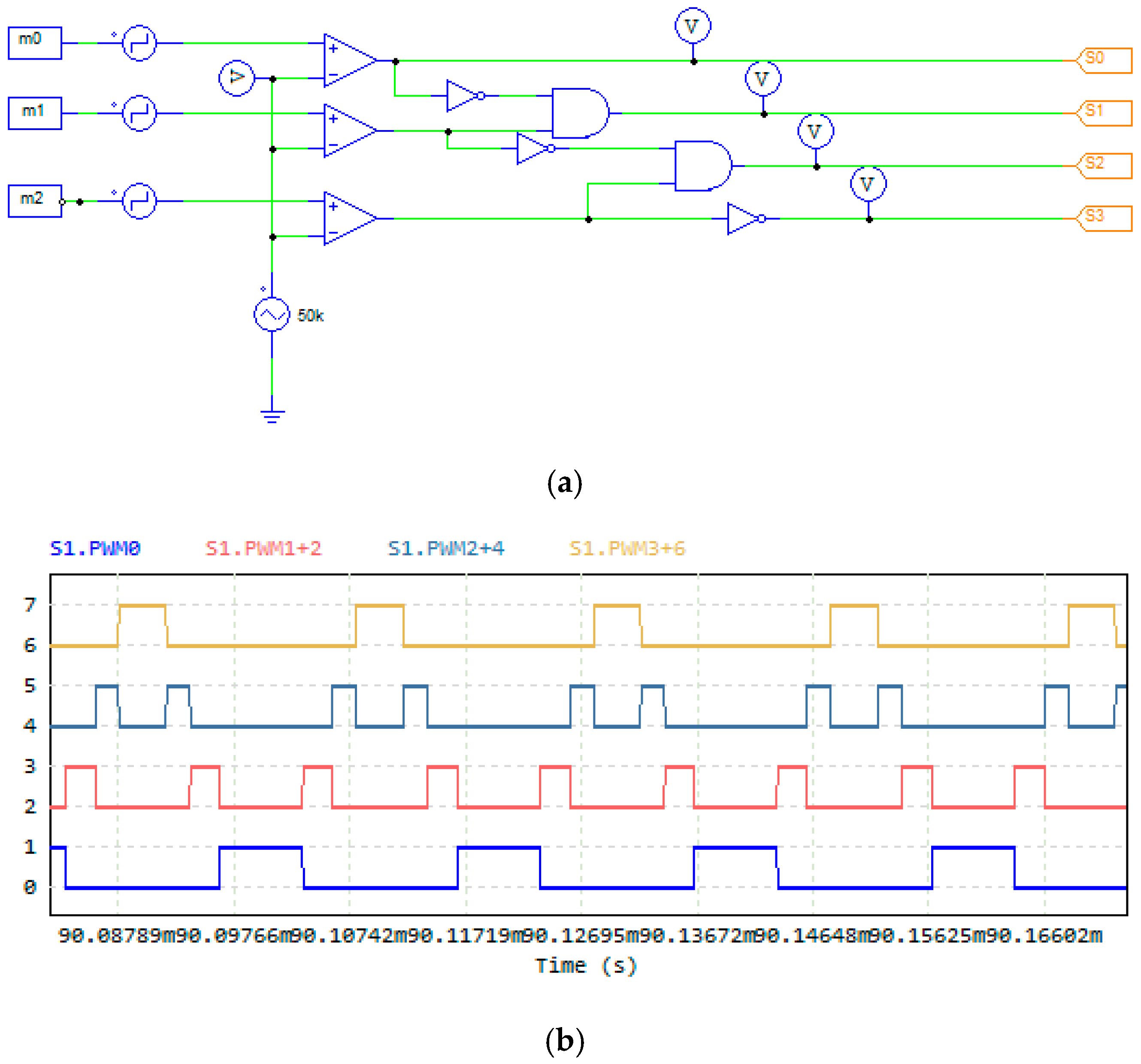

5.1.2. Modulation Logic and PWM Signal

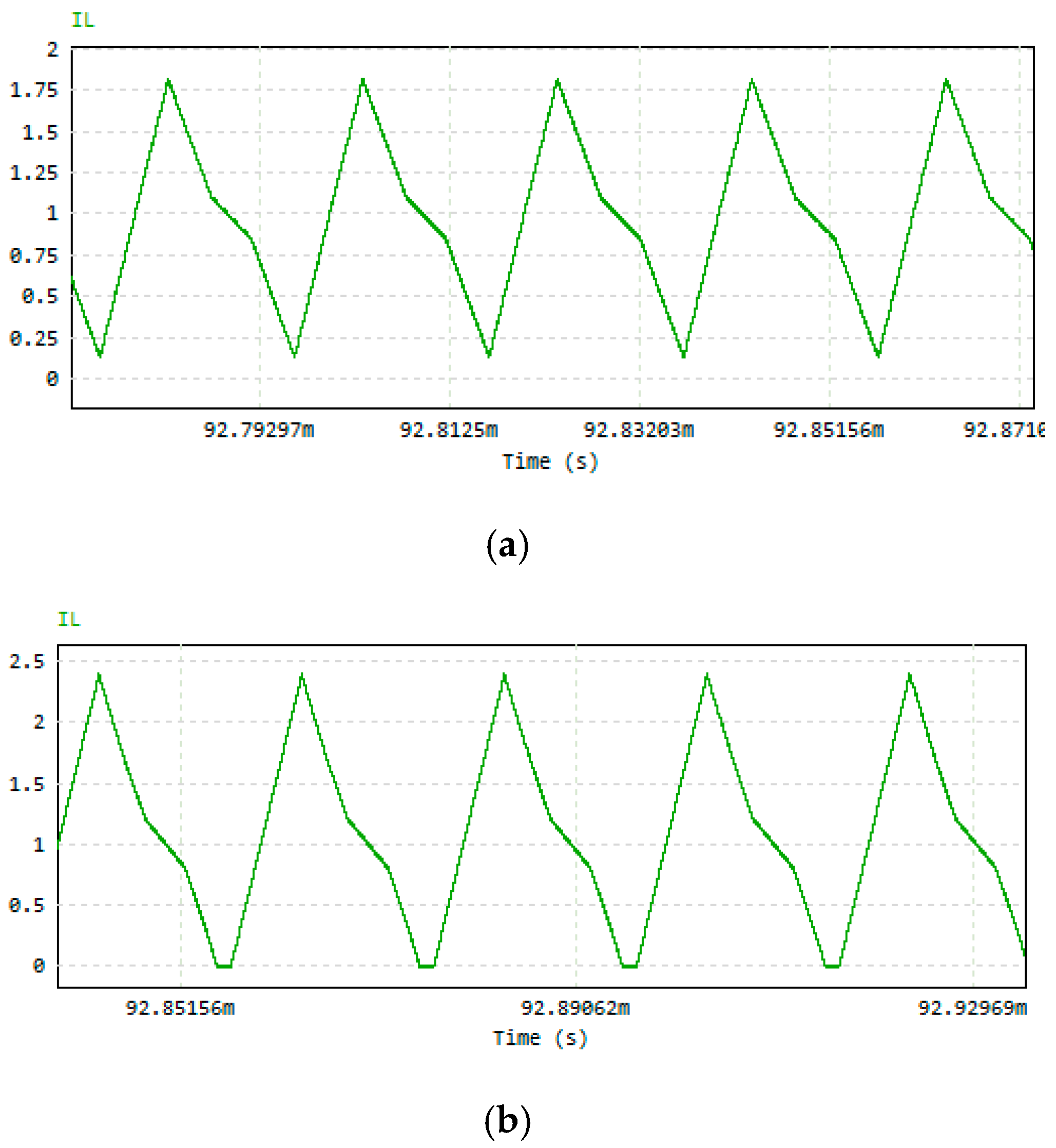

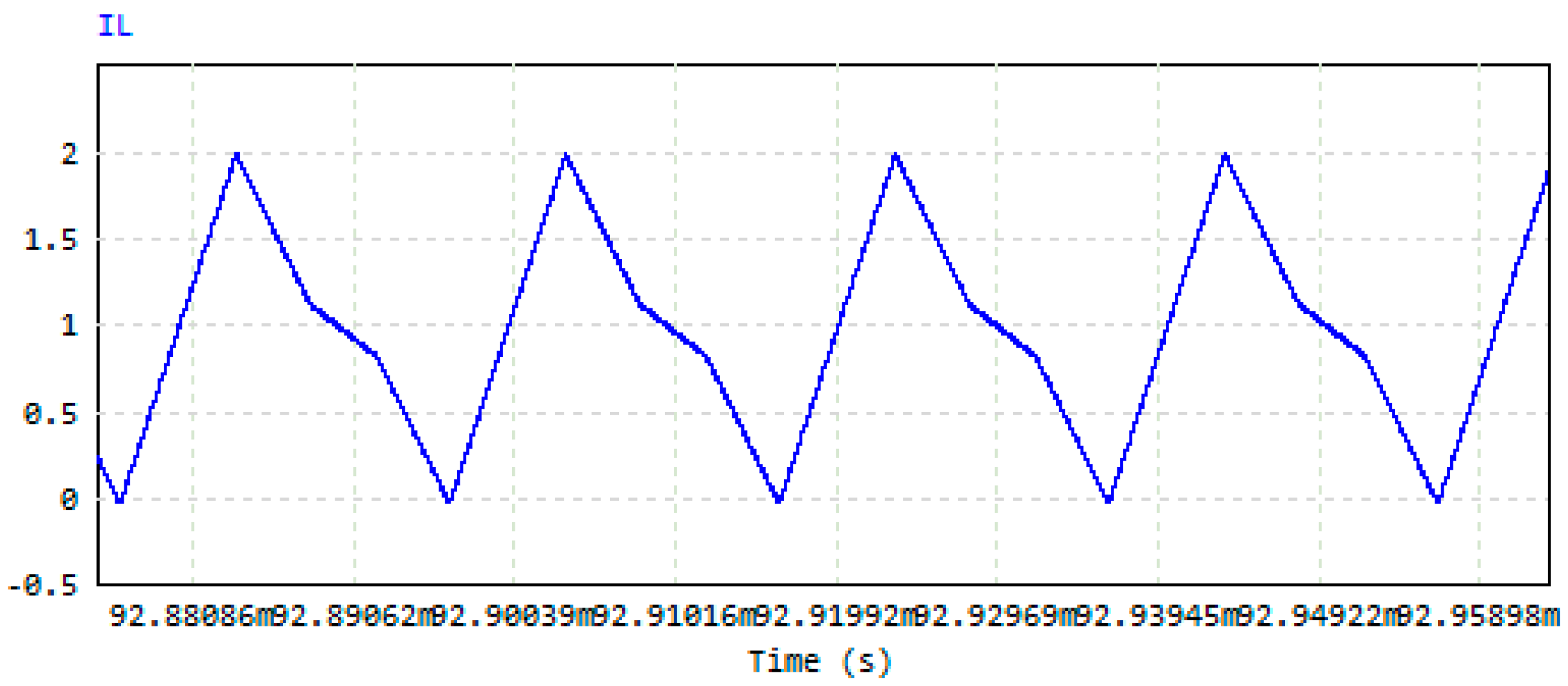

5.1.3. CCM/DCM Simulation

5.1.4. Critical Inductor Value Simulation

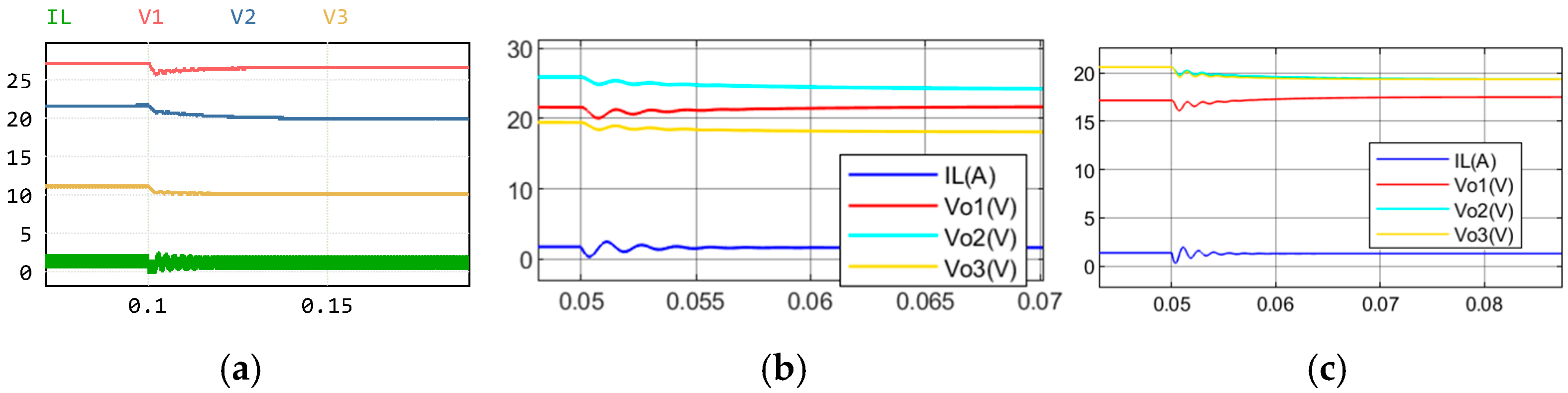

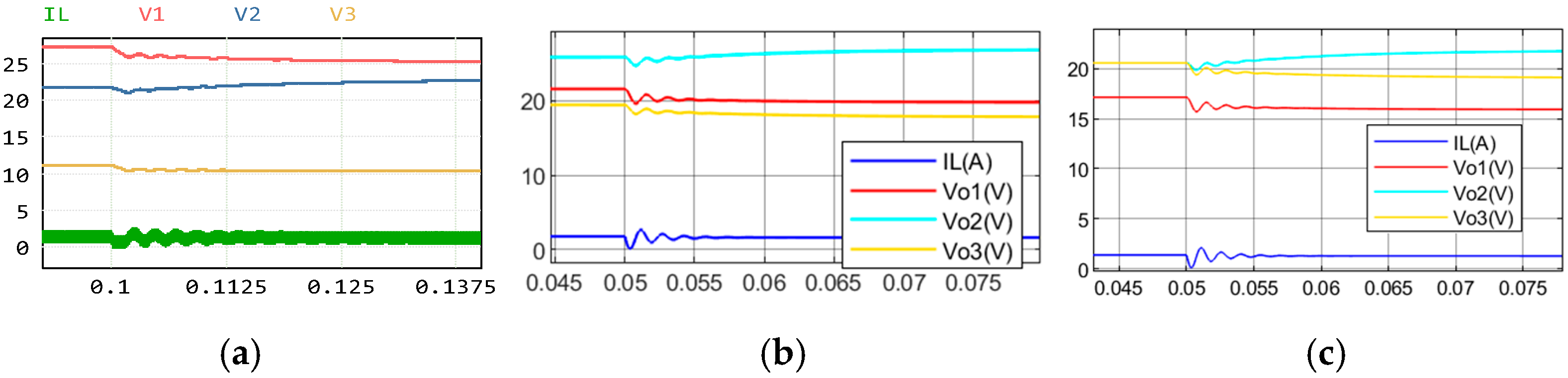

5.1.5. Steady-State Average Test

5.2. SI-SIMO Dynamic Modeling Comparison

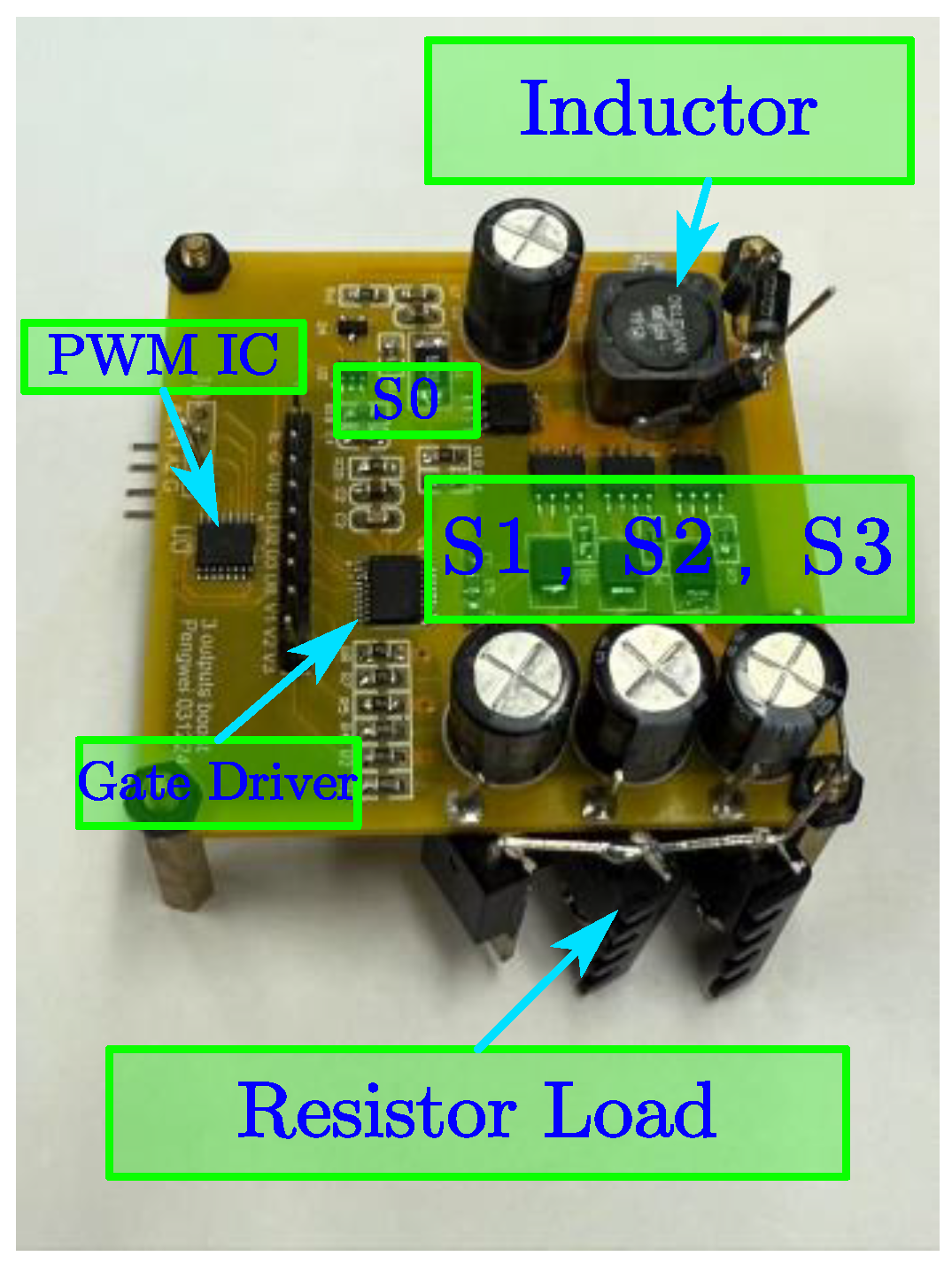

5.3. Experiment

6. Discussion

7. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Almakhles, D.; Ali, J.S.M.; Navamani, J.D.; Lavanya, A.; Bhaskar, M.S. Single Switch Module Type DC-DC Converter with Reduction in Voltage Stress. IEEE Access 2022, 10, 107877–107887. [Google Scholar] [CrossRef]

- Remya, K.P.; Mathew, J.; Nandana, V.S. High Gain Switched Inductor-Capacitor Split Source Inverter. In Proceedings of the 2021 IEEE 2nd International Conference on Smart Technologies for Power, Energy and Control (STPEC), Bilaspur, India, 19–22 December 2021; pp. 1–5. [Google Scholar]

- Asapu, S.; Palleswari, Y.T.R.; Rapaka, P.S.; Bade, M.C.; Deenakonda, M.; Banothu, R. Design and Implementation of High Voltage Gain DC-DC Converter for Solar PV Applications. In Proceedings of the 2024 International Conference on Computational Intelligence for Green and Sustainable Technologies (ICCIGST), Vijayawada, India, 18–19 July 2024; pp. 1–5. [Google Scholar]

- Das, R.; Le, H.-P. Modular Isolated Vertically Symmetric Dual Inductor Hybrid Converter for Differential Power Processing. In Proceedings of the 2021 IEEE Energy Conversion Congress and Exposition (ECCE), Vancouver, BC, Canada, 10–14 October 2021; pp. 2439–2443. [Google Scholar]

- Hamza, A.; Tahir, H.B.; Siraj, K.; Nasir, M. Hybrid AC/DC Microgrid for Residential Applications. In Proceedings of the 2019 IEEE Third International Conference on DC Microgrids (ICDCM), Matsue, Japan, 20–23 May 2019; pp. 1–5. [Google Scholar]

- Nayak, P.; Rajashekara, K. A Single-Stage Isolated AC-DC Converter to Interlink Utility Grid and Renewable Energy Sources in a Residential DC Distribution System. IEEE Trans. Ind. Appl. 2021, 57, 4409–4419. [Google Scholar] [CrossRef]

- Korobkov, D.V.; Reshetnikov, A.N.; Shtein, D.A.; Geist, A.V.; Sekushenko, T.S.; Klassen, S.V. Simulation of the Multiple Port DC-DC Converter. In Proceedings of the 2017 18th International Conference of Young Specialists on Micro/Nanotechnologies and Electron Devices (EDM), Chemal, Russia, 29 June–3 July 2017; pp. 429–434. [Google Scholar]

- Jia, X.; Xu, D.; Du, S.; Hu, C.; Chen, M.; Lin, P. A high power density and efficiency bi-directional DC/DC converter for electric vehicles. In Proceedings of the 2015 9th International Conference on Power Electronics and ECCE Asia (ICPE-ECCE Asia), Seoul, Republic of Korea, 1–5 June 2015; pp. 874–880. [Google Scholar]

- Kanaparthi, R.K.; Singh, J.P.; Ballal, M.S. A Review on Multi-Port Bidirectional Isolated and Non-Isolated DC-DC Converters for Renewable Applications. In Proceedings of the 2022 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), Jaipur, India, 14–17 December 2022; pp. 1–6. [Google Scholar]

- Li, P.; Silverman, M.; Bazzi, A. Fault-Tolerant Power-Sharing Strategy with A Novel MPPT Method for Parallel PV Converters in Electric Airplanes. In Proceedings of the 2023 IEEE Transportation Electrification Conference & Expo (ITEC), Detroit, MI, USA, 21–23 June 2023; pp. 1–6. [Google Scholar] [CrossRef]

- Wang, C.; Sun, D.; Gu, W.; Gui, S. An Adaptive Dead Time Prediction Method for Primary-Side Regulation Active-Clamp Flyback Converter. In Proceedings of the 2022 IEEE Energy Conversion Congress and Exposition (ECCE), Detroit, MI, USA, 9–13 October 2022; pp. 1–6. [Google Scholar]

- Xu, C.; Liu, S.; Guo, X.; Xiao, C.; Zou, X.; Zhang, L. A Novel Converter Integrating Buck-Boost and DAB Converter for Wide Input Voltage. In Proceedings of the IECON 2020 The 46th Annual Conference of the IEEE Industrial Electronics Society, Singapore, 18–21 October 2020; pp. 2877–2882. [Google Scholar]

- Gevorkov, L.; Domínguez-García, J.L.; Martínez, À.F. Modern Trends in MultiPort Converters: Isolated, Non-Isolated, and Partially Isolated. In Proceedings of the 2022 IEEE 63th International Scientific Conference on Power and Electrical Engineering of Riga Technical University (RTUCON), Riga, Latvia, 10–12 October 2022; pp. 1–6. [Google Scholar]

- Verma, H.K.; Mitra, U.; Gupta, A.K.; Mishra, R.; Bhoi, R. Design and Analysis of a Novel Transformer Less Non-Isolated Bi-Directional DC-DC Converter for Applications in Isolated DC Microgrids. In Proceedings of the 2024 IEEE Silchar Subsection Conference (SILCON 2024), Agartala, India, 15–17 November 2024; pp. 1–6. [Google Scholar]

- Kumari, D.; Chattopadhyay, S.K.; Verma, A. Multi-Winding Transformer based High Resolution Power Flow Controller. In Proceedings of the 2019 IEEE 28th International Symposium on Industrial Electronics (ISIE), Vancouver, BC, Canada, 12–14 June 2019; pp. 2377–2382. [Google Scholar]

- Li, M.; Yu, D.; Yu, S.S.; Li, X.; Geng, H. Enhanced Fault Detection, Localization, and Tolerance Strategy for Dual Active Bridge DC–DC Converters Through Frequency-Domain Analysis of Remote Voltage. IEEE Trans. Ind. Electron. 2025, 1–12. [Google Scholar] [CrossRef]

- Villalva, M.G.; Gazoli, J.R.; Filho, E.R. Modeling and control of a three-phase isolated grid-connected converter fed by a photovoltaic array. In Proceedings of the 2009 Brazilian Power Electronics Conference, Bonito-Mato Grosso do Sul, Brazil, 27 September–1 October 2009; pp. 202–210. [Google Scholar]

- Kulsangcharoen, P.; Klumpner, C.; Rashed, M.; Asher, G. A new duty cycle based efficiency estimation method for a supercapacitor stack under constant power operation. In Proceedings of the 5th IET International Conference on Power Electronics, Machines and Drives (PEMD 2010), Brighton, UK, 19–21 April 2010; pp. 1–6. [Google Scholar]

- Baig, M.J.; Singh, R.K. A Soft-Switched ZVS-ZCS Boost Converter Design and Analysis. In Proceedings of the 2024 IEEE 3rd International Conference on Electrical Power and Energy Systems (ICEPES), Bhopal, India, 21–22 June 2024; pp. 1–4. [Google Scholar]

- Ranjan, R.; Singh, P.N.; Karanki, S.B. A Dual-Active-Bridge Based Four-Port Bidirectional DC-DC Converter for Renewable Energy Integration. In Proceedings of the 2023 11th National Power Electronics Conference (NPEC), Guwahati, India, 14–16 December 2023; pp. 1–6. [Google Scholar]

- Al-Obaidi, N.A.; Abbas, R.A.; Khazaal, H.F. A Review of Non-Isolated Bidirectional DC-DC Converters for Hybrid Energy Storage System. In Proceedings of the 2022 5th International Conference on Engineering Technology and its Applications (IICETA), Al-Najaf, Iraq, 31 May–1 June 2022; pp. 248–253. [Google Scholar]

- Li, P.; Bazzi, A.M. A Three-Port DC-DC Converter for Energy Exchange in Microgrids. In Proceedings of the 2023 IEEE Energy Conversion Congress and Exposition (ECCE), Nashville, TN, USA, 29 October–2 November 2023; pp. 1396–1403. [Google Scholar] [CrossRef]

- Li, P.; Nisar, H.; Bazzi, A. Nonlinear Control of A Three-Port DC-DC Converter for Multi-Directional Energy Exchange. In Proceedings of the 2024 IEEE Workshop on Control and Modeling for Power Electronics (COMPEL), Lahore, Pakistan, 24–27 June 2024; pp. 1–5. [Google Scholar] [CrossRef]

- Stephen, A.; Remya, K.P.; Gomathy, S. Review on Non-isolated High Gain DC-DC Converters. In Proceedings of the 2022 Third International Conference on Intelligent Computing Instrumentation and Control Technologies (ICICICT), Kannur, India, 11–12 August 2022; pp. 200–205. [Google Scholar]

- Lin, R.-L.; Pan, C.-R.; Liu, K.-H. Family of single-inductor multi-output DC-DC converters. In Proceedings of the 2009 International Conference on Power Electronics and Drive Systems (PEDS), Taipei, Taiwan, 2–5 November 2009; pp. 1216–1221. [Google Scholar]

- Lodh, T.; Majumder, T. Highly efficient and compact single input multiple output dc-dc converters. In Proceedings of the 2016 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), Trivandrum, India, 14–17 December 2016; pp. 1–6. [Google Scholar]

- Solangi, H.; Hafeez, K.; Mekhilef, S.; Seyedmahmoudian, M.; Stojcevski, A.; Khan, L. Advanced Multi-Sampling PWM Technique for Single-Inductor MIMO DC-DC Converter in Electric Vehicles. Energies 2024, 17, 3633. [Google Scholar] [CrossRef]

- Pham, N.-S.; Yoo, T.; Kim, T.T.-H.; Lee, C.-G.; Baek, K.-H. A 0.016 mV/mA Cross-Regulation 5-Output SIMO DC-DC Buck Converter Using Output-Voltage-Aware Charge Control Scheme. IEEE Trans. Power Electron. 2018, 33, 9619–9630. [Google Scholar] [CrossRef]

- Mohd-Mokhtar, R.; Wang, L. Continuous Time State Space Model Identification Using Closed-Loop Data. In Proceedings of the 2008 Second Asia International Conference on Modelling & Simulation (AMS), Kuala Lumpur, Malaysia, 13–15 May 2008; pp. 812–817. [Google Scholar]

- Wang, H.; Sun, H.; Lu, X. An Overview on Small-Signal Modeling and Stability Analysis Methods of Voltage-Source Converter Grid-Connected System. In Proceedings of the 2021 3rd Asia Energy and Electrical Engineering Symposium (AEEES), Chengdu, China, 26–29 March 2021; pp. 320–326. [Google Scholar]

| RX Vx DX | [100 100 100] | [75 80 100] | [60 90 80] |

| [0.2 0.3 0.4] | [18.70 12.47 15.58] | [12.47 15.58 18.70] | [21.05 16.84 16.84] |

| {20.03 12.98 14.91} | {13.84 15.60 18.28} | {22.29 17.01 16.97} | |

| [0.2 0.25 0.3] | [16.67 12.85 18.52] | [10.59 14.12 21.18] | [18.93 16.15 20.19] |

| {16.33 11.59 18.04} | {11.10 14.14 20.62} | {18.64 15.87 19.76} | |

| [0.25 0.2 0.2] | [15.43 15.43 17.14] | [9.458 17.73 18.92] | [17.06 20.47 18.20] |

| {15.12 15.04 16.73} | {9.686 17.49 18.53} | {16.74 20.05 17.82} |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yan, Y.; Wang, H.; Ma, P.; Liao, J. Topology Analysis and Modeling Comparison of SI-SIMO Boost Converter Used in Multiple Output Applications. Energies 2025, 18, 3585. https://doi.org/10.3390/en18133585

Yan Y, Wang H, Ma P, Liao J. Topology Analysis and Modeling Comparison of SI-SIMO Boost Converter Used in Multiple Output Applications. Energies. 2025; 18(13):3585. https://doi.org/10.3390/en18133585

Chicago/Turabian StyleYan, Yilin, Honghong Wang, Ping Ma, and Jianquan Liao. 2025. "Topology Analysis and Modeling Comparison of SI-SIMO Boost Converter Used in Multiple Output Applications" Energies 18, no. 13: 3585. https://doi.org/10.3390/en18133585

APA StyleYan, Y., Wang, H., Ma, P., & Liao, J. (2025). Topology Analysis and Modeling Comparison of SI-SIMO Boost Converter Used in Multiple Output Applications. Energies, 18(13), 3585. https://doi.org/10.3390/en18133585