A Comparative Study of Direct Power Control Strategies for STATCOM Using Three-Level and Five-Level Diode-Clamped Inverters

Abstract

1. Introduction

- When the variable switching frequencies are introduced, the harmonics within the system appear, making the designing process of the input EMI filter more challenging.

- In the presence of some changes in the sector, the current in the source inductance, as well as the voltage at the DC link, may experience distortions.

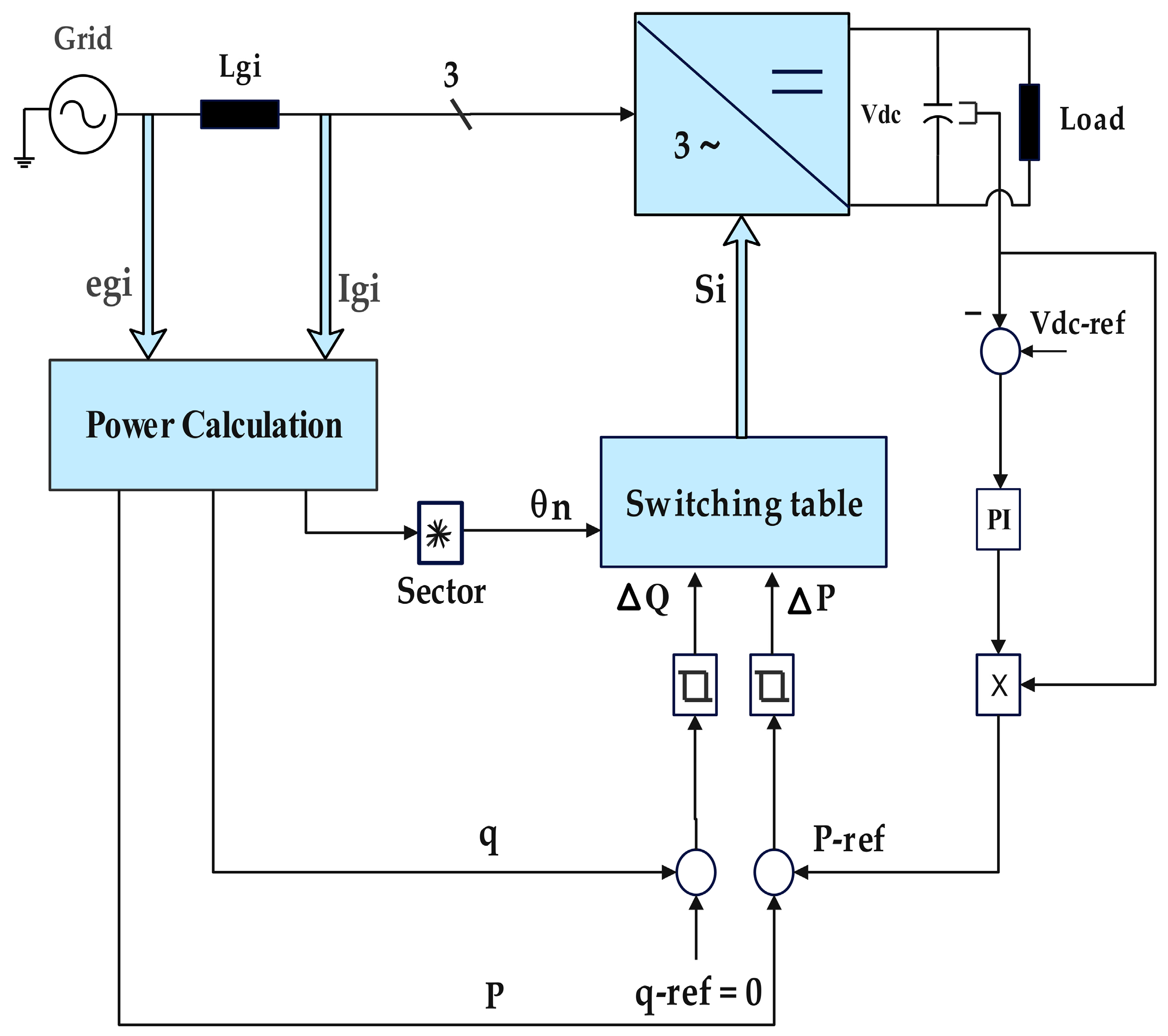

2. Direct Power Control (DPC)

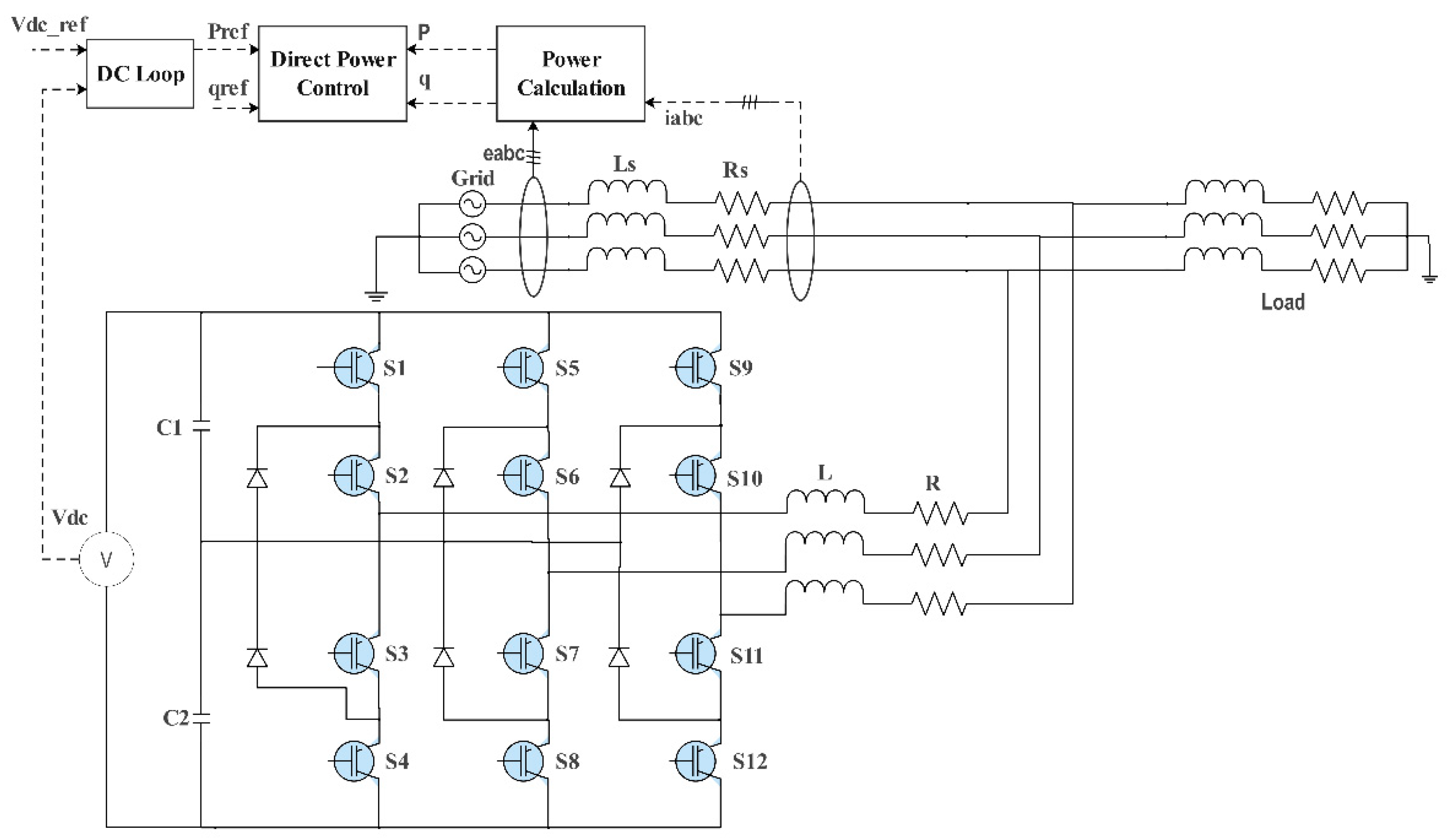

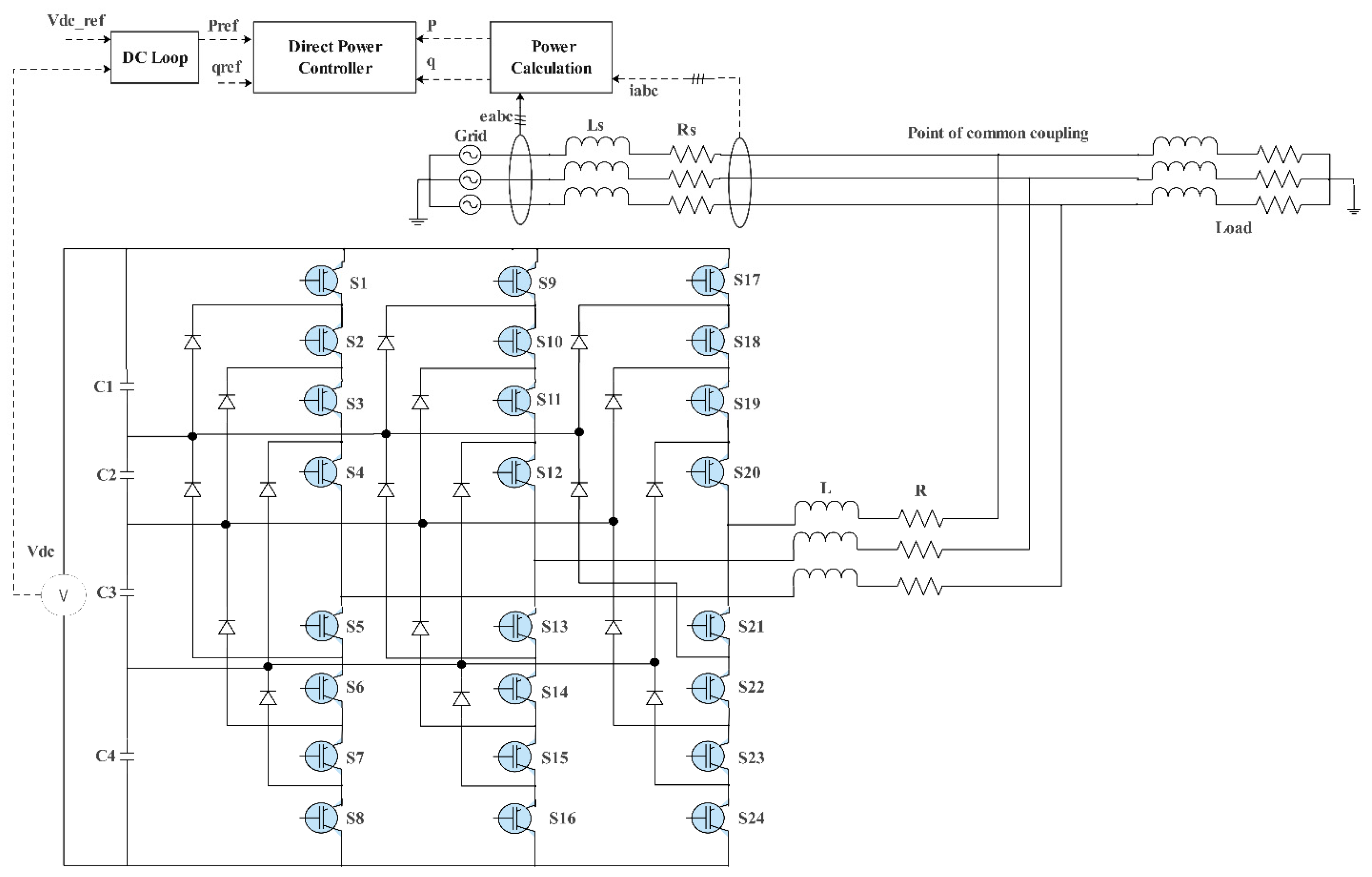

3. System Configuration

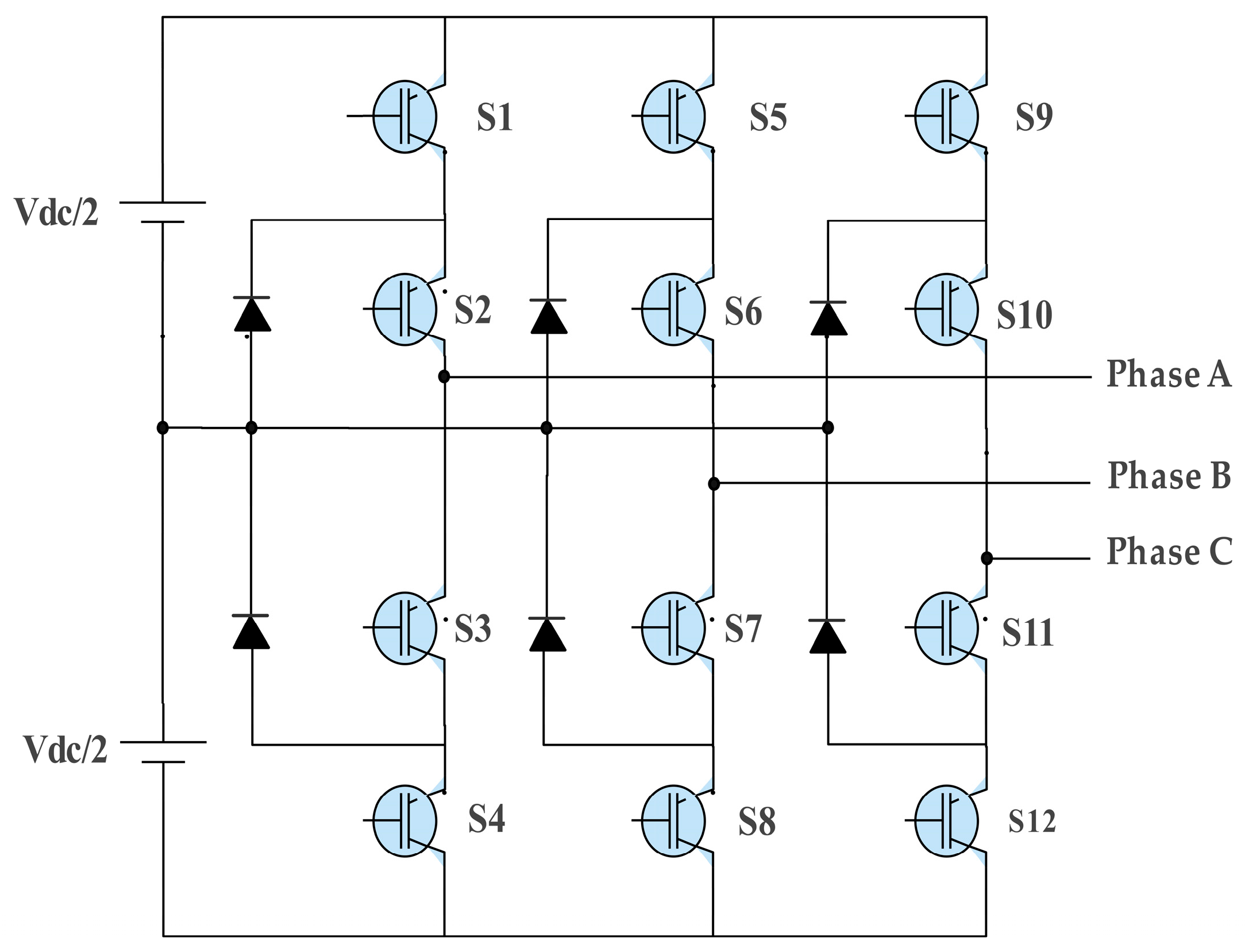

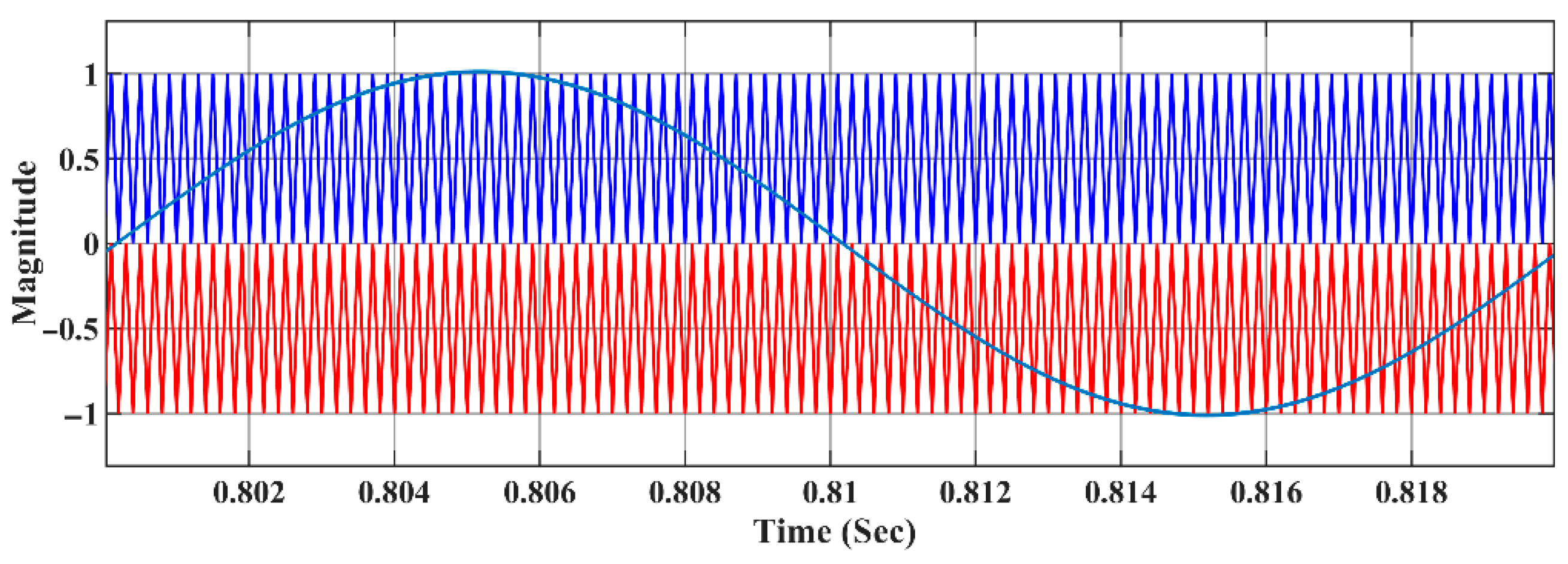

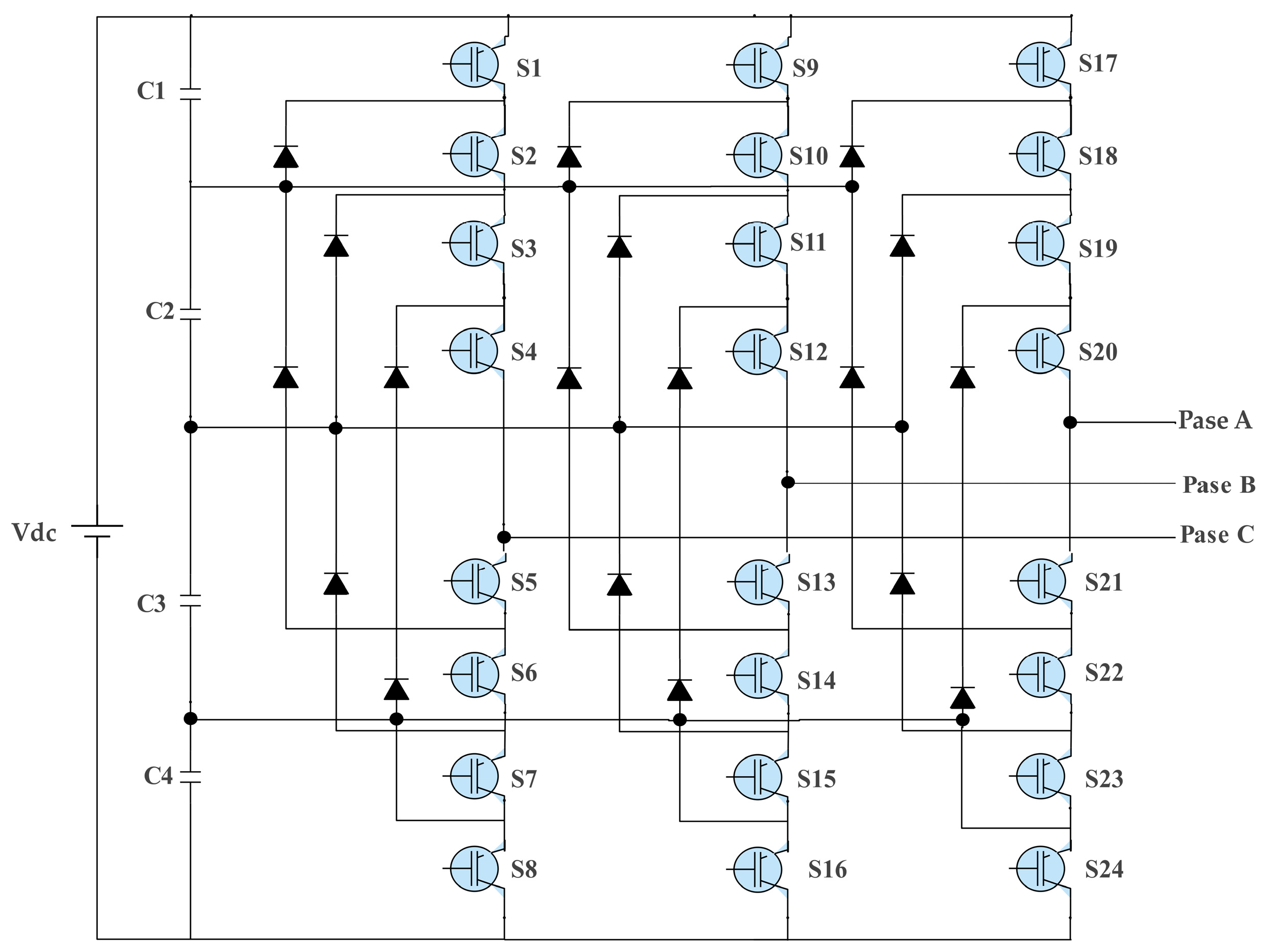

3.1. Modulation Technique

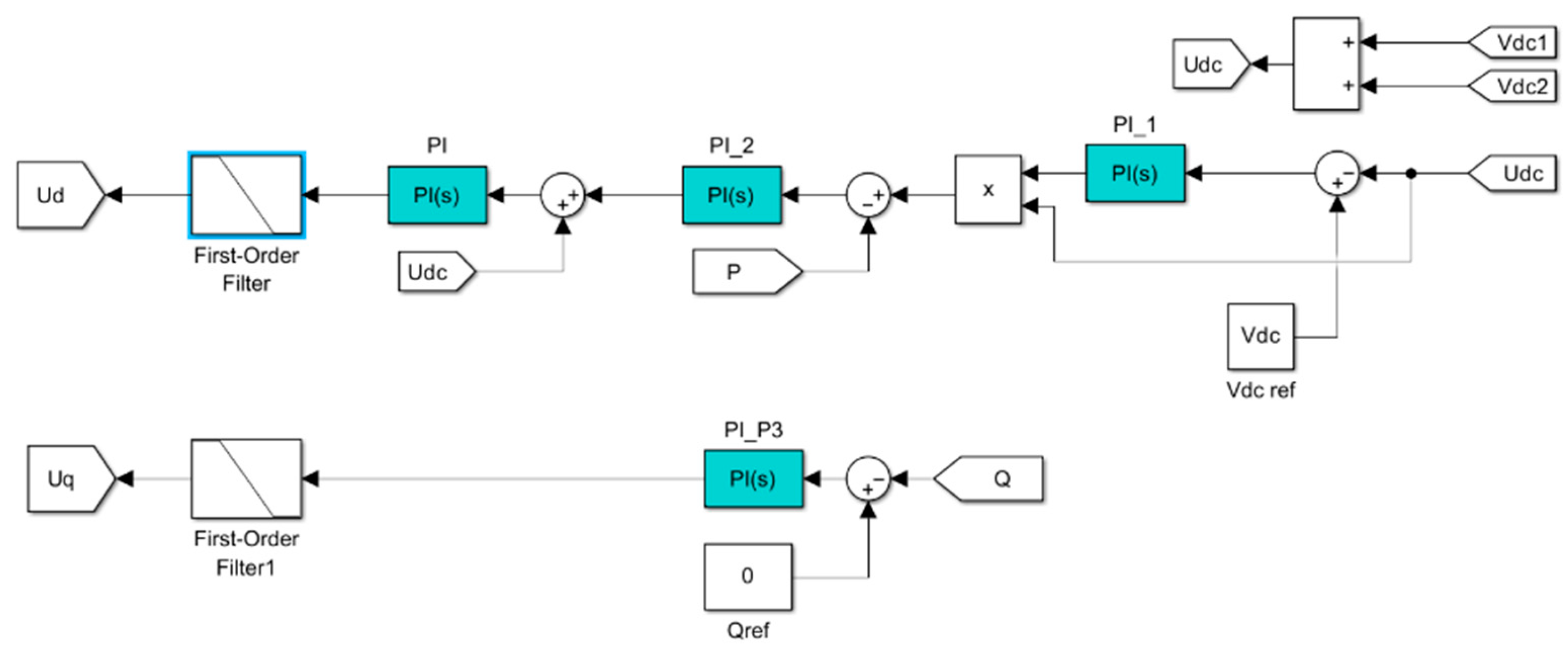

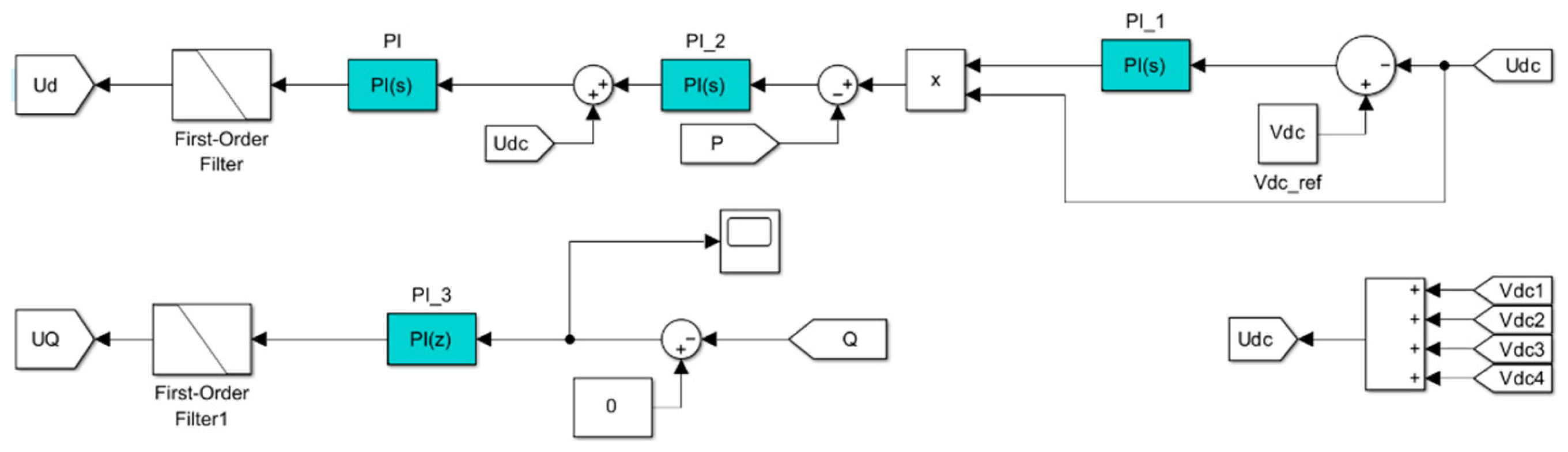

3.2. DC Voltage Control Loop

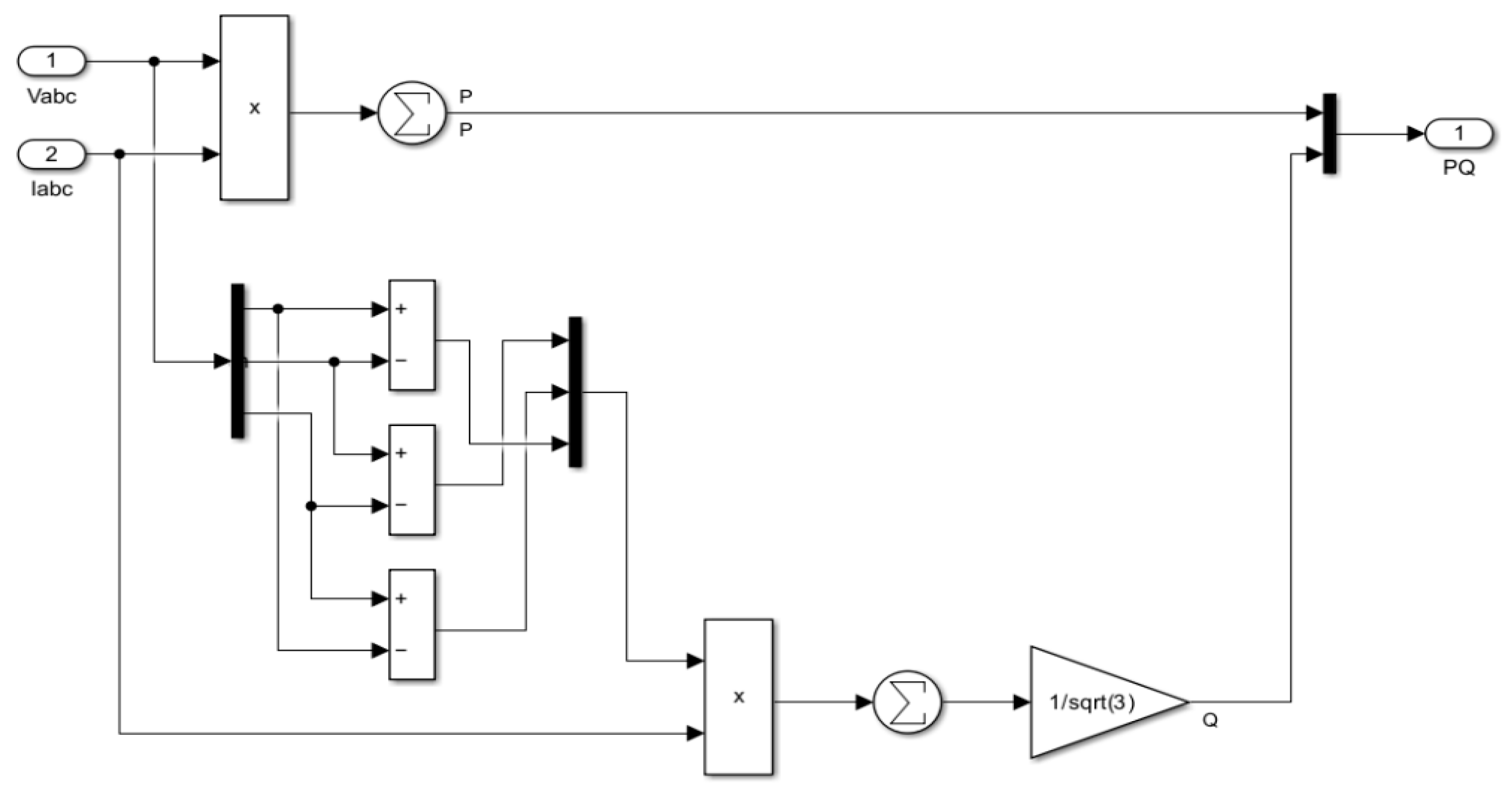

3.3. Power Calculations

3.4. Direct Power Controller Block for Three-Level Inverter (DPC)

3.5. Direct Power Controller Block for Five-Level Inverter

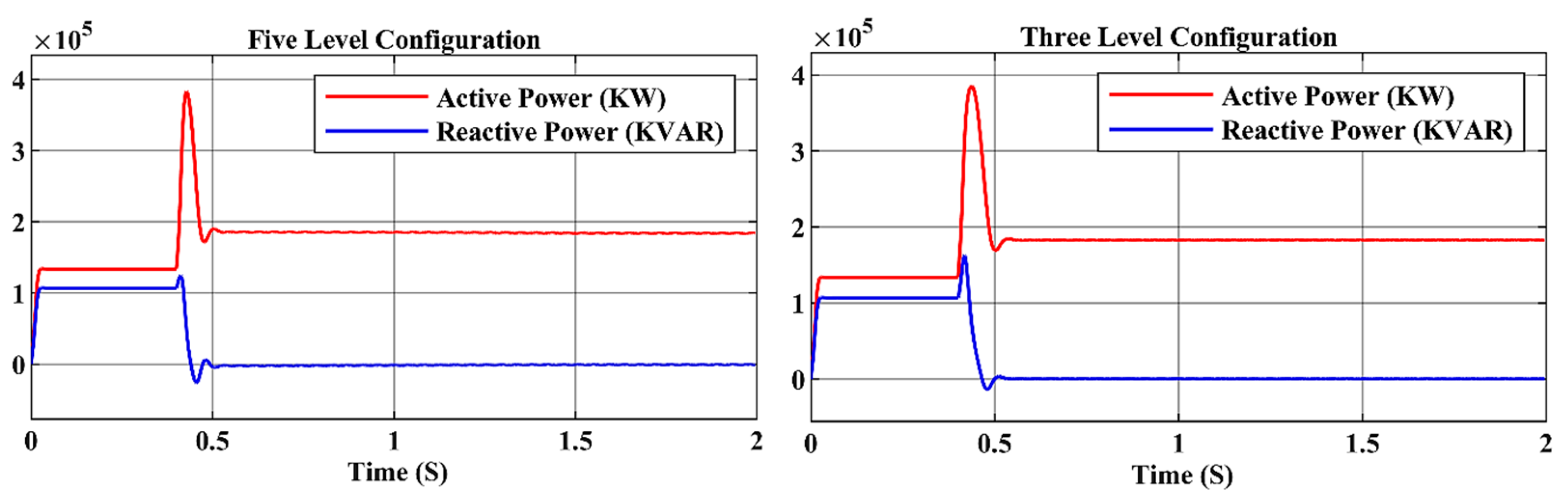

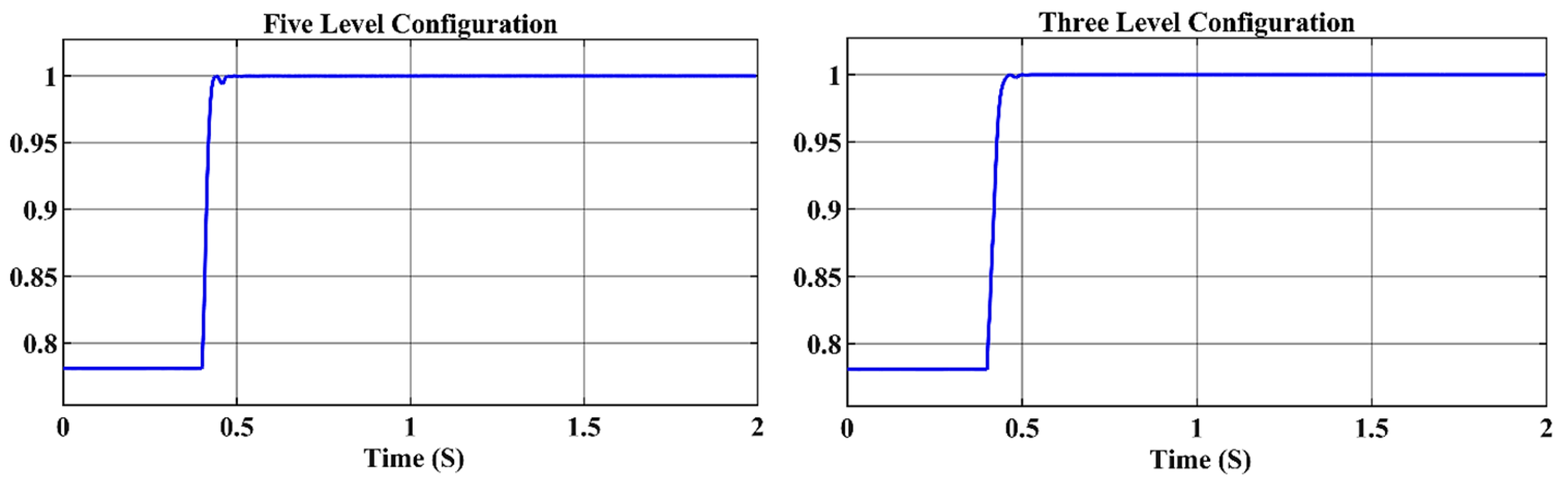

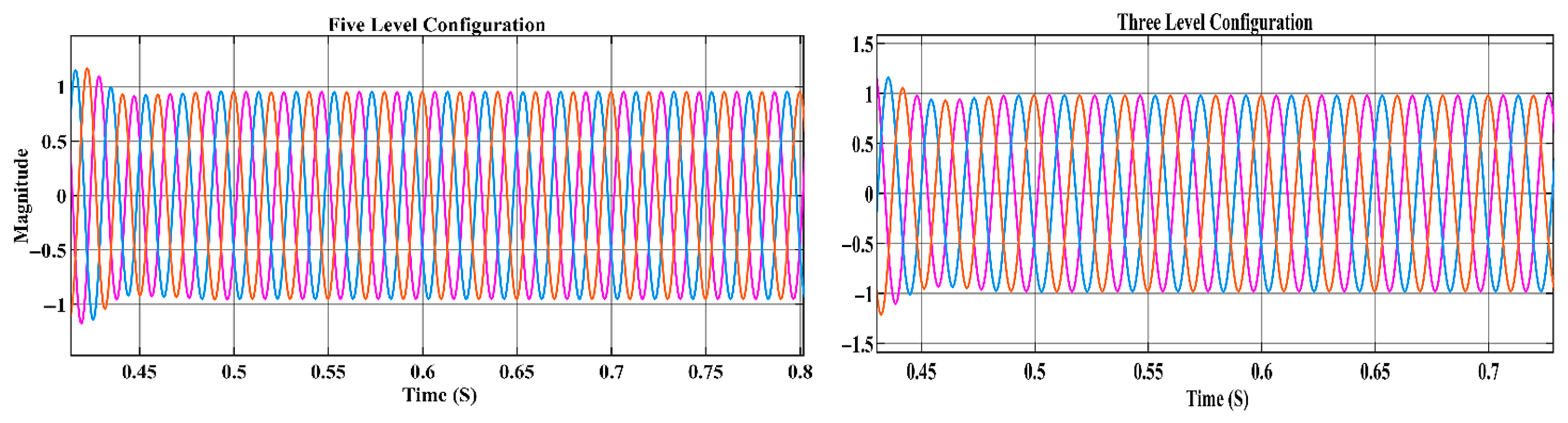

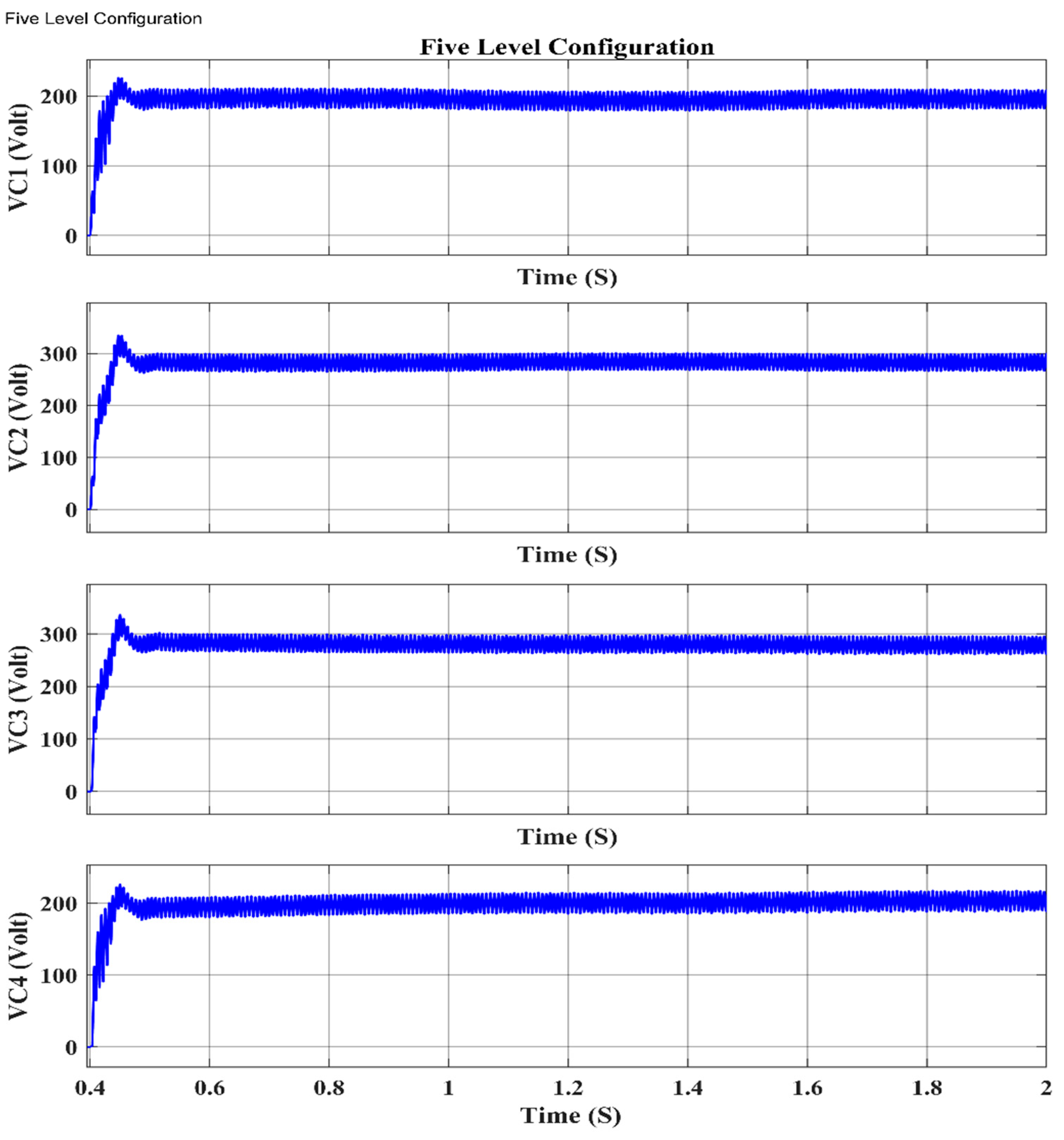

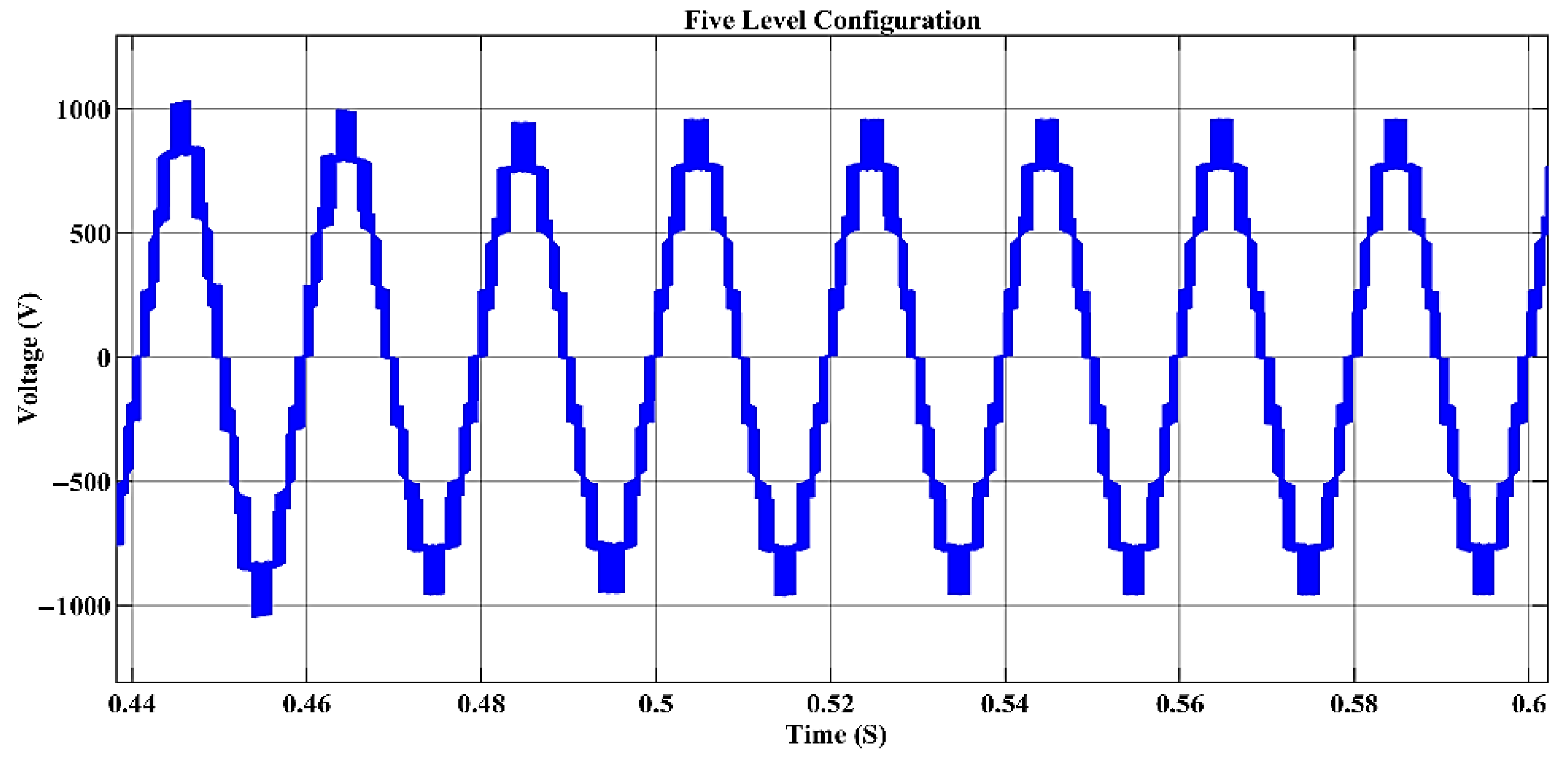

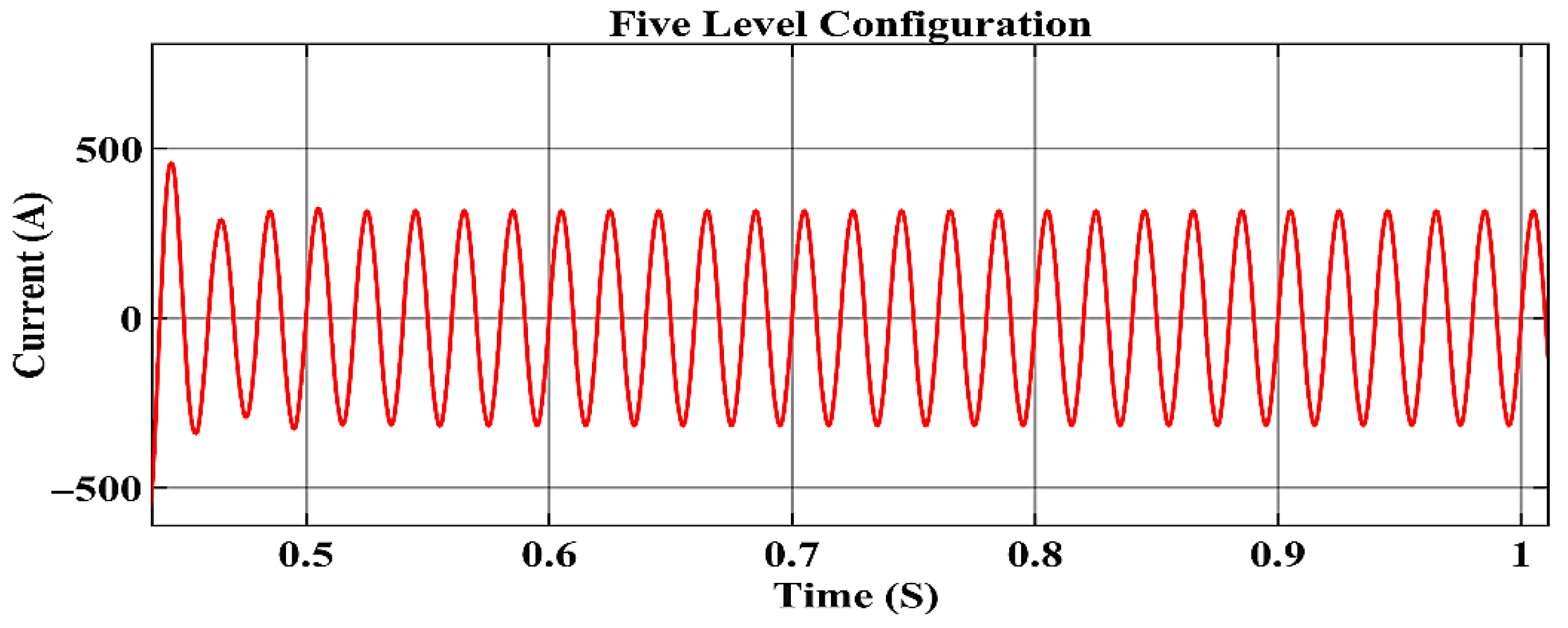

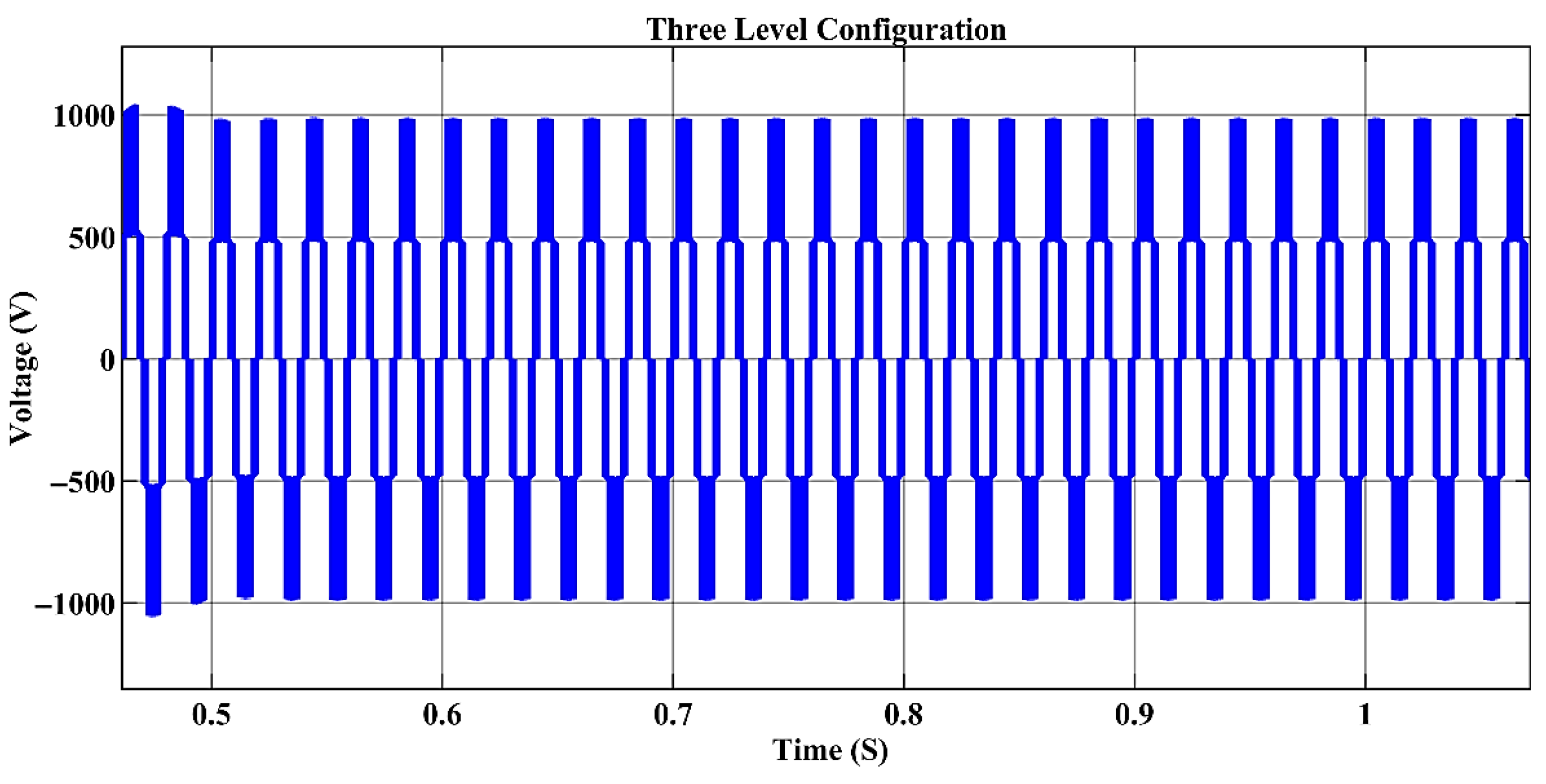

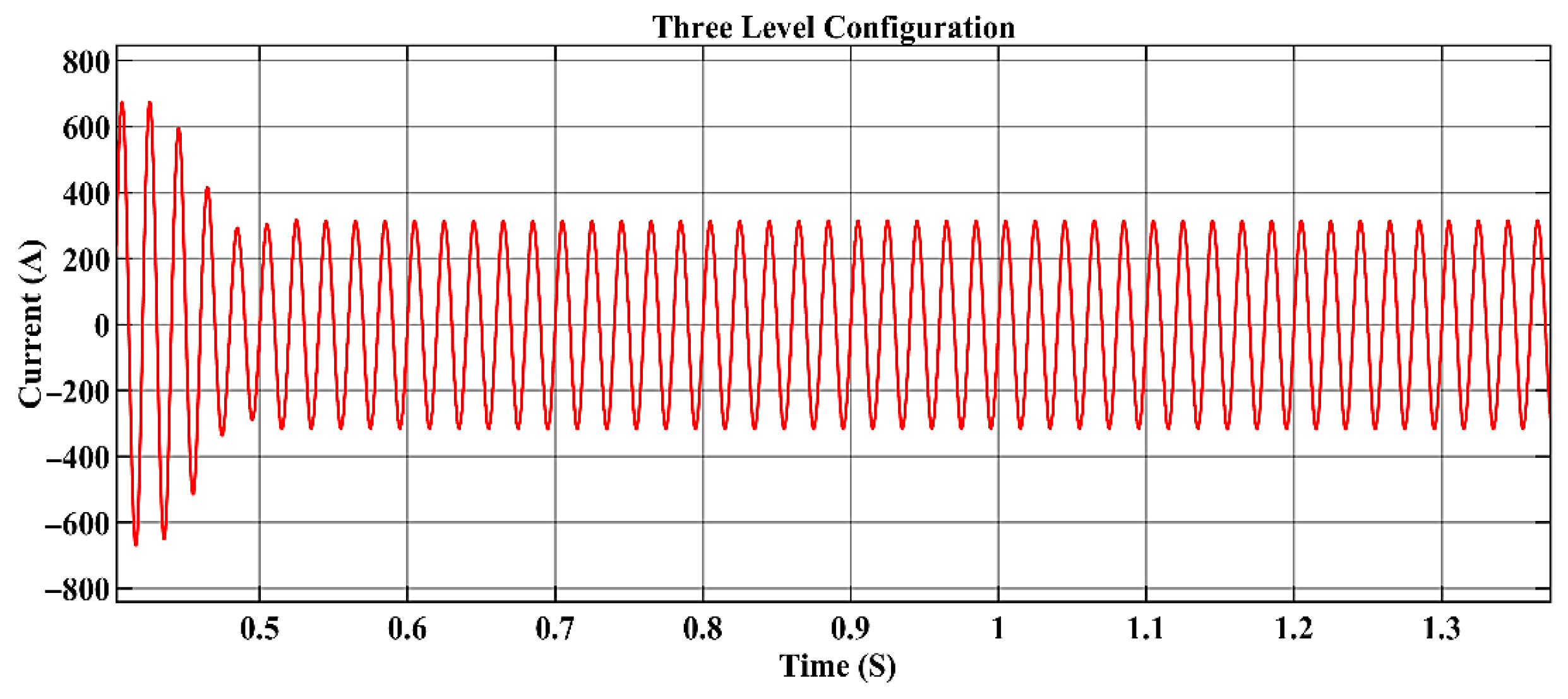

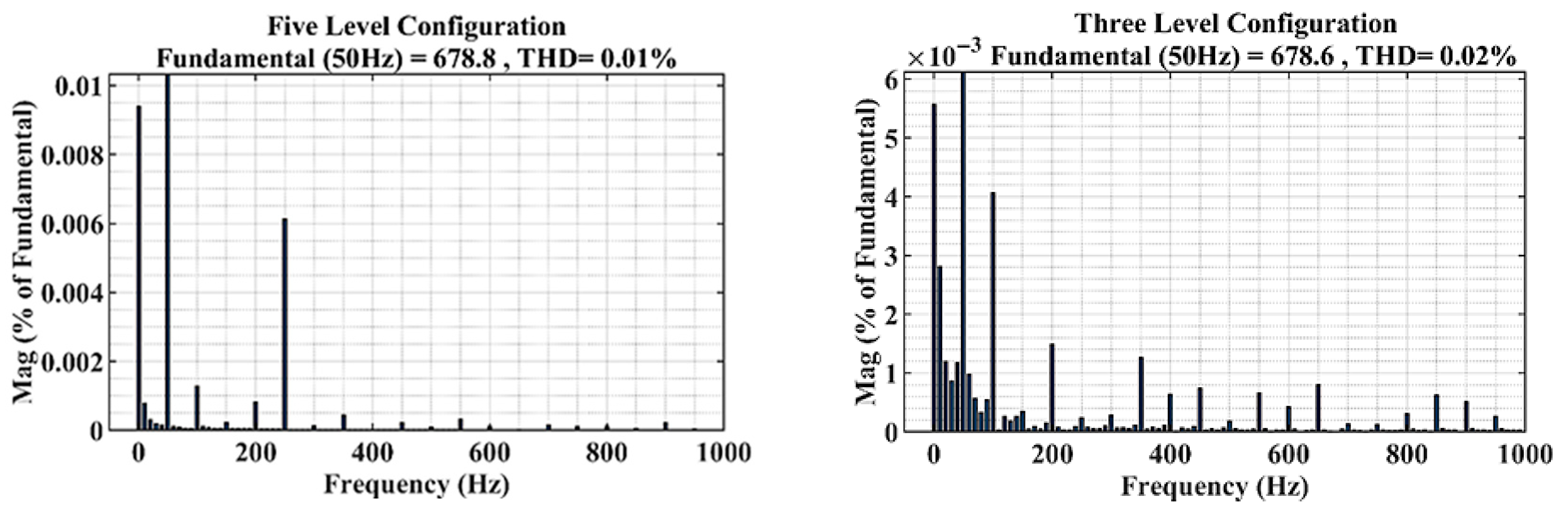

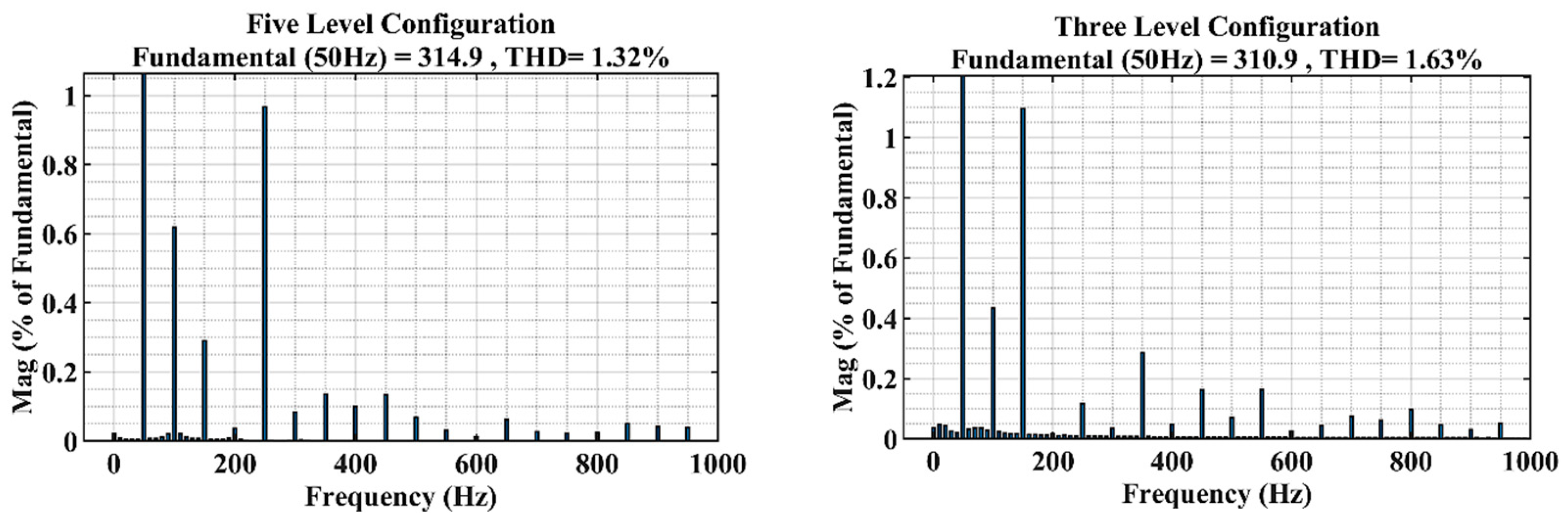

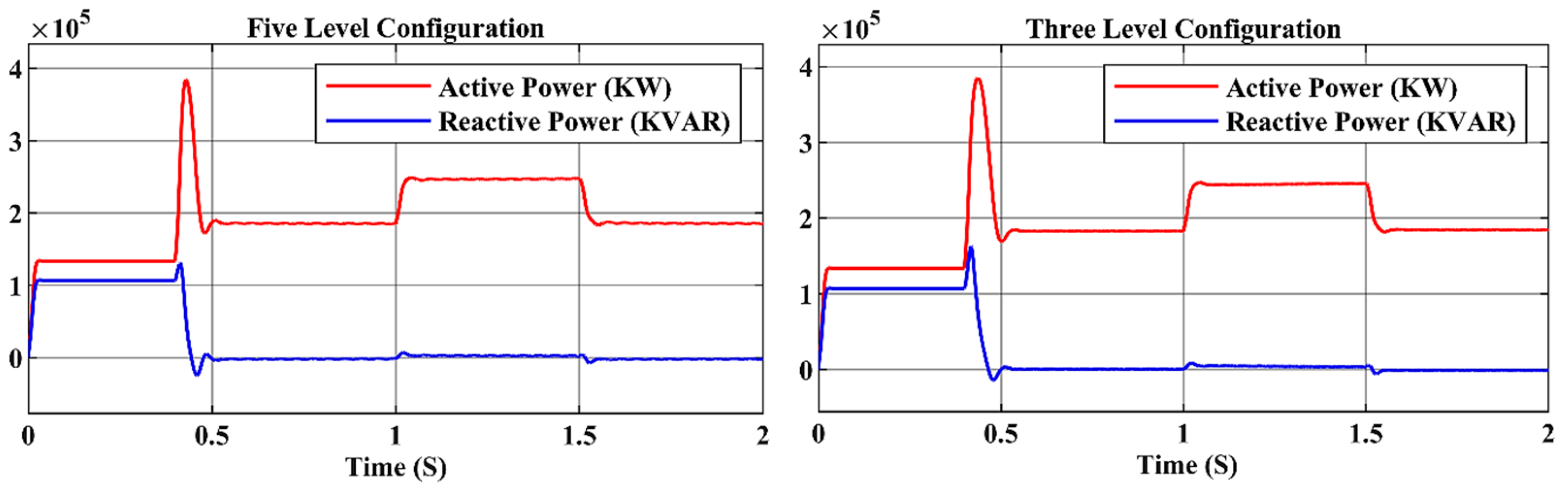

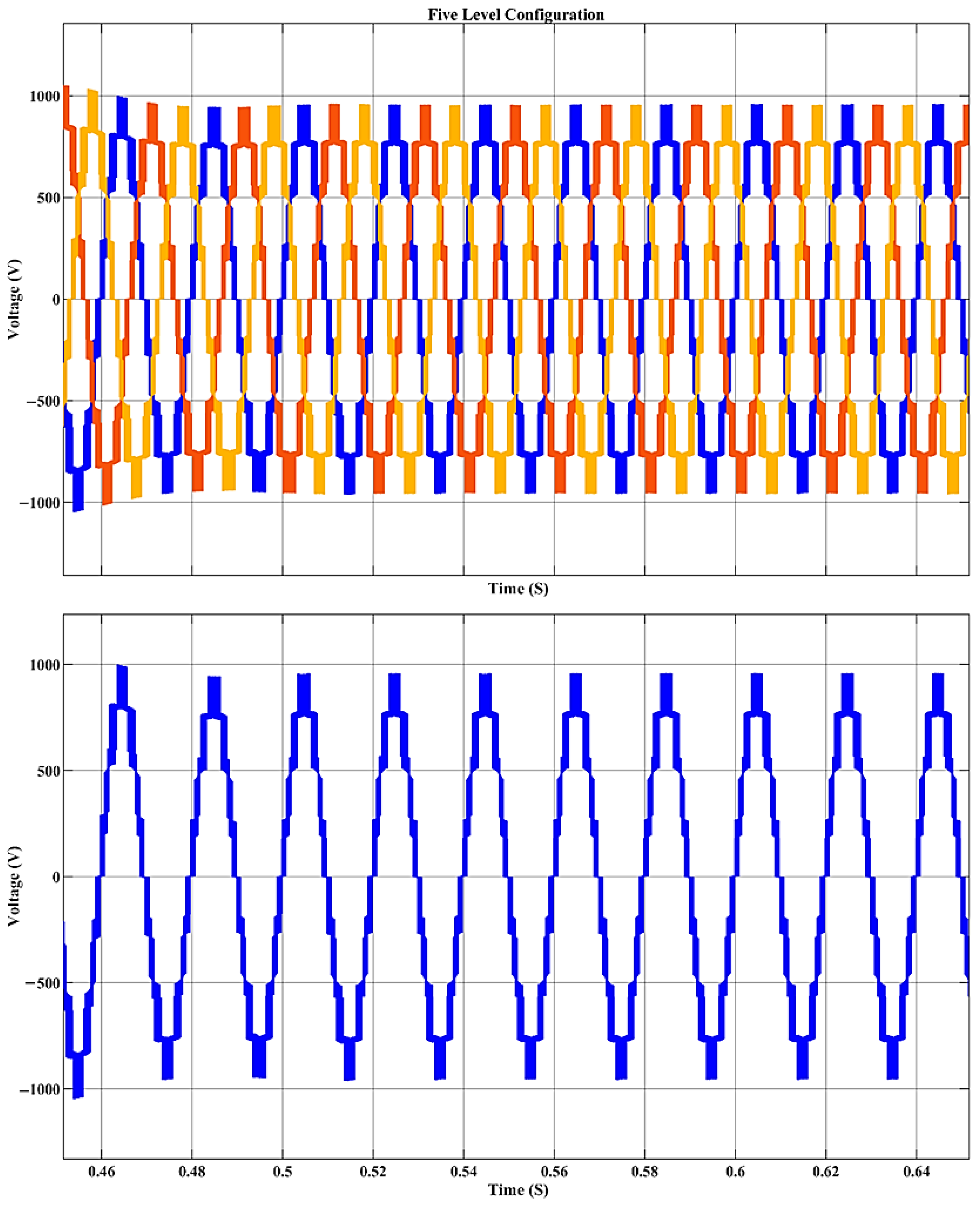

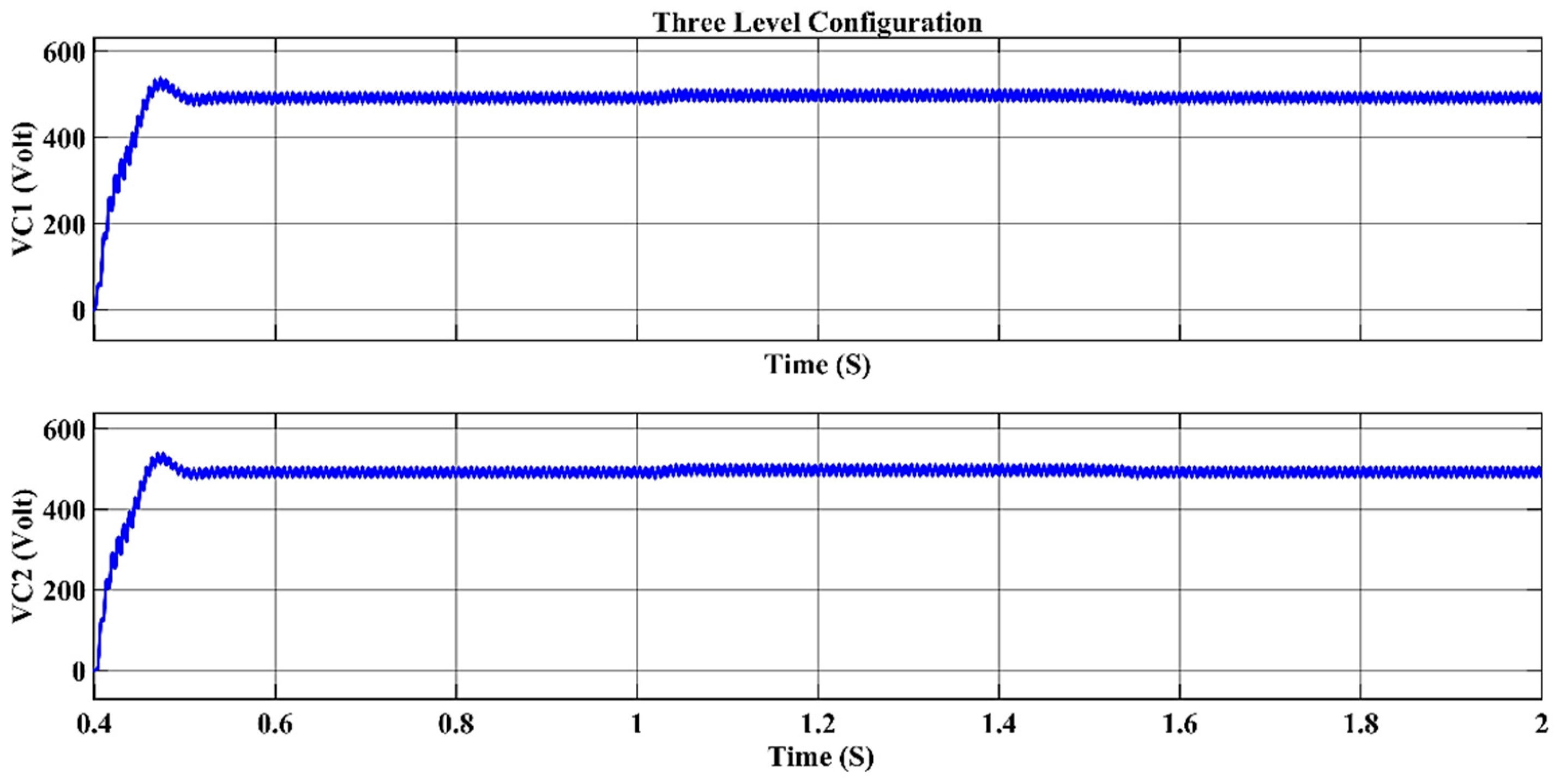

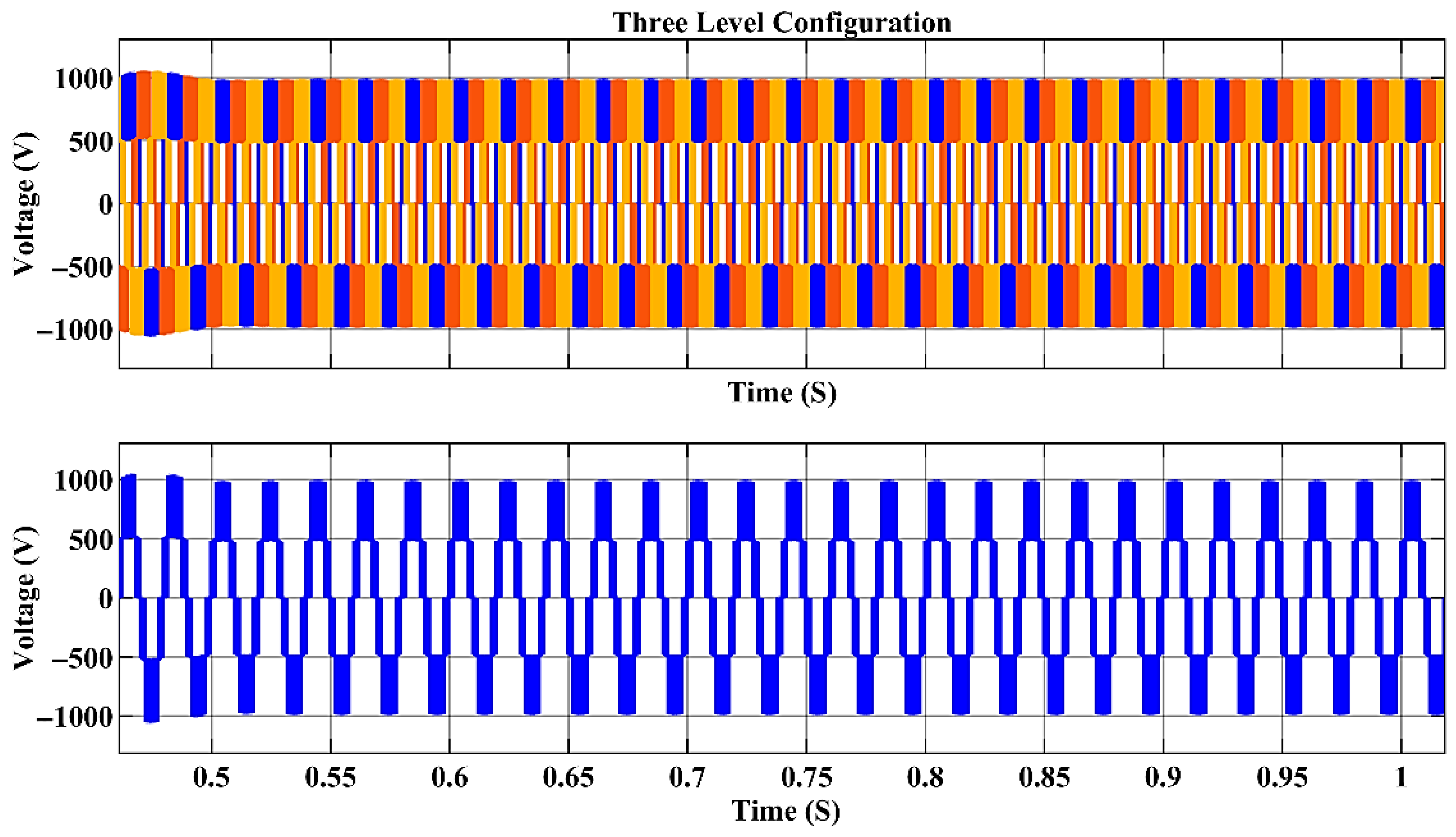

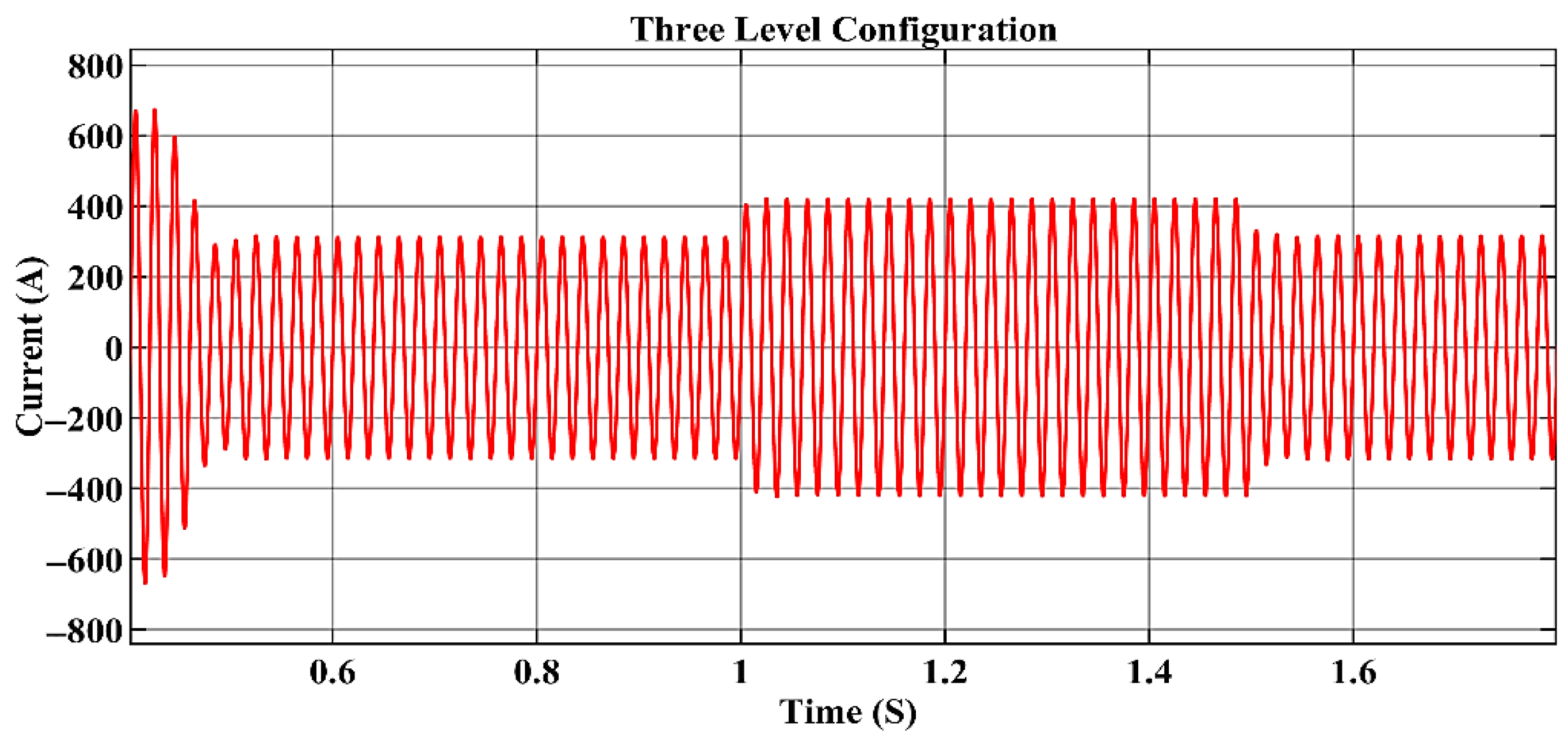

4. Results and Discussions

Trade-Off Analysis: Computational Complexity vs. Performance Metrics

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

Abbreviations

| MDPI | Multidisciplinary Digital Publishing Institute |

| DOAJ | Directory of open access journals |

| TLA | Three-letter acronym |

| LD | Linear dichroism |

References

- Blaabjerg, F.; Teodorescu, R.; Liserre, M.; Timbus, A.V. Overview of control and grid synchronization for distributed power generation systems. IEEE Trans. Ind. Electron. 2006, 53, 1398–1409. [Google Scholar] [CrossRef]

- Karthik, T.; Prathyusha, M.; Thirumalaivasan, R.; Janaki, M. Power quality improvement using DSTATCOM. In Proceedings of the 2019 Innovations in Power and Advanced Computing Technologies (i-PACT), Vellore, India, 22–23 March 2019. [Google Scholar]

- Akagi, H.; Watanabe, E.H.; Aredes, M. Instantaneous Power Theory and Applications to Power Conditioning; John Wiley & Sons: Hoboken, NJ, USA, 2017. [Google Scholar]

- Muñoz, J.A.; Espinoza, J.R.; Baier, C.R.; Morán, L.A.; Espinosa, E.E.; Melin, P.E.; Sbarbaro, D.G. Design of a discrete-time linear control strategy for a multicell UPQC. IEEE Trans. Ind. Electron. 2011, 59, 3797–3807. [Google Scholar] [CrossRef]

- Singh, B.; Al-Haddad, K.; Chandra, A. A review of active filters for power quality improvement. IEEE Trans. Ind. Electron. 1999, 46, 960–971. [Google Scholar] [CrossRef]

- Bozorgi, A.M.; Gholami-Khesht, H.; Farasat, M.; Mehraeen, S.; Monfared, M. Model predictive direct power control of three-phase grid-connected converters with fuzzy-based duty cycle modulation. IEEE Trans. Ind. Appl. 2018, 54, 4875–4885. [Google Scholar] [CrossRef]

- Kouro, S.; Malinowski, M.; Gopakumar, K.; Pou, J.; Franquelo, L.G.; Wu, B.; Rodriguez, J.; Pérez, M.A.; Leon, J.I. Recent advances and industrial applications of multilevel converters. IEEE Trans. Ind. Electron. 2010, 57, 2553–2580. [Google Scholar] [CrossRef]

- Nabae, A.; Takahashi, I.; Akagi, H. A new neutral-point-clamped PWM inverter. IEEE Trans. Ind. Appl. 1981, IA-17, 518–523. [Google Scholar] [CrossRef]

- Malinowski, M.; Gopakumar, K.; Rodriguez, J.; Perez, M.A. A survey on cascaded multilevel inverters. IEEE Trans. Ind. Electron. 2009, 57, 2197–2206. [Google Scholar] [CrossRef]

- Liu, J.; Zhou, L.; Yu, X.; Li, B.; Zheng, C. Design and analysis of an LCL circuit-based three-phase grid-connected inverter. IET Power Electron. 2017, 10, 232–239. [Google Scholar] [CrossRef]

- Bonaldo, J.P.; de Arimatéia Olímpio Filho, J.; dos Santos Alonso, A.M.; Paredes, H.K.M.; Marafão, F.P. Modeling and control of a single-phase grid-connected inverter with lcl filter. IEEE Lat. Am. Trans. 2021, 19, 250–259. [Google Scholar] [CrossRef]

- Busquets-Monge, S.; Rocabert, J.; Rodriguez, P.; Alepuz, S.; Bordonau, J. Multilevel diode-clamped converter for photovoltaic generators with independent voltage control of each solar array. IEEE Trans. Ind. Electron. 2008, 55, 2713–2723. [Google Scholar] [CrossRef]

- Rodriguez, J.; Lai, J.-S.; Peng, F.Z. Multilevel inverters: A survey of topologies, controls, and applications. IEEE Trans. Ind. Electron. 2002, 49, 724–738. [Google Scholar] [CrossRef]

- Abu-Rub, H.; Holtz, J.; Rodriguez, J.; Baoming, G. Medium-voltage multilevel converters—State of the art, challenges, and requirements in industrial applications. IEEE Trans. Ind. Electron. 2010, 57, 2581–2596. [Google Scholar] [CrossRef]

- Badoni, M.; Singh, A.; Singh, B. Power quality improvement using DSTATCOM with affine projection algorithm. IET Gener. Transm. Distrib. 2018, 12, 3261–3269. [Google Scholar] [CrossRef]

- Chen, J.-H.; Tan, K.-H.; Lee, Y.-D. Intelligent controlled DSTATCOM for power quality enhancement. Energies 2022, 15, 4017. [Google Scholar] [CrossRef]

- Khariy, A.H.; Ajel, A.R.; Gharghan, S.K.; Noaman Mohammad, N. Grid-Connected PV System for 324 kW with Improved Maximum PowerPoint Tracking. J. Tech. 2023, 5, 20–31. [Google Scholar] [CrossRef]

- Balogun, A.; Agoro, S.; Sunday, A.; Olajube, A.; Okafor, F. An Efficiency Optimized Direct Model Predictive Control of Induction Machine Drive. J. Tech. 2024, 6, 76–84. [Google Scholar] [CrossRef]

- Peng, F.Z.; Lai, J.-S. Generalized instantaneous reactive power theory for three-phase power systems. IEEE Trans. Instrum. Meas. 1996, 45, 293–297. [Google Scholar] [CrossRef]

- Zhang, Y.; Zhang, W.; Gao, F.; Gao, S.; Rogers, D.J. A switched-capacitor interleaved bidirectional converter with wide voltage-gain range for super capacitors in EVs. IEEE Trans. Power Electron. 2019, 35, 1536–1547. [Google Scholar] [CrossRef]

- Maurya, V.K.; Pandey, J.; Gaur, C.; Singh, S. Original Research Article Design analysis of intelligent controller to minimize harmonic distortion and power loss of wind energy conversion system (grid connected). J. Auton. Intell. 2024, 7. [Google Scholar] [CrossRef]

- Ahmad, S.; Mekhilef, S.; Mokhlis, H.; Karimi, M.; Pourdaryaei, A.; Ahmed, T.; Jhuma, U.K.; Afzal, S. Fuzzy logic-based direct power control method for pv inverter of grid-tied ac microgrid without phase-locked loop. Electronics 2021, 10, 3095. [Google Scholar] [CrossRef]

- Benbouhenni, H.; Bizon, N.; Mosaad, M.I.; Colak, I.; Djilali, A.B.; Gasmi, H. Enhancement of the power quality of DFIG-based dual-rotor wind turbine systems using fractional order fuzzy controller. Expert Syst. Appl. 2024, 238, 121695. [Google Scholar] [CrossRef]

- Chavali, R.V.; Dey, A.; Das, B. An abc Reference Frame Hysteresis Current Controller for Grid Connected Converter With Constant Switching Frequency Operation. IEEE Trans. Ind. Electron. 2024, 72, 1159–1169. [Google Scholar] [CrossRef]

- Blaabjerg, F.; Iov, F.; Kerekes, T.; Teodorescu, R.; Ma, K. Power electronics-key technology for renewable energy systems. In Proceedings of the 2011 2nd Power Electronics, Drive Systems and Technologies Conference, Tehran, Iran, 16–17 February 2011; pp. 445–466. [Google Scholar]

- Mirdas, Q.H.; Yasin, N.M.; Alshamaa, N.K. Grey wolf optimization-based improved closed-loop speed control for a 3-phase IM motor drive with SVPWM switching and V/f control. In Proceedings of the 2022 International Conference on Engineering & MIS (ICEMIS), Istanbul, Turkey, 4–6 July 2022; pp. 1–6. [Google Scholar]

- Rodríguez, J.; Bernet, S.; Wu, B.; Pontt, J.O.; Kouro, S. Multilevel voltage-source-converter topologies for industrial medium-voltage drives. IEEE Trans. Ind. Electron. 2007, 54, 2930–2945. [Google Scholar] [CrossRef]

- Perez, M.A.; Cortés, P.; Rodríguez, J. Predictive control algorithm technique for multilevel asymmetric cascaded H-bridge inverters. IEEE Trans. Ind. Electron. 2008, 55, 4354–4361. [Google Scholar] [CrossRef]

- Kouro, S.; Perez, M.A.; Rodriguez, J.; Llor, A.M.; Young, H.A. Model predictive control: MPC’s role in the evolution of power electronics. IEEE Ind. Electron. Mag. 2015, 9, 8–21. [Google Scholar] [CrossRef]

- Newman, M.J.; Holmes, D.G. Delta operator digital filters for high performance inverter applications. IEEE Trans. Power Electron. 2003, 18, 447–454. [Google Scholar] [CrossRef]

- Vazquez, S.; Rodriguez, J.; Rivera, M.; Franquelo, L.G.; Norambuena, M. Model predictive control for power converters and drives: Advances and trends. IEEE Trans. Ind. Electron. 2016, 64, 935–947. [Google Scholar] [CrossRef]

- Yasin, N.M. Simulation of Solar Cell and sinusoidal pulse width modulation inverter Using MATLAB and Proteus. In Proceedings of the 2019 4th Scientific International Conference Najaf (SICN), Najef, Iraq, 29–30 April 2019; pp. 86–91. [Google Scholar]

- Ghafour, Z.A.; Ajel, A.R.; Yasin, N.M. Super lift Luo converter using MPPT strategy for PV system. In Proceedings of the AIP Conference Proceedings, Baghdad, Iraq, 15–16 June 2022. [Google Scholar]

- Dardabi, C.; Álvarez, S.C.; Djebli, A. An Artificial-Neural-Network-Based Direct Power Control Approach for Doubly Fed Induction Generators in Wind Power Systems. Energies 2025, 18, 1989. [Google Scholar] [CrossRef]

- Sheh Zad, H.; Ulasyar, A.; Zohaib, A.; Khattak, A. Adaptive sliding mode predictive power control of three-phase AC/DC converters. Proc. Inst. Mech. Eng. Part I J. Syst. Control. Eng. 2022, 236, 897–912. [Google Scholar] [CrossRef]

- Benbouhenni, H.; Zellouma, D.; Bizon, N.; Colak, I. A new PI (1+ PI) controller to mitigate power ripples of a variable-speed dual-rotor wind power system using direct power control. Energy Rep. 2023, 10, 3580–3598. [Google Scholar] [CrossRef]

- Benbouhenni, H.; Bizon, N. A new direct power control method of the DFIG-DRWT system using neural PI controllers and four-level neural modified SVM technique. J. Appl. Res. Technol. 2023, 21, 36–55. [Google Scholar] [CrossRef]

- Ahmad, S.; Jhuma, U.K.; Karimi, M.; Pourdaryaei, A.; Mekhilef, S.; Mokhlis, H.; Kauhaniemi, K. Direct power control based on point of common coupling voltage modulation for grid-tied AC microgrid PV inverter. IEEE Access 2022, 10, 109187–109202. [Google Scholar] [CrossRef]

- Alturki, Y.A.; Alhussainy, A.A.; Alghamdi, S.M.; Rawa, M. A Novel Point of Common Coupling Direct Power Control Method for Grid Integration of Renewable Energy Sources: Performance Evaluation among Power Quality Phenomena. Energies 2024, 17, 5111. [Google Scholar] [CrossRef]

- Yang, X.; Zhang, Z.; Xu, M.; Li, S.; Zhang, Y.; Zhu, X.-F.; Ouyang, X.; Alù, A. Digital non-Foster-inspired electronics for broadband impedance matching. Nat. Commun. 2024, 15, 4346. [Google Scholar] [CrossRef]

- Zhang, Y.; Yang, X.; Zhang, Z. High-Efficiency Broadband Electroacoustic Energy Conversion Using Non-Foster-Inspired Circuit and Adaptively Switched Capacitor. IEEE Trans. Ind. Electron. 2025. early access. [Google Scholar] [CrossRef]

- Zhang, Y.; Jiao, J.; Liu, J. Direct power control of PWM rectifiers with online inductance identification under unbalanced and distorted network conditions. IEEE Trans. Power Electron. 2019, 34, 12524–12537. [Google Scholar] [CrossRef]

- Singh, B.; Murthy, S.S.; Gupta, S. STATCOM-based voltage regulator for self-excited induction generator feeding nonlinear loads. IEEE Trans. Ind. Electron. 2006, 53, 1437–1452. [Google Scholar] [CrossRef]

- Kouro, S.; Cortés, P.; Vargas, R.; Ammann, U.; Rodríguez, J. Model predictive control—A simple and powerful method to control power converters. IEEE Trans. Ind. Electron. 2008, 56, 1826–1838. [Google Scholar] [CrossRef]

- Sguarezi, A. Model Predictive Control for Doubly-Fed Induction Generators and Three-Phase Power Converters; Elsevier: Amsterdam, The Netherlands, 2022. [Google Scholar]

- Tawfiq, K.B.; Sergeant, P.; Mansour, A.S. Comparative Analysis of Space Vector Pulse-Width Modulation Techniques of Three-Phase Inverter to Minimize Common Mode Voltage and/or Switching Losses. Mathematics 2024, 12, 2832. [Google Scholar] [CrossRef]

- Shyaa, S.S.; Hassan, R.F. Design and Software Implementation of Multilevel Diode Clamped Converter. In Proceedings of the IOP Conference Series: Materials Science and Engineering, Baghdad, Iraq, 15 April 2020; p. 012140. [Google Scholar]

- Dan, H.; Peng, T.; Su, M.; Sun, Y.; Zhang, G.; Xiong, W. Implementation of phase disposition modulation method for the three-level diode-clamped matrix converter. IET Power Electron. 2015, 8, 2107–2114. [Google Scholar] [CrossRef]

- Ben Mahmoud, Z.; Khedher, A. A Comprehensive Review on Space Vector Based-PWM Techniques for Common Mode Voltage Mitigation in Photovoltaic Multi-Level Inverters. Energies 2024, 17, 916. [Google Scholar] [CrossRef]

- Arora, S.; Balsara, P.T.; Bhatia, D. Digital pulsewidth modulation (DPWM) using direct digital synthesis. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 10, 4231–4244. [Google Scholar] [CrossRef]

- Kasim, M.Q.; Hassan, R.F. Reduced computational burden model predictive current control of asymmetric stacked multi-level inverter based STATCOM. In Proceedings of the 2021 IEEE International Conference on Automatic Control & Intelligent Systems (I2CACIS), Shah Alam, Malaysia, 26 June 2021; pp. 374–379. [Google Scholar]

- Kasim, M.Q.; Hassan, R.F. Active voltage balancing strategy of asymmetric stacked multilevel inverter. Indones. J. Electr. Eng. Comput. Sci. 2021, 23, 665–674. [Google Scholar] [CrossRef]

- Busquets-Monge, S.; Alepuz, S.; Bordonau, J.; Peracaula, J. Voltage balancing control of diode-clamped multilevel converters with passive front-ends. IEEE Trans. Power Electron. 2008, 23, 1751–1758. [Google Scholar] [CrossRef]

- Taha, S.A.; Al-Sagar, Z.S.; Abdulsada, M.A.; Alruwaili, M.; Ibrahim, M.A. Design of an Efficient MPPT Topology Based on a Grey Wolf Optimizer-Particle Swarm Optimization (GWO-PSO) Algorithm for a Grid-Tied Solar Inverter Under Variable Rapid-Change Irradiance. Energies 2025, 18, 1997. [Google Scholar] [CrossRef]

- Mahato, B.; Majumdar, S.; Jana, K.C. Carrier-based PWM techniques for multi-level inverters: A comprehensive performance study. Gazi Univ. J. Sci. Part A Eng. Innov. 2018, 5, 101–111. [Google Scholar]

- Ramasamy, T.; Abdul Basheer, A.; Tak, M.-H.; Joo, Y.-H.; Lee, S.-R. An effective dc-link voltage control strategy for grid-connected PMVG-based wind energy conversion system. Energies 2022, 15, 2931. [Google Scholar] [CrossRef]

- Zhang, Y.; Wang, Z.; Jiao, J.; Liu, J. Grid-voltage sensorless model predictive control of three-phase PWM rectifier under unbalanced and distorted grid voltages. IEEE Trans. Power Electron. 2019, 35, 8663–8672. [Google Scholar] [CrossRef]

- Lee, S.S.; Lim, C.S.; Lee, K.-B. Novel active-neutral-point-clamped inverters with improved voltage-boosting capability. IEEE Trans. Power Electron. 2019, 35, 5978–5986. [Google Scholar] [CrossRef]

- Gang, L.; Dafang, W.; Miaoran, W.; Cheng, Z.; Mingyu, W. Neutral-point voltage balancing in three-level inverters using an optimized virtual space vector PWM with reduced commutations. IEEE Trans. Ind. Electron. 2018, 65, 6969. [Google Scholar]

- Alonso-Martı, J.; Arnaltes, S. Direct power control of grid connected PV systems with three level NPC inverter. Sol. Energy 2010, 84, 1175–1186. [Google Scholar] [CrossRef]

- Langella, R.; Testa, A.; Alii, E. IEEE recommended practice and requirements for harmonic control in electric power systems. In IEEE Recommended Practice; IEEE: New York, NY, USA, 2014. [Google Scholar]

| Switching States | Phase A | Terminal Voltage | |||

|---|---|---|---|---|---|

| S1 | S2 | S3 | S4 | ||

| P | ON | ON | OFF | OFF | +Vdc/2 |

| O | OFF | ON | ON | OFF | 0 |

| N | OFF | OFF | ON | ON | −Vdc/2 |

| Switching States | Terminal Voltage | |||||||

|---|---|---|---|---|---|---|---|---|

| S1 | S2 | S3 | S4 | S5 | S6 | S7 | S8 | |

| ON | ON | ON | ON | OFF | OFF | OFF | OFF | Vdc/2 |

| OFF | ON | ON | ON | ON | OFF | OFF | OFF | Vdc/4 |

| OFF | OFF | ON | ON | ON | ON | OFF | OFF | 0 |

| OFF | OFF | OFF | ON | ON | ON | ON | OFF | −Vdc/4 |

| OFF | OFF | OFF | OFF | ON | ON | ON | ON | −Vdc/2 |

| Controller | Kp | Ki |

|---|---|---|

| PI_1 | 0.0001 | 0.00001 |

| PI_2 | 0.0005 | 0.00001 |

| PI_3 | 0.006 | 0.0094 |

| Parameter | Value | |

|---|---|---|

| DC-link voltage | 1000 V | |

| Utility line voltage | 480 V | |

| Utility frequency | 50 Hz | |

| Average switching frequency | 5 kHz | |

| Inverter loss resistance R | 1 mΩ | |

| Filter inverter side inductor | 2 mH | |

| Filter inverter side resistor | 0.8 Ω | |

| DC-link capacitor for three-level inverter | 8000 µF | |

| DC-link capacitor for five-level inverter | 5000 µF | |

| Load 1 Inductive load 0.78 lagging PF | Active Power | 100 kW |

| Reactive Power | 80 kVAR | |

| Load 2 Inductive load 0.98 lagging PF | Active Power | 40 kW |

| Reactive Power | 8 kvar | |

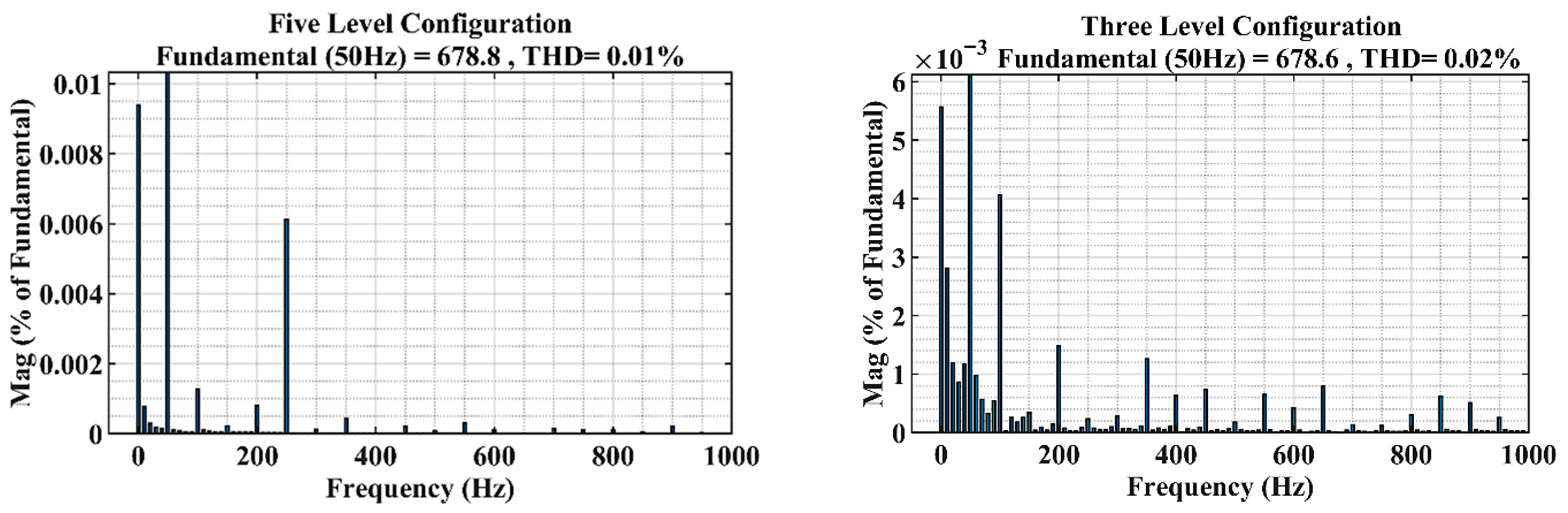

| Metric | 3-Level STATCOM | 5-Level STATCOM |

|---|---|---|

| Current THD | (0.4–1) s | (1–1.5) s |

| 1.86% | 1.16% | |

| Voltage THD after the filter | 0.02% | 0.01% |

| Reactive Power Settling Time | 35 ms | 20 ms |

| DC-Link Voltage Overshoot | 3.5% | 1.2% |

| Steady-State Power Factor | 0.985 | 0.998 |

| Computational Load | Low (8 switching states) | High (32 switching states) |

| 5-Level NPC (Per Phase Leg) | 3-Level NPC (Per Phase Leg) | Component |

|---|---|---|

| 8 | 4 | IGBTs/Switches |

| 12 | 2 | Diodes (clamping) |

| 4 | 2 | DC-Link Capacitors |

| 8 | 4 | Gate Driver Circuits |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Mohammed, D.M.; Hassan, R.F.; Yasin, N.M.; Alruwaili, M.; Ibrahim, M.A. A Comparative Study of Direct Power Control Strategies for STATCOM Using Three-Level and Five-Level Diode-Clamped Inverters. Energies 2025, 18, 3582. https://doi.org/10.3390/en18133582

Mohammed DM, Hassan RF, Yasin NM, Alruwaili M, Ibrahim MA. A Comparative Study of Direct Power Control Strategies for STATCOM Using Three-Level and Five-Level Diode-Clamped Inverters. Energies. 2025; 18(13):3582. https://doi.org/10.3390/en18133582

Chicago/Turabian StyleMohammed, Diyaa Mustaf, Raaed Faleh Hassan, Naseer M. Yasin, Mohammed Alruwaili, and Moustafa Ahmed Ibrahim. 2025. "A Comparative Study of Direct Power Control Strategies for STATCOM Using Three-Level and Five-Level Diode-Clamped Inverters" Energies 18, no. 13: 3582. https://doi.org/10.3390/en18133582

APA StyleMohammed, D. M., Hassan, R. F., Yasin, N. M., Alruwaili, M., & Ibrahim, M. A. (2025). A Comparative Study of Direct Power Control Strategies for STATCOM Using Three-Level and Five-Level Diode-Clamped Inverters. Energies, 18(13), 3582. https://doi.org/10.3390/en18133582