A Low Inrush Current Pre-Charging Strategy of M3C with Improved Nearest Level Modulation

Abstract

1. Introduction

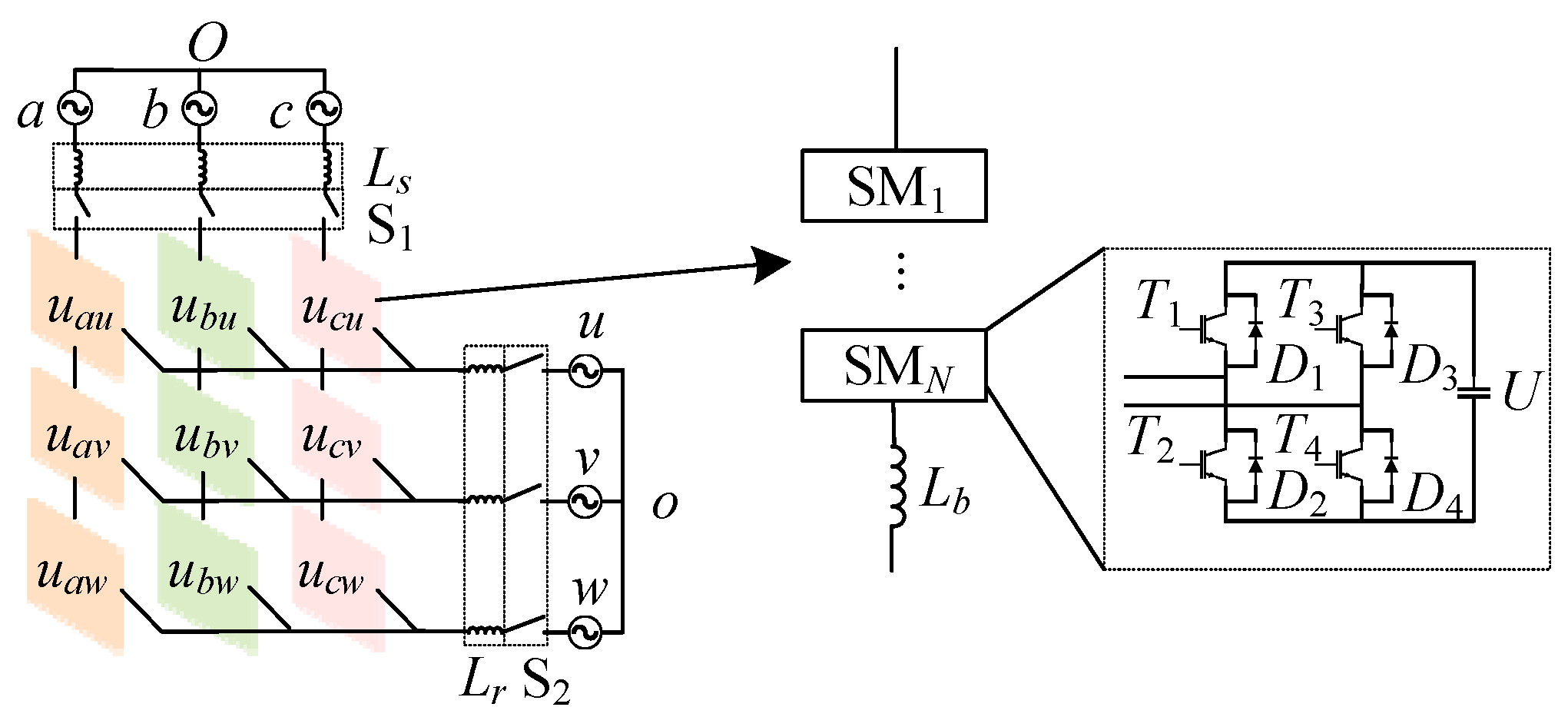

2. Operating Principles and Selection of Current-Limiting Resistors for M3C

2.1. The Mathematical Model of M3C

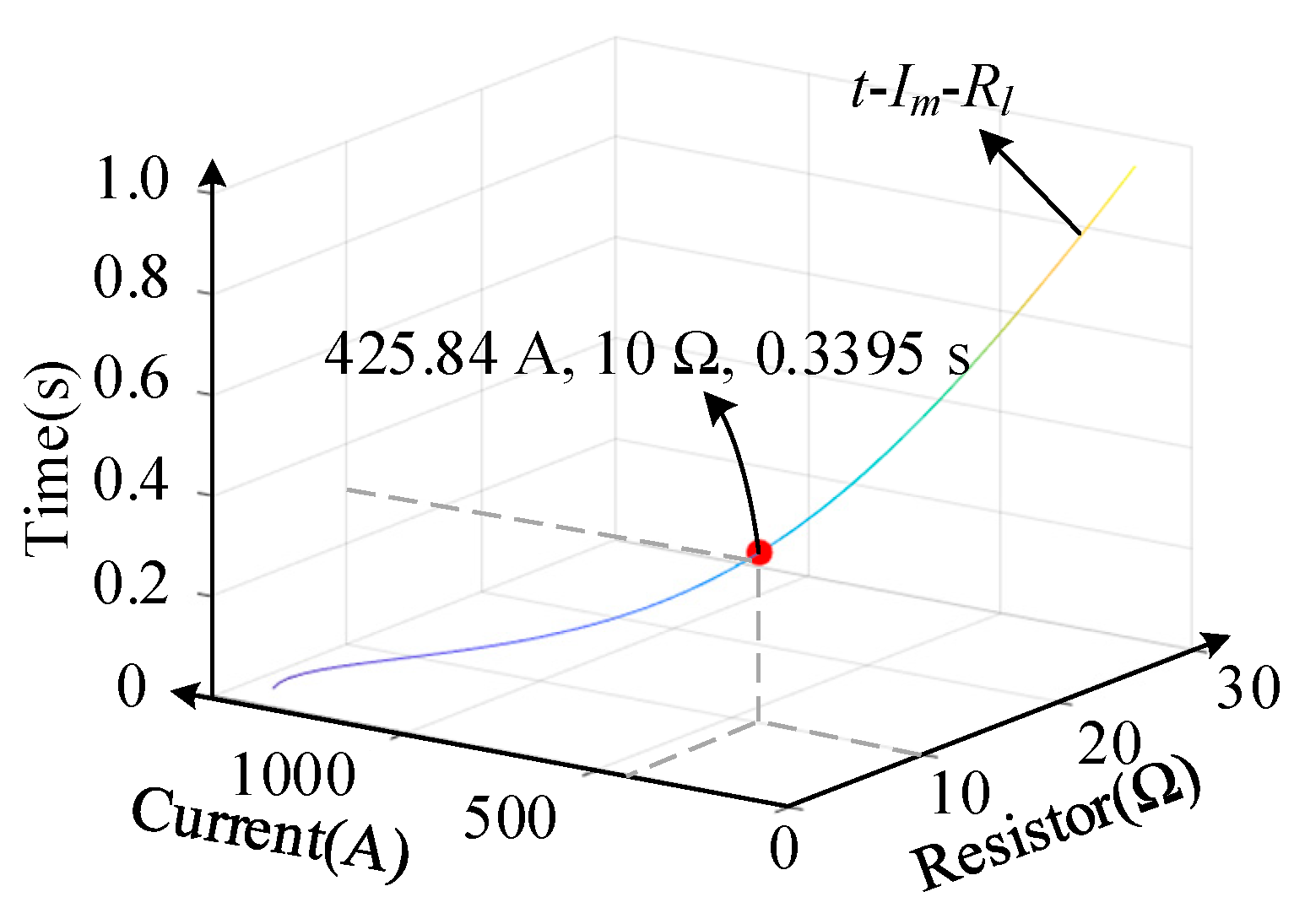

2.2. Selection of Current-Limiting Resistors

3. The NLM-Based Pre-Charging Strategy of M3C

3.1. Traditional NLM Pre-Charging Strategy

3.1.1. Number of SMs in Operation

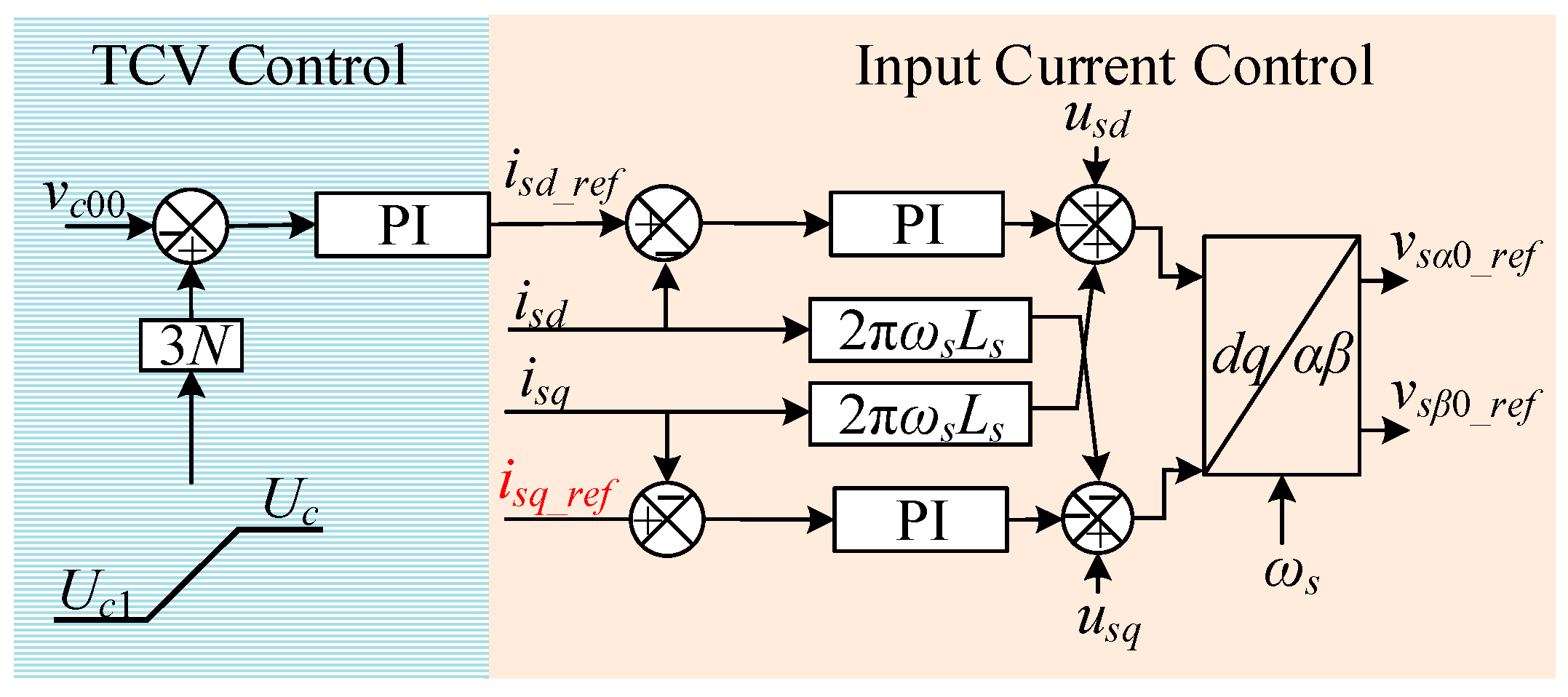

3.1.2. Input Reactive Current Compensation

3.2. Proposed NLM Pre-Charging Strategy

3.2.1. Quick-Sorting Algorithm

3.2.2. The M3C Pre-Charging Based on Improved NLM Strategy

4. Simulation Analysis

4.1. Simulation Parameters

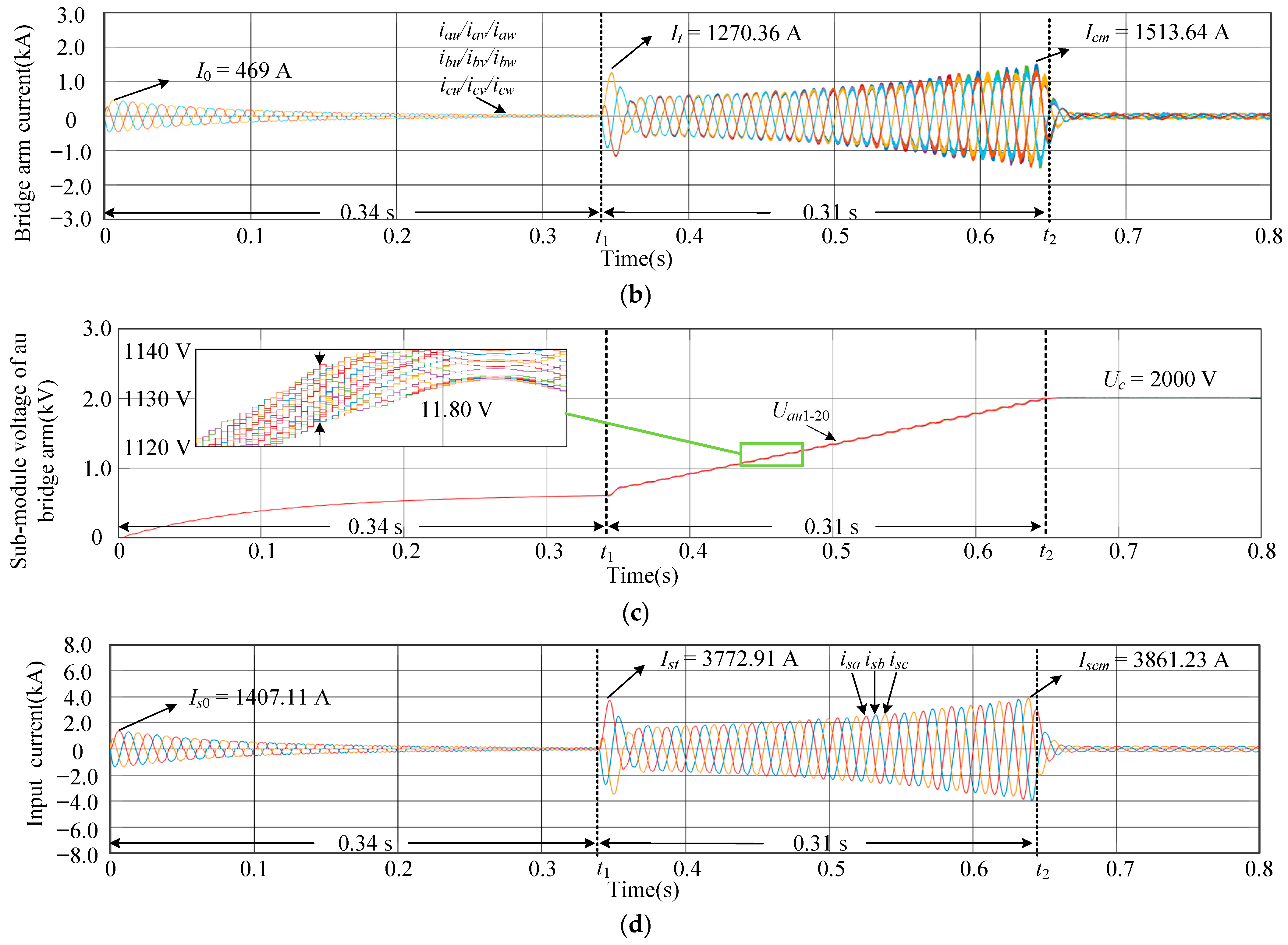

4.2. Pre-Charging of M3C Based on CPS-PWM Strategy

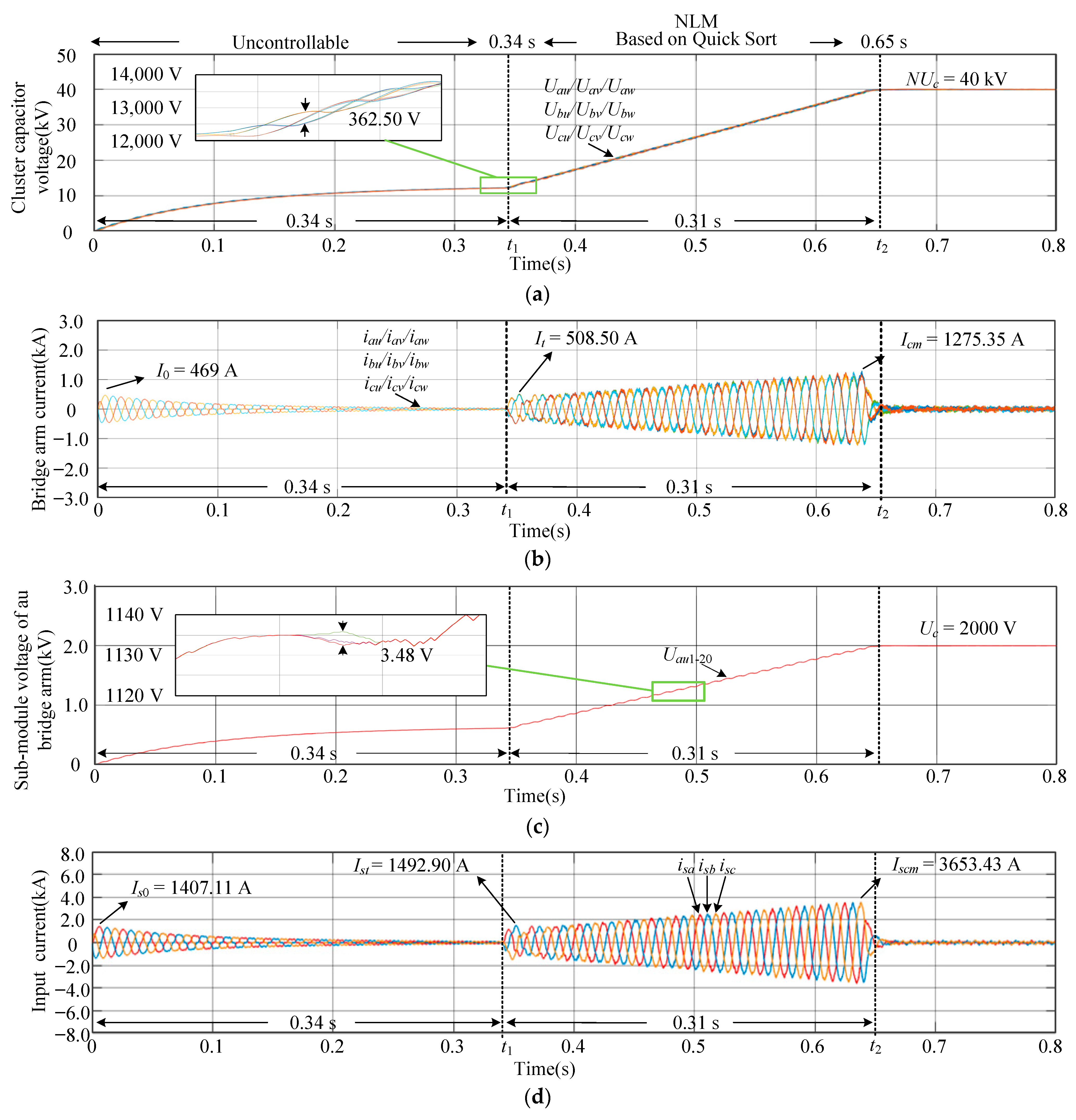

4.3. Pre-Charging of M3C Based on NLM Strategy with Quick-Sorting Algorithm

5. Experiment Validation

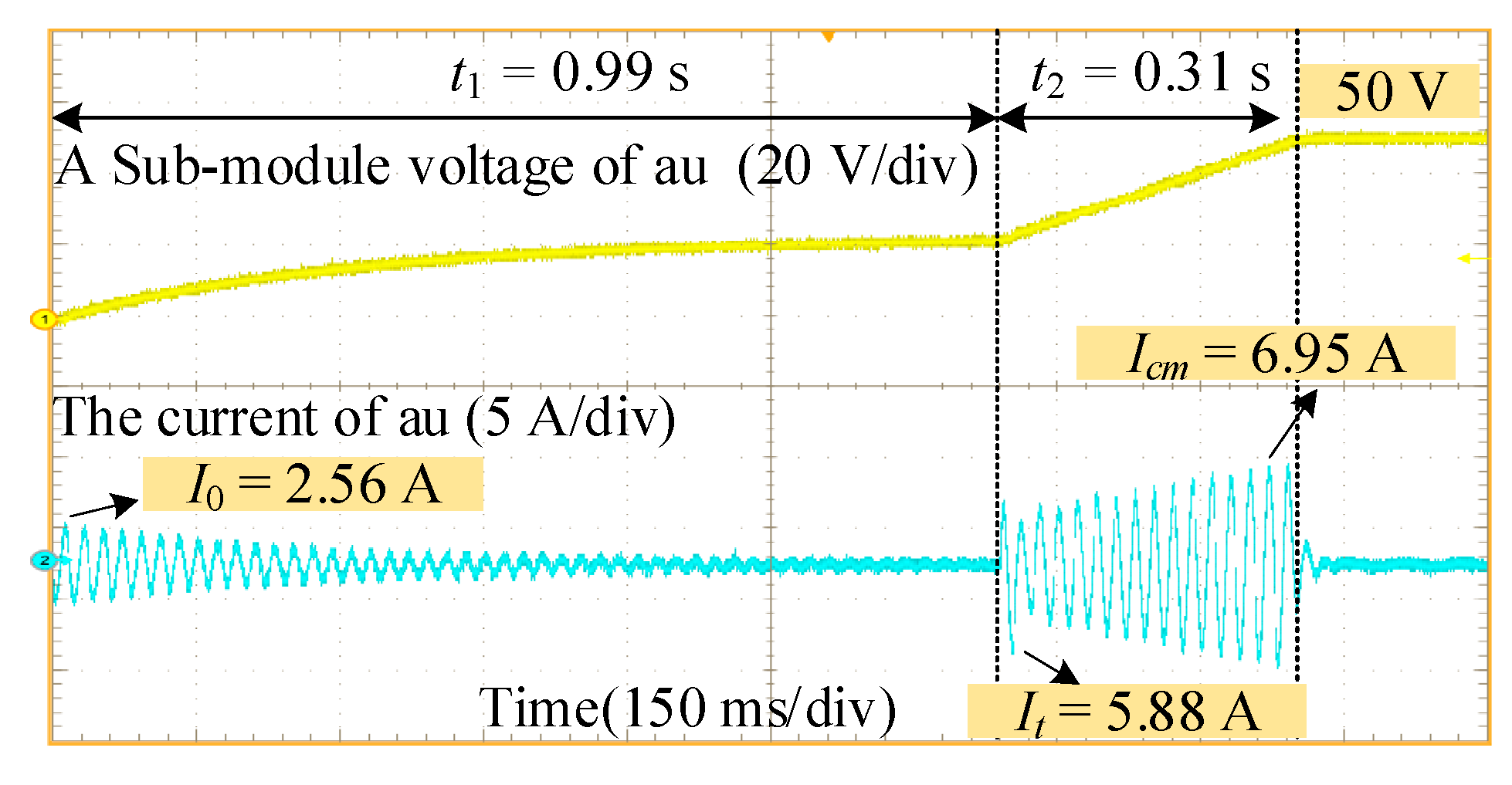

5.1. M3C Pre-Charging Strategy Based on CPS-PWM Strategy

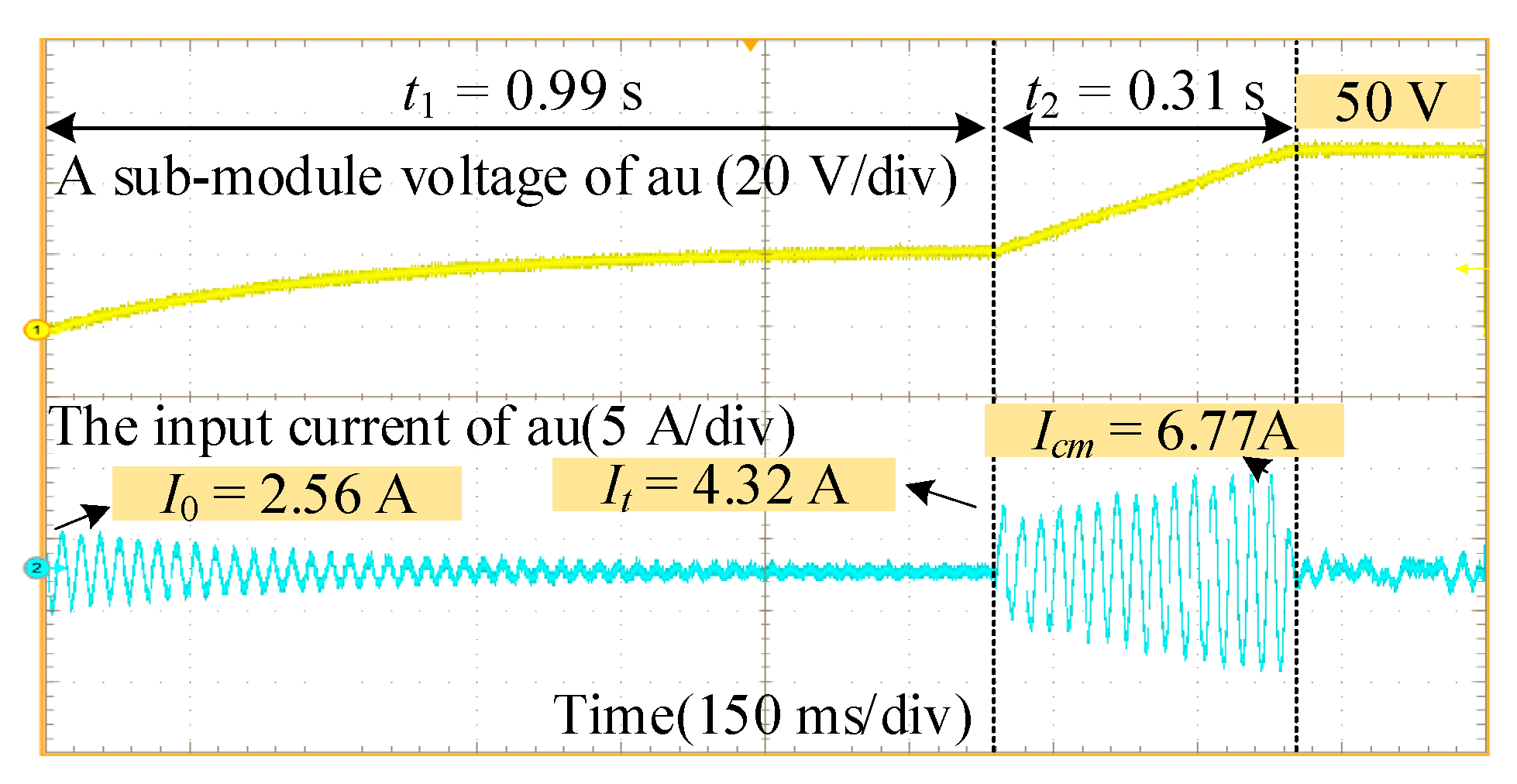

5.2. Bubble Sorting Algorithm-Based NLM Strategy

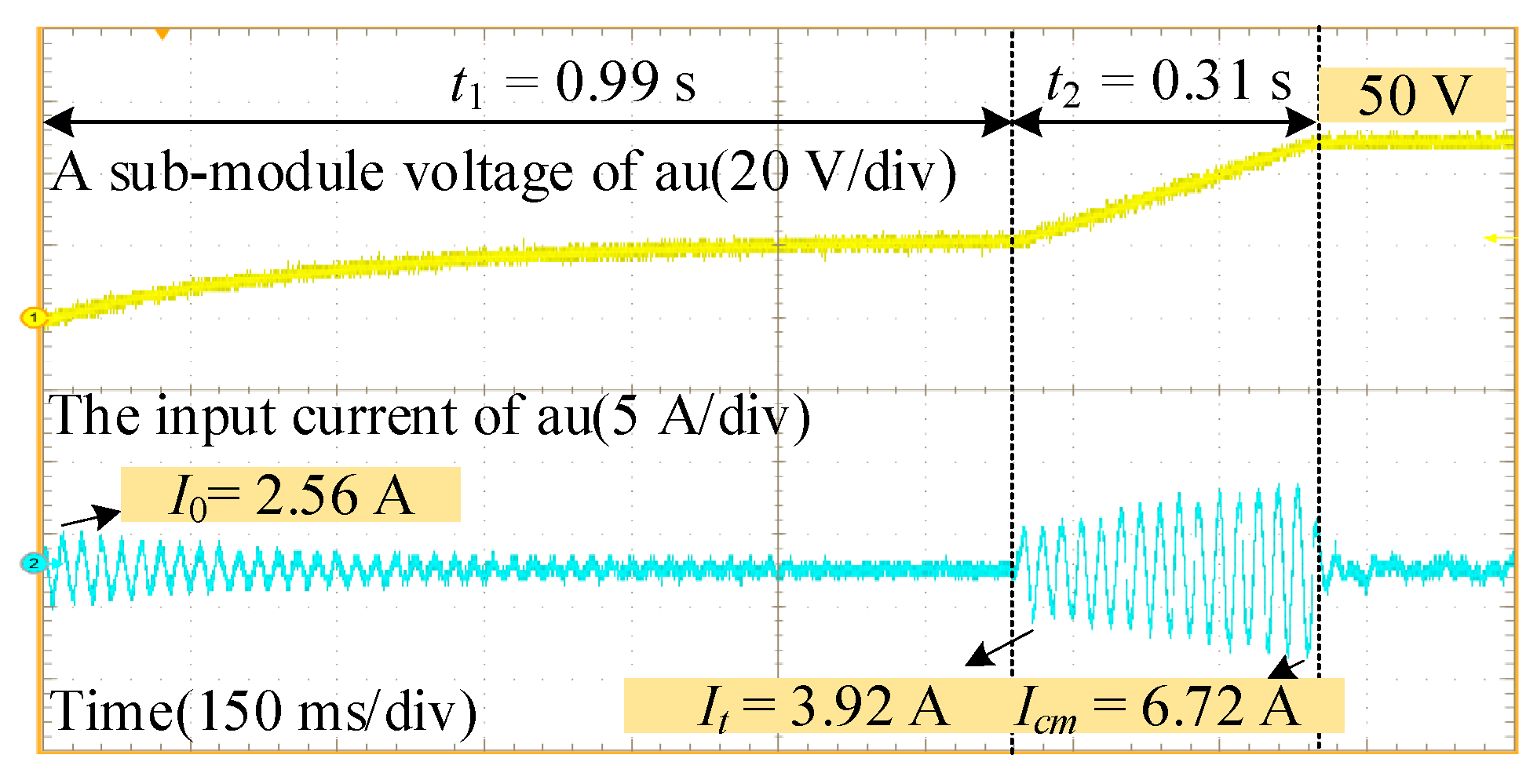

5.3. Quick-Sorting Algorithm-Based NLM Strategy

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Liu, S.; Zhao, B.; Wang, G.; Wang, X. An Improved Phasor Method for Modelling and Analysis of Modular Multilevel Matrix Converter. IEEE Trans. Power Del. 2021, 36, 1744–1755. [Google Scholar] [CrossRef]

- Yan, Y.; Sun, Y.; Teixeira, C.; Ma, J.; Asif, M. Enhanced dynamic voltage balance control of modular multilevel matrix converters with switched circulating current control. In Proceedings of the IEEE 9th International Power Electronics and Motion Control Conference (IPEMC2020-ECCE Asia), Nanjing, China, 29 November–2 December 2020; pp. 3391–3396. [Google Scholar]

- Sun, Y.; Yan, Y.; Teixeira, C.; Ma, J.; Asif, M. Inter-arm voltage balance control of a modular multilevel matrix converter with injecting dual frequency circulating current. In Proceedings of the IEEE 9th International Power Electronics and Motion Control Conference (IPEMC2020-ECCE Asia), Nanjing, China, 29 November–2 December 2020; pp. 2396–2401. [Google Scholar]

- Kawamura, W.; Chiba, Y.; Hagiwara, M.; Akagi, H. Experimental verification of TSBC-based electrical drives when the motor frequency is passing through, or equal to, the supply frequency. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Montreal, QC, Canada, 20–24 September 2015; pp. 5490–5497. [Google Scholar]

- Li, B.; Zhang, Y.; Xu, D.; Yang, R. Start-up control with constant precharge current for the modular multilevel converter. In Proceedings of the IEEE 23rd International Symposium on Industrial Electronics (ISIE), Istanbul, Turkey, 1–4 June 2014; pp. 673–676. [Google Scholar]

- Tian, K.; Wu, B.; Du, S.; Xu, D.; Cheng, Z.; Zargari, N.R. A simple and cost-effective precharge method for modular multilevel converters by using a low-voltage DC Source. IEEE Trans. Power Electron. 2016, 31, 5321–5329. [Google Scholar] [CrossRef]

- Huo, X.; Xie, X.; Wu, Z.; Dou, X. A novel strategy for DC distribution start-up based on MMC. In Proceedings of the IEEE Sustainable Power and Energy Conference (iSPEC), Beijing, China, 21–23 November 2019; pp. 952–956. [Google Scholar]

- Yan, F.; Wang, P.; Zhang, X.-P.; Xie, J.; Li, X.; Tang, C.; Zhao, Z. Coordinated start-up control and inter-converter oscillations damping for MMC-HVDC grid. IEEE Access 2019, 7, 65093–65102. [Google Scholar] [CrossRef]

- Zhu, K.; Deng, F.; Chen, S.; Hou, J.; Abulanwar, S.; Ufa, R. An AC-side start-up scheme for thyristor-based modular multilevel converters. In Proceedings of the IEEE International Power Electronics and Application Conference and Exposition (PEAC), Guangzhou, China, 4–7 November 2022; pp. 1426–1431. [Google Scholar]

- Dekka, A.; Wu, B.; Zargari, N.R. Start-up operation of a modular multilevel converter with flying capacitor submodules. IEEE Trans. Power Electron. 2017, 32, 5873–5877. [Google Scholar] [CrossRef]

- Das, A.; Nademi, H.; Norum, L. A method for charging and discharging capacitors in modular multilevel converter. In Proceedings of the 37th Annual Conference of the IEEE Industrial Electronics Society, Melbourne, VIC, Australia, 7–10 November 2011; pp. 1058–1062. [Google Scholar]

- Liu, W.; Li, K.-J.; Liu, Z.; Wang, M. A simple and novel precharging control strategy for modular multilevel converter. IEEE Access 2019, 7, 170500–170512. [Google Scholar] [CrossRef]

- Qin, J.; Debnath, S.; Saeedifard, M. Precharge strategy for soft startup process of modular multilevel converters based on various sm circuits. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 20–24 March 2016; pp. 1528–1533. [Google Scholar]

- Shi, K.; Shen, F.; Lv, D.; Lin, P.; Chen, M.; Xu, D. A novel start-up scheme for modular multilevel converter. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Raleigh, NC, USA, 15–20 September 2012; pp. 4180–4187. [Google Scholar]

- Xu, L.; Luo, Y.; Song, Y.; Blaabjerg, F. A smooth startup strategy for hybrid MMC based HVDC systems. Int. J. Electr. Power Energy Syst. 2021, 133, 0142–0615. [Google Scholar] [CrossRef]

- Li, B.; Xu, D.; Zhang, Y.; Yang, R.; Wang, G.; Wang, W.; Xu, D. Closed-loop precharge control of modular multilevel converters during start-up processes. IEEE Trans. Power Electron. 2015, 30, 524–531. [Google Scholar] [CrossRef]

- Wang, J.; Tang, Y.; Qi, Y.; Lin, P.; Zhang, Z. A unified startup strategy for modular multilevel converters with deadbeat predictive current control. IEEE Trans. Ind. Electron. 2021, 68, 6401–6411. [Google Scholar] [CrossRef]

- Li, A.; Lin, L.; Xu, C.; Hu, J. AC- and DC-side start-up strategies for half-/full-bridge hybrid modular multilevel converter. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition (APEC), San Antonio, TX, USA, 4–8 March 2018; pp. 3121–3126. [Google Scholar]

- Zhang, L.; Qin, J.; Wu, X.; Debnath, S.; Saeedifard, M. A generalized precharging strategy for soft startup process of the modular multilevel converter-based HVDC systems. IEEE Trans. Ind. Appl. 2017, 53, 5645–5657. [Google Scholar] [CrossRef]

- Bissal, A.; Ali, W. A fast acting precharge control strategy for modular multilevel converters. In Proceedings of the IEEE 13th International Conference on Power Electronics and Drive Systems (PEDS), Toulouse, France, 9–12 July 2019; pp. 1–4. [Google Scholar]

- Liu, W.; Li, G.; Ugalde-Loo, C.E.; Liang, J. Start-up strategy for modular multilevel converters with modified nearest level modulation method. In Proceedings of the 8th Renewable Power Generation Conference (RPG), Shanghai, China, 24–25 October 2019; pp. 1–6. [Google Scholar]

- Sarwer, Z.; Sarwar, A.; Zaid, M.; Hussan, M.R.; Tariq, M.; Alamri, B.; Alahmadi, A. Implementation of a novel variable structure nearest level modulation on cascaded H-bridge multilevel inverter. IEEE Access 2021, 9, 133974–133988. [Google Scholar] [CrossRef]

| Parameter | Value |

|---|---|

| Input grid voltage vs/kV | 11 |

| Output grid voltage vr/kV | 11 |

| SM capacitance C/mF | 50 |

| Input inductance Ls/mH | 8 |

| Output inductance Lr/mH | 8 |

| Arm inductors Lb/mH | 10 |

| Sampling period Ts/µs | 10 |

| Input frequency fs/Hz | 50 |

| Output frequency fr/Hz | 50/3 |

| Rated value of SM Uc/V | 2000 |

| Number of SMs (per arm) N | 20 |

| Parameters | Value |

|---|---|

| Input grid voltage vs/V | 60 |

| Output grid voltage vr/V | 60 |

| SM capacitance C/mF | 22 |

| Input inductance Ls/mH | 10 |

| Output inductance Lr/mH | 10 |

| Arm inductors Lb/mH | 5 |

| AC Y-connect Load Ro/Ω | 15 |

| Current-limiting resistor Rl/Ω | 10 |

| Input frequency fs/Hz | 50 |

| Output frequency fr/Hz | 50/3 |

| Number of SMs (per arm) N | 3 |

| Rated value of capacitor voltage in SM Uc/V | 50 |

| Controllable stage time t/s | 0.3 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

He, R.; Li, Y.; Peng, Y.; Ma, Y.; Huang, F.; Li, H.; Luo, W. A Low Inrush Current Pre-Charging Strategy of M3C with Improved Nearest Level Modulation. Energies 2025, 18, 2895. https://doi.org/10.3390/en18112895

He R, Li Y, Peng Y, Ma Y, Huang F, Li H, Luo W. A Low Inrush Current Pre-Charging Strategy of M3C with Improved Nearest Level Modulation. Energies. 2025; 18(11):2895. https://doi.org/10.3390/en18112895

Chicago/Turabian StyleHe, Rufei, Yikai Li, Yumin Peng, Yiming Ma, Fanqi Huang, Hailong Li, and Wei Luo. 2025. "A Low Inrush Current Pre-Charging Strategy of M3C with Improved Nearest Level Modulation" Energies 18, no. 11: 2895. https://doi.org/10.3390/en18112895

APA StyleHe, R., Li, Y., Peng, Y., Ma, Y., Huang, F., Li, H., & Luo, W. (2025). A Low Inrush Current Pre-Charging Strategy of M3C with Improved Nearest Level Modulation. Energies, 18(11), 2895. https://doi.org/10.3390/en18112895