1. Introduction

Permanent-magnet synchronous motors have been extensively used in many Internet of Things applications, such as electric vehicles, robots, and aerospace [

1]. The stability and rapidity of motor control are crucial indicators for PMSM control systems. The proportional–integral (PI) controller is used for speed control in the PMSM control system. It is vital to realize the proportional and integral gain tuning parameters of the PI controller for accurate speed control. However, when the model of the controlled object changes, the PI control strategy may not be sufficient to meet the control requirements of the PMSM with respect to its complex structure. As a result, PI control strategies may suffer from significant overshoots, sophisticated parameter settings, and slow motor response speeds. To address these issues, several studies have been performed. For example, sliding mode control [

2], a model reference adaptive system [

3], model predictive control [

4], the Extended Kalman Filter [

5], and intelligent optimization algorithms [

6,

7,

8] have been investigated. These techniques are aimed at achieving motor speed control with a minimal overshoot and a rapid response. Intelligent optimization algorithms not only improve system performance but also play a significant role in system performance optimization, especially when dealing with complex optimization problems. These complex problems may involve high dimensions, nonlinearity, and non-convexity, features that make traditional optimization methods difficult to effectively address. Xie et al. [

6] proposed a speed estimation strategy for a PMSM based on a particle swarm optimization Kalman filter (KF) sequence algorithm. Chen et al. [

7] optimized the parameters of a fractional-order PID controller of a PMSM using various intelligent optimization methods. Guo et al. [

8] applied the Fish Migration Optimization (FMO) algorithm to tune the PID parameters, enhancing the robustness of the PID controller. These intelligent optimization algorithms are computationally cumbersome and arduous to implement using hardware. Therefore, a simple and adaptable intelligent optimization algorithm is necessary and should be embedded into the PMSM speed control system to achieve more efficient control. Considering the practical application of algorithms, it is imperative to study how to implement the algorithm in hardware.

In recent years, there has been a growing focus on intelligent optimization algorithms in various fields of research. These algorithms, which require minimal prior knowledge and assumptions, autonomously seek optimal solutions and exhibit advantages when dealing with complex nonlinear and high-dimensional problems. Wild Horse Optimization (WHO) [

9], Gray Wolf Optimization (GWO) [

10], the Beetle Antennae Search (BAS) algorithm [

11], and Intelligent Water Drop (IWD) [

12] are among these introduced algorithms. The BAS algorithm has been successfully applied in various domains owing to its outstanding performance in tackling complex optimization problems. The BAS algorithm has been successfully applied in various fields, such as the spring design problem [

13], the geometric parameter identification of medical robots [

14], triaxial accelerometers [

15], and robot path planning [

16]. Additionally, its fast convergence rate has made it widely popular in other fields, like portfolio management [

17], robot arm calibration methods [

18], exoskeleton robots [

19], and economic load distribution problems [

20]. The BAS demonstrates a rapid convergence rate and strong optimization capabilities, allowing it to maintain excellent solution performance even amidst noise and uncertainty. Zhang et al. [

13] demonstrated the convergence and stability of the BAS algorithm, and they successfully applied the algorithm to six engineering cases with high requirements for real-time optimization. Additionally, Refs. [

17,

18,

19,

20] also applied the BAS algorithm to other engineering domains, meeting diverse real-time optimization needs. Compared to other mathematical control algorithms, the BAS algorithm presents several advantages when utilized in the speed loop of PMSM control systems. These advantages encompass its global optimization capability, adaptability, high robustness, simplicity, and parallelization ability. Therefore, the BAS method proves suitable for solving the PI controller parameter optimization problem.

However, due to the characteristics of a multivariable, nonlinear, and strongly coupled PMSM system, it is difficult to apply the BAS algorithm directly to the PMSM system. This area has not received extensive research attention, which is the motivation for our present study. This paper addresses the speed control problem of the PMSM system by studying how to utilize the BAS in the PMSM system and addressing its limitations to optimize the parameters of the PI controller and enhance the performance of the control system. Additionally, an FPGA has the advantages of parallelism capability, flexibility, high performance, and low power consumption compared to conventional hardware. An unrivaled advantage is that its hardware implementation can be customized [

21,

22]. Based on these unique advantages, FPGAs are widely used in various fields [

23,

24,

25]. To date, several metaheuristic algorithms have been implemented on the FPGA platform and successfully applied to practical engineering, such as the BAS algorithm [

26], genetic algorithm [

27], particle swarm algorithm [

28], cuckoo search algorithm [

29], etc. An FPGA can process large amounts of data to meet high-performance requirements. Of particular importance is the advantage that the FPGA can respond in microseconds to meet the real-time requirements of the system. Consequently, the FPGA is well suited for PMSM control systems. However, due to the complex structure of a PMSM control system involving a large number of mathematical functions and the existence of floating-point calculations in the BAS algorithm, it is not easy to implement both of them on an FPGA.

This paper proposes an LDSBAS (Linear Decreasing Step Beetle Antennae Search) algorithm, which enhances the beetle’s ability to perform global and local searches while allowing adjustable parameters within a certain range for the PI controller. Based on this algorithm, we investigate the LDSBAS-PI control strategy. When the PMSM control system is subjected to external disturbances, compared to the conventional PI controller and BAS-based controller, the LDSBAS-PI control strategy exhibits better system performance in minimizing the overshoot and improving the motor response speed. Moreover, we implemented the PMSM control system based on the LDSBAS algorithm on an FPGA. The main contributions of this paper are as follows:

In this paper, we propose an LDSBAS algorithm to solve the optimization problem of PI controller parameters. The LDSBAS algorithm linearly decreases the search step length such that the beetle’s global and local search capabilities are significantly improved compared with the traditional BAS algorithm.

The LFSR model, which has the ability to generate four random numbers, is developed for the first time on an FPGA platform. Compared to the existing LFSR model, which can generate only one random number, the model that we propose can provide more random numbers.

This paper solves the problem of implementing a PMSM control system based on the BAS algorithm on an FPGA and provides a more feasible solution for the application of intelligent optimization algorithms in PMSM control systems.

The PMSM control system presented in this paper, which is based on the LDSBAS algorithm, was developed using a register transfer level description. This approach directly represents the underlying circuitry and meets the need for dynamic function expansion.

This paper is organized as follows: In

Section 2, we offer a succinct overview of the mathematical model pertaining to a permanent-magnet synchronous motor. The LDSBAS algorithm is presented in

Section 3.

Section 4 describes the LDSBAS algorithm in a hardware description language.

Section 5 proposes the PMSM control system based on the LDSBAS algorithm. We built and simulated the PMSM control system using Simulink to demonstrate the effectiveness of the LDSBAS algorithm, as described in

Section 6. In

Section 7, hardware simulations of the PMSM control system using the LDSBAS algorithm are presented, the resource consumption on different FPGA platforms is discussed, and the feasibility of the hardware implementation of the LDSBAS algorithm is verified. Concluding remarks are made in

Section 8.

3. LDSBAS Algorithm

The Beetle Antennae Search algorithm draws inspiration from the foraging behavior of beetles. In unfamiliar environments, beetles employ their two antennae located on their heads to execute a sequence of flight and landing actions for foraging purposes. At the onset of the foraging phase, the beetle lacks awareness of the food source’s location. Its two antennae move randomly, and the beetle relies on the odor detected by its antennae to infer the direction of the food.

When a beetle is searching for food in an unknown location, its two antennae receive different concentrations of food odors in the traditional BAS algorithm. If the left antenna detects a stronger odor, the beetle moves toward the left direction; otherwise, it will move toward the right direction, continuously searching until it finds food and stops. The position where the beetle finds food can be regarded as the optimal value of the fitness function, and the independent variable of the fitness function can be considered the beetle’s position in the search area. Based on the traditional BAS algorithm, this section proposes the LDSBAS algorithm, which improves the beetle’s global and local search capabilities.

3.1. Random Search Direction and Antenna Coordinate Calculation

The position of the beetle in an arbitrary dimensional space is random, as is its food source. The following normalization is applied to the random search direction of the BAS algorithm.

where

denotes the normalized direction vector, and

denotes the random vector.

In the search area, the beetle uses two antennae to probe its surroundings for food. The left antenna position is indicated by

, the right antenna position by

, and the beetle detection distance by

. The coordinates of the two antenna locations are described as follows:

The distance between the beetle’s two antennae and the length of each search step, as specified in Ref. [

11], are as follows:

where

is the generation beetle antenna location, and

is the number of iterations. Larger

values should be used initially to avoid getting stuck in local minima.

3.2. Update of Location and Fitness Function

To ensure access to the best possible food source, the beetle’s position must be updated at each iteration. Using

and

as the right- and left-antenna fitness function values, the sign function and beetle search step are described in Equation (

7):

The search step size is fixed in the BAS algorithm, bringing about reduced global and local search efficiencies. To speed up the search process, both global and local search capabilities are improved. In general, intelligent algorithms are capable of mitigating non-optimal solutions or premature convergence to some extent [

9]. By appropriately setting and adjusting the step size in the BAS algorithm, the algorithm is able to fully explore the entire solution space during the search process. We have made improvements to the traditional BAS algorithm and propose the LDSBAS algorithm. The enhanced step size is updated as follows:

In Equation (

8),

is the maximum number of iterations,

is the minimum step length, and

is the maximum step length. Differing from traditional BAS algorithms, the search step and iteration number of the LDSBAS algorithm proposed in this article are related. At the beginning of the iterations, the step size changes rapidly, which benefits the global search. As the number of iterations increases, the step size change slows down, which benefits the local search. In addition, the LDSBAS algorithm has a simple structure that does not require parameter coding or complex functions. Thus, the algorithm is easy to implement and validate.

Generally, in optimization algorithms, a fitness function is chosen to evaluate the quality or suitability of candidate solutions (or individuals) in the solution space. In optimization problems, designing the fitness function may involve modeling and transforming the objective function or constraints. The selection of the fitness function has a significant impact on the performance and convergence of optimization algorithms, so it needs to be reasonably designed according to the specific problem. According to references [

30,

31], we employed the ITAE (Integral of Time-weighted Absolute Error) as the fitness function of the LDSBAS algorithm to balance the convergence speed and control the accuracy of the LDSBAS-PI controller.

Let

where

represents the error between the expected value and the feedback value. To minimize the value of ITAE, we introduce the parameter adjustment process of the LDSBAS-PI controller in the pseudocode below (Algorithm 1).

| Algorithm 1: LDSBAS algorithm |

Input: The parameter ranges of and ; Maximum step size, ; minimum step size, ; initialize values of and ; Maximum number of iterations, .

Output: - 1:

for to do - 2:

Normalize beetle orientation according to Equation ( 2); - 3:

Calculate the coordinates of the beetle’s two antennae according to Equations ( 3) and ( 4); - 4:

Update the beetle position in the search area according to Equation ( 7); - 5:

Update the beetle’s optimal position globally by comparing the current minimum with the minimum from the previous generation; - 6:

Update the beetle position and step size according to Equation ( 8); - 7:

Number of update iterations: ; - 8:

end for - 9:

return , , and .

|

Above, this section presents the execution process of the LDSBAS algorithm, which dynamically adjusts the search step size of beetles with the number of iterations. In the initial iterations, the step size changes rapidly, facilitating the global search, while as the number of iterations increases, the step size changes more slowly, promoting the local search. Therefore, this adaptive search strategy helps mitigate the risk of algorithms getting trapped in local optima to some extent. The following part of the paper will show the implementation of the LDSBAS algorithm using a hardware description language.

4. Hardware Description of LDSBAS Algorithm

We used an FPGA to implement the LDSBAS algorithm to improve the efficiency and performance of the algorithm, primarily due to the following two reasons. Firstly, the LDSBAS algorithm can process multiple solutions simultaneously to find the global optimal solution. The FPGA has a large number of parallel circuit units in hardware, which can separately process each solution in the LDSBAS algorithm, further improving the algorithm’s parallel processing capability. Secondly, the LDSBAS algorithm needs a significant amount of computing resources to search the solution space and find the global optimum. The FPGA has a high-speed parallel circuit structure that can provide faster computing speed and lower latency for the LDSBAS algorithm.

In this section, the LDSBAS algorithm will be decomposed into five modules, and the corresponding circuits will be constructed for each module.

4.1. Random Number Generator Module

According to the principles of the LDSBAS algorithm, the first step involves the generation of random vectors for the movement and evolution directions of the beetles. As this paper primarily optimizes the P and I parameters of the PI controller, the environment for beetle activity is set in two dimensions. In contrast to other high-level programming languages where the

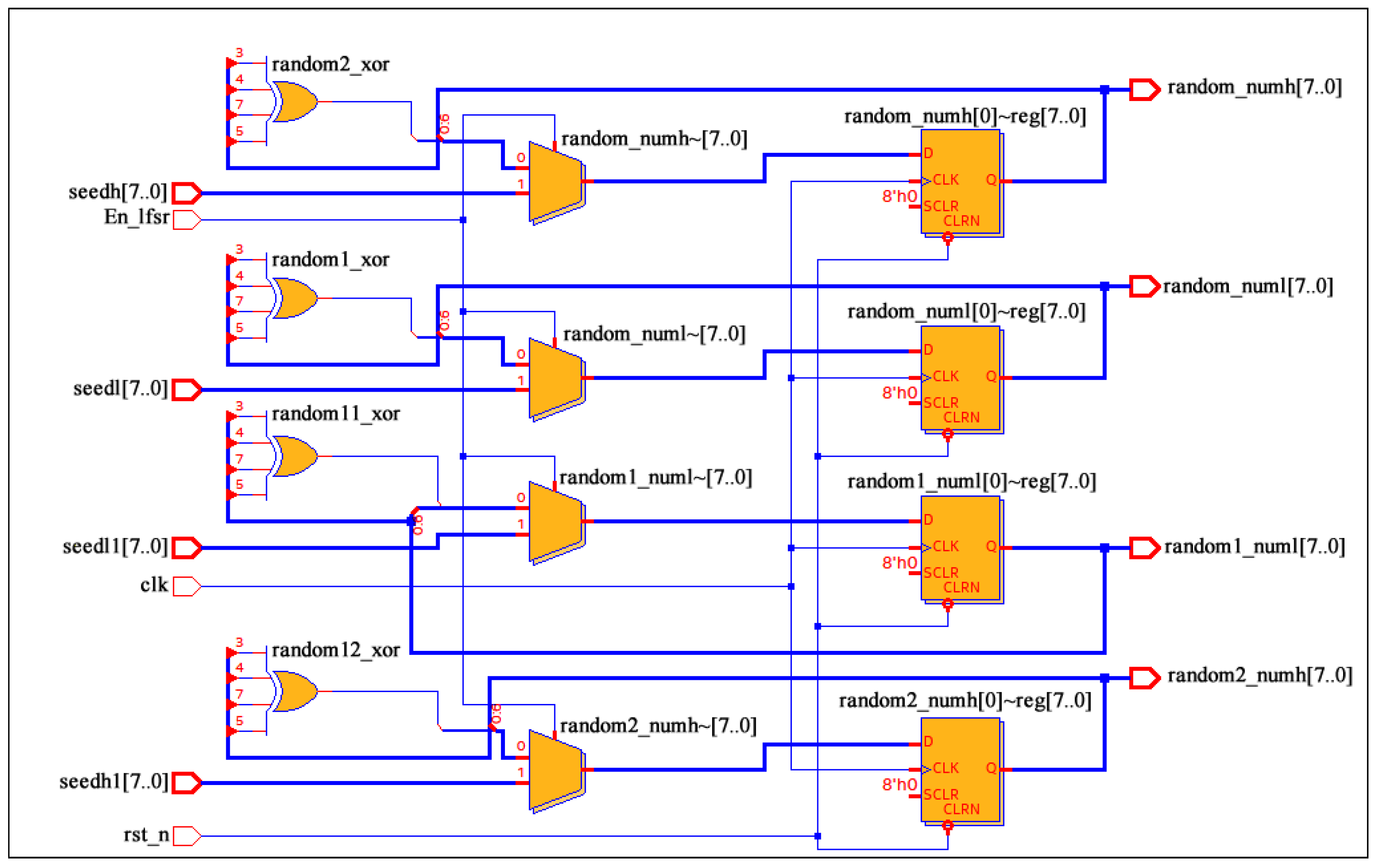

$random function cannot be directly synthesized into a circuit, this paper employs a linear feedback shift register (LFSR) to generate pseudo-random numbers [

32]. To address the requirement for multiple streams of random numbers, this paper has developed a generator capable of producing four streams of LFSR pseudo-random numbers. This generator accomplishes this by performing an XOR operation on the outputs of the 6th, 4th, 3rd, and 2nd bits and feeding the result back to the input. The circuit depicted in

Figure 1 is replicated four times, each receiving a different seed, thereby producing a polynomial, as shown in Equation (

10).

The seed width is set to 8 bits, and the XOR operation of the 7th, 5th, 4th, and 3rd bits of the output is fed back to the input. The RTL model of the LFSR in

Figure 1 complies with the given polynomial. Given four different seeds, the LFSR model generates four different random numbers, as the ‘En_lfsr’ signal is valid.

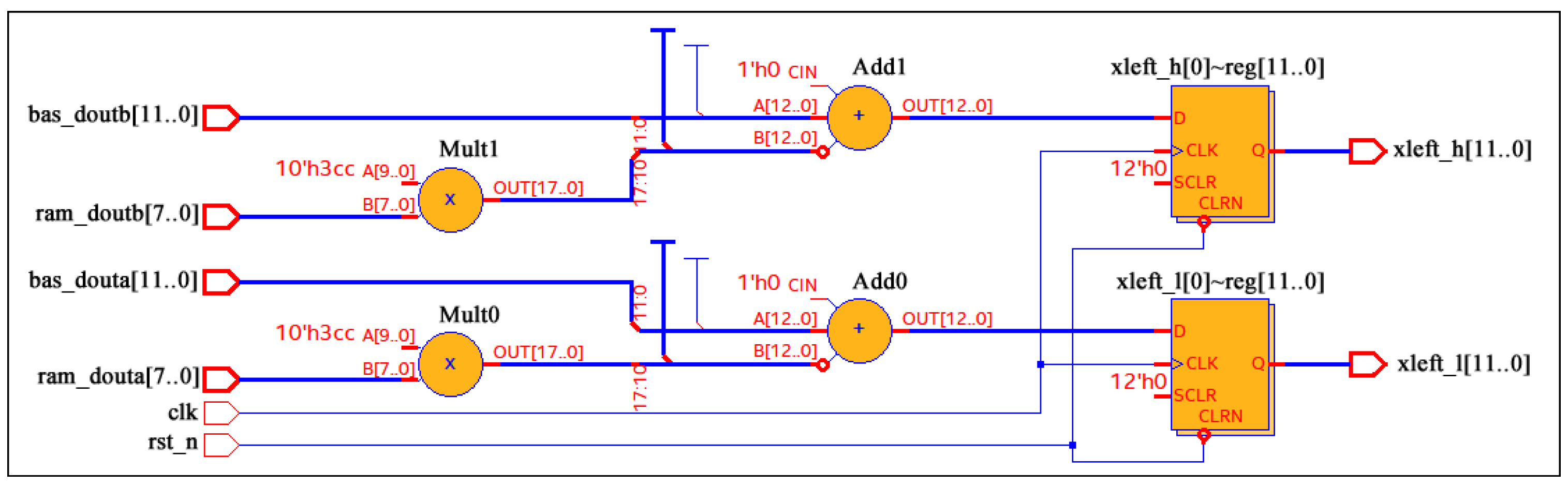

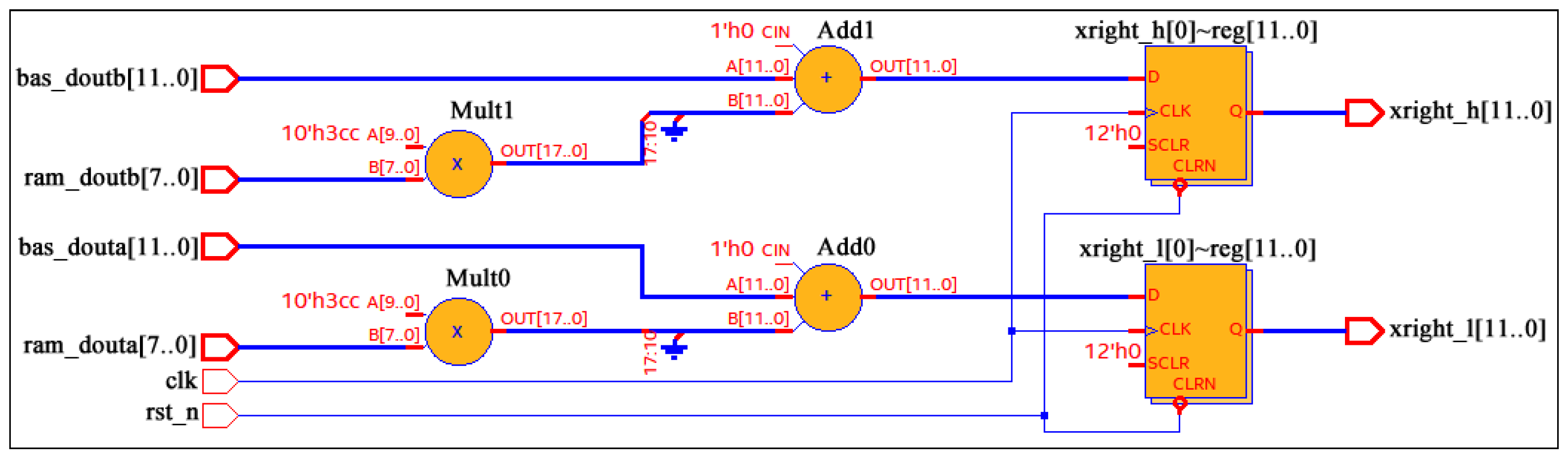

4.2. Antenna Update Module

The method for calculating the coordinates of the beetle’s antennae indicates that the updates of the two antennae are related to the detection distance ‘

’, which is set to 0.95 according to Ref. [

11]. However, floating-point numbers cannot be directly computed in the Verilog hardware description language. We use fixed-point arithmetic [

33,

34] to solve the floating-point number problems in the BAS algorithm. We use Equation (

11) to calculate the fixed-point ‘

’.

In order to use bitwise operations to restore the data in subsequent calculations, we multiply the floating-point number by 2 to the power of 10 in Equation (

11). The RTL models for the updated antennae are shown in

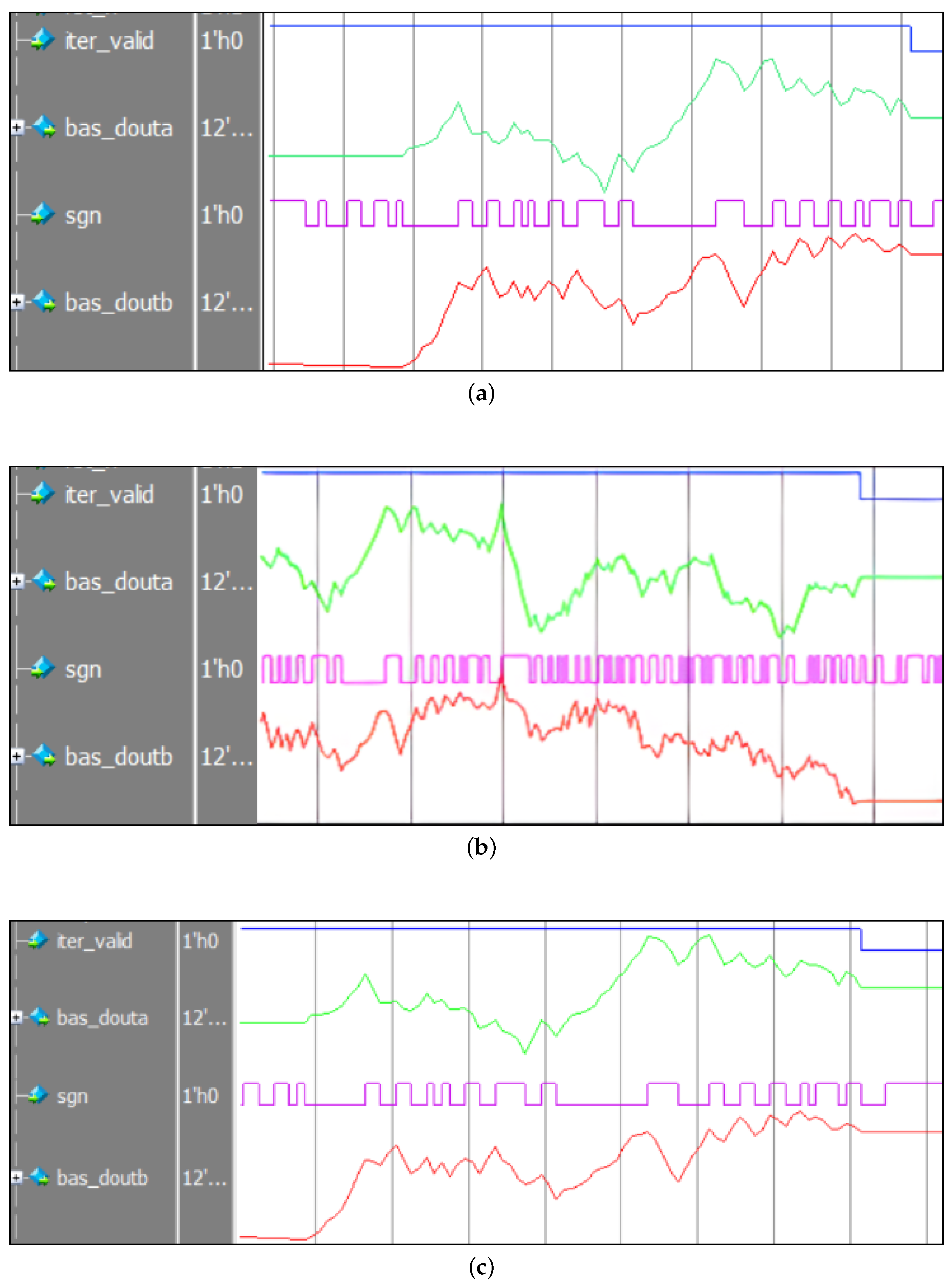

Figure 2 and

Figure 3. The Ram outputs ‘ram_douta’ and ‘ram_doutb’ are two sets of random numbers read from the Ram. ‘Bas_douta’ and ‘bas_doutb’ represent the position coordinates of the beetle. ‘Xleft_h’ and ‘xleft_l’ are the two-dimensional coordinates of the current left antenna, and ‘xright_h’ and ‘xright_l’ are the two-dimensional coordinates of the current right antenna. Finally, the two-dimensional coordinates of the left and right antennae are sent to the fitness function module to calculate the fitness function values for these two antennae.

4.3. Position Update Module

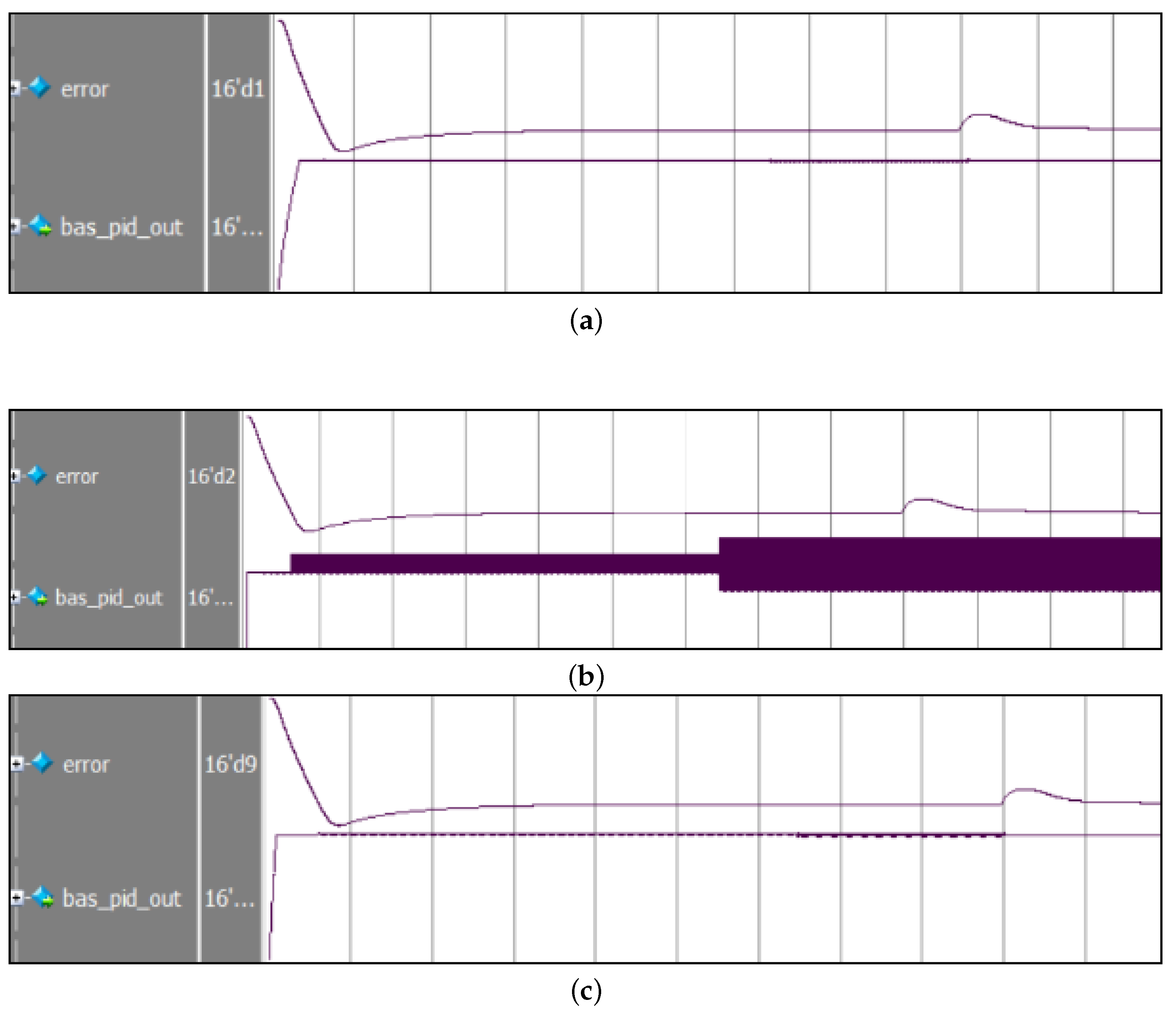

After multiple experiments, it was found that the PI controller works best when the maximum number of iterations

in Equation (

8) is set to 200, the minimum step size

is set to 0.4, and the maximum step size

is set to 0.8. The step size update is given by

The floating-point numbers in the step size formula are also enlarged by 1024 times and fixed-pointed as follows:

During the position update process of the beetle, the sign function determines which direction the beetle moves toward. ‘xleft_fitness’ and ‘xright_fitness’ represent the fitness values of the left and right antennae, respectively. The sign function in Verilog is represented as follows:

According to the meaning of the sign function, a sign function value of ‘1’ indicates a beetle moving forward, ‘−1’ indicates moving backward, and ‘0’ indicates no movement. Unlike in other programming languages, in Verilog, a sign function value of ‘1’ indicates movement forward, ‘0’ indicates movement backward, and the D flip-flop maintains its current value when the beetle is still.

Figure 4 shows the RTL model for updating the position of the beetle. When ‘iter_valid’ is low, it indicates that the beetle has found food at the end of the iteration. ‘Bas_douta’ and ‘bas_doutb’ represent the current coordinates of the beetle’s location, while ‘ram_doutaa’ and ‘ram_doutbb’ are two different random numbers of RAM.

4.4. Fitness Function Calculation Module

In the design of the LDSBAS algorithm, computing the fitness function is critical not only for the algorithm speed but also for minimal logic resource consumption during FPGA implementation. The fitness function calculation needs to be optimized to reduce the computational burden and save logic resources during FPGA implementation.

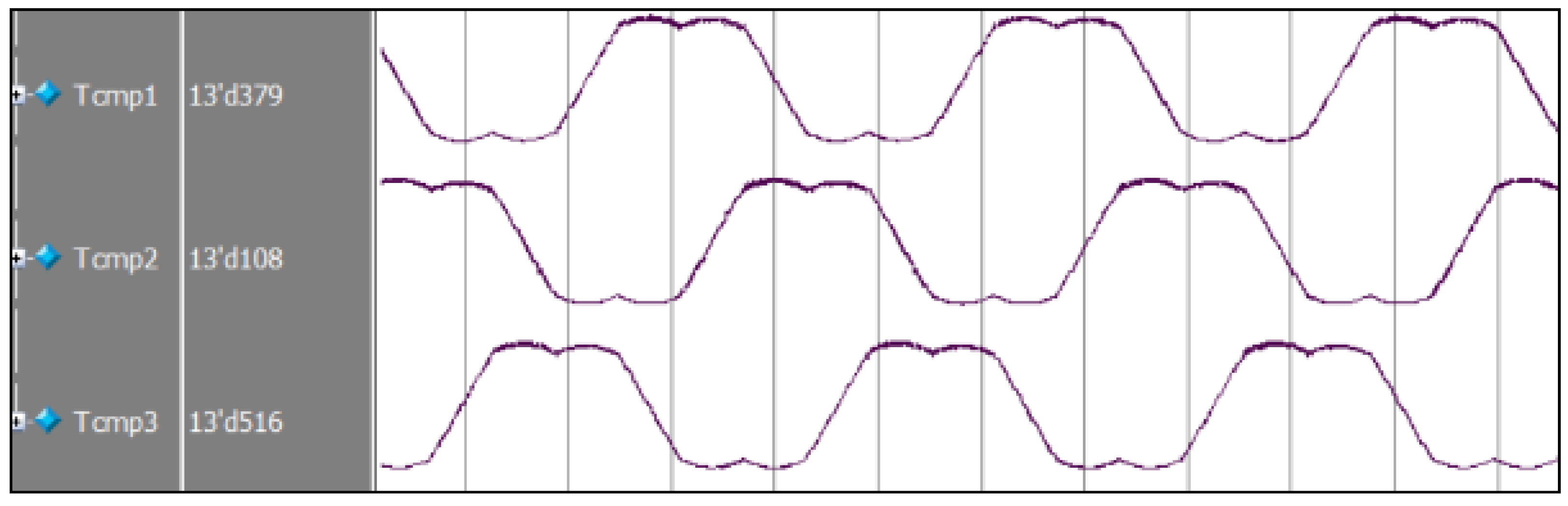

The ITAE is further written in discrete form:

where

is the number of sampling points, and

is the sampling period.

Once the sampling period is determined,

is a constant whose existence does not affect the performance of the PMSM control system. Therefore, the ITAE can be calculated on the FPGA according to the following equation:

This section introduces the hardware description of the LDSBAS algorithm. We will now turn our attention to investigating the PMSM control algorithm.

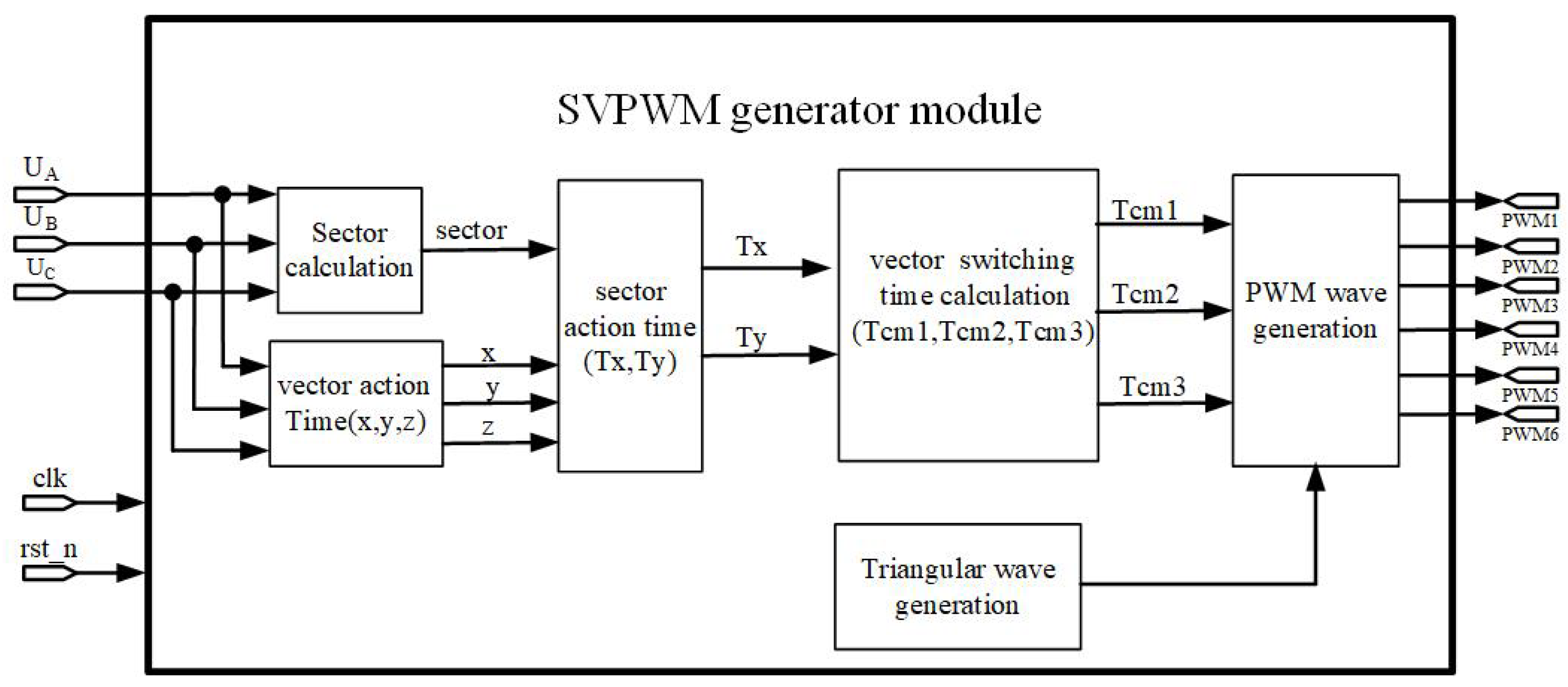

6. Results Analysis of PMSM Control System Simulation

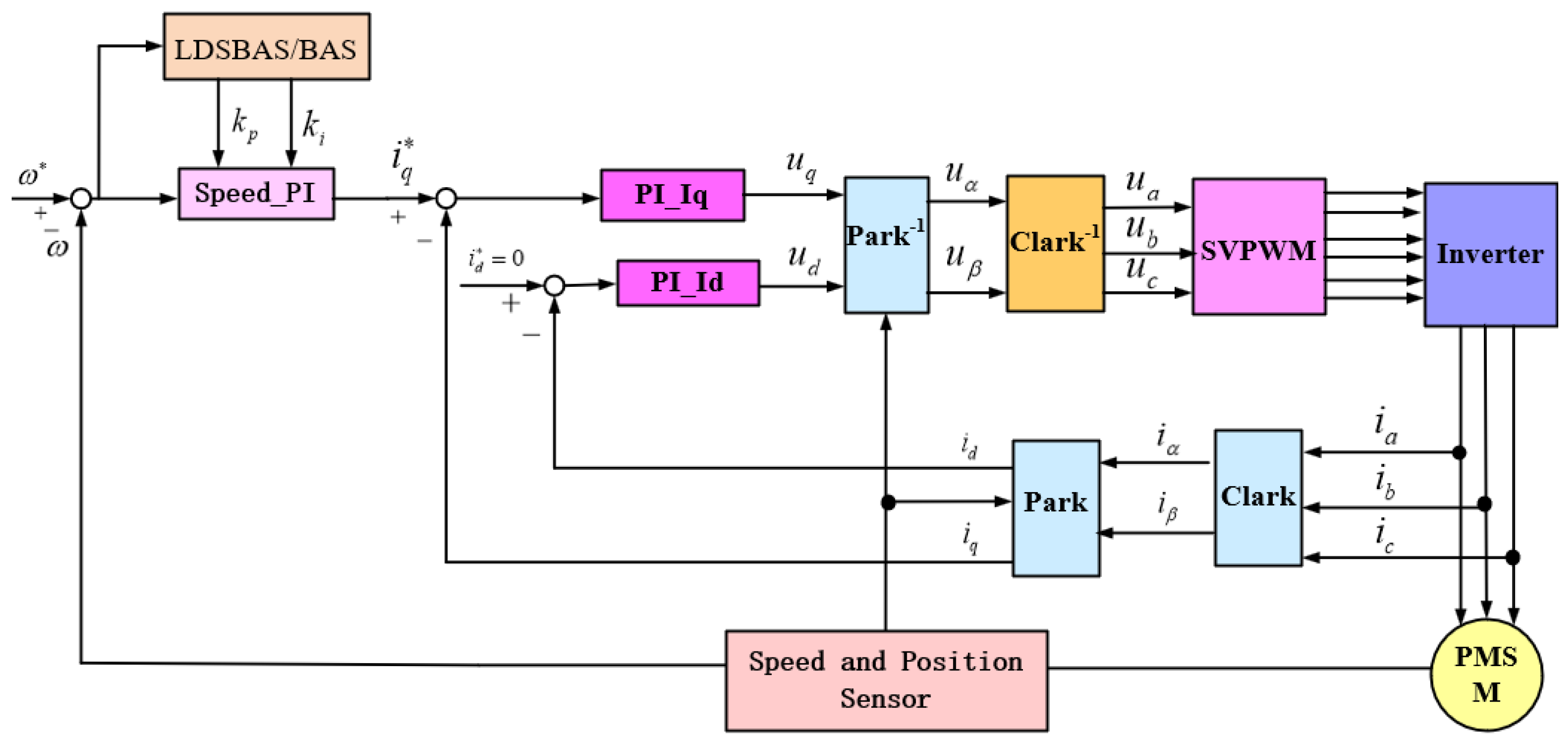

To comprehensively assess the performance of the LDSBAS algorithm within the PMSM control system, simulations were performed for three cases, namely, no load, speed transient, and load transients, which can lead to changes in motor parameters. Throughout these simulations, the performance of the PI controller, BAS-algorithm-based speed controller, and LDSBAS-algorithm-based speed controller was compared. This paper aimed to further substantiate the advantages of the LDSBAS algorithm by contrasting simulations across different scenarios.

Figure 6 illustrates a schematic diagram of the PMSM control system based on the LDSBAS algorithm. To calculate the parameters of the PI controller, the parameters of the PMSM in the simulation are given in

Table 1. According to [

36,

37], we obtain

= 0.14 and

= 7 by utilizing the parameters in

Table 1 and Equation (

24) as follows:

where

represents the speed loop bandwidth,

represents the number of motor poles,

represents the flux linkage, and

J represents rotational inertia.

Table 2 provides the parameters of different controllers. The parameters of the BAS/ LDSBAS-PI controller are adjustable. Their initial ranges are determined based on the parameters of the PI controller. Then, according to the performance of the PMSM control system under three different disturbance conditions, we further provide the upper and lower bounds of the parameter variations.

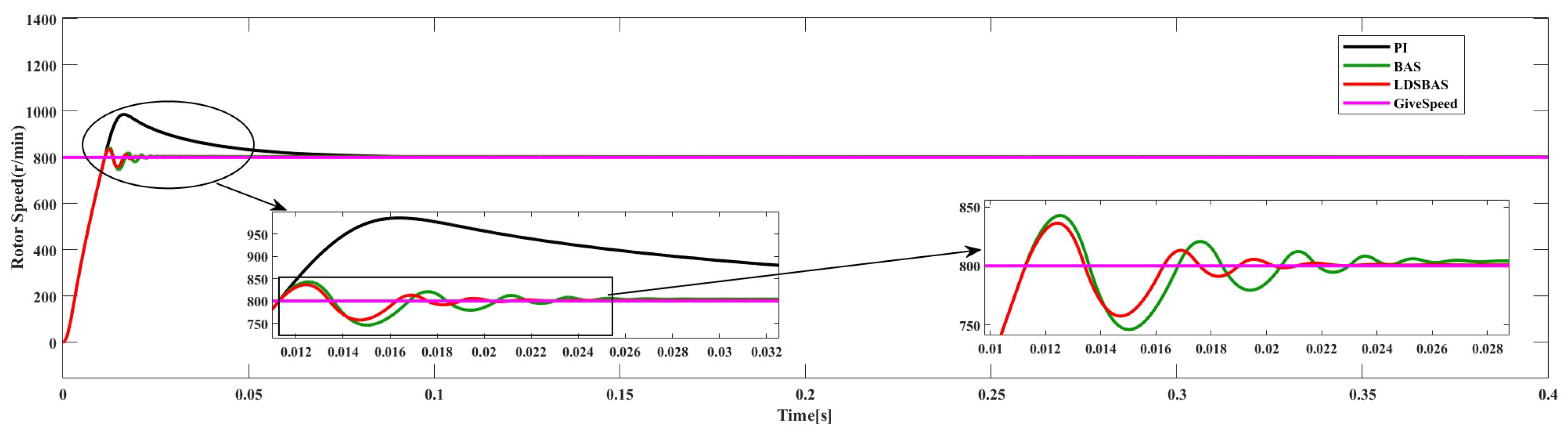

6.1. No Load

Figure 7 shows the simulation results under no-load conditions at a given speed of 800 r/min. The output of the PI controller exhibits a significant overshoot, surpassing 150 r/min as the maximum. In contrast, both the BAS-algorithm- and LDSBAS-algorithm-based speed controllers demonstrate notably reduced overshoots, each with a maximum of less than 50 r/min. By 0.025 s, the speed controllers of both optimization algorithms have reached the target speed, while the PI controller starts approaching it gradually at the same time. Clearly, these two algorithms significantly expedite the motor’s response speed. At around 0.02 s, the LDSBAS algorithm has already reached the target speed with a smaller error, indicating its enhanced motor response speed. Analyzing the simulation results of the PI controller, BAS-algorithm-based speed controller, and LDSBAS-algorithm-based speed controller confirms that the LDSBAS algorithm effectively reduces the overshoot in the PI controller’s output while enhancing the response speed of the PMSM control system.

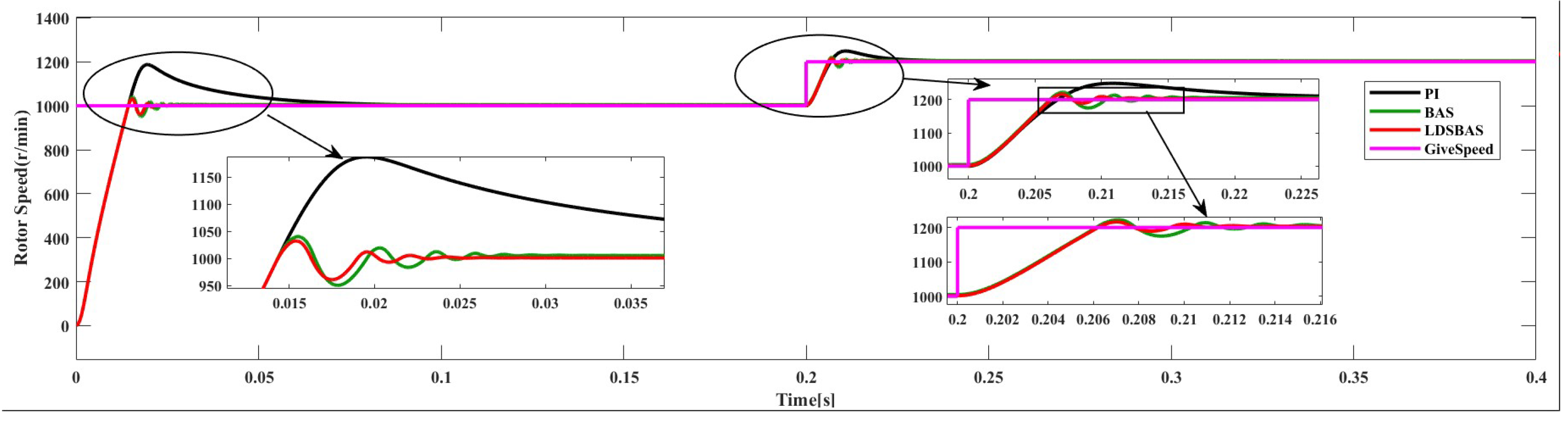

6.2. Speed Transient

Figure 8 depicts the simulation results with speed transient variation without a load. Initially set at 1000 r/min, the speed abruptly changed to 1200 r/min at 0.2 s. The speed error indicated that the PI controller output had an overshoot exceeding 150 r/min. Conversely, both the BAS- and LDSBAS-algorithm-based speed controllers exhibited notably reduced overshoots. The LDSBAS-algorithm-based controller reached the target speed by 0.02 s, while the BAS algorithm required 0.025 s. The LDSBAS-algorithm-based speed controller demonstrated a faster response. At 0.2 s, during the speed change, the PI controller showed the most severe amplitude oscillations, followed by a slight improvement with the BAS algorithm. Comparatively, while the LDSBAS algorithm also exhibited amplitude oscillations, the maximum did not exceed 20 r/min. By 0.22 s, the PI controller was close to the target speed, exhibiting the maximum overshoot. The BAS algorithm approached the target speed at 0.215 s, whereas the LDSBAS algorithm had already done so by 0.21 s. The LDSBAS algorithm provided a system with a smaller overshoot and faster response during sudden speed variations. The comparative simulation results demonstrate that the PMSM control system using the LDSBAS algorithm maintains good stability and a faster response.

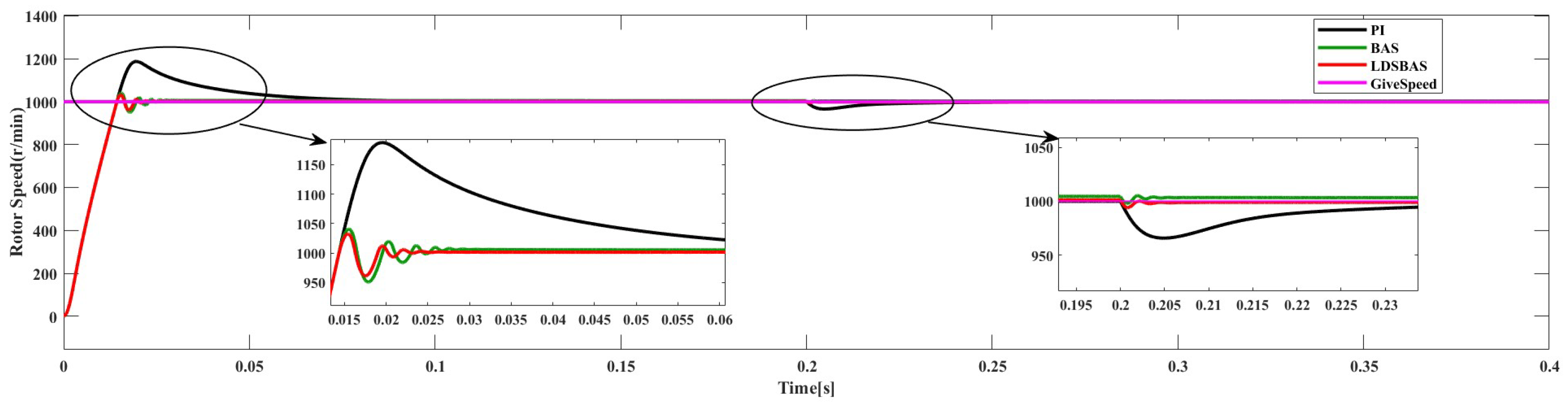

6.3. Load Transients

Figure 9 demonstrates the simulation results of the load torque transient from 0 N·m to 5 N·m at 0.2 s when the given speed is 1000 r/min. In this situation, the LDSBAS algorithm’s PI controller still has the smallest overshoot and fastest response time, while the PI controller still has the largest overshoot and takes 0.23 s to gradually approach the target speed. At 0.21 s, both the LDSBAS and BAS algorithms reach the target speed, but the BAS algorithm has a smaller error. Therefore, in dealing with the load torque transient of the PMSM control system, the LDSBAS algorithm performs better than the PI and the BAS algorithm.

Through simulations under three different scenarios, it can be observed that, compared to the traditional PI and BAS-based PI controllers, the LDSBAS-PI controller minimizes the overshoot and improves the motor response speed against load disturbances to some extent. Furthermore, the LDSBAS algorithm exhibits an inevitable overshoot and oscillations in the speed response curve during motor startup or in the presence of external forces. However, compared to PI control, the magnitude of the overshoot is much smaller, and the duration of oscillations is much shorter. Especially when external disturbances occur, the disturbance rejection capability of the LDSBAS algorithm is superior to PI control. This validates the effectiveness of the LDSBAS algorithm.