Review of DC-DC Partial Power Converter Configurations and Topologies

Abstract

1. Introduction

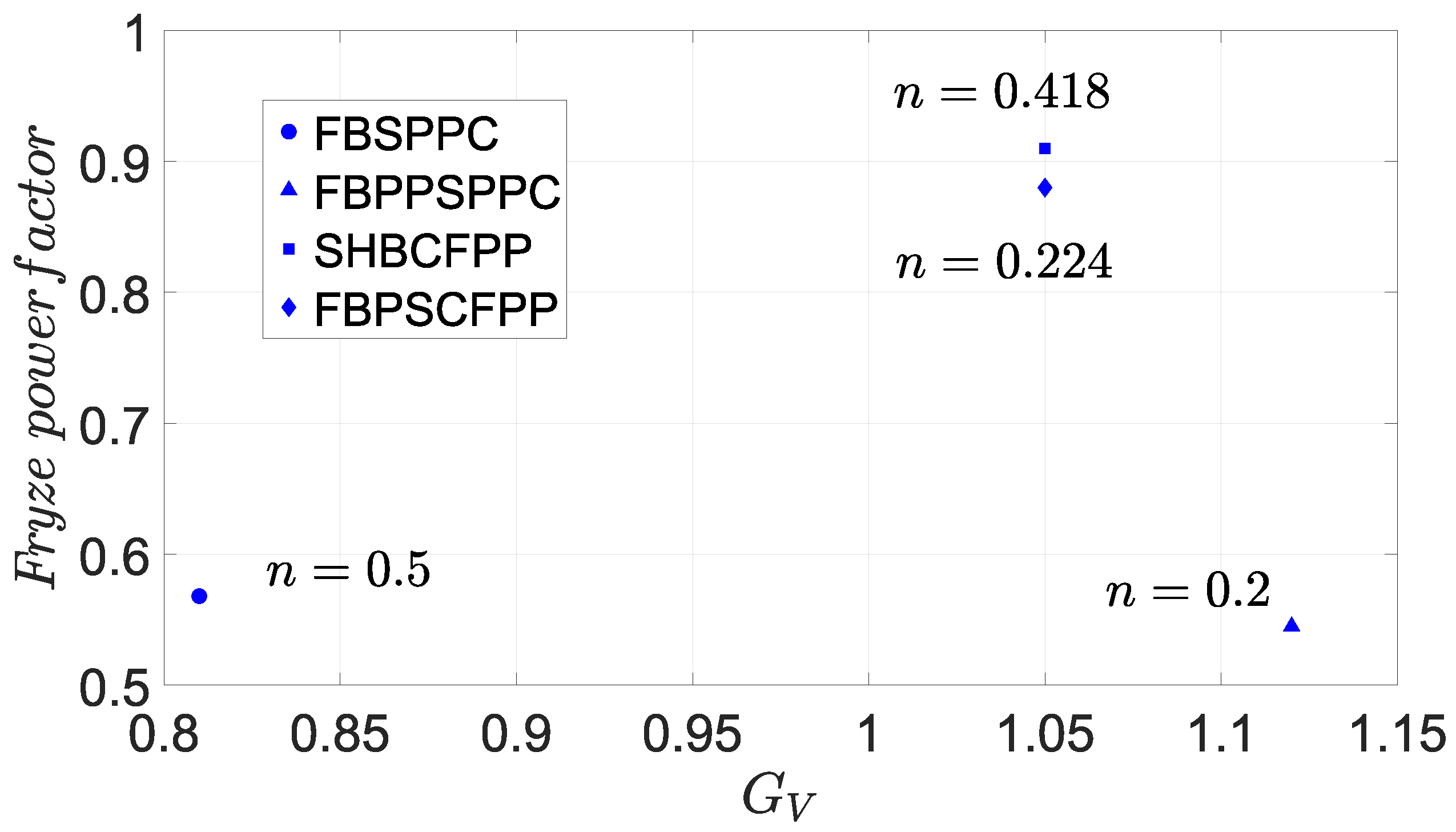

2. Comparison Metrics

3. Isolated PPP Architectures

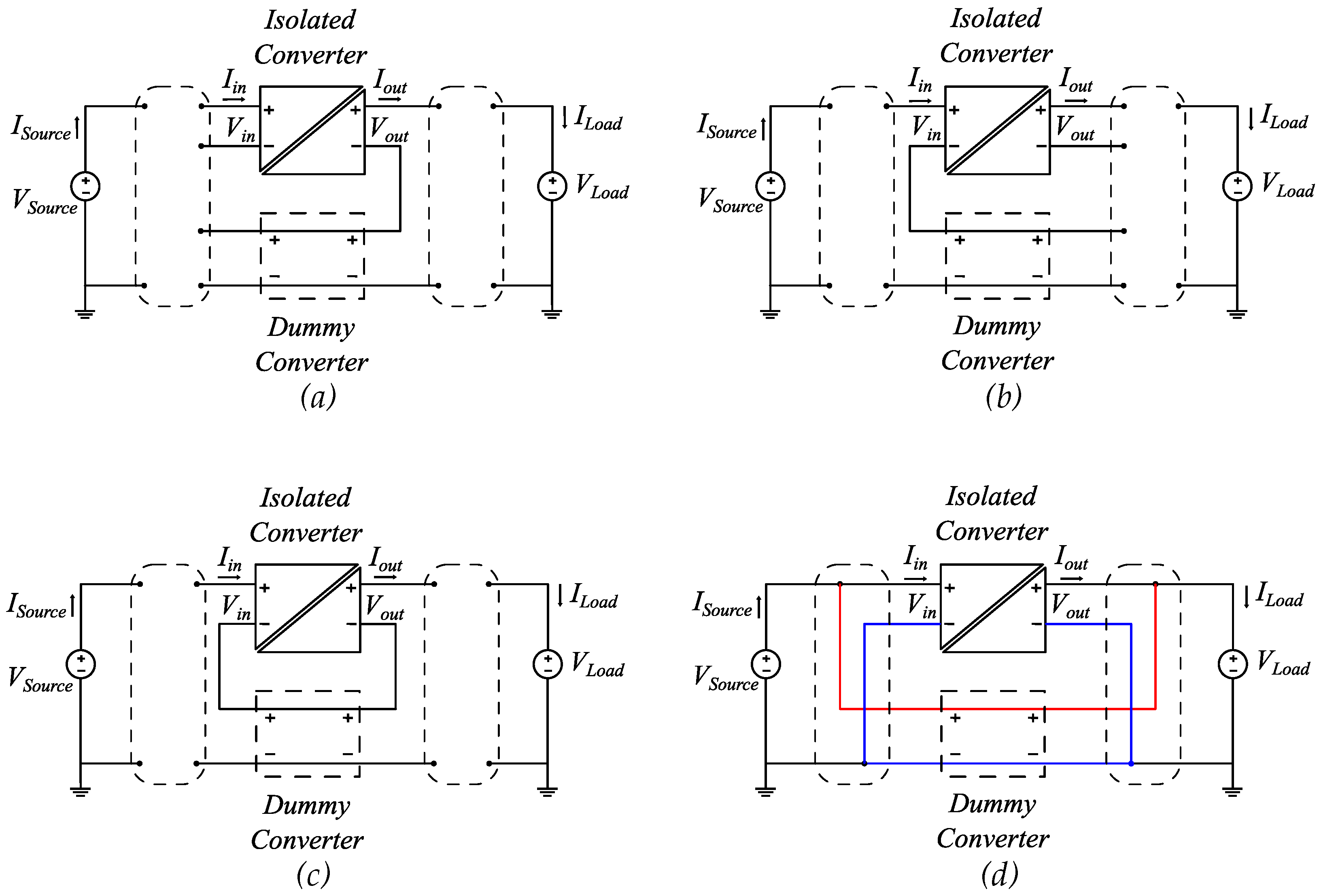

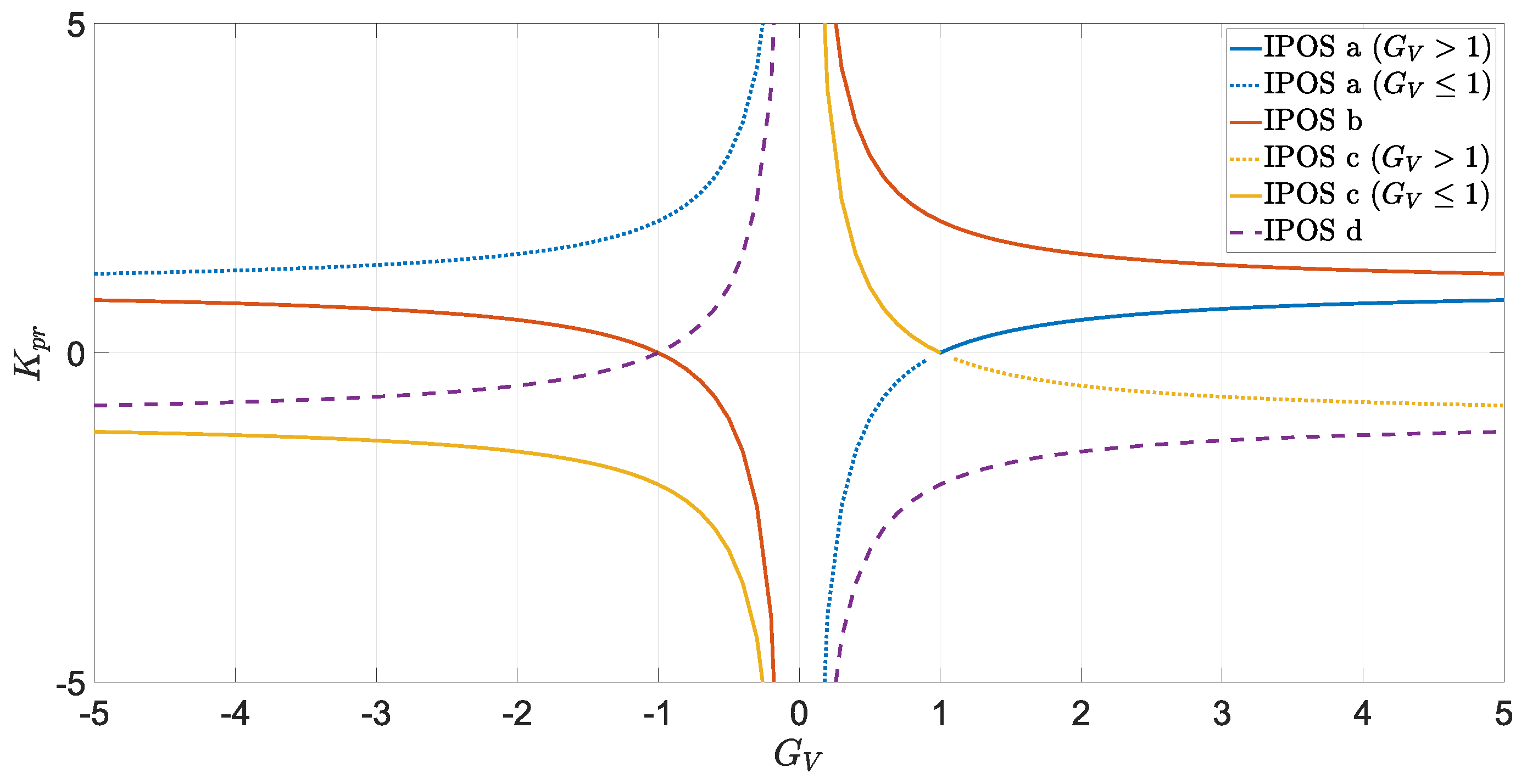

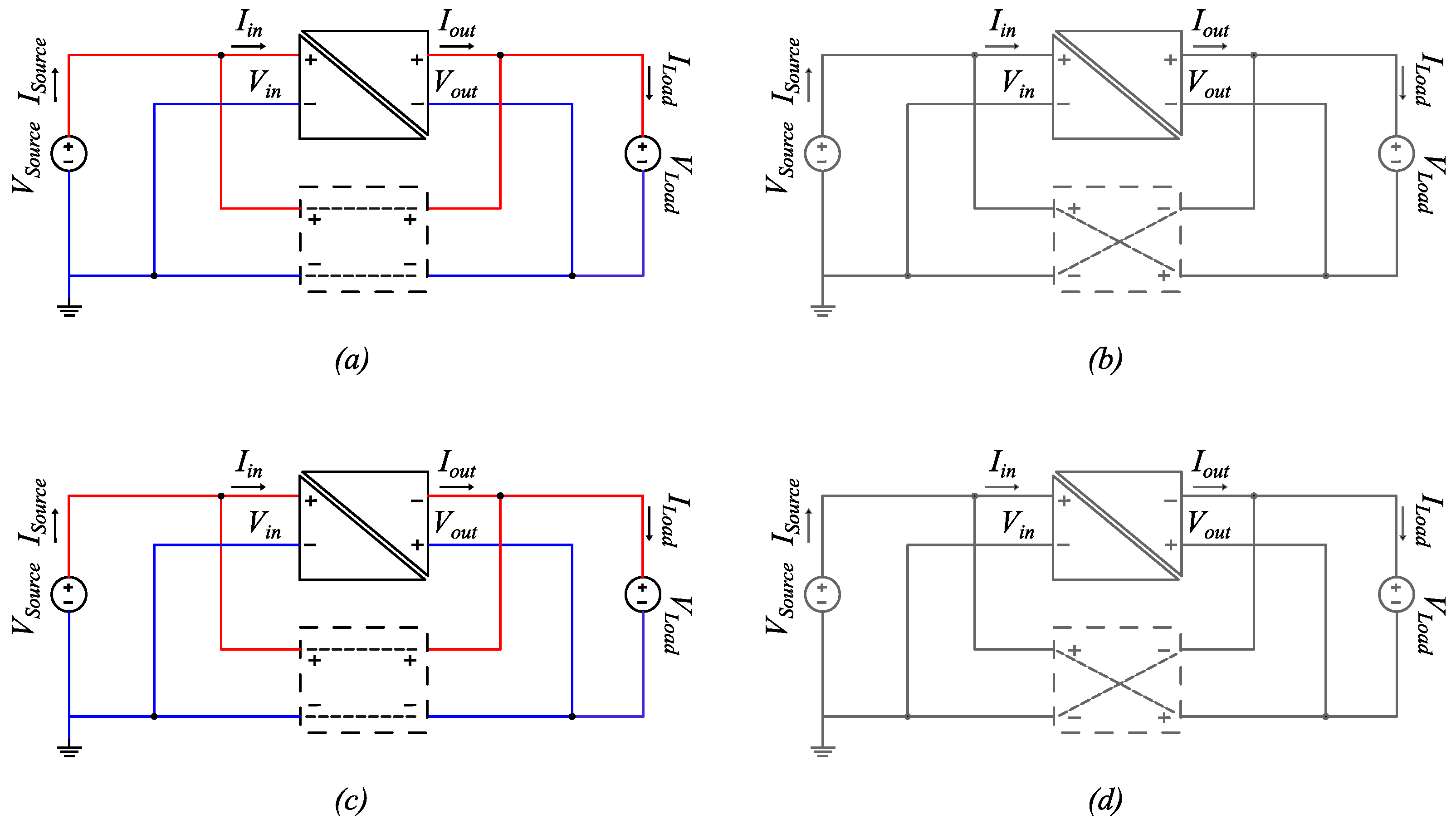

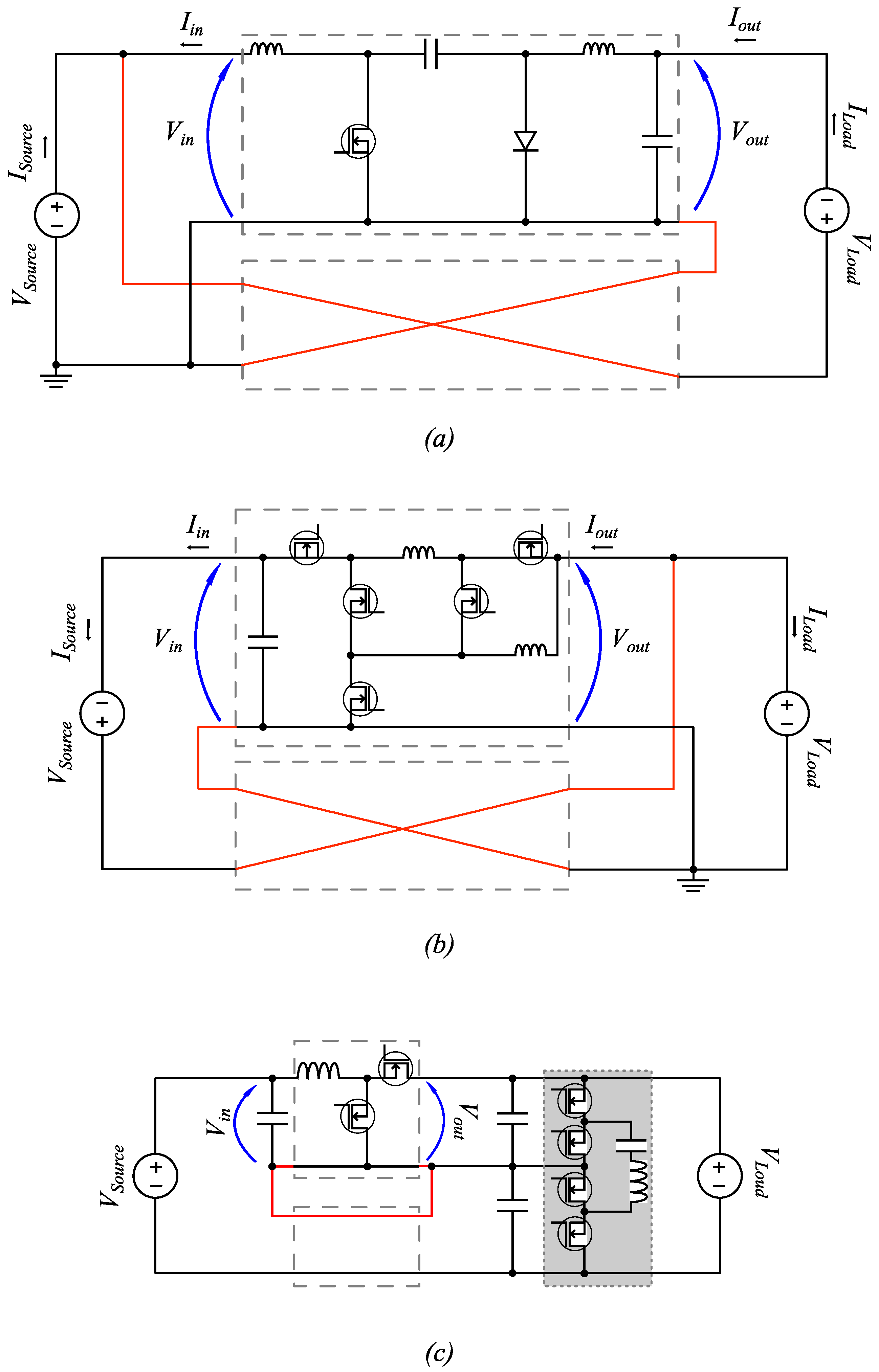

3.1. Input-Parallel-Output-Series Topology (IPOS)

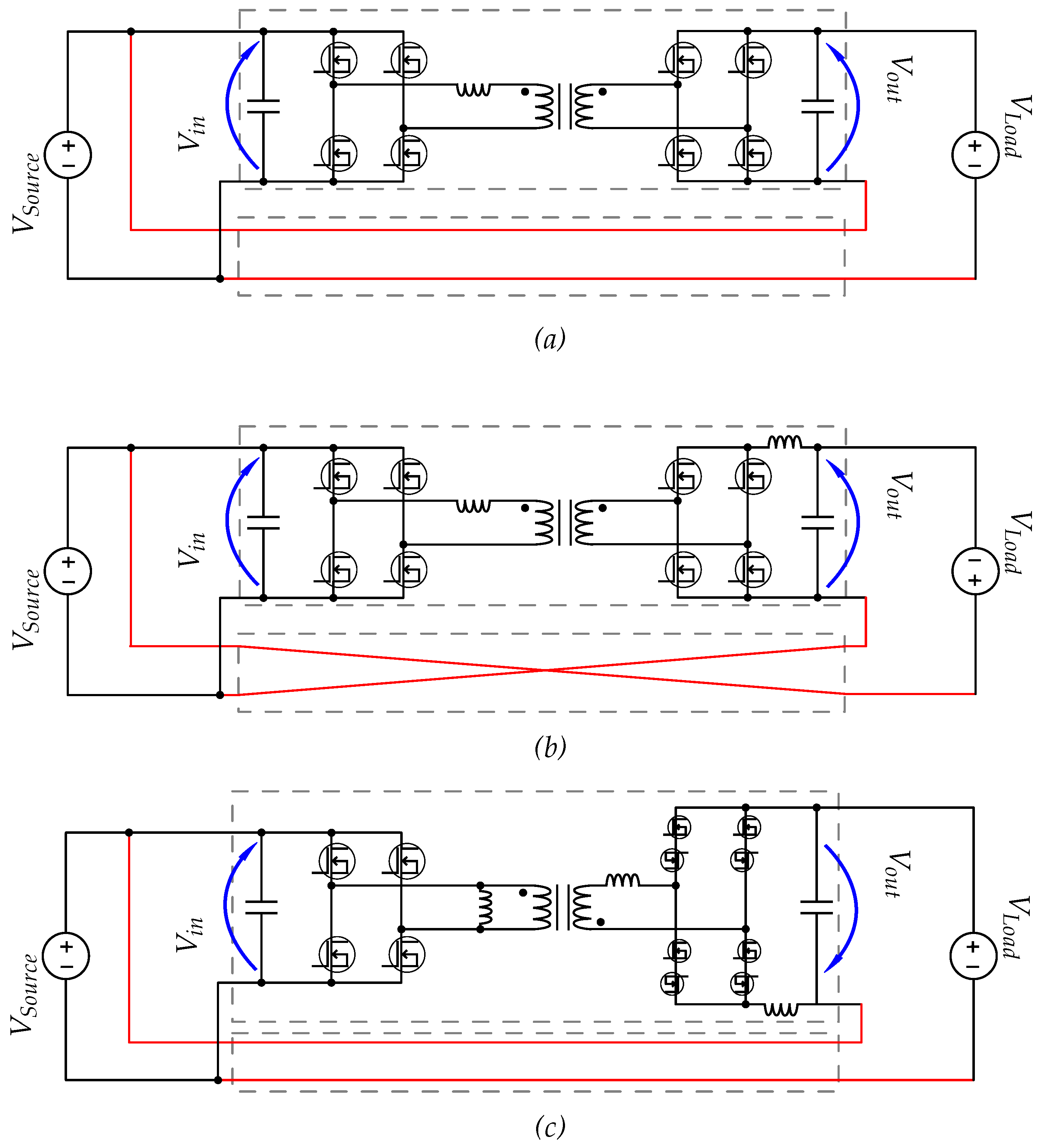

3.2. IPOS-Based Converters

| Reference | Converter | Topology | Application | System Power [kW] | [%] | ||

|---|---|---|---|---|---|---|---|

| [31] | DAB | IPOS (a) | 40% | 1.73 | Battery emulator | 0.10 | 99.90 |

| [14] | Dual-inductor push–pull | IPOS (a) | 25% | 13.3 | PV | 1.20 | 99.00 |

| [28] | Flyback | IPOS (a) | 41% | 1.43 | PV | 0.10 | 95.50 |

| [16] | Flyback | IPOS (a) | 44% | 1.99 | PV | 0.10 | 98.50 |

| [32] | DAB | IPOS (a) | 44% | 3.00 | Battery charging | 0.72 | 95.60 |

| [11] | Flyback | IPOS (a) | 20% | 1.17 | PV | 0.99 | 90.00 |

| [33] | Buck-boost Full-bridge | IPOS (b) | <40% | <3.5 | PV | 1.80 | 98.90 |

| [34] | Full bridge push–pull | IPOS (a) | 20% | 0.99 | Battery charging | 22.00 | 99.0 |

| [35] | Full bridge phase shift | IPOS (a) | 20% | <1.0 | PV | 78.00 | 98.5 |

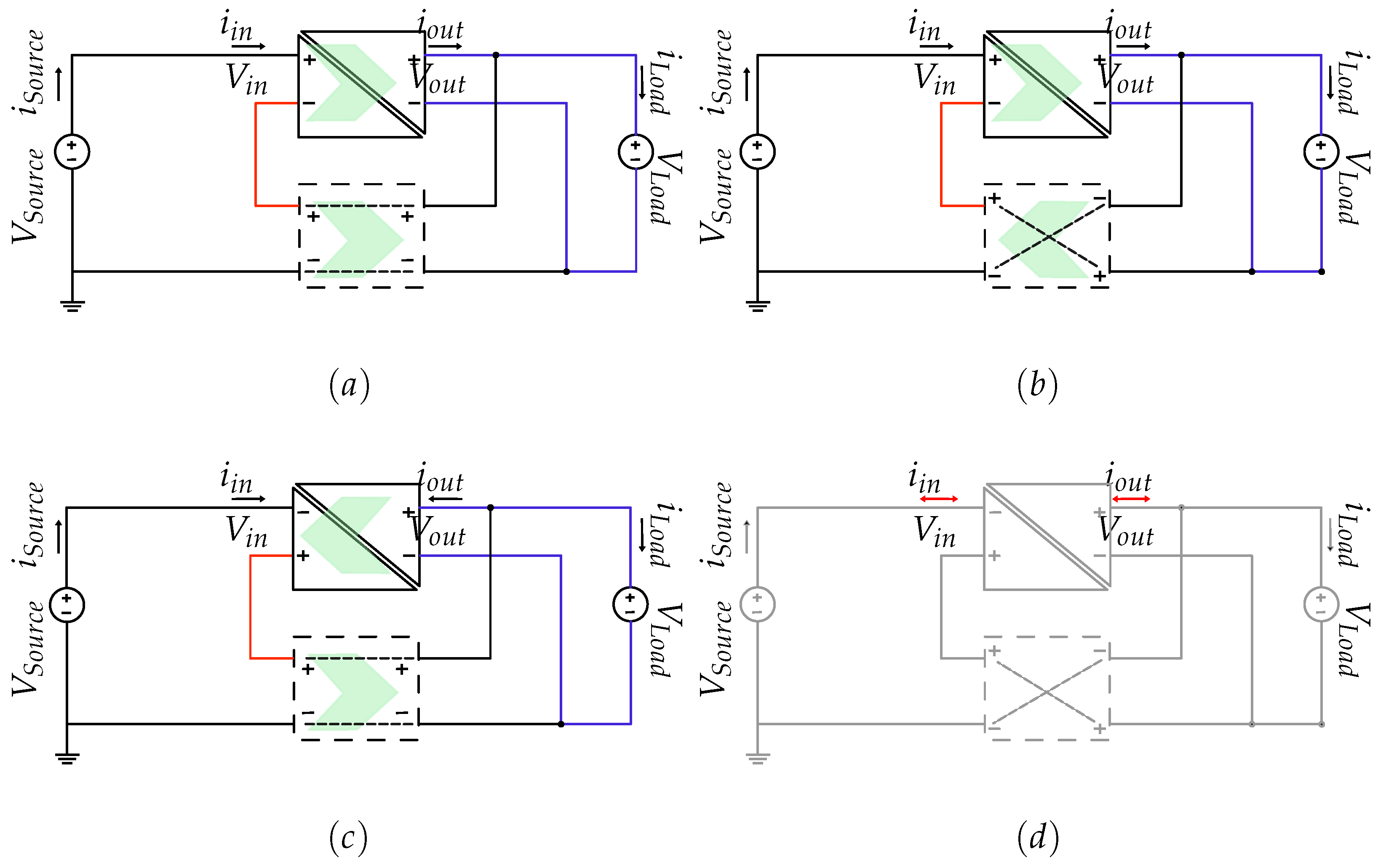

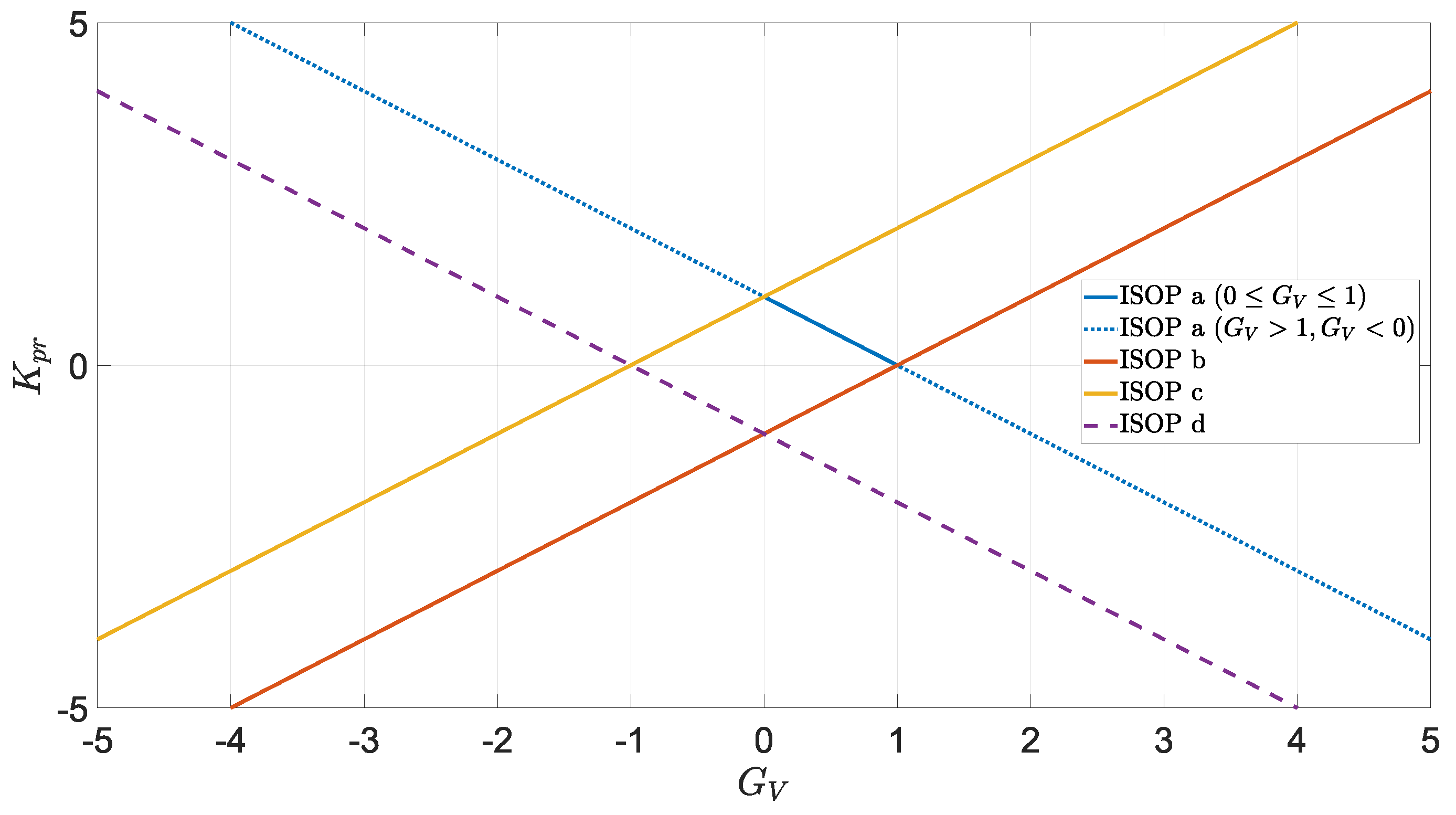

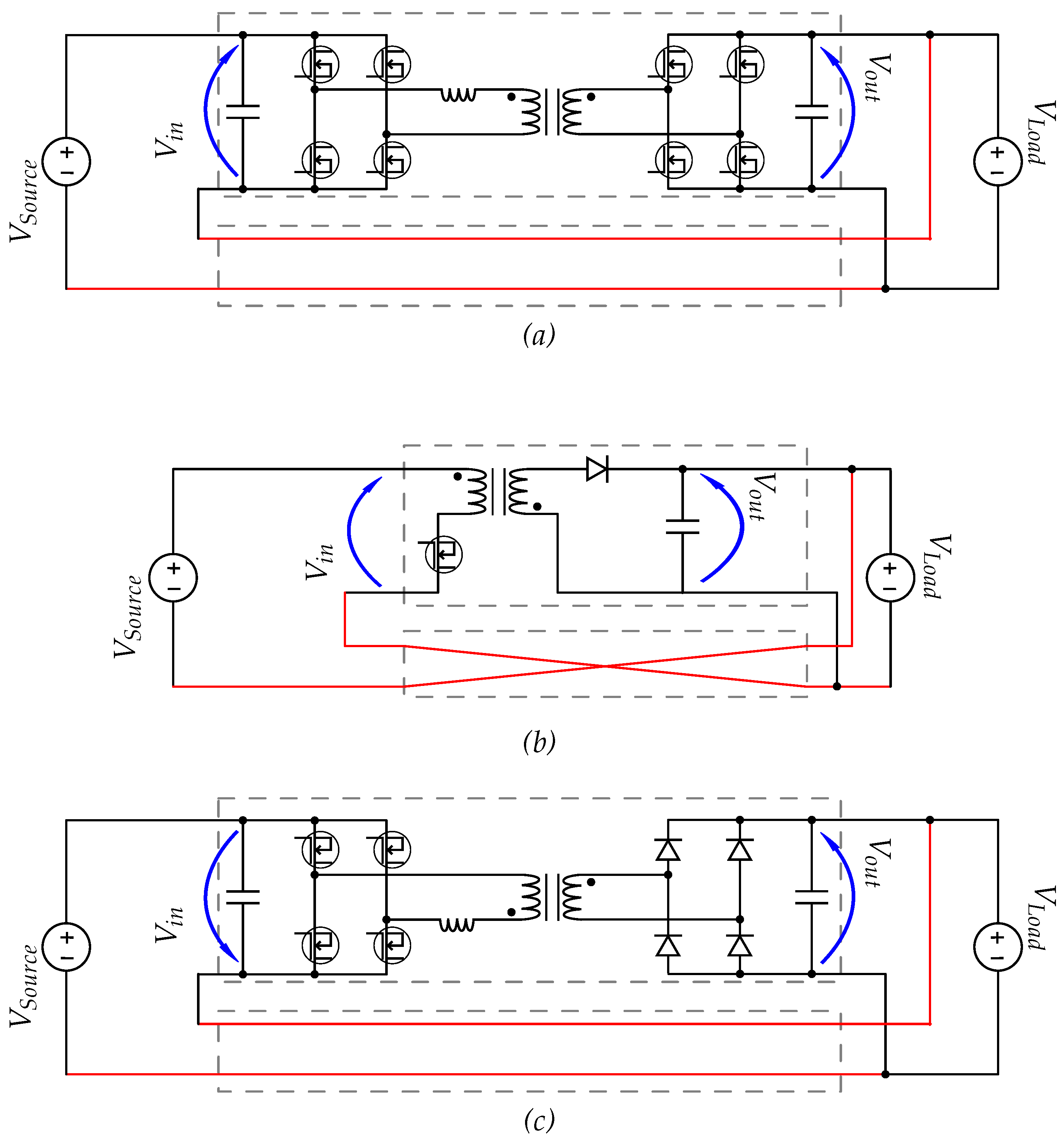

3.3. Input-Series-Output-Parallel Topology (ISOP)

3.4. ISOP-Based Converters

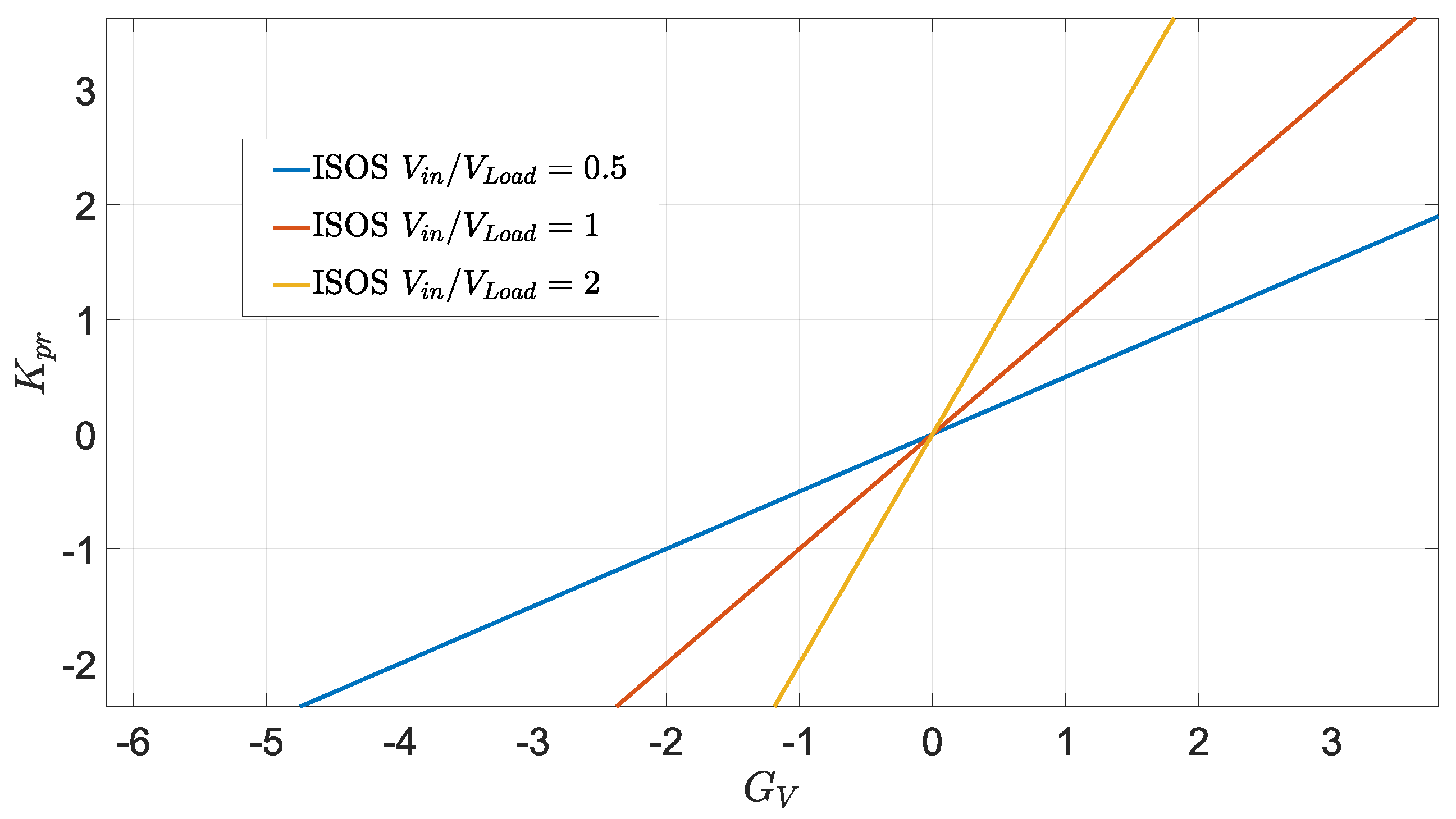

3.5. Input-Series-Output-Series Topology (ISOS)

3.6. ISOS-Based Converters

3.7. Input-Parallel-Output-Parallel Topology (IPOP)

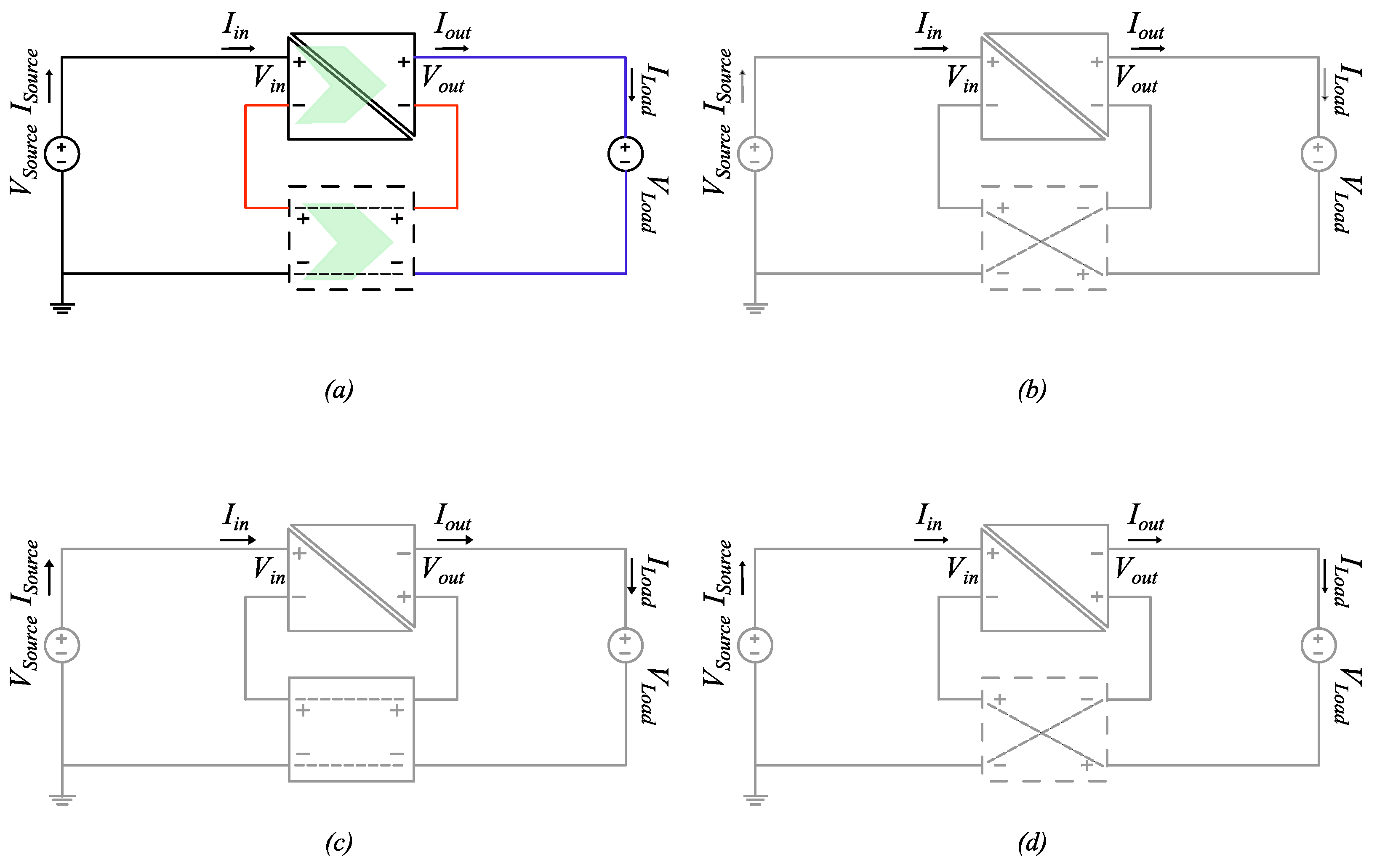

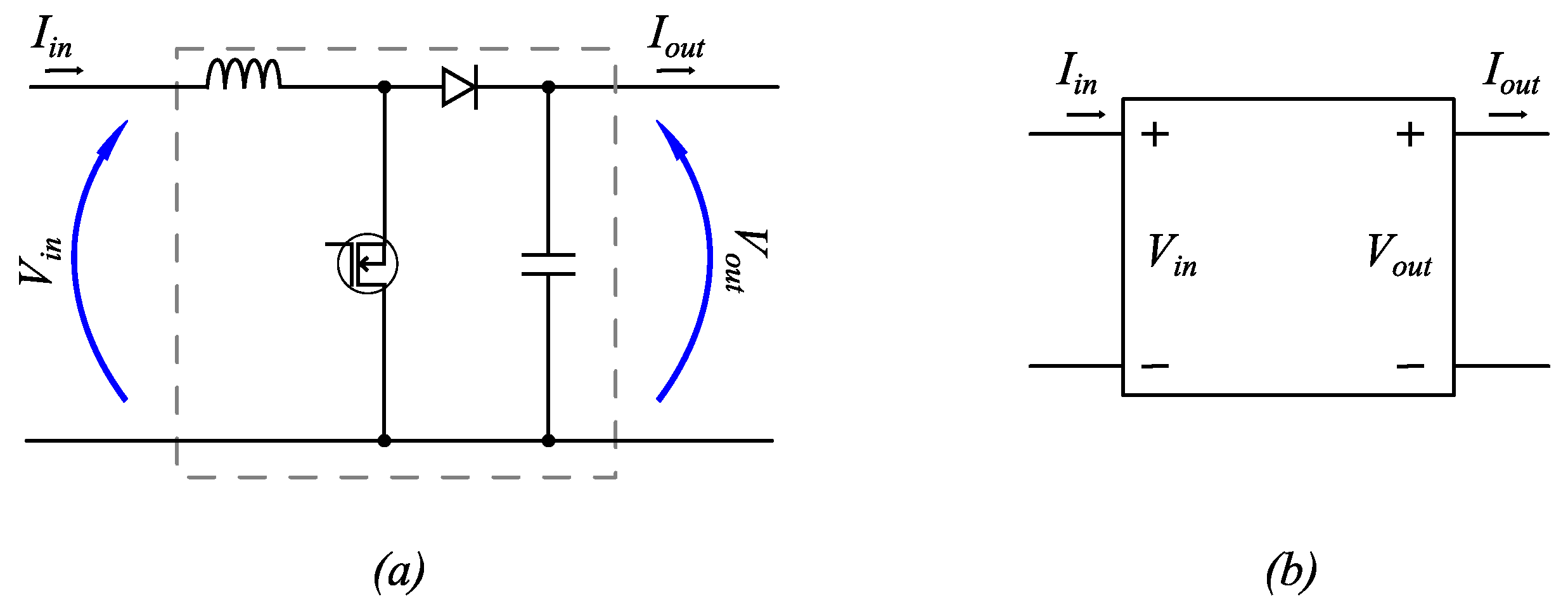

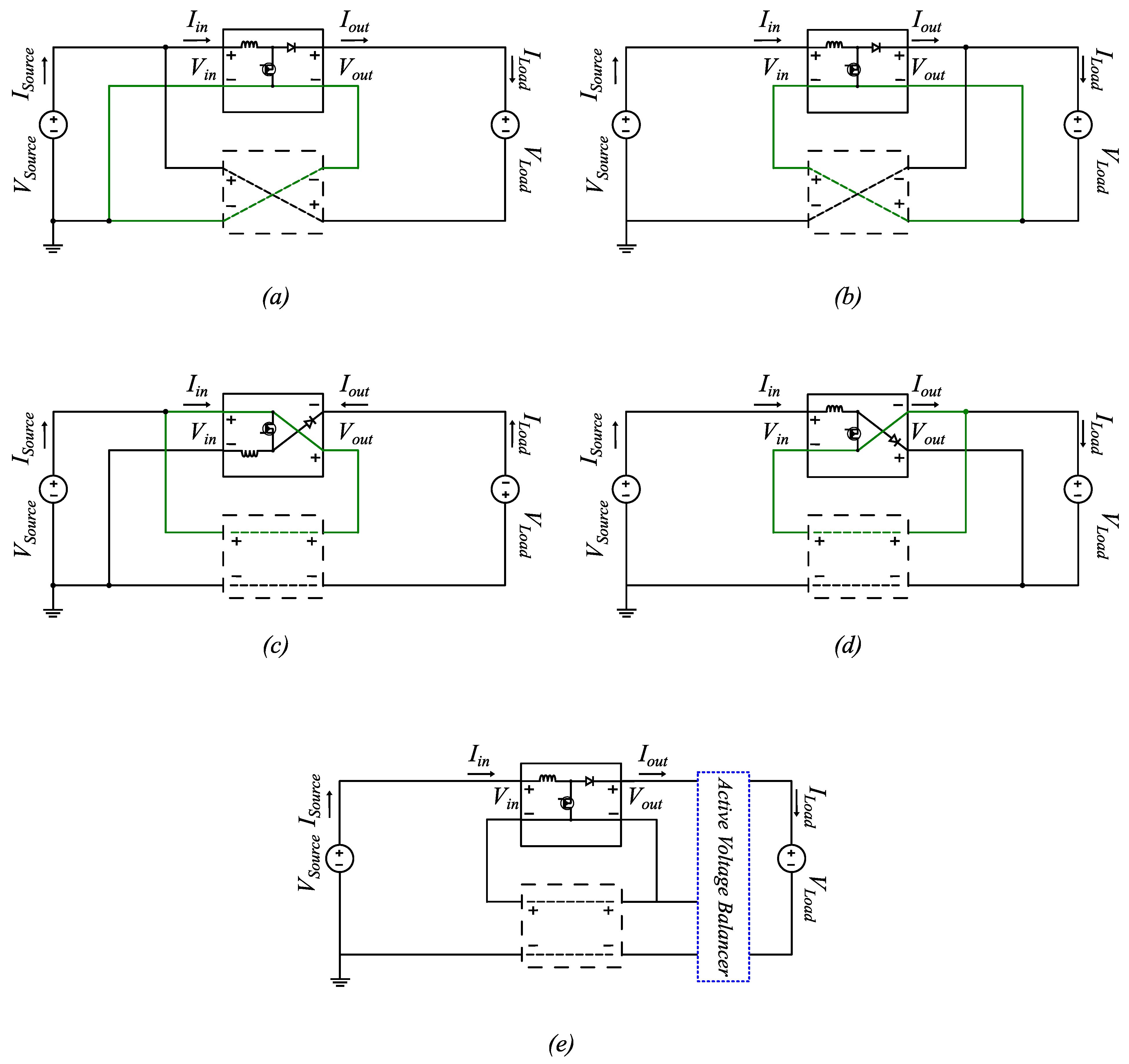

4. Non-Isolated PPP Architectures

4.1. Fractional Topology

4.2. Fractional Topology-Based Converters

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Li, C.; Cobos, J.A. Classification of Differential Power Processing Architectures Based on VA Area Modeling. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 10, 7849–7866. [Google Scholar] [CrossRef]

- dos Santos, N.G.F.; Zientarski, J.R.R.; da Silva Martins, M.L. A Review of Series-Connected Partial Power Converters for DC–DC Applications. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 10, 7825–7838. [Google Scholar] [CrossRef]

- Wouters, H.; Martinez, W. Bidirectional Onboard Chargers for Electric Vehicles: State-of-the-Art and Future Trends. IEEE Trans. Power Electron. 2024, 39, 693–716. [Google Scholar] [CrossRef]

- Anzola, J.; Aizpuru, I.; Romero, A.A.; Loiti, A.A.; Lopez-Erauskin, R.; Artal-Sevil, J.S.; Bernal, C. Review of Architectures Based on Partial Power Processing for DC-DC Applications. IEEE Access 2020, 8, 103405–103418. [Google Scholar] [CrossRef]

- Müller, S.; Deicke, M.; Doncker, R.W.D. Doubly fed induction generator systems for wind turbines. IEEE Ind. Appl. Mag. 2002, 8, 26–33. [Google Scholar] [CrossRef]

- Anzola, J.; Aizpuru, I.; Arruti, A.; Artal-Sevil, J.S.; Bernal, C. Demystifying Non-Isolated DC–DC Topologies on Partial Power Processing Architectures. Electronics 2022, 11, 480. [Google Scholar] [CrossRef]

- Liu, C.; Zhuang, K.; Pei, Z.; Zhu, D.; Li, X.; Yu, Q.; Xin, H. Hybrid SiC-Si DC–AC Topology: SHEPWM Si-IGBT Master Unit Handling High Power Integrated With Partial-Power SiC-MOSFET Slave Unit Improving Performance. IEEE Trans. Power Electron. 2022, 37, 3085–3098. [Google Scholar] [CrossRef]

- Kim, J.W. LLC Converter with Hold-Up Time Compensation using Partial Power Process with Semi-Active Bridge Rectifier. IEEE Trans. Power Electron. 2024; Early Access. [Google Scholar] [CrossRef]

- Lopez, D.; Muller, N.; Renaudineau, H.; Kouro, S.; Rodriguez, J. Partial power differential-mode inverter for photovoltaic microinverter applications. In Proceedings of the IECON 2021—47th Annual Conference of the IEEE Industrial Electronics Society, Toronto, ON, Canada, 13–16 October 2021. [Google Scholar] [CrossRef]

- de Andrade, J.M.; Coelho, R.F.; Lazzarin, T.B. Partial Power Processing and Efficiency Analysis of dc-dc Differential Converters. Energies 2022, 15, 1159. [Google Scholar] [CrossRef]

- Zapata, J.; Kouro, S.; Carrasco, G.; Renaudineau, H. Step-Up Partial Power DC-DC Converters for Two-Stage PV Systems with Interleaved Current Performance. Energies 2018, 11, 357. [Google Scholar] [CrossRef]

- Mira, M.C.; Zhang, Z.; Jorgensen, K.L.; Andersen, M.A.E. Fractional Charging Converter With High Efficiency and Low Cost for Electrochemical Energy Storage Devices. IEEE Trans. Ind. Appl. 2019, 55, 7461–7470. [Google Scholar] [CrossRef]

- Tao, X.; Wang, F.; Zhuo, F. A Four-quadrant Buck-boost Partial Power DC/DC Converter for Battery Energy Storage System. In Proceedings of the 2023 25th European Conference on Power Electronics and Applications (EPE’23 ECCE Europe), Aalborg, Denmark, 4–8 September 2023. [Google Scholar] [CrossRef]

- Abdel-Rahim, O.; Chub, A.; Blinov, A.; Vinnikov, D. Current-Fed Dual Inductor Push-Pull Partial Power Converter. In Proceedings of the 2022 IEEE 20th International Power Electronics and Motion Control Conference (PEMC), Brasov, Romania, 25–28 September 2022. [Google Scholar] [CrossRef]

- Liu, C.; Zhang, Z.; Ouyang, Z.; Andersen, M.A.E.; Zsurzsan, T.G. Analysis and Comparison of Isolated Converter based Step-Down Partial Power Processing Configurations. In Proceedings of the 2022 International Power Electronics Conference (IPEC-Himeji 2022-ECCE Asia), Himeji, Japan, 15–19 May 2022. [Google Scholar] [CrossRef]

- Zapata, J.W.; Kouro, S.; Carrasco, G.; Renaudineau, H.; Meynard, T.A. Analysis of Partial Power DC–DC Converters for Two-Stage Photovoltaic Systems. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 591–603. [Google Scholar] [CrossRef]

- Rojas, J.; Renaudineau, H.; Kouro, S.; Rivera, S. Partial power DC-DC converter for electric vehicle fast charging stations. In Proceedings of the IECON 2017—43rd Annual Conference of the IEEE Industrial Electronics Society, Beijing, China, 29 October–1 November 2017. [Google Scholar] [CrossRef]

- Wittenbreder, E. Topology selection by the numbers—Part one. Power Electron. Technol. 2006, 32, 32–36. [Google Scholar]

- Wittenbreder, E. Topology selection by the numbers—Part two. Power Electron. Technol. 2006, 33, 28–32. [Google Scholar]

- Hassanpour, N.; Chub, A.; Blinov, A.; Vinnikov, D. Comparison of Full Power and Partial Power Buck-Boost DC-DC Converters for Residential Battery Energy Storage Applications. In Proceedings of the 2022 IEEE 16th International Conference on Compatibility, Power Electronics, and Power Engineering (CPE-POWERENG), Birmingham, UK, 29 June–1 July 2022. [Google Scholar] [CrossRef]

- Jørgensen, K. Towards Partial Power Processing with Built in Impedance Spectroscopy. Ph.D. Thesis, Technical University of Denmark, Kgs. Lyngby, Denmark, 2020. [Google Scholar]

- Mira, M.C.; Zhang, Z.; Michael Andersen, A.E. Analysis and Comparison of dc/dc Topologies in Partial Power Processing Configuration for Energy Storage Systems. In Proceedings of the 2018 International Power Electronics Conference (IPEC-Niigata 2018-ECCE Asia), Niigata, Japan, 20–24 May 2018; pp. 1351–1357. [Google Scholar] [CrossRef]

- Liu, C. Partial Power Processing for High Efficient Power Converters. Ph.D. Thesis, Technical University of Denmark, Kgs. Lyngby, Denmark, 2023. [Google Scholar]

- Pittini, R.; Mira, M.C.; Zhang, Z.; Knott, A.; Andersen, M.A. Analysis and comparison based on component stress factor of dual active bridge and isolated full bridge boost converters for bidirectional fuel cells systems. In Proceedings of the 2014 International Power Electronics and Application Conference and Exposition, Shanghai, China, 5–8 November 2014; pp. 1026–1031. [Google Scholar] [CrossRef]

- Zientarski, J.R.R.; Martins, M.L.d.S.; Pinheiro, J.R.; Hey, H.L. Series-Connected Partial-Power Converters Applied to PV Systems: A Design Approach Based on Step-Up/Down Voltage Regulation Range. IEEE Trans. Power Electron. 2018, 33, 7622–7633. [Google Scholar] [CrossRef]

- IEEE Std 1459-2010; IEEE Standard Definitions for the Measurement of Electric Power Quantities Under Sinusoidal, Nonsinusoidal, Balanced, or Unbalanced Conditions. IEEE Power & Energy Society: Piscataway, NJ, USA, 2010. [CrossRef]

- Santos, N.G.F.; Hey, H.L.; Zientarski, J.R.R.; Martins, M.L.d.S. Piecewise Fryze power theory analysis applied to PWM DC–DC converters. IET Power Electron. 2020, 13, 2029–2038. [Google Scholar] [CrossRef]

- Zhao, J.; Yeates, K.; Han, Y. Analysis of high efficiency DC/DC converter processing partial input/output power. In Proceedings of the 2013 IEEE 14th Workshop on Control and Modeling for Power Electronics (COMPEL), Salt Lake City, UT, USA, 23–26 June 2013. [Google Scholar] [CrossRef]

- Anzola, J.; Aizpuru, I.; Arruti, A. Non-Isolated Partial Power Converter for Electric Vehicle Fast Charging Stations. In Proceedings of the 2020 IEEE 11th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Dubrovnik, Croatia, 28 September–1 October 2020. [Google Scholar] [CrossRef]

- Zapata, J.; Kouro, S.; Carrasco, G.; Meynard, T. Step-Down Partial Power DC-DC Converters for Two-Stage Photovoltaic String Inverters. Electronics 2019, 8, 87. [Google Scholar] [CrossRef]

- Mishra, S.; Tamballa, S.; Pallantala, M.; Raju, S.; Mohan, N. Cascaded Dual-Active Bridge Cell Based Partial Power Converter for Battery Emulation. In Proceedings of the 2019 20th Workshop on Control and Modeling for Power Electronics (COMPEL), Toronto, ON, Canada, 17–20 June 2019. [Google Scholar] [CrossRef]

- Zheng, K.; Zhang, W.; Wu, X.; Jing, L.; Zhao, H. Partial Power Conversion for Increased Energy Storage Capability of Li-ion Battery Energy Storage System. IEEE Trans. Ind. Electron. 2023, 71, 4742–4752. [Google Scholar] [CrossRef]

- Abdel-Rahim, O.; Chub, A.; Blinov, A.; Vinnikov, D. Performance Evaluation of Step-Up/Down Current-Source Partial Power Converters for PV Applications. In Proceedings of the 2022 IEEE 63th International Scientific Conference on Power and Electrical Engineering of Riga Technical University (RTUCON), Riga, Latvia, 10–12 October 2022; pp. 1–5. [Google Scholar] [CrossRef]

- Köse, H.; Aydemir, M.T. Design and implementation of a 22kW full-bridge push–pull series partial power converter for stationary battery energy storage system with battery charger. Meas. Control 2020, 53, 1454–1464. [Google Scholar] [CrossRef]

- Min, B.D.; Lee, J.P.; Kim, J.H.; Kim, T.J.; Yoo, D.W.; Song, E.H. A New Topology With High Efficiency Throughout All Load Range for Photovoltaic PCS. IEEE Trans. Ind. Electron. 2009, 56, 4427–4435. [Google Scholar] [CrossRef]

- Wei, R.; Ding, L.; Li, Y. Efficiency-Oriented Optimized Design and Control of Hybrid FSBB-CLLC Converters with Partial Power Processing Capability. IEEE Trans. Power Electron. 2024; Early Access. [Google Scholar] [CrossRef]

- Renaudineau, H.; Flores-Bahamonde, F.; Kouro, S.; Zapata, J.W. Single-Phase partial power unfolding inverter for photovoltaic string application. In Proceedings of the 2021 IEEE 30th International Symposium on Industrial Electronics (ISIE), Kyoto, Japan, 20–23 June 2021. [Google Scholar] [CrossRef]

- Anzola, J.; Aizpuru, I.; Arruti, A. Partial Power Processing Based Converter for Electric Vehicle Fast Charging Stations. Electronics 2021, 10, 260. [Google Scholar] [CrossRef]

- Gao, S.; Zhang, Y.; Wang, Y.; Liu, J.; Xu, D. An Optimal Control Strategy for the DAB-Based Partial Power Converter Based on Extended-Phase-Shift Control. IEEE Open J. Power Electron. 2023, 4, 817–827. [Google Scholar] [CrossRef]

- Hernandez, M.S.; Renaudineau, H.; Concha, D.; Llor, A.M. Series Partial Power Pre-Regulator for DCX-based Stand-Alone Green Hydrogen Production. In Proceedings of the 2021 IEEE 30th International Symposium on Industrial Electronics (ISIE), Kyoto, Japan, 20–23 June 2021. [Google Scholar] [CrossRef]

- Grbović, P.J.; Delarue, P.; Le Moigne, P. Boost diode rectifier for three-phase variable speed drives supplied from the single-phase mains: Analysis and design. In Proceedings of the IECON 2012—38th Annual Conference on IEEE Industrial Electronics Society, Montreal, QC, Canada, 25–28 October 2012; pp. 274–280. [Google Scholar] [CrossRef]

- Giri, R.; Ayyanar, R.; Ledezma, E. Input-series and output-series connected modular DC-DC converters with active input voltage and output voltage sharing. In Proceedings of the Nineteenth Annual IEEE Applied Power Electronics Conference and Exposition, 2004, APEC’04, Anaheim, CA, USA, 22–26 February 2004; Volume 3, pp. 1751–1756. [Google Scholar] [CrossRef]

- Lopušina, I.; Grbović, P. Comparative Analysis of Input-Series-Output-Series Partial Power Rated DC to DC Converters. In Proceedings of the 2021 21st International Symposium on Power Electronics (Ee), Novi Sad, Serbia, 27–30 October 2021; pp. 1–7. [Google Scholar] [CrossRef]

- Wang, F.; Lei, Z.; Xu, X.; Shu, X. Topology Deduction and Analysis of Voltage Balancers for DC Microgrid. IEEE J. Emerg. Sel. Top. Power Electron. 2017, 5, 672–680. [Google Scholar] [CrossRef]

- Kim, N.; Parkhideh, B. Comparative Analysis of Non-Isolated and Isolated Type Partial-Power Optimizers for PV-Battery Series Inverter Architecture. In Proceedings of the 2018 IEEE Energy Conversion Congress and Exposition (ECCE), Portland, OR, USA, 23–27 September 2018. [Google Scholar] [CrossRef]

- Sadaf, S.; Bhaskar, M.S.; Meraj, M.; Iqbal, A.; Al-Emadi, N. A Novel Modified Switched Inductor Boost Converter With Reduced Switch Voltage Stress. IEEE Trans. Ind. Electron. 2021, 68, 1275–1289. [Google Scholar] [CrossRef]

- Artal-Sevil, J.; Anzola, J.; Ballestín-Bernad, V.; Bernal-Agustín, J. Analysis and Implementation of different non-isolated Partial-Power Processing Architectures based on the Cuk Converter. In Proceedings of the 2022 24th European Conference on Power Electronics and Applications (EPE’22 ECCE Europe), Hannover, Germany, 5–9 September 2022; pp. 1–10. [Google Scholar]

- Xue, F.; Yu, R.; Huang, A. Fractional converter for high efficiency high power battery energy storage system. In Proceedings of the 2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, USA, 1–5 October 2017; pp. 5144–5150. [Google Scholar] [CrossRef]

| Source | Load | Connection Diagram from Figure 4 |

|---|---|---|

| (a) | ||

| (b) | ||

| (c) | ||

| (a) | ||

| (b) | ||

| (c) |

| Source | Load | Connection Diagram from Figure 7 |

|---|---|---|

| (a) | ||

| (b) | ||

| (c) | ||

| (a) | ||

| (b) | ||

| (c) |

| Reference | Converter | Topology | Application | System Power [kW] | [%] | ||

|---|---|---|---|---|---|---|---|

| [13] | H-bridge+CLLC | ISOP (a) | 16% | 1.00 | Battery | 45.0 | 97.91 |

| [39] | DAB | ISOP (a) | 25% | 0.75 | EV | 1.00 | 97.00 |

| [16] | isolated full-bridge | ISOP (a) | 13% | 0.84 | PV | 0.82 | 98.50 |

| [16] | Full-bridge | ISOP (b) | 11% | 1.10 | PV | 1.00 | 97.50 |

| [38] | DAB | ISOP (a) | 19% | 0.45 | Battery | 2.20 | 99.62 |

| [40] | Integrated full-bridge | ISOP (a) | 25% | 0.75 | PV | 2.0 | 98.60 |

| [37] | Full-bridge | ISOP (a) | 12% | 0.89 | PV | 3.30 | 97.50 |

| [28] | Flyback | ISOP (c) | 58% | 1.40 | PV | 0.10 | 92.00 |

| Source | Load | Figure 10 Diagram | Viability |

|---|---|---|---|

| (a) | yes | ||

| (b) | no | ||

| (c) | no | ||

| (d) | no | ||

| (a) | yes | ||

| (b) | no | ||

| (c) | no | ||

| (d) | no |

| Source | Load | Connection Diagram from Figure 14 |

|---|---|---|

| (a) | ||

| (b) | ||

| (c) | ||

| (d) | ||

| (e) | ||

| (a) | ||

| (b) | ||

| (c) | ||

| (d) | ||

| (e) |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Gsous, O.; Rizk, R.; Barbón, A.; Georgious, R. Review of DC-DC Partial Power Converter Configurations and Topologies. Energies 2024, 17, 1496. https://doi.org/10.3390/en17061496

Gsous O, Rizk R, Barbón A, Georgious R. Review of DC-DC Partial Power Converter Configurations and Topologies. Energies. 2024; 17(6):1496. https://doi.org/10.3390/en17061496

Chicago/Turabian StyleGsous, Omar, Reem Rizk, Arsenio Barbón, and Ramy Georgious. 2024. "Review of DC-DC Partial Power Converter Configurations and Topologies" Energies 17, no. 6: 1496. https://doi.org/10.3390/en17061496

APA StyleGsous, O., Rizk, R., Barbón, A., & Georgious, R. (2024). Review of DC-DC Partial Power Converter Configurations and Topologies. Energies, 17(6), 1496. https://doi.org/10.3390/en17061496