A Flyback Converter with a Simple Passive Circuit for Improving Power Efficiency

Abstract

1. Introduction

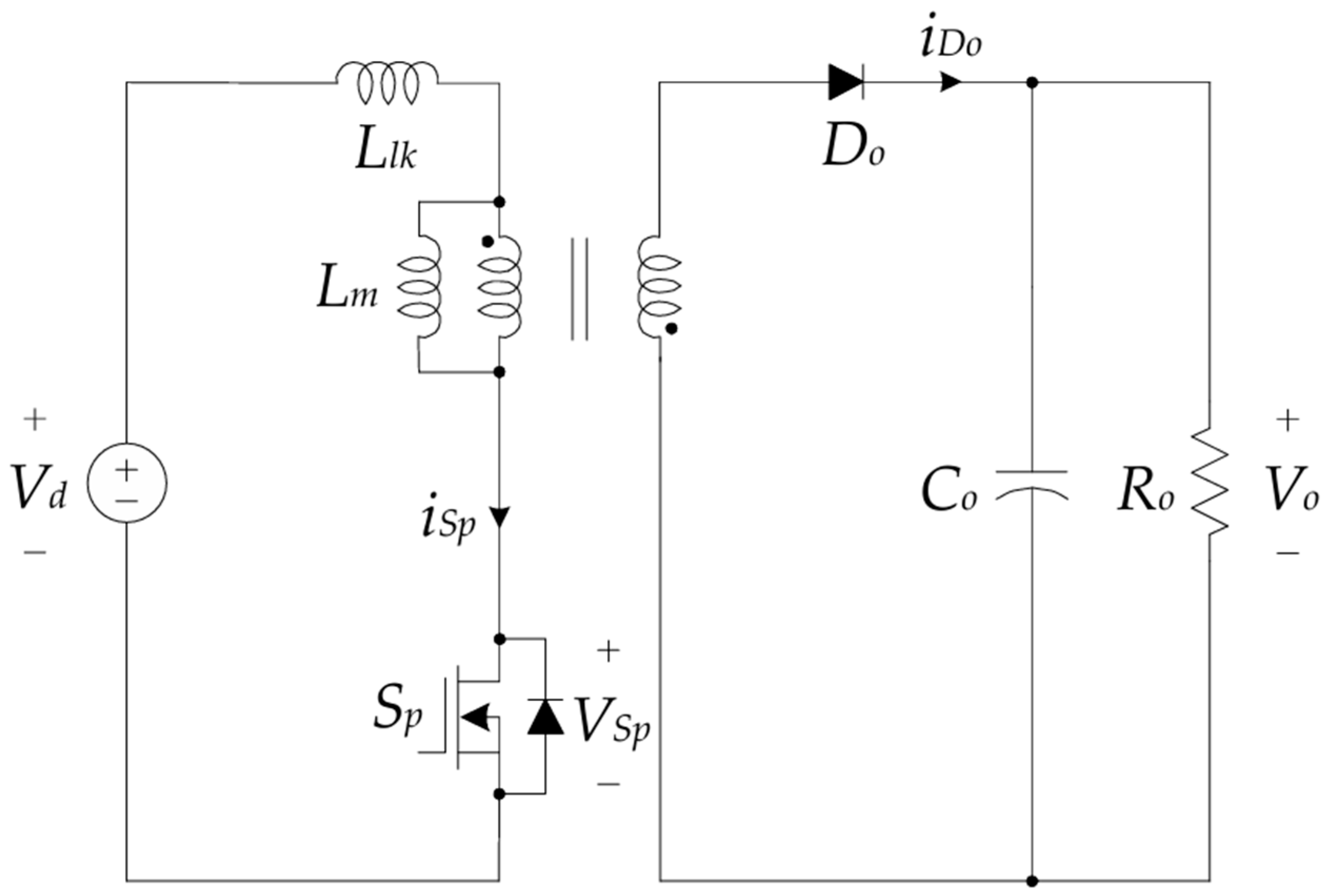

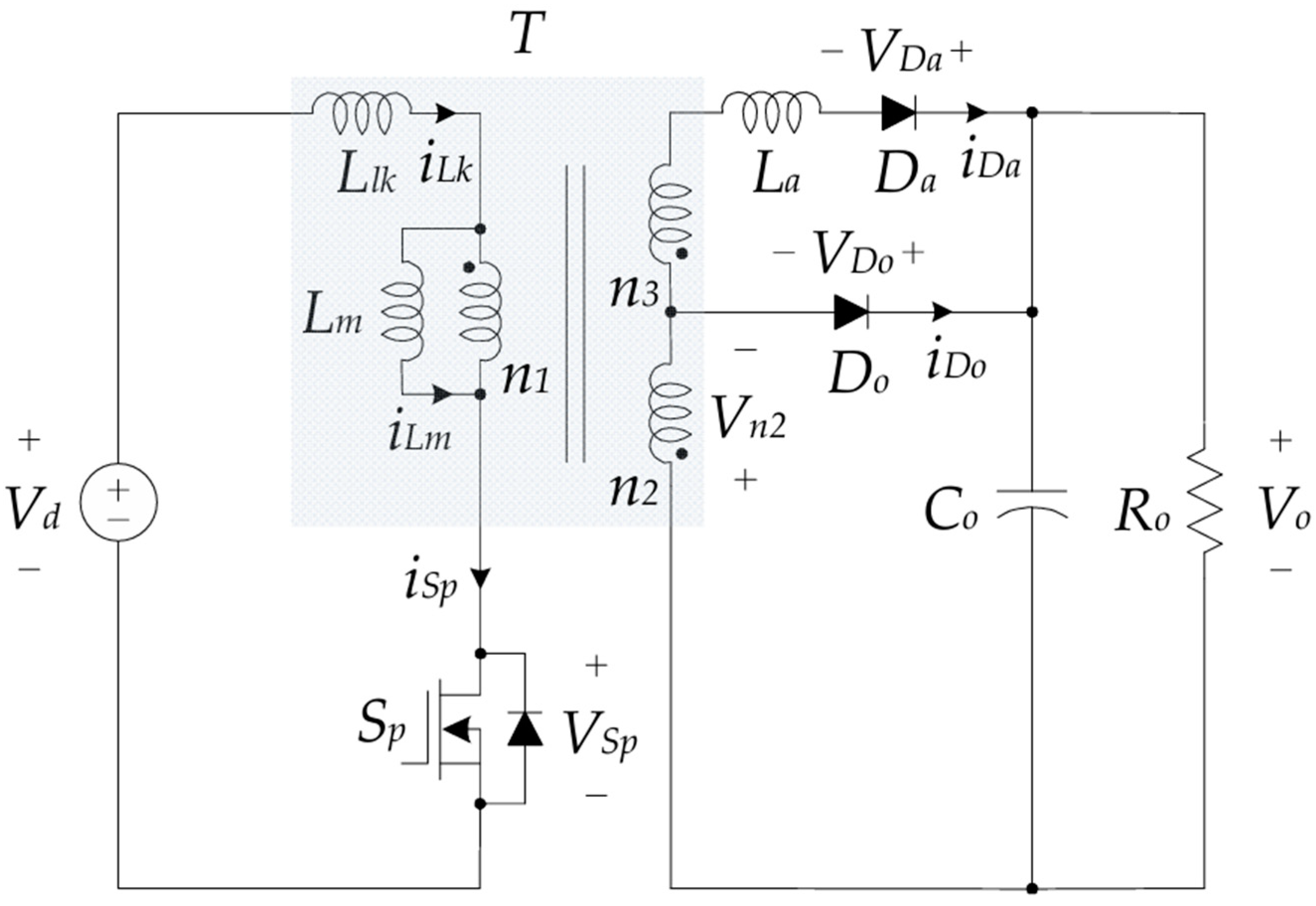

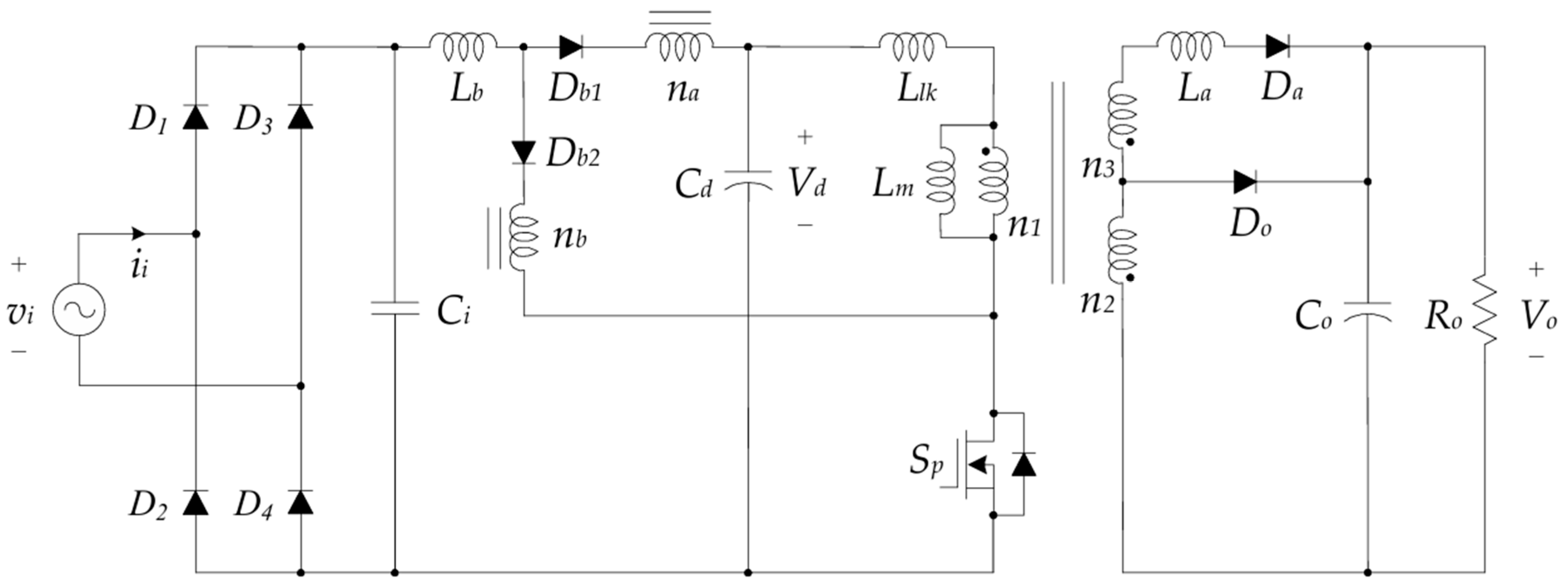

2. Proposed Converter

2.1. Circuit Configuration

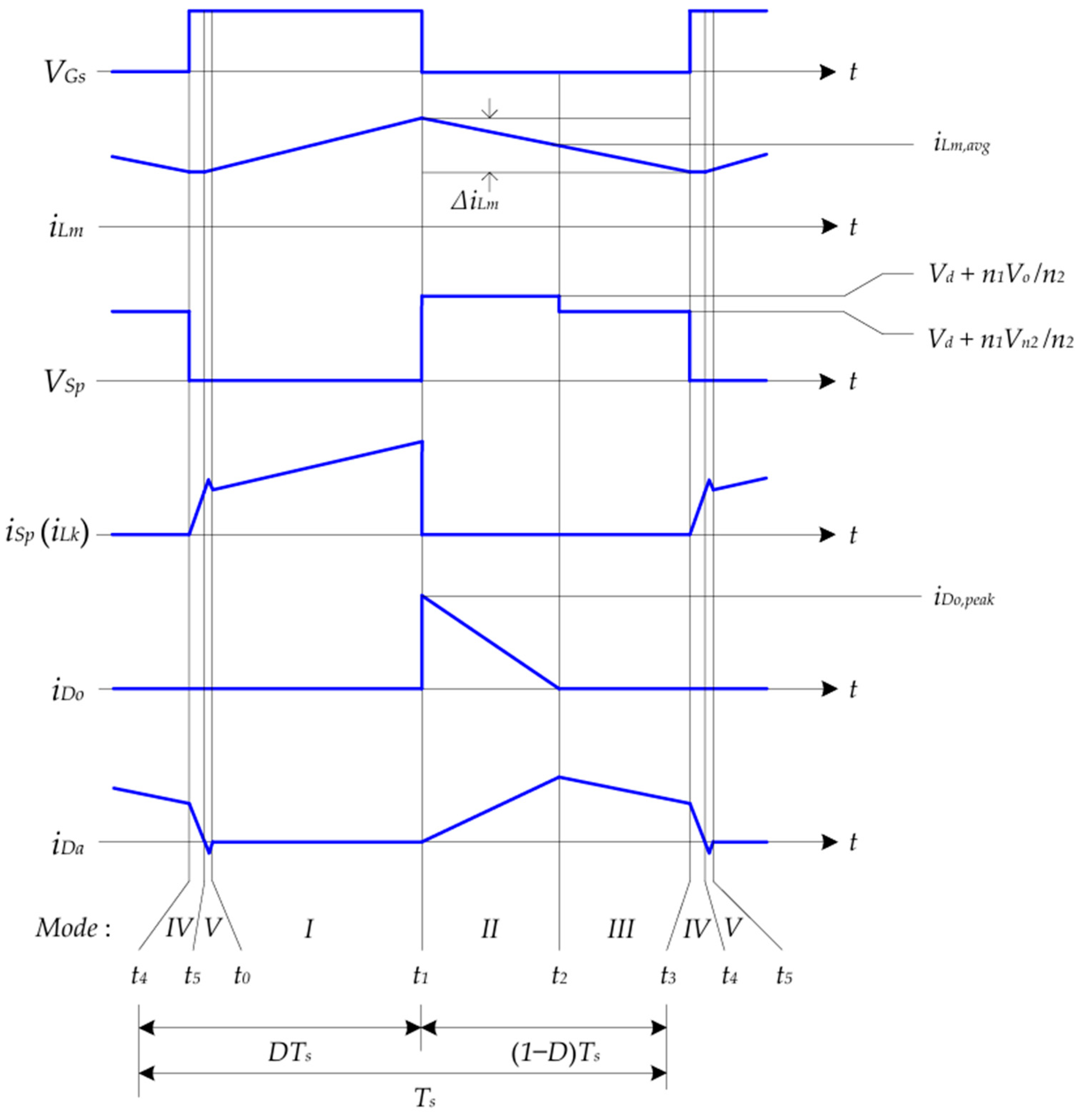

2.2. Operation Principle

3. Design Considerations

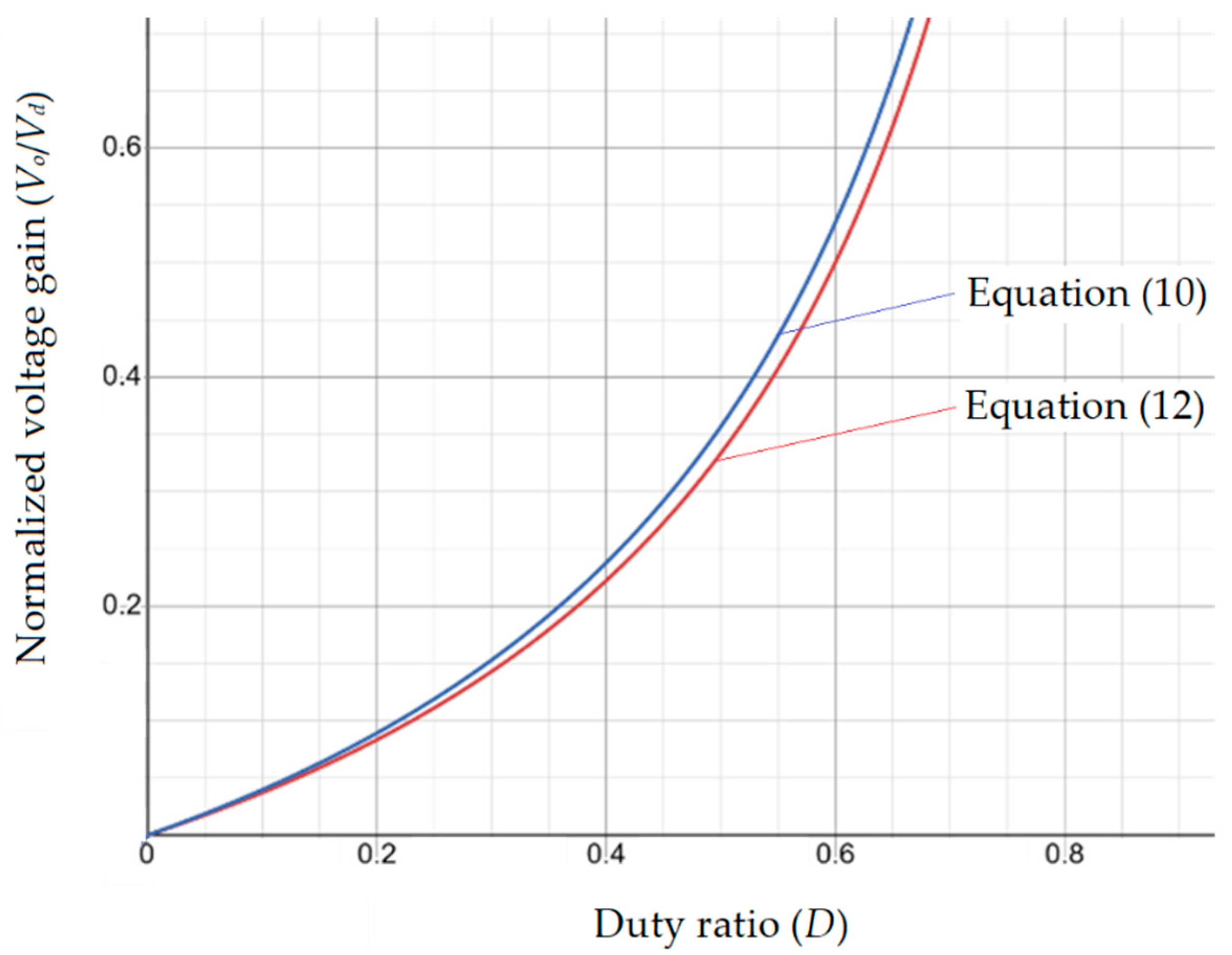

3.1. Voltage Gain and Magnetizing Inductance

3.2. Auxiliary Winding Turns and Additional Inductor

3.3. Output Capacitor and Switching Devices

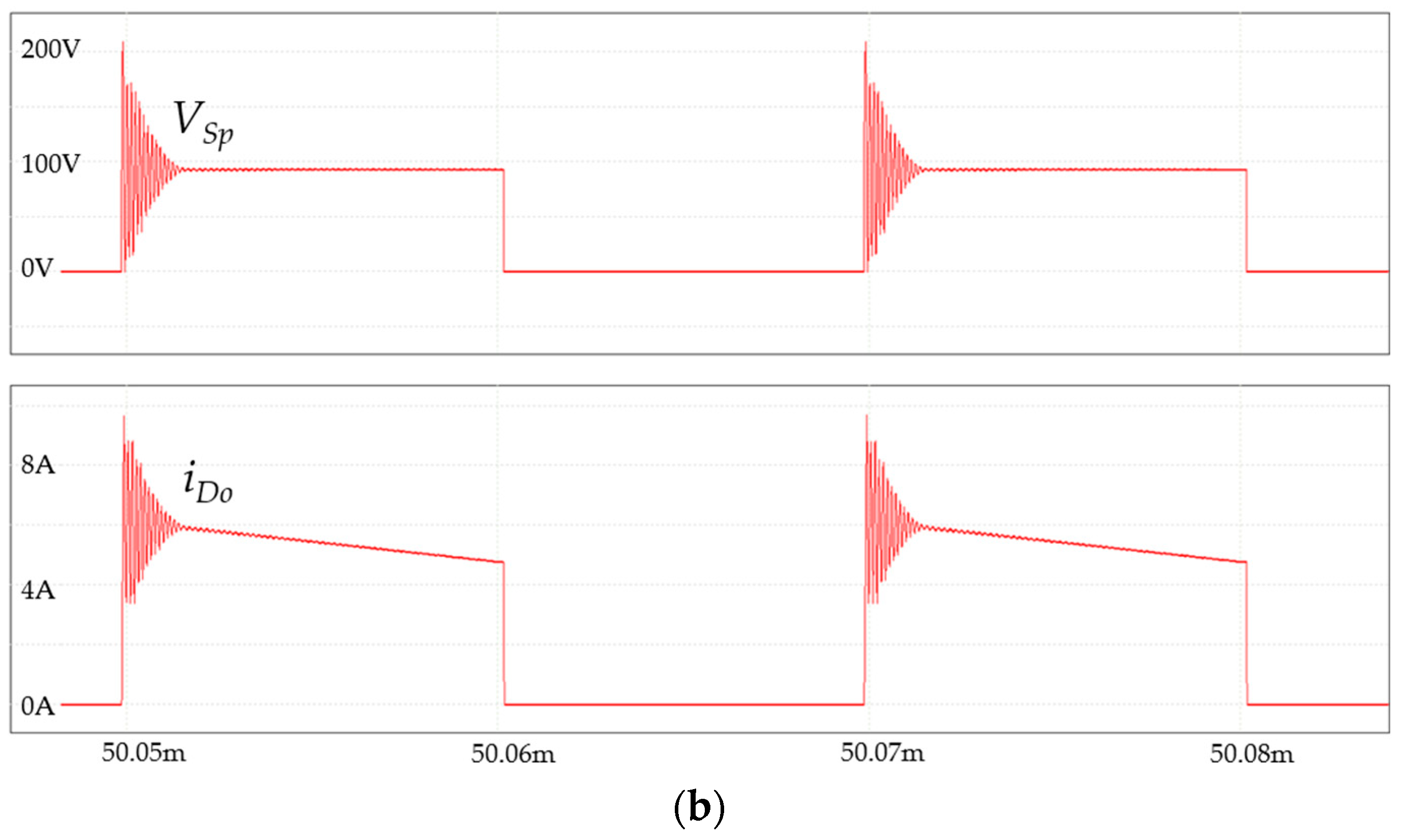

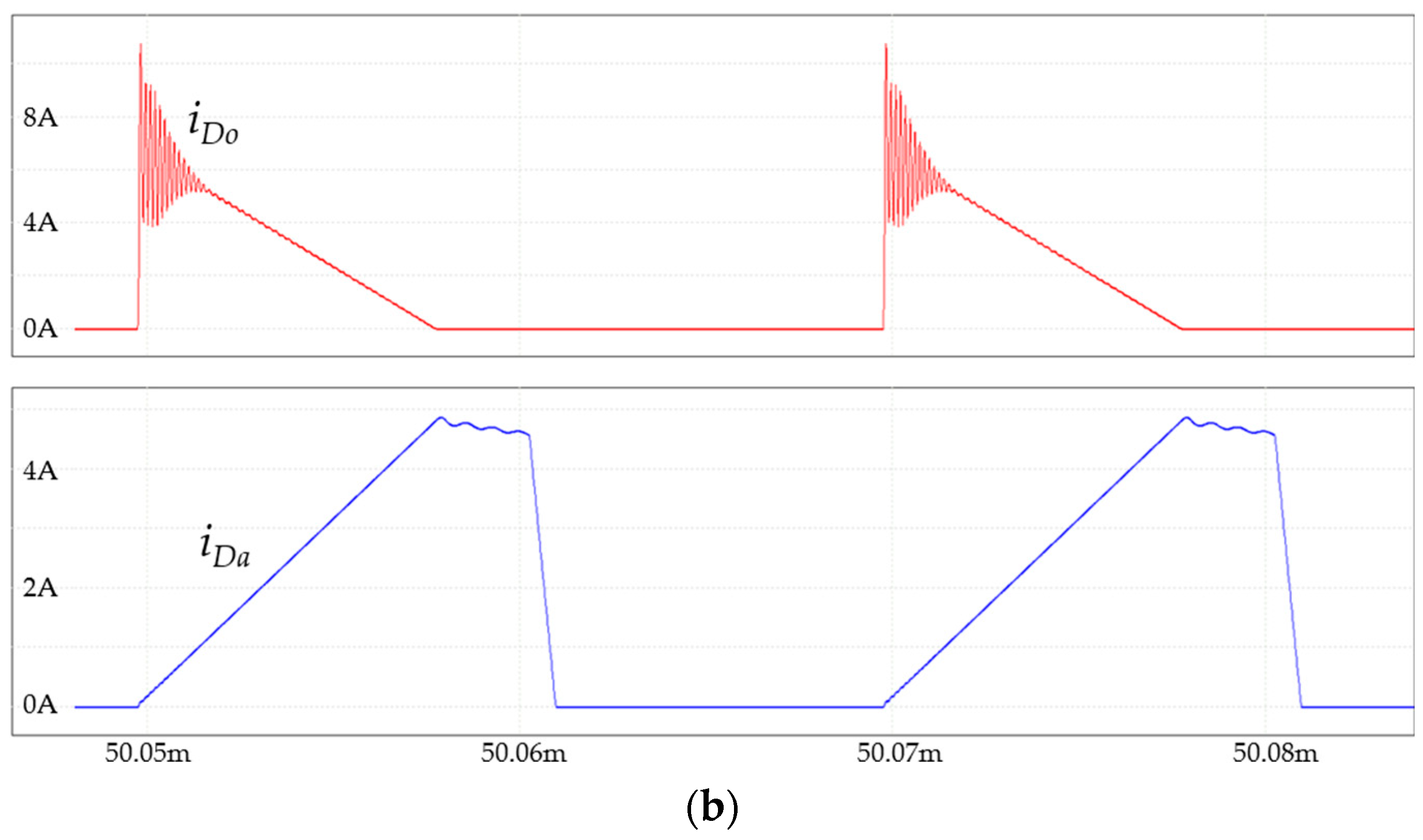

3.4. Simulation Verification

4. Experimental Results

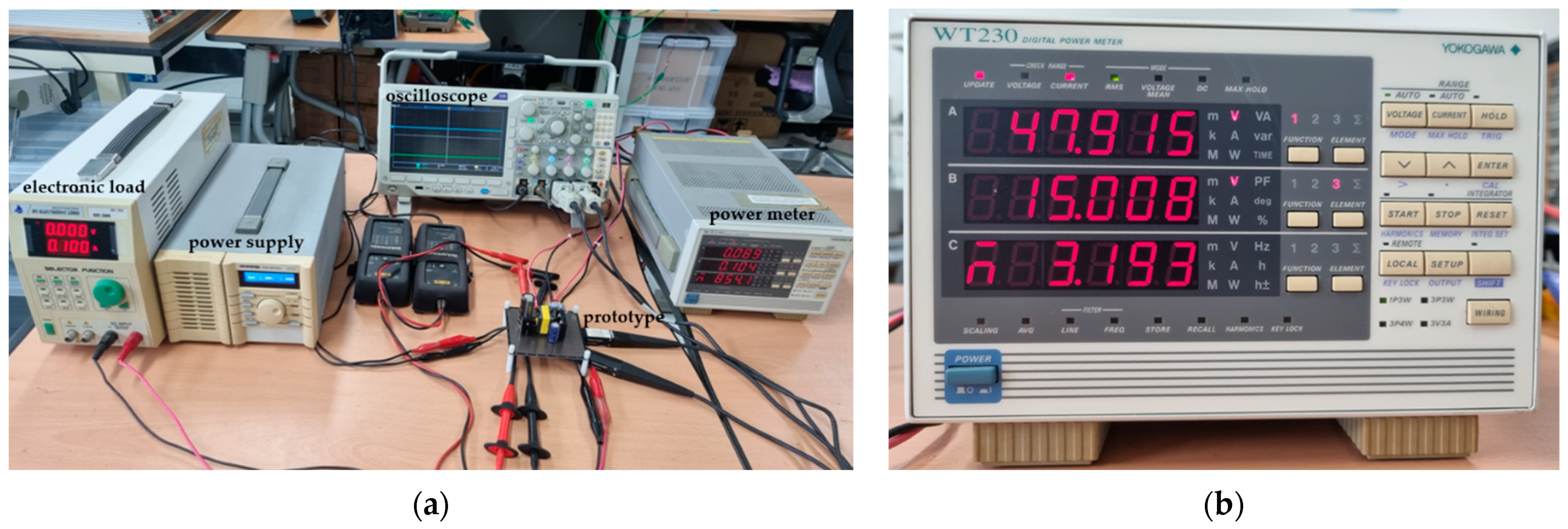

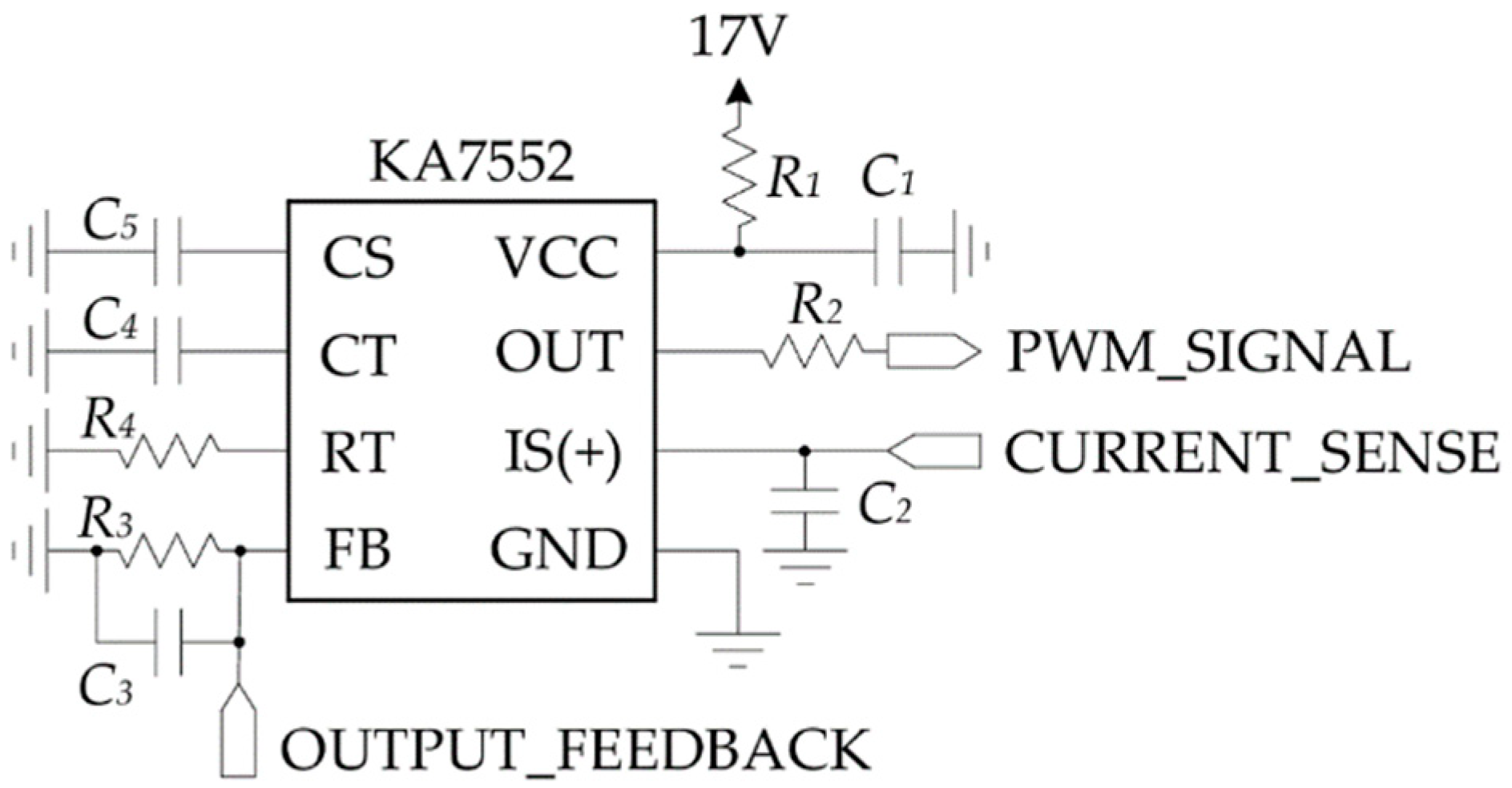

4.1. Experimental Setup

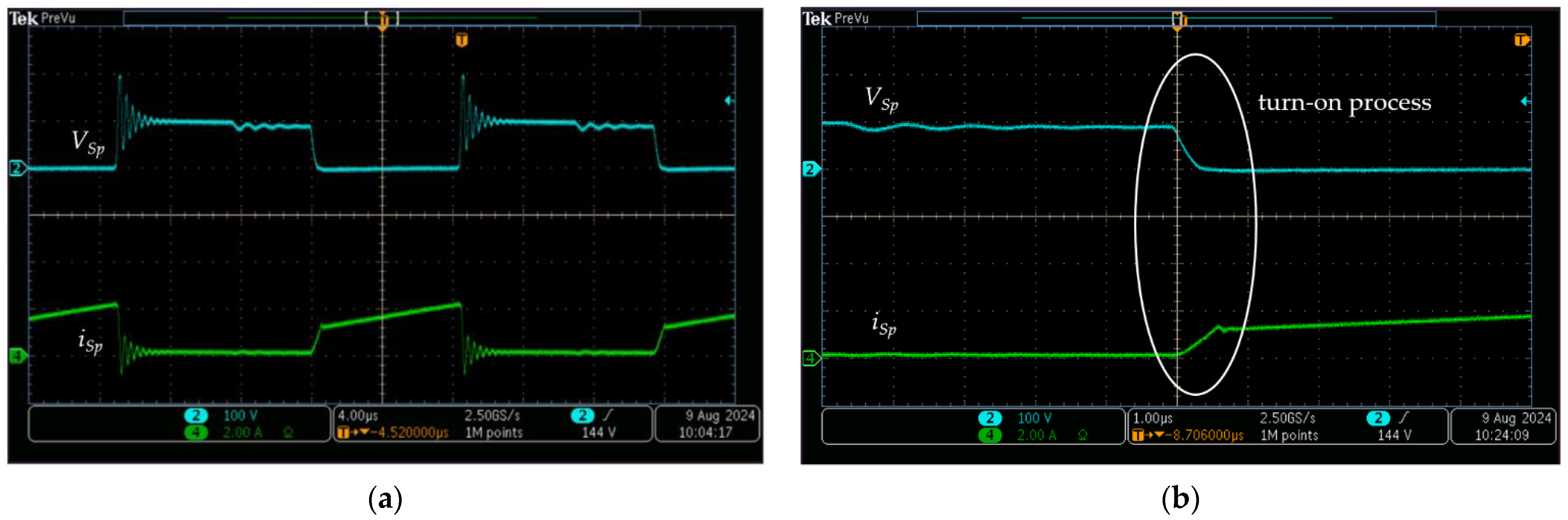

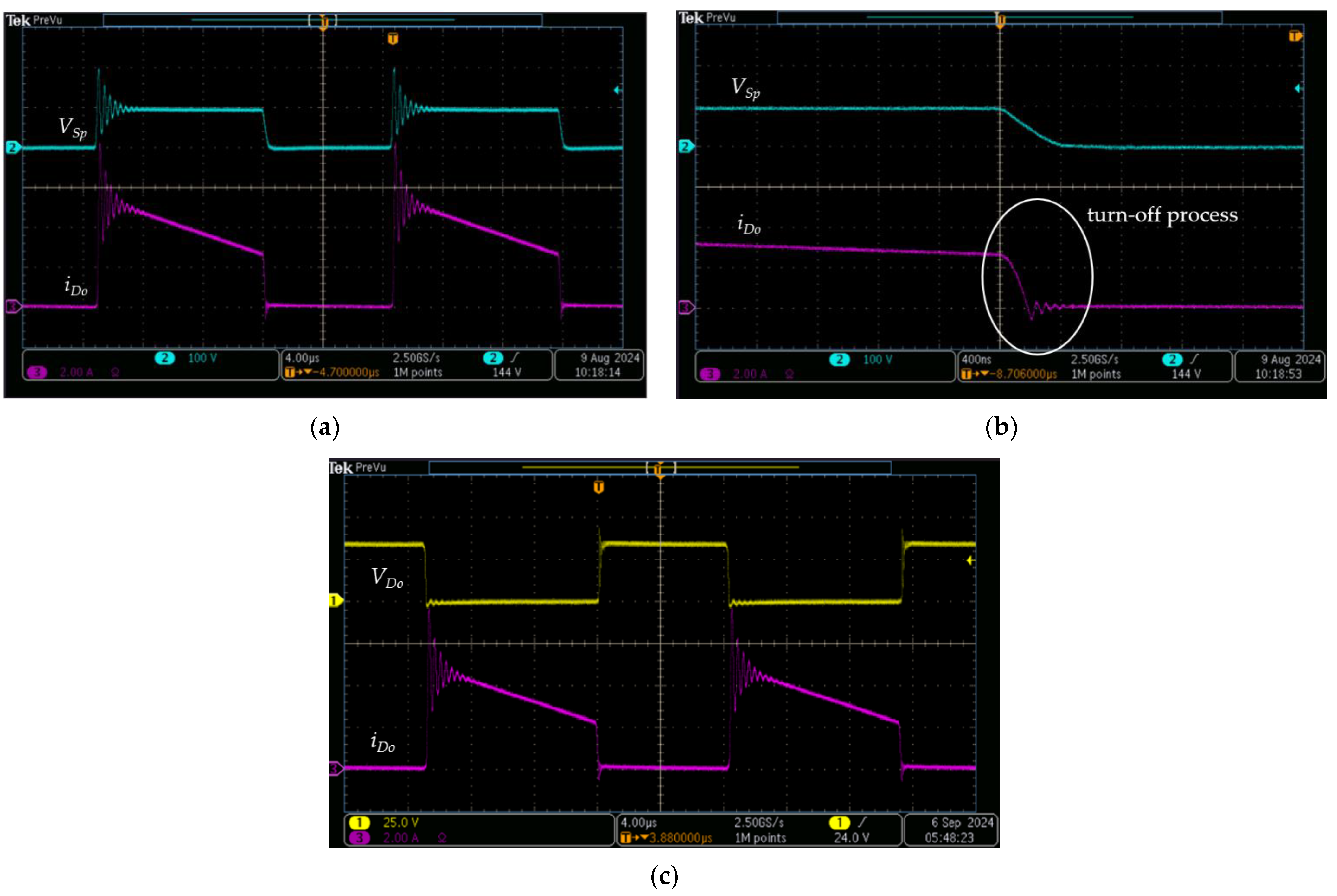

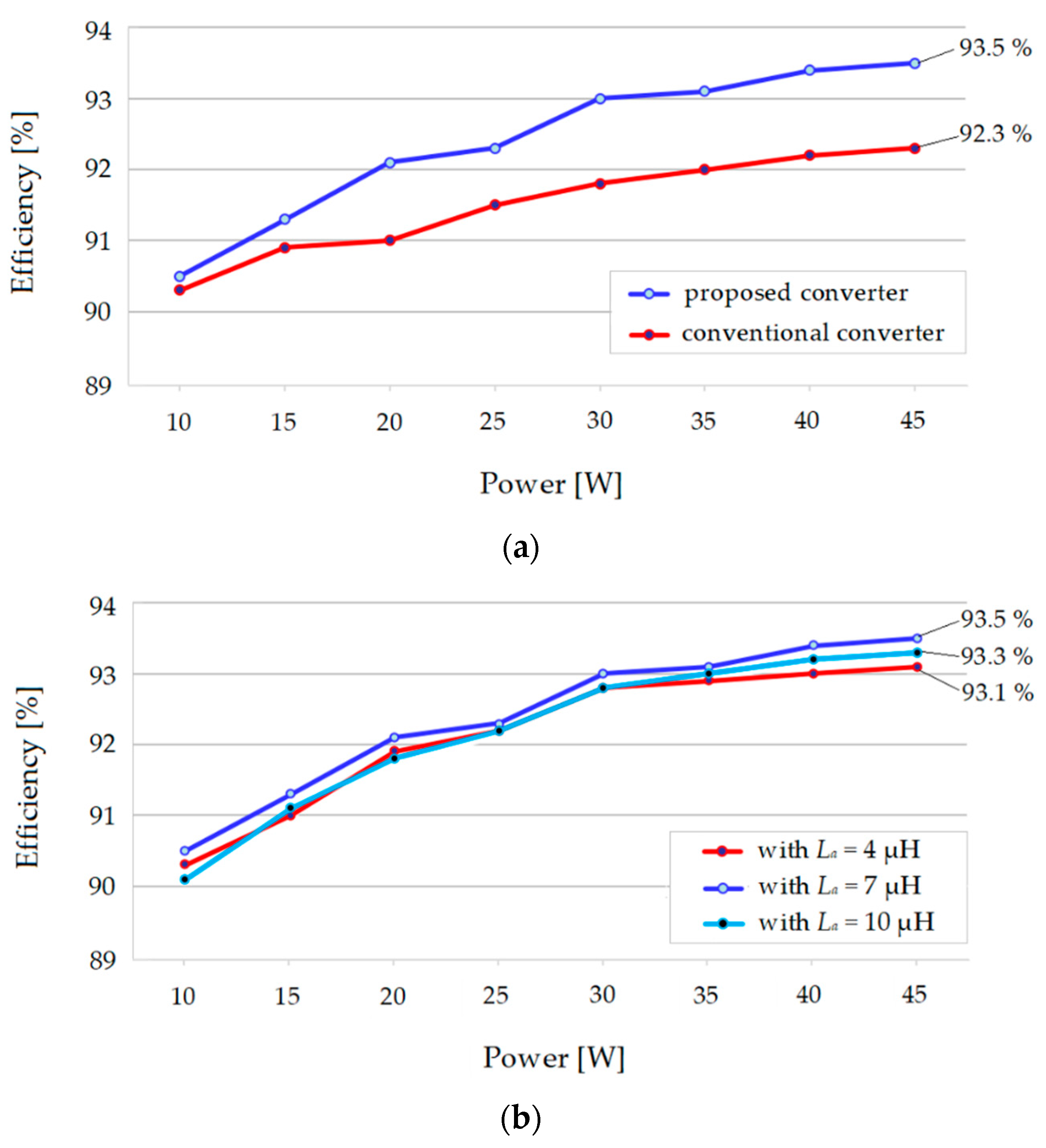

4.2. Experimental Verifications

5. Discussion

5.1. Application for Auxiliary Power Supplies

5.2. Application for Power Factor Corrections

6. Concluding Remark

Funding

Data Availability Statement

Conflicts of Interest

References

- Zhu, B.; Yang, Y.; Wang, K.; Liu, J.; Vilathgamuwa, D.M. High transformer utilization ratio and high voltage conversion gain flyback converter for photovoltaic application. IEEE Trans. Ind. Appl. 2024, 60, 2840–2851. [Google Scholar] [CrossRef]

- Omer, S.A.; Abdulsamed, L.; Meltem, L.; Arda, A.; Bati, E.E.; Mehmet, O.G. Meta-heuristics based design and optimization of active clamp flyback converter for USB PD. IEEE Access 2024, 12, 29269–29280. [Google Scholar]

- Mario, P.S.; Daniel, S.P.; Oscar, M.R.B.; Luis, G.V.V.; Abraham, C.S.; Susana, E.D.L.A.; Claudia, C.G.; Yesica, I.S.B.; Ricardo, E.L.P.; Juan, A.A.T. Flyback converter for solid-state lighting applications with partial energy processing. Electronics 2021, 10, 60. [Google Scholar]

- Novakovic, B.; Stern, D.; Stamenkovic, I.; Milivojevic, N. Flyback converter as auxiliary power supply for low-cost single-phase motor system. In Proceedings of the International Conference on “Computer as a Tool” (EUROCON 2005), Belgrade, Serbia, 21–24 November 2005; pp. 1493–1496. [Google Scholar]

- Halder, T. A comparative study of the hard & soft switching of the flyback converters. In Proceedings of the 2014 IEEE Power India International Conference (PIICON), Delhi, India, 5–7 December 2014; pp. 1–5. [Google Scholar]

- Yuri, P.; Milan, M.J. Adaptive off-time control for variable-frequency, soft-switched flyback converter at light loads. IEEE Trans. Power Electron. 2002, 17, 596–603. [Google Scholar]

- Hong, J.P.; Moon, G.W. A digitally controlled soft valley change technique for a flyback converter. IEEE Trans. Ind. Electron. 2015, 62, 966–971. [Google Scholar] [CrossRef]

- Yoo, J.S.; Baek, J.O.; Ahn, T.Y. A high-efficiency QR flyback dc-dc converter with reduced switch voltage stress realized by applying a self-driven active snubber (SDAS). Energies 2023, 16, 1068. [Google Scholar] [CrossRef]

- Park, J.P.; Moon, Y.J.; Jeong, M.G.; Kang, J.G.; Kim, S.H.; Gong, J.C.; Yoo, C.S. Quasi-resonant controller with adaptive switching frequency reduction scheme for flyback converter. IEEE Trans. Ind. Electron. 2016, 63, 3571–3581. [Google Scholar] [CrossRef]

- Wang, C.; Xu, S.; Shen, W.; Lu, S.; Sun, W. A single-switched high-switching-frequency quasi-resonant flyback converter. IEEE Trans. Power Electron. 2019, 34, 8775–8786. [Google Scholar] [CrossRef]

- Sayeb, M.T.; Sayed, R.B.S.; Mohammad, R.T.H. A brief review of snubber circuits for flyback converter. In Proceedings of the 2018 International Conference for Convergence in Technology (I2CT), Pune, India, 6–7 April 2018; pp. 1–5. [Google Scholar]

- Watson, R.; Lee, F.C.; Hua, G.C. Utilization of an active-clamp circuit to achieve soft switching in flyback converters. IEEE Trans. Power Electron. 1996, 11, 162–169. [Google Scholar] [CrossRef]

- Tang, C.Y.; Lin, W.Z.; Tan, Y.C. An active clamp flyback converter with high precision primary-side regulation strategy. IEEE Trans. Power Electron. 2022, 37, 10281–10289. [Google Scholar] [CrossRef]

- Jacinto, M.J.M.; Esther, J.; Jose, V. Parasitic capacitance effects on active clamp flyback output characteristics: Application to IPOP connection. Energies 2022, 15, 3201. [Google Scholar] [CrossRef]

- Hadi, T.; Ebrahim, B.; Amirreza, Z.G. A full soft-switching ZVZCS flyback converter using an active auxiliary cell. IEEE Trans. Ind. Electron. 2017, 64, 1123–1129. [Google Scholar]

- Chung, H.H.; Hui, S.R.; Wang, W.H. A zero-current-switching PWM flyback converter with a simple auxiliary switch. IEEE Trans. Power Electron. 1999, 14, 329–342. [Google Scholar] [CrossRef]

- Li, J.; van Horck, F.B.; Daniel, B.J.; Bergveld, H.J. A high-switching-frequency flyback converter in resonant mode. IEEE Trans. Power Electron. 2017, 32, 8582–8592. [Google Scholar] [CrossRef]

- Mehdi, M.; Ehsan, A.; Mohammad, R.Y. Family of soft-switching single-switch PWM converters with lossless passive snubber. IEEE Trans. Ind. Electron. 2015, 62, 3473–3481. [Google Scholar]

- Mehdi, M.; Martin, O. Flyback lossless passive snubber. In Proceedings of the 2015 IEEE Energy Conversion Congress and Exposition (ECCE), Montreal, QC, Canada, 20–24 September 2015; pp. 5896–5901. [Google Scholar]

- Adel, A.; Gerry, M. A comparative study of two passive regenerative snubbers for flyback converters. In Proceedings of the 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, Italy, 27–30 May 2018; pp. 1–7. [Google Scholar]

- Gianpaolo, V.; Guiseppe, L.; Daniel, S. Thermal stability of a DC/DC converter with inductor in partial saturation. IEEE Trans. Ind. Electron. 2021, 68, 7985–7995. [Google Scholar]

- Daniele, S.; Giuseppe, L.; Gianpaolo, V. Assessment of the current for a non-linear power inductor including temperature in DC-DC converters. Electronics 2023, 12, 579. [Google Scholar] [CrossRef]

- Gerry, M.; Praveen, J. Single-phase single-stage power-factor-corrected converter topologies. IEEE Trans. Ind. Electron. 2005, 52, 23–35. [Google Scholar]

- Laszlo, H.; Milan, M.J. Single-stage single-switch input-current-shaping technique with reduced switching loss. IEEE Trans. Power Electron. 2000, 15, 681–687. [Google Scholar]

- Giorgio, S.; Simone, B. An isolated soft-switched high-power-factor rectifier based on the asymmetrical half-bridge flyback converter. IEEE Trans. Ind. Electron. 2022, 69, 6722–6731. [Google Scholar]

- Seyed, M.H.; Seyed, M.S.; Yousef, A.B. A new method for active power factor correction using a dual-purpose inverter in a flyback converter. Turk. J. Electr. Eng. Comput. Sci. 2016, 24, 4736–4750. [Google Scholar]

- Tseng, K.C.; Huang, G.Y.; Hsiung, H.Y. Isolated high step-down DC-DC converter with current-doubler rectifier for ultracapacitor charger applications. Int. J. Circuit Theory Appl. 2023, 52, 582–597. [Google Scholar] [CrossRef]

- Ang, S.; Oliva, A. Power Switching Converters; CRC Press: Boca Raton, FL, USA, 2011. [Google Scholar]

- Mohan, N. Power Electronics: A First Course; John Wiley & Sons: Hoboken, NJ, USA, 2012. [Google Scholar]

- Halder, T. Comprehensive power loss model of the main switch of the flyback converter. In Proceedings of the 2013 International Conference on Power, Energy and Control (ICPEC), Dindigul, India, 6–8 February 2013; pp. 792–797. [Google Scholar]

- Lee, J.J.; Kwon, J.M.; Kim, E.H.; Choi, W.Y.; Kwon, B.H. Single-stage single-switch PFC flyback converter using a synchronous rectifier. IEEE Trans. Ind. Electron. 2008, 55, 1352–1365. [Google Scholar]

- Tianyu, C.; Carlos, C.N.; Pengyuan, C.; Amir, P.; Babak, F. Design of a 6.8-kW two-phase converter for 48 V automotive applications. In Proceedings of the 2020 IEEE Applied Power Electronics Conference and Exposition (APEC), New Orleans, LA, USA, 15–19 March 2020; pp. 2455–2461. [Google Scholar]

| Symbol | Quantity | Value |

|---|---|---|

| Vd | input voltage | 48 V |

| Vo | output voltage | 15 V |

| Po | rated output power | 45 W |

| fs | switching frequency | 50 kHz |

| Lm | magnetizing inductance | 300 μH |

| Llk | leakage inductance | 1 μH |

| Sp | power switch | IRF640NPbF |

| Do | output diode | MBR10100G |

| Da | additional diode | MBR10100G |

| La | additional inductor | 7 μH |

| Co | output capacitor | 2200 μF |

| Input Voltage/Output Voltage | Rated Output Power | Power Efficiency | |

|---|---|---|---|

| [18] | 50 V/100 V | 200 W | not announced |

| [19] | 140 V/24 V | 100 W | 90.5% |

| [20] | 72 V/12 V | 100 W | 77.5% |

| Component | Advantage | Complexity | |

|---|---|---|---|

| Lossless snubber [18] | inductor × 2, diode × 4, capacitor × 1, coupled inductor × 1 | zero-voltage turn-on (switch), zero-current-turn-off (diode) | high |

| Lossless snubber [19] | capacitor × 2, diode × 4, coupled inductor × 1 | zero-voltage turn-on (switch), zero-current-turn-off (diode) | high |

| Regenerative snubber [20] | capacitor × 1, diode × 3, coupled inductor × 1 | zero-voltage turn-on (switch), energy regeneration | high |

| Proposed method | inductor × 1, diode × 1, transformer winding × 1 | zero-current turn-off (diode), reduced turn-on loss (switch) | low |

| Operation | Advantage | Complexity | |

|---|---|---|---|

| Converter in [31] | APWM operation (switch × 2) | Zero-voltage switching (switch) | medium |

| Converter in [32] | BCM operation (switch × 5) | Zero-current switching (diode) | high |

| Proposed converter in Figure 18 | CCM Operation (switch × 1) | Zero-current switching (diode) | low |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Choi, W.-Y. A Flyback Converter with a Simple Passive Circuit for Improving Power Efficiency. Energies 2024, 17, 4729. https://doi.org/10.3390/en17184729

Choi W-Y. A Flyback Converter with a Simple Passive Circuit for Improving Power Efficiency. Energies. 2024; 17(18):4729. https://doi.org/10.3390/en17184729

Chicago/Turabian StyleChoi, Woo-Young. 2024. "A Flyback Converter with a Simple Passive Circuit for Improving Power Efficiency" Energies 17, no. 18: 4729. https://doi.org/10.3390/en17184729

APA StyleChoi, W.-Y. (2024). A Flyback Converter with a Simple Passive Circuit for Improving Power Efficiency. Energies, 17(18), 4729. https://doi.org/10.3390/en17184729