Development of a Series Braking Resistor to Eliminate Control Interference in Multi-Infeed HVDC Systems Considering the AC Three-Phase Fault—An Actual Case Study

Abstract

1. Introduction

- Ours is the first study to propose a facility-based approach to suppress the effects of control interference caused by a fault in a single HVDC unit within a multi-infeed HVDC system on the control of adjacent HVDC systems.

- The proposed method ensures that adjacent HVDC systems operate stably even when a fault occurs in a single HVDC unit within a multi-infeed HVDC system. The developed SeBR is used for rapid voltage recovery at the fault bus to prevent the propagation of the fault, particularly in weak AC grids.

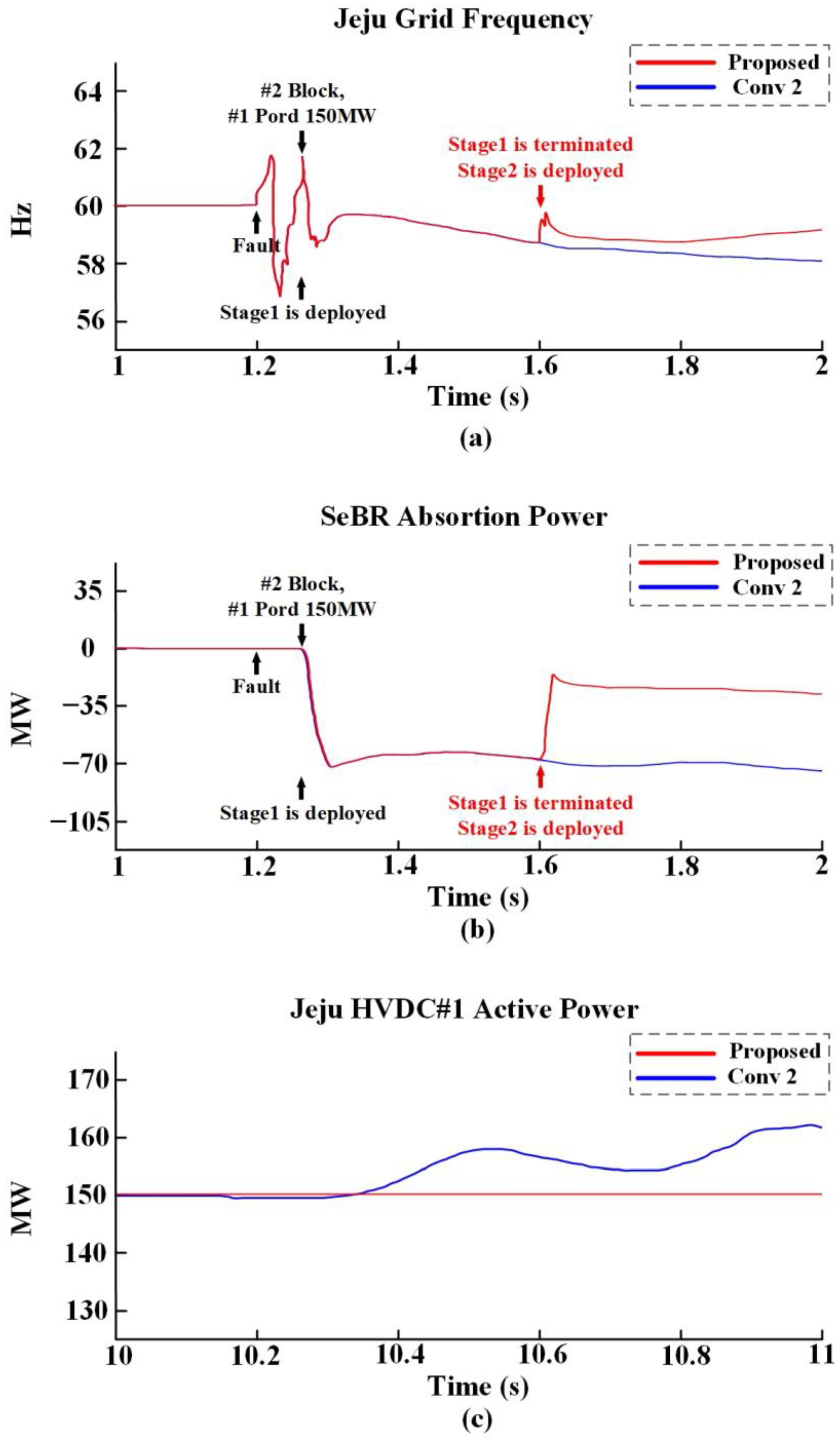

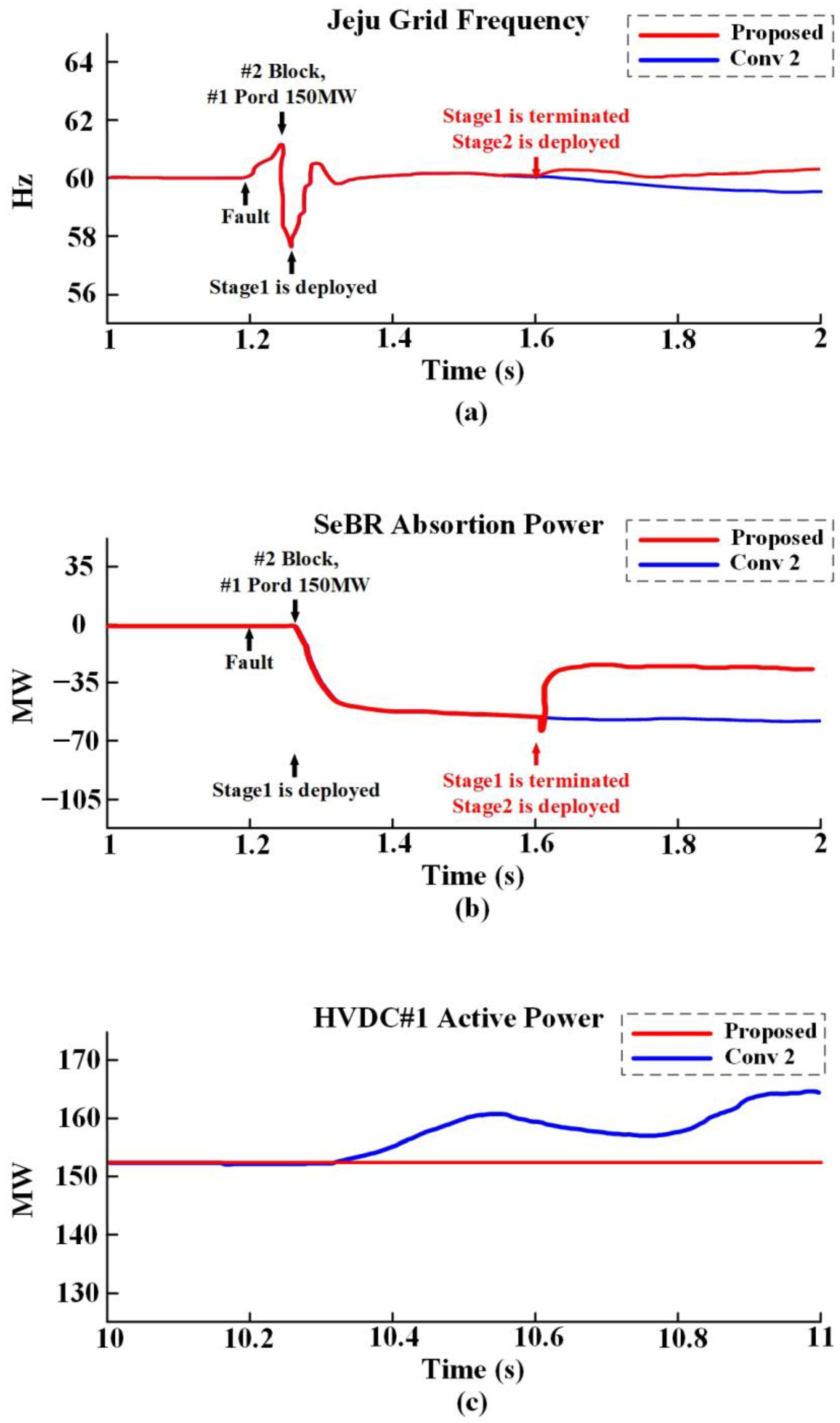

- We also considered scenarios where converter blocking is applied to address the fault occurring in a single HVDC unit yet the impact of the fault continues to affect the control of adjacent HVDC systems. To address this, we modeled the SeBR with long-term application considerations by dividing it into Stage 1 and Stage 2, which are activated based on frequency detection.

- The effectiveness of the proposed SeBR is validated via detailed modeling and verification of the HVDC systems of Jeju Island and the mainland in South Korea, where two adjacent HVDC units are currently operational.

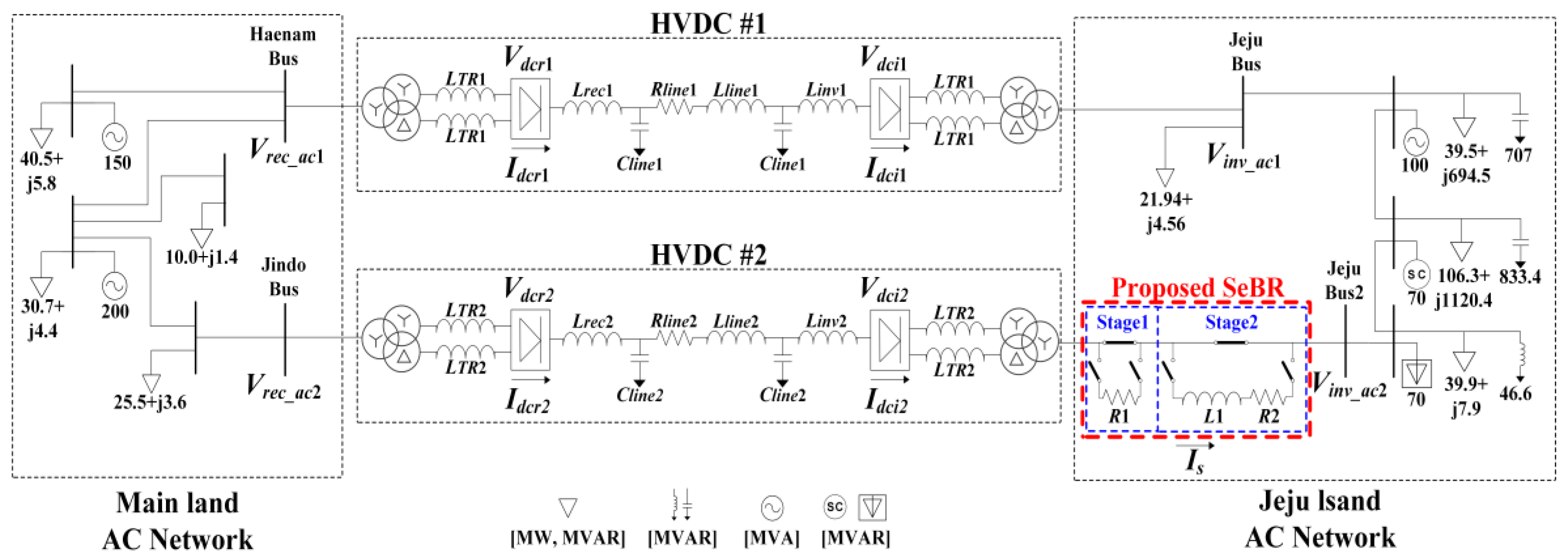

2. System Configuration

3. Modeling of the Jeju HVDC System

3.1. Normal Operation of the Jeju HVDC #1 and #2

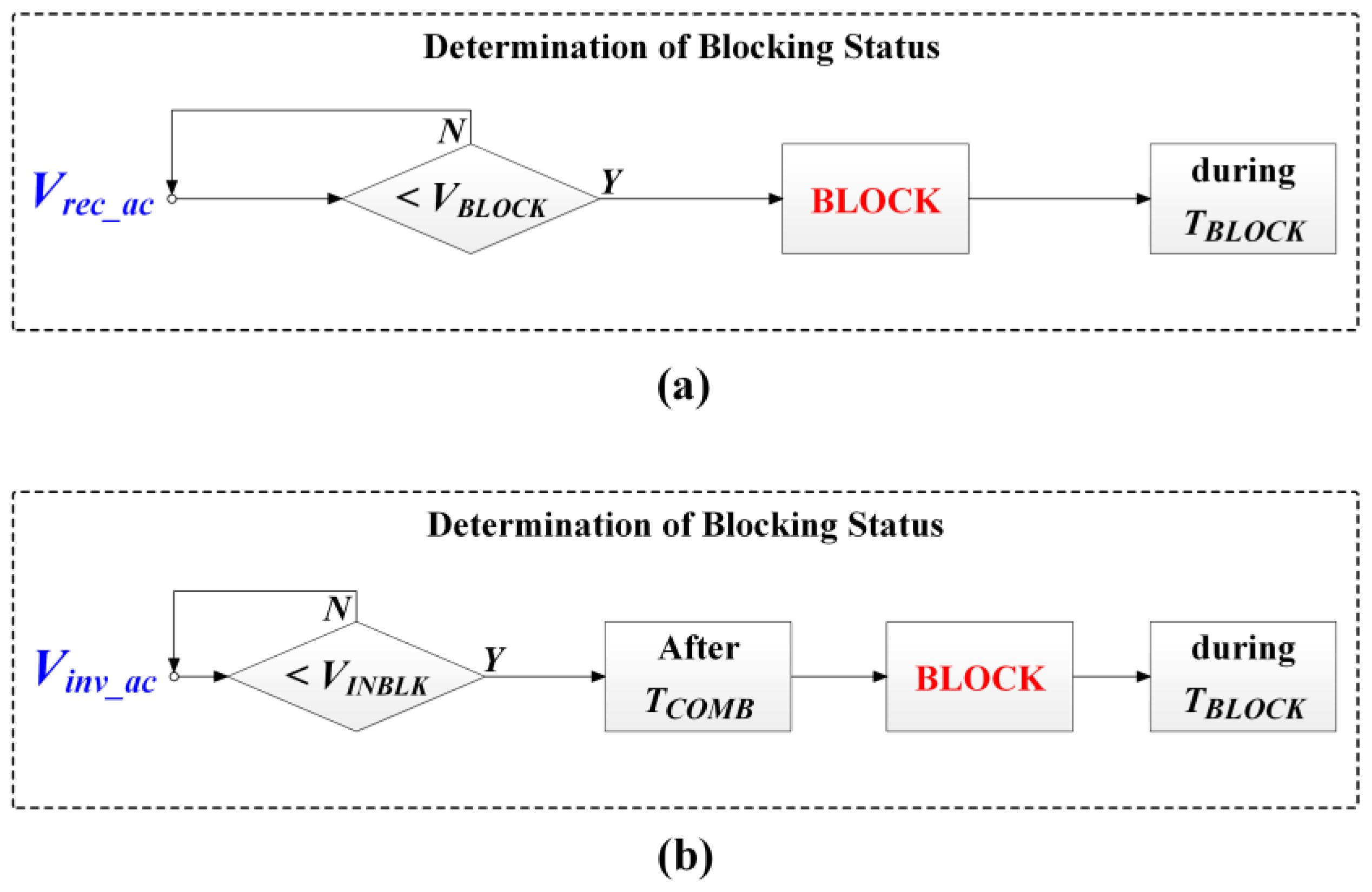

3.2. Converter Blocking Scheme of the Jeju HVDC #1 and #2

4. Proposed SeBR

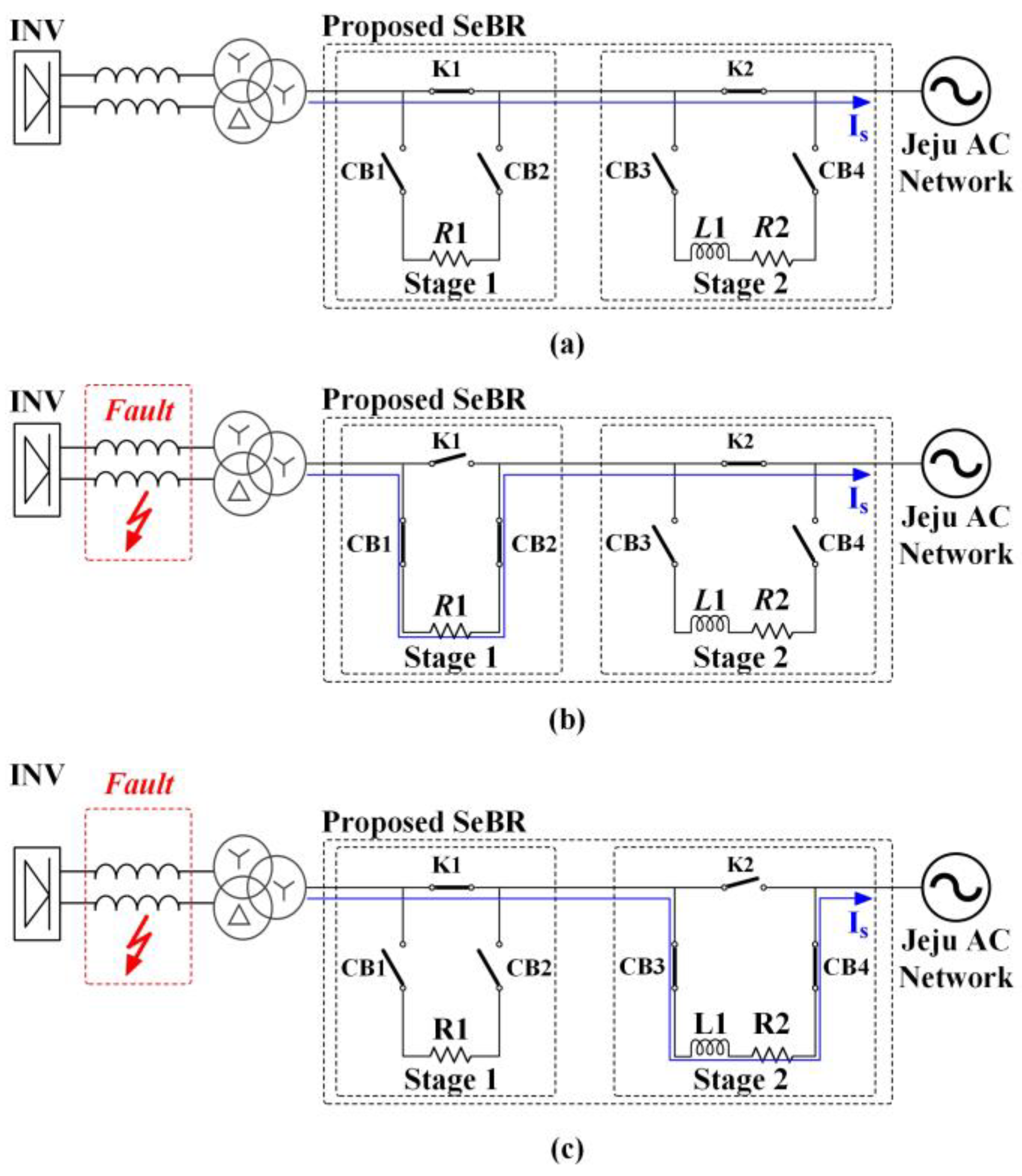

4.1. Configuration and Workflow of the Proposed SeBR

4.2. The Necessity of the Inductor Element in the Proposed SeBR

5. Case Studies and Simulation Results

5.1. Test System and Simulation Conditions

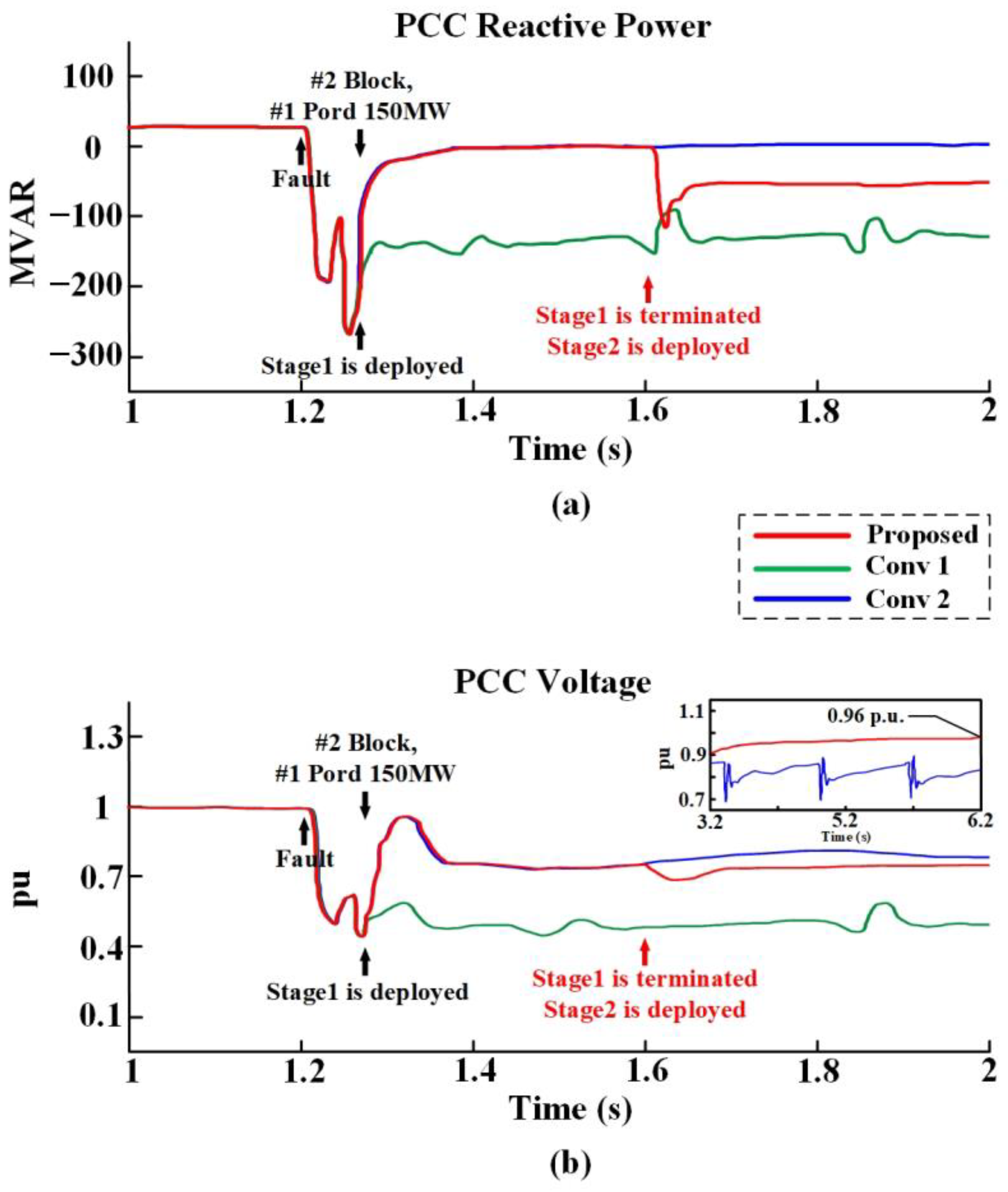

5.2. Verification of the SeBR

5.3. Verification of the Proposed SeBR

5.4. Verification of Proposed SeBR in the CIGRE HVDC Benchmark Model Environment

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- International Energy Agency (IEA). Renewables 2023; IEA: Paris, France, 2023; pp. 1–248. [Google Scholar]

- Xiaoyu, Z.; Chao, L.; Zhibing, W. Analysis and control on Sub-synchronous oscillation (SSO) of HVDC transmission for large-scale permanent magnet synchronous generators (PMSG)-based wind farm integration. J. Eng. 2019, 2019, 2440–2444. [Google Scholar] [CrossRef]

- Rudan, V.; Saad, H.; Yates, D.; Ahmedi, A.; Oluic, M.; Wijesinghe, S. On control interaction studies of HVDC-connected OWFs—Carbon trust OWA project. Electr. Power Syst. Res. 2023, 220, 109328. [Google Scholar] [CrossRef]

- Tavakoli, S.D.; Prieto-Araujo, E.; Gomis-Bellmunt, O. AC Fault Ride through in MMC-Based HVDC Systems. IEEE Trans. Power Deliv. 2022, 37, 2775–2786. [Google Scholar] [CrossRef]

- Wu, X.; Cao, B.; Shi, H.; Shi, P.; Wang, Y.; Liao, J.; Li, Y.; Zeng, W. Overvoltage Suppression Strategy of LCC-HVDC Delivery System Based on Hydropower Phase Control Participation. Electronics 2024, 13, 1223. [Google Scholar] [CrossRef]

- Sun, P.; Wickramasinghe, H.R.; Khalid, M.; Konstantinou, G. AC/DC fault handling and expanded DC power flow expression in hybrid multi-converter DC grids. Int. J. Electr. Power Energy Syst. 2022, 141, 107989. [Google Scholar] [CrossRef]

- Jiang, S.; Xin, Y.; Li, G.; Wang, L. A Novel DC Fault Ride-Through Method for Wind Farms Connected to the Grid through Bipolar MMC-HVDC Transmission. IEEE Trans. Power Deliv. 2020, 35, 2937–2950. [Google Scholar] [CrossRef]

- Zhou, H.; Yao, W.; Zhou, M.; Ai, X.; Wen, J.; Cheng, S. Active Energy Control for Enhancing AC Fault Ride-Through Capability of MMC-HVDC Connected with Offshore Wind Farms. IEEE Trans. Power Syst. 2023, 38, 2705–2718. [Google Scholar] [CrossRef]

- Zhou, H.; Yao, W.; Sun, K.; Ai, X.; Wen, J.; Cheng, S. Dynamic Reactive Current Optimization Based Onshore AC Fault Ride-through Strategy for MMC-HVDC Integrated Offshore Wind Farms. IEEE Trans. Sustain. Energy 2024, 15, 735–746. [Google Scholar] [CrossRef]

- Gao, G.; Wu, H.; Blaabjerg, F.; Wang, X. Fault current control of MMC in HVDC-connected offshore wind farm: A coordinated perspective with current differential protection. Int. J. Electr. Power Energy Syst. 2023, 148, 108952. [Google Scholar] [CrossRef]

- Salehi, F.; Golshani, A.; Matsuo, I.B.M.; Dehghanian, P. On Mitigation of Sub-Synchronous Control Interactions in Hybrid Generation Resources. IEEE Trans. Ind. Inform. 2021, 18, 4372–4382. [Google Scholar] [CrossRef]

- Gu, M.; Huang, L.; Lv, M.; Bian, R.; Li, G.; Ma, Z.; Hong, C.; Jiang, W.; Qi, X. Adaptive Robust Control Method of Battery Storage Systems for Power Oscillation Suppression of MMC-HVDC Offshore Wind Farms. In Proceedings of the 2023 13th International Conference on Power and Energy Systems (ICPES), Chengdu, China, 8–10 December 2023; pp. 307–312. [Google Scholar]

- Luo, C.; Guo, Q.; Hu, Y.; Li, S.; Zhu, Y.; Guo, H. Analysis and Countermeasures of Harmonic Instability in a Practical HVDC System with Fixed Series Compensation and STATCOM. IEEE Trans. Ind. Appl. 2023, 59, 2509–2518. [Google Scholar] [CrossRef]

- Li, G.; Chen, Y.; Luo, A.; Liu, X. Wideband Harmonic Voltage Feedforward Control Strategy of STATCOM for Mitigating Subsynchronous Resonance in Wind Farm Connected to Weak Grid and LCC HVDC. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 4546–4557. [Google Scholar] [CrossRef]

- Kim, K.; Kim, B.; Kim, I. A Study on the Global HVDC Trends and the Current Status of HVDC in Korea. Trans. Korean Inst. Electr. Eng. 2023, 72, 321–329. [Google Scholar] [CrossRef]

- Park, K.H.; Baek, S.T.; Chung, Y.H.; Jang, G.S. The Development of the ±80kV 60MW HVDC System in Korea. J. Electr. Eng. Technol. 2017, 12, 594–600. [Google Scholar] [CrossRef][Green Version]

- Kim, C.K.; Jang, G.; Jeong-Boo, K.; Shim, U.B. Transient performance of Cheju-Haenam HVDC system. In Proceedings of the 2001 Power Engineering Society Summer Meeting, Vancouver, BC, Canada, 15–19 July 2001; pp. 343–348. [Google Scholar]

- Kunder, K. Power System Stability and Control, 1st ed.; McGraw-Hill: New York, NY, USA, 1971; pp. 528–533. [Google Scholar]

- Kim, C.K.; Kwon, Y.H.; Jang, G. New HVDC Interaction between AC network and HVDC Shunt Reactor on Jeju Converter Station. In Proceedings of the 2007 IEEE Power Engineering Society General Meeting, Tampa, FL, USA, 24–28 June 2007; pp. 1–4. [Google Scholar]

- Rahimi, E.; Gole, A.; Davies, B.; Fernando, I.; Kent, K. Commutation failure analysis in multi-infeed HVDC systems. In Proceedings of the 2011 IEEE Power and Energy Society General Meeting, Detroit, MI, USA, 24–29 July 2011; pp. 378–384. [Google Scholar]

- Gururajapathy, S.S.; Mokhlis, H.; Illias, H.A. Fault Location and Detection Techniques in Power Distribution Systems with Distributed Generation: A Review. Renew. Sustain. Energy Rev. 2017, 74, 949–958. [Google Scholar] [CrossRef]

- Australian Energy Market Operator (AEMO). Black System South Australia: Final Report; AEMO: Melbourne, Australia, 2017. [Google Scholar]

- Mukhopadhyay, P.; Anumasula, R.; Gartia, A.; Kumar, C.; Seshadri, P.; Patil, S. Case Study on Fault Analysis Using PMU. In Proceedings of the 2014 National Power Systems Conference (NPSC), Guwahati, India, 18–20 December 2014; pp. 1–8. [Google Scholar]

- Lee, Y.; Hur, J. Practical Generation Resource Planning Based on Screening Curve Method Considering Must-Run Constraints: The Case of Jeju Island’s Power Grids. IEEE Access 2023, 11, 139260–139271. [Google Scholar] [CrossRef]

- Dai, R.; Hwang, M.D.; Qiu, W.; Wang, W.; Liu, X.; Xia, Y. EMS experience of reactive power control for LCC based HVDC system. In Proceedings of the 2015 IEEE Power & Energy Society General Meeting, Denver, CO, USA, 26–30 July 2015; pp. 1–5. [Google Scholar]

- Chae, S.H.; Kang, M.H.; Song, S.-H.; Kim, E.-H. Analysis of the Jeju Island Power System with an Offshore Wind Farm Applied to a Diode Rectifier HVDC. Energies 2019, 12, 4515. [Google Scholar] [CrossRef]

- Marken, P.E.; Skliutas, J.P.; Sung, P.Y.; Kim, K.S. New synchronous condensers for Jeju Island. In Proceedings of the 2012 IEEE Power and Energy Society General Meeting, San Diego, CA, USA, 22–26 July 2012; pp. 1–6. [Google Scholar]

- Liu, W.; Li, G.; Liang, J.; Ugalde-Loo, C.E.; Li, C.; Guillaud, X. Protection of Single-Phase Fault at the Transformer Valve Side of FB-MMC-Based Bipolar HVdc Systems. IEEE Trans. Ind. Electron. 2020, 67, 8416–8427. [Google Scholar] [CrossRef]

- Li, Y.; Wang, X.; Guo, J.; Wu, H.; Zhao, B.; Wang, S.; Wu, G.; Wang, T. PLL Synchronization Stability Analysis of MMC-Connected Wind Farms Under High-Impedance AC Faults. IEEE Trans. Power Syst. 2021, 36, 2251–2261. [Google Scholar] [CrossRef]

- Zhang, Q.; Mao, M.; Ke, G.; Zhou, L.; Xie, B. Stability problems of PV inverter in weak grid: A review. IET Power Electron. 2020, 13, 2165–2174. [Google Scholar] [CrossRef]

- Musengimana, A.; Li, H.; Zheng, X.; Yu, Y. Small-Signal Model and Stability Control for Grid-Connected PV Inverter to a Weak Grid. Energies 2021, 14, 3907. [Google Scholar] [CrossRef]

- Hamood, M.A.; Marjanovic, O.; Carrasco, J. Adaptive Impedance-Conditioned Phase-Locked Loop for the VSC Converter Connected to Weak Grid. Energies 2021, 14, 6040. [Google Scholar] [CrossRef]

- Li, T.; Li, Y.; Zhu, Y. Research on the Voltage Supporting Capability of Multi-VSC-HVDC Subsystems Operation Strategy to Receiving-end LCC-HVDC Network in Weak AC Grid. CES Trans. Electr. Mach. Syst. 2023, 7, 11–20. [Google Scholar] [CrossRef]

- Li, Z.; Xu, H.; Wang, Z.; Yan, Q. Stability Assessment and Enhanced Control of DFIG-Based WTs during Weak AC Grid. IEEE Access 2022, 10, 41371–41380. [Google Scholar] [CrossRef]

- Morris, J.F.; Ahmed, K.H.; Egea-Àlvarez, A. Standardized Assessment Framework for Design and Operation of Weak AC Grid-Connected VSC Controllers. IEEE Access 2021, 9, 95282–95293. [Google Scholar] [CrossRef]

- Ramadhan, U.F.; Suh, J.; Hwang, S.; Lee, J.; Yoon, M. A Comprehensive Study of HVDC Link with Reserve Operation Control in a Multi-Infeed Direct Current Power System. Sustainability 2022, 14, 6091. [Google Scholar] [CrossRef]

- Jung, A.; Park, J.; Lee, H.; Lee, B. Evaluation of inertia resource for securing nadir frequency in HVDC interconnected system with high penetration of RES. Energy Rep. 2023, 9, 1374–1383. [Google Scholar] [CrossRef]

- Kim, C.K.; Jang, G. Development of Jeju–Haenam HVDC system model for dynamic performance study. Int. J. Electr. Power Energy Syst. 2006, 28, 570–580. [Google Scholar] [CrossRef]

- Kwon, D.; Kim, Y.; Moon, S.; Kim, C. Modeling of HVDC System to Improve Estimation of Transient DC Current and Voltages for AC Line-to-Ground Fault—An Actual Case Study in Korea. Energies 2017, 10, 1543. [Google Scholar] [CrossRef]

- Kwon, D.; Kim, Y. Analyses and Comparisons of Generic and User Writing Models of HVDC System Considering Transient DC Current and Voltages. Energies 2021, 14, 7897. [Google Scholar] [CrossRef]

- Yan, S.; He, Z.; Yang, J.; Kong, M.; Hu, M. Optimized Protection Strategies for HVDC Grid with Fault-blocking Modular Multilevel Converters for Overhead Line Applications. J. Mod. Power Syst. Clean Energy 2020, 8, 1168–1177. [Google Scholar] [CrossRef]

- Liu, Y.; Zhu, X.; Deng, J.B.; Guo, J. Research on protection block strategy of grounding faults in HVDC converter station. J. Eng. 2019, 2019, 1016–1019. [Google Scholar] [CrossRef]

- Wang, P.; Zhang, X.P.; Coventry, P.F.; Li, Z. Control and protection strategy for MMC MTDC system under converter-side AC fault during converter blocking failure. J. Mod. Power Syst. Clean Energy 2014, 2, 272–281. [Google Scholar] [CrossRef]

- Robak, S.; Gryszpanowicz, K. Comprehensive dimensioning of series braking resistor for transient stability improvement. Electr. Power Syst. Res. 2018, 154, 59–66. [Google Scholar] [CrossRef]

- Ministry of Trade, Industry and Energy (MOTIE). Standards for Maintaining Power System Reliability and Power Quality; MOTIE Notice No. 2023-65; Ministry of Trade, Industry and Energy (MOTIE): Sejong, Republic of Korea, 25 April 2023.

| Parameters | Descriptions and Sample Values |

|---|---|

| Vrec_ac | Rectifier side AC bus voltage |

| Vinv_ac | Inverter side AC bus voltage |

| VBLOCK | Rectifier AC blocking voltage |

| VINBLK | Inverter AC voltage that causes the block after communication delay TCOMB |

| TBLOCK | Minimum blocking time |

| TCOMB | Communication delay in signaling the rectifier to block because of low inverter voltage |

| Devices | Description | Parameters | Value |

|---|---|---|---|

| Jeju HVDC #1 | Nominal DC voltage [kV] | Vdcr1, Vdci1 | 183.9, 182.7 |

| Nominal DC [A] | Idcr1, Idci1 | 282 | |

| HVDC DC link length [km] | - | 101 | |

| HVDC parameter of inductor [mH] | LTR1, Lline1 Lrec1, Linv1 | 22.5, 9.6, 60, 60 | |

| DC line capacitor [μF] | Cline1 | 27.7 | |

| DC line resistor [Ω] | Rline1 | 2.5 | |

| Jeju HVDC #2 | Nominal DC voltage [kV] | Vdcr2, Vdci2 | 254.4, 252.7 |

| Nominal DC [A] | Idcr2, Idci2 | 312.4 | |

| HVDC DC link length [km] | - | 113 | |

| HVDC parameter of inductor [mH] | LTR2, Lline2 Lrec2, Linv2 | 22.5, 16.18, 60, 60 | |

| DC line capacitor [μF] | Cline2 | 65.3 | |

| DC line resistor [Ω] | Rline2 | 2.44 | |

| SeBR | Rated voltage [kV] | - | 154 |

| Rated MVA [MVA] | - | 100 | |

| Stage 1 [p.u.] | R1 | 1 | |

| Stage 2 [p.u.] | R2, L1 | 0.3, 0.7 | |

| Jeju HVDC Systems’ Control Mode Selection | DC voltage [p.u.] | Vdcr_max, Vdci_max | 1.0, 1.2 |

| DC current [p.u.] | Idcr_max, Idcr_min, Idci_max | 1.3, 1.2, 1.2 | |

| Alpha and Gamma [°] | αmax, αmin, γmax | 165°, 5°, 18° | |

| PI gains | Kp1, Kp2, Kp3, Kp4, Kp5 | 0.01, 1.3, 1.42 0.01, 0.1 | |

| PI gains | Ki1, Ki2, Ki3, Ki4, Ki5 | 0.01, 2.5, 5.5 0.01, 0.01 | |

| Jeju HVDC Systems’ Converter Blocking Status | AC bus voltage [p.u.] | Vrec_ac, Vinv_ac | Measurement value |

| AC blocking voltage [p.u.] | VBLOCK | 0.6 | |

| AC blocking voltage [p.u.] | VINBLK | 0.65 | |

| Minimum blocking time [p.u.] | TBLOCK | 0.1 | |

| Communication delay [s] | TCOMB | 0.05 |

| Case | SeBR | Jeju HVDC #2 Block | Jeju HVDC #1 Pord 150 MW |

|---|---|---|---|

| Prop | Stage 1, Stage 2 | O | O |

| Conv 1 | X | O | O |

| Conv 2 | Stage 1 | O | O |

| Devices | Description | Parameters |

|---|---|---|

| CIGRE HVDC | AC base voltage | Rectifier: 345 [kV] Inverter: 230 kV |

| Nominal DC voltage | 500 [kV] | |

| Nominal DC current | 2 [kA] | |

| DC line impedance (Rec side) | R = 2.5 [Ω] L = 0.5968 [H] | |

| DC line impedance (Inv side) | R = 2.5 [Ω] L = 0.5968 [H] | |

| System frequency | 60 [Hz] | |

| Converter control | Rectifier: current Inverter: voltage |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, S.; Hong, J.; Kwon, D. Development of a Series Braking Resistor to Eliminate Control Interference in Multi-Infeed HVDC Systems Considering the AC Three-Phase Fault—An Actual Case Study. Energies 2024, 17, 4112. https://doi.org/10.3390/en17164112

Lee S, Hong J, Kwon D. Development of a Series Braking Resistor to Eliminate Control Interference in Multi-Infeed HVDC Systems Considering the AC Three-Phase Fault—An Actual Case Study. Energies. 2024; 17(16):4112. https://doi.org/10.3390/en17164112

Chicago/Turabian StyleLee, Sungwook, Junho Hong, and Dohoon Kwon. 2024. "Development of a Series Braking Resistor to Eliminate Control Interference in Multi-Infeed HVDC Systems Considering the AC Three-Phase Fault—An Actual Case Study" Energies 17, no. 16: 4112. https://doi.org/10.3390/en17164112

APA StyleLee, S., Hong, J., & Kwon, D. (2024). Development of a Series Braking Resistor to Eliminate Control Interference in Multi-Infeed HVDC Systems Considering the AC Three-Phase Fault—An Actual Case Study. Energies, 17(16), 4112. https://doi.org/10.3390/en17164112