A Reconfigurable Phase-Shifted Full-Bridge DC–DC Converter with Wide Range Output Voltage

Abstract

1. Introduction

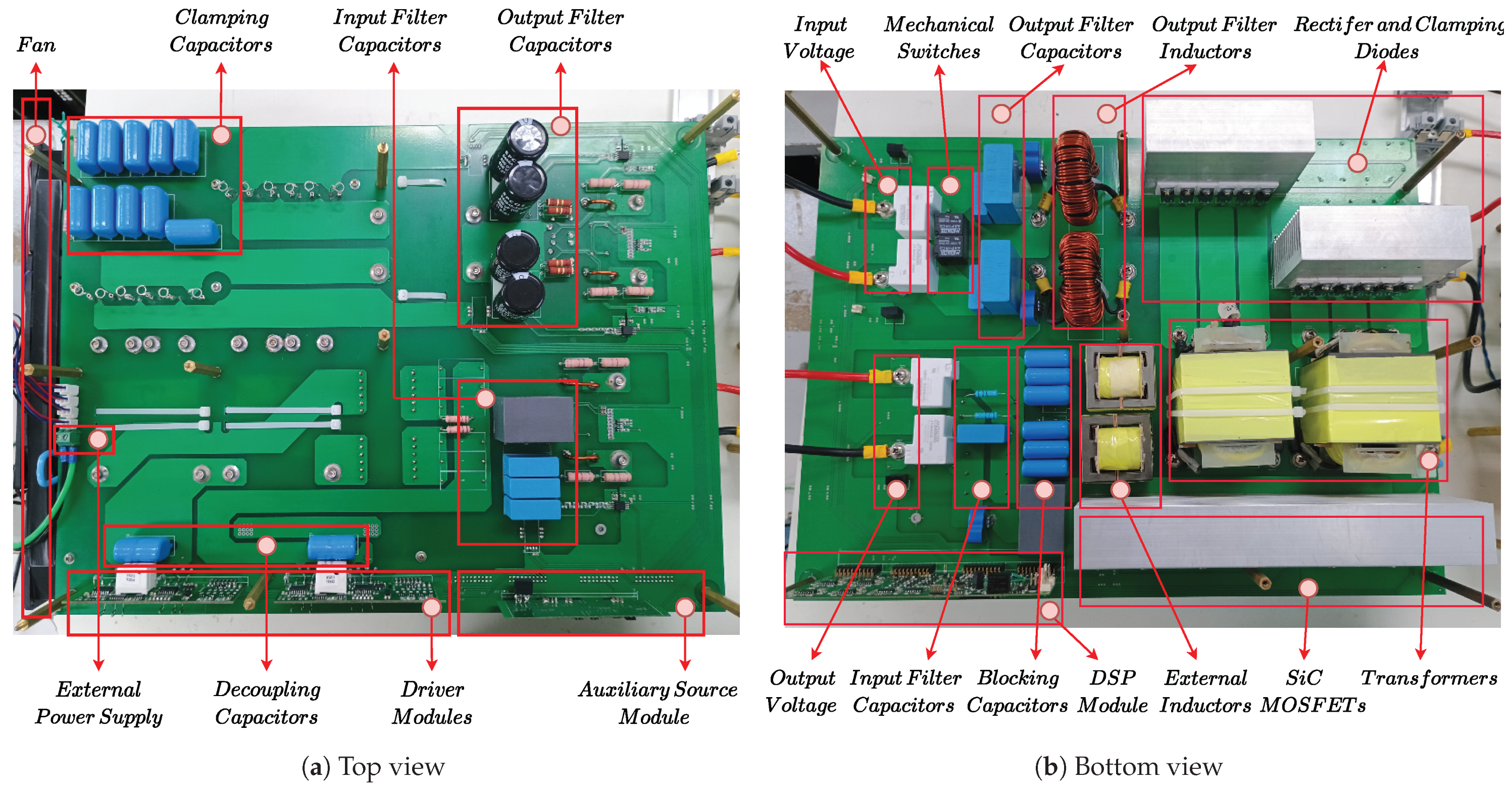

2. Materials and Methods

2.1. Circuit Description

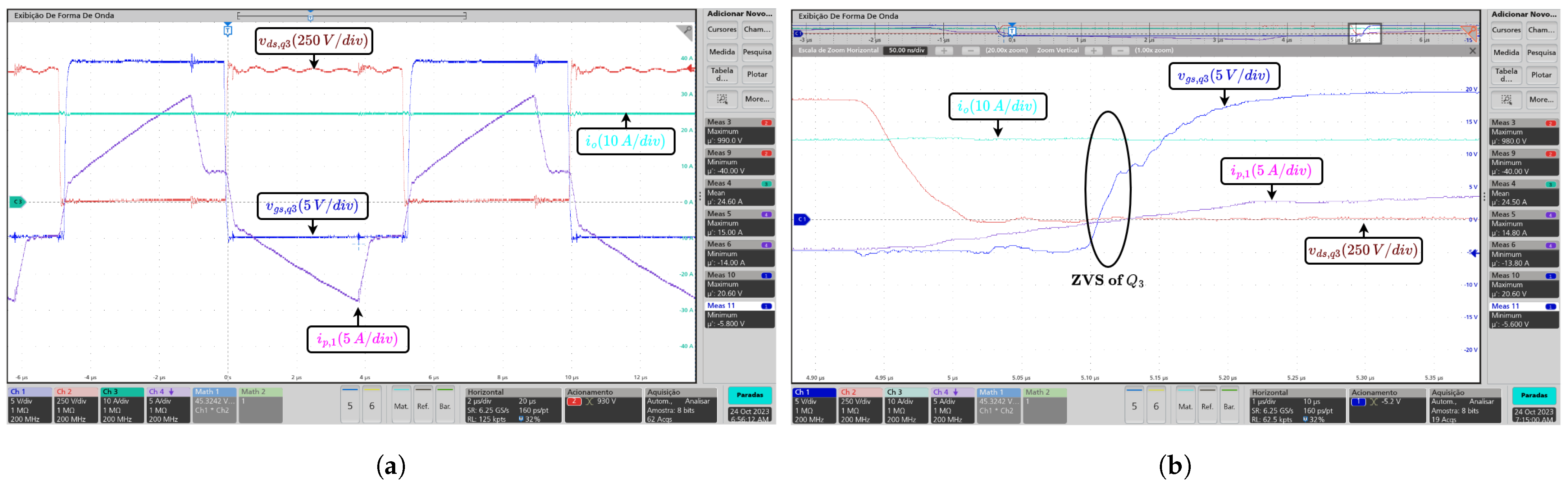

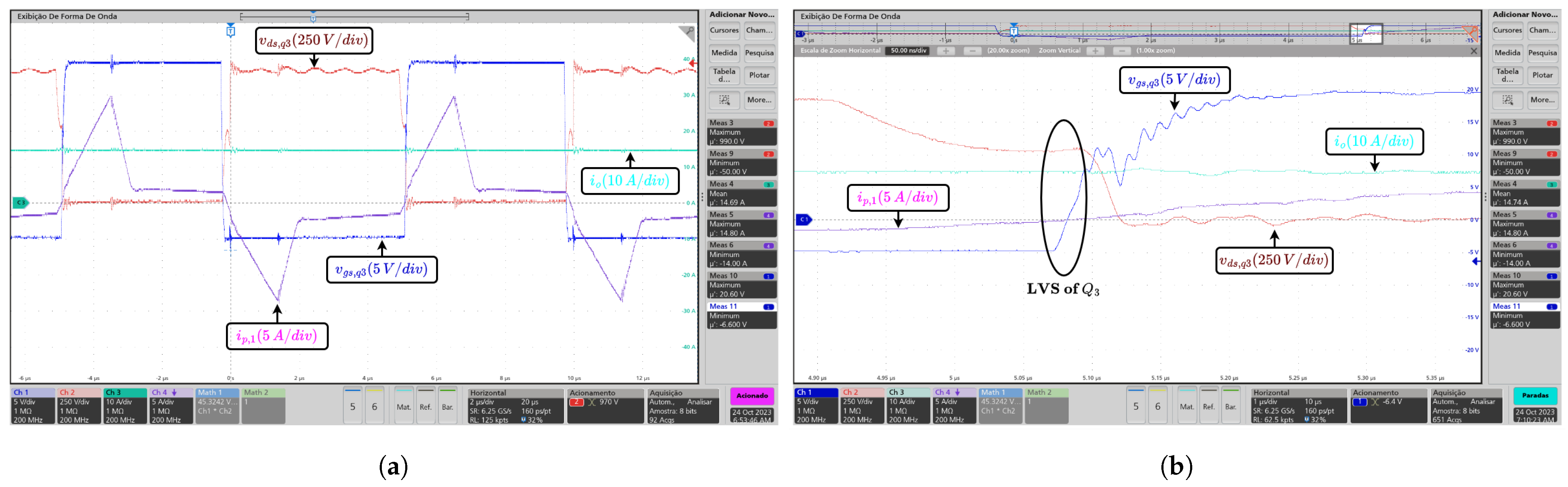

2.2. Operation Analysis

2.3. Steady-State Analysis

2.4. Electrical Stress

2.5. Parameter Design

2.5.1. Leakage Inductance

2.5.2. Magnetizing Inductance

2.5.3. Output Filter Inductance

2.5.4. Clamping Capacitance

2.5.5. Input Filter Capacitance

2.5.6. Output Filter Capacitance

2.5.7. Blocking Capacitance

2.5.8. Dead Time

2.6. Transient-State Analysis

3. Results

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Agarwal, A.; Prabowo, Y.; Bhattacharya, S. Analysis and Design Considerations of Input Parallel Output Series-Phase Shifted Full Bridge Converter for a High-Voltage Capacitor Charging Power Supply System. IEEE Trans. Ind. Appl. 2023, 59, 6037–6050. [Google Scholar] [CrossRef]

- Lee, D.; Youn, H.; Kim, J. Development of Phase-Shift Full-Bridge Converter with Integrated Winding Planar Two-Transformer for LDC. IEEE Trans. Transp. Electrif. 2023, 9, 1215–1226. [Google Scholar] [CrossRef]

- Mukherjee, S.; Saha, S.; Chowdhury, S. Battery Integrated Three-Port Soft-Switched DC–DC PSFB Converter for SPV Applications. IEEE Access 2023, 11, 62472–62483. [Google Scholar] [CrossRef]

- Métayer, P.; Loeuillet, Q.; Wallart, F.; Buttay, C.; Dujic, D.; Dworakowski, P. Phase-Shifted Full Bridge DC–DC Converter for Photovoltaic MVDC Power Collection Networks. IEEE Access 2023, 11, 19039–19048. [Google Scholar] [CrossRef]

- Pei, Z.; Guo, D.; Cui, T.; Liu, C.; Kong, D.; Zhu, D.; Jiang, Y.; Chen, N. Phase-Shift Full-Bridge (PSFB) Converter Integrated Double-Inductor Rectifier with Separated Resonant Circuits (SRCs) for 800 V High-Power Electric Vehicles. IEEE J. Emerg. Selec. Top. Power Electron. 2024, 12, 269–282. [Google Scholar] [CrossRef]

- Sabate, J.; Vlatkovic, V.; Ridley, R.; Lee, F.; Cho, B. Design considerations for high-voltage high-power full-bridge zero-voltage-switched PWM converter. In Proceedings of the Fifth Annual Proceedings on Applied Power Electronics Conference and Exposition, Los Angeles, CA, USA, 11–16 March 1990; pp. 275–284. [Google Scholar]

- Sabate, J.; Vlatkovic, V.; Ridley, R.; Lee, F. High-voltage, high-power, ZVS, full-bridge PWM converter employing an active snubber. In Proceedings of the Sixth Annual Applied Power Electronics Conference and Exhibition, Dallas, TX, USA, 10–15 March 1991; pp. 158–163. [Google Scholar]

- Yungtack, J.; Jovanovic, M.; Yu-Ming, C. A new ZVS-PWM full-bridge converter. IEEE Trans. Power Electron. 2003, 18, 1122–1129. [Google Scholar] [CrossRef]

- Guo, Z.; Sha, D.; Liao, X.; Luo, J. Input-Series-Output-Parallel Phase-Shift Full-Bridge Derived DC–DC Converters with Auxiliary LC Networks to Achieve Wide Zero-Voltage Switching Range. IEEE Trans. Power Electron. 2014, 29, 5081–5086. [Google Scholar] [CrossRef]

- Safaee, A.; Jain, P.; Bakhshai, A. A ZVS Pulsewidth Modulation Full-Bridge Converter with a Low-RMS-Current Resonant Auxiliary Circuit. IEEE Trans. Power Electron. 2016, 31, 4031–4047. [Google Scholar] [CrossRef]

- Zhao, L.; Li, H.; Wu, X.; Zhang, J. An Improved Phase-Shifted Full-Bridge Converter with Wide-Range ZVS and Reduced Filter Requirement. IEEE Trans. Ind. Electron. 2018, 65, 2167–2176. [Google Scholar] [CrossRef]

- Yang, X.; Li, Y.; Gao, Z.; Xi, L.; Wen, J. Analysis and Design of Full-Bridge Converter with a Simple Passive Auxiliary Circuit Achieving Adaptive Peak Current for ZVS and Low Circulating Current. IEEE J. Emerg. Selec. Top. Power Electron. 2021, 9, 2051–2065. [Google Scholar] [CrossRef]

- Shi, Y.; Feng, L.; Li, Q.; Kang, J. High Power ZVZCS Phase Shift Full Bridge DC–DC Converter with High Current Reset Ability and No Extra Electrical Stress. IEEE Trans. Ind. Electron. 2022, 69, 12688–12697. [Google Scholar] [CrossRef]

- Liu, G.; Wang, B.; Liu, F.; Wang, X.; Guan, Y.; Wang, W.; Wang, Y.; Xu, D. An Improved Zero-Voltage and Zero-Current- Switching Phase-Shift Full-Bridge PWM Converter with Low Output Current Ripple. IEEE Trans. Power Electron. 2023, 38, 3419–3432. [Google Scholar] [CrossRef]

- Mishima, T.; Akamatsu, K.; Nakaoka, M. A High Frequency-Link Secondary-Side Phase-Shifted Full-Range Soft-Switching PWM DC–DC Converter with ZCS Active Rectifier for EV Battery Chargers. IEEE Trans. Power Electron. 2013, 28, 5758–5773. [Google Scholar] [CrossRef]

- Dudrik, J.; Pástor, M.; Lacko, M.; Žatkovič, R. Zero-Voltage and Zero-Current Switching PWM DC–DC Converter Using Controlled Secondary Rectifier With One Active Switch and Nondissipative Turn-Off Snubber. IEEE Trans. Power Electron. 2018, 33, 6012–6023. [Google Scholar] [CrossRef]

- Li, G.; Xia, J.; Wang, K.; Deng, Y.; He, X.; Wang, Y. Hybrid Modulation of Parallel-Series LLC Resonant Converter and Phase Shift Full-Bridge Converter for a Dual-Output DC–DC Converter. IEEE J. Emerg. Selec. Top. Power Electron. 2019, 7, 833–842. [Google Scholar] [CrossRef]

- Li, G.; Yang, D.; Zhou, B.; Liu, Y.; Zhang, H. Integration of Three-Phase LLC Resonant Converter and Full-Bridge Converter for Hybrid Modulated Multioutput Topology. IEEE J. Emerg. Selec. Top. Power Electron. 2022, 10, 5844–5856. [Google Scholar] [CrossRef]

- Kim, J.; Lee, I.; Moon, G. Integrated Dual Full-Bridge Converter with Current-Doubler Rectifier for EV Charger. IEEE Trans. Power Electron. 2016, 31, 942–951. [Google Scholar] [CrossRef]

- Kanamarlapudi, V.; Wang, B.; Kandasamy, N.; So, P. A New ZVS Full-Bridge DC–DC Converter for Battery Charging with Reduced Losses Over Full-Load Range. IEEE Trans. Ind. Appl. 2018, 54, 571–579. [Google Scholar] [CrossRef]

- Tran, D.; Vu, H.; Yu, S.; Choi, W. A Novel Soft-Switching Full-Bridge Converter with a Combination of a Secondary Switch and a Nondissipative Snubber. IEEE Trans. Power Electron. 2018, 33, 1440–1452. [Google Scholar] [CrossRef]

- Lim, C.; Jeong, Y.; Lee, M.; Yi, K.; Moon, G. Half-Bridge Integrated Phase-Shifted Full-Bridge Converter with High Efficiency Using Center-Tapped Clamp Circuit for Battery Charging Systems in Electric Vehicles. IEEE Trans. Power Electron. 2020, 35, 4934–4945. [Google Scholar] [CrossRef]

- Jeong, H.; Lim, C. Hybrid DC–DC Converter with Novel Clamp Circuit in Wide Range of High Output Voltage. IEEE Access 2024, 12, 7775–7785. [Google Scholar] [CrossRef]

- Lim, C.; Jeong, Y.; Moon, G. Phase-Shifted Full-Bridge DC–DC Converter with High Efficiency and High Power Density Using Center-Tapped Clamp Circuit for Battery Charging in Electric Vehicles. IEEE Trans. Power Electron. 2019, 34, 10945–10959. [Google Scholar] [CrossRef]

- Bakar, M.; Alam, M.; Majid, A.; Bertilsson, K. Dual-Mode Stable Performance Phase-Shifted Full-Bridge Converter for Wide-Input and Medium-Power Applications. IEEE Trans. Power Electron. 2021, 36, 6375–6388. [Google Scholar] [CrossRef]

- Bakar, M.; Alam, M.; Wårdemark, M.; Bertilsson, K. A 2 × 3 Reconfigurable Modes Wide Input Wide Output Range DC-DC Power Converter. IEEE Access 2021, 9, 44292–44303. [Google Scholar] [CrossRef]

- Lyu, D.; Soeiro, T.; Bauer, P. Design and Implementation of a Reconfigurable Phase Shift Full-Bridge Converter for Wide Voltage Range EV Charging Application. IEEE Trans. Transp. Electrific. 2023, 9, 1200–1214. [Google Scholar] [CrossRef]

- Benites, J.; Mezaroba, M.; Batschauer, A.; Ribeiro, J. A DC/DC Converter for 400 V and 800 V EVs Fast Charging Stations. In Proceedings of the IEEE 8th Southern Power Electronics Conference and 17th Brazilian Power Electronics Conference, Florianopolis, Brazil, 26 November 2023. [Google Scholar]

- Tang, L.; Jiang, H.; Zhong, X.; Qiu, G.; Mao, H.; Jiang, X.; Qi, X.; Du, C.; Peng, Q.; Liu, L.; et al. Investigation Into the Third Quadrant Characteristics of Silicon Carbide MOSFET. IEEE Trans. Power Electron. 2023, 38, 1155–1165. [Google Scholar] [CrossRef]

| - | |||||||||||

| series | 1, 0 | ||||||||||

| parallel | 0, 1 | n | |||||||||

| Variable | Value | |

|---|---|---|

| Q | ||

| 0 | ||

| D | ||

| T | ||

| Parameter | Symbol | Value |

|---|---|---|

| Input voltage | 900 V | |

| Rated output voltage | 400 V/800 V | |

| Rated output current | 25 A/12.5 A | |

| Rated output power | 10 kW | |

| Switching frequency | 100 kHz | |

| Maximum output current ripple | 4.5 A | |

| Maximum input voltage ripple | 9 V | |

| Maximum output voltage ripple | 5 V | |

| Maximum blocking voltage ripple | 9 V | |

| Transformer turns ratio | n | 0.6 |

| Leakage Inductance | 27.4 H | |

| Magnetizing Inductance | 640 H |

| Component | Symbol | Description |

|---|---|---|

| MOSFET | – | NTHL080N120SC1 (1200 V, 22 A, 110 m, = 80 pF) |

| Rectifier Diode | – | VS-ETX3007-M3 (650 V, 30 A, = 1.6 V, = 35 ns) |

| Clamping Diode | VS-15ETH03-M3 (300 V, 15 A, = 0.85 V, = 32 ns) | |

| VS-30ETH06-M3 (600 V, 30 A, = 1.34 V, = 23 ns) | ||

| Core: 2 × MMT140EE6527 | ||

| Transformer | T | = 641 H/665.3 H, = 8.4 H/8.83 H |

| External Inductor | Core: 1 × MMT140EE4220 | |

| L = 18.37 H/18.6 H | ||

| Output Filter Inductor | Core: 1 × MMTS60T5715 | |

| L = 237.8 H/342.51 H | ||

| Input Filter Capacitor | MP F863H KEMET (10 F, 1200 V) + | |

| MP B32774 TDK (4 × 1.5 F, 1200 V)+ | ||

| B43840-A9477 Epcos (2/3 × 470 F, 400 V) | ||

| Blocking Capacitor | MP B32614 TDK (3 × 1 F, 630 V) | |

| Clamping Capacitor | MP B32614 TDK (5 × 2.2 F, 630 V) | |

| Output Filter Capacitor | MP B32776 TDK (12 F, 1000 V)+ | |

| MP B32774 TDK (1.5 F, 1200 V)+ | ||

| B43845-A5227 Epcos (1/2 × 220 F, 450 V) |

| 1.5 A | 1.552 A | 1.484 A | 4.48% | 44.066 V | 40.984 V | 85.050 V | 7.25% |

| 3 A | 2.999 A | 2.961 A | 1.27% | 85.817 V | 81.617 V | 167.434 V | 5.01% |

| 4.5 A | 4.542 A | 4.466 A | 1.68% | 128.305 V | 123.881 V | 252.186 V | 3.51% |

| 6 A | 6.037 A | 5.932 A | 1.75% | 171.706 V | 166.629 V | 338.335 V | 3.01% |

| 7.5 A | 7.532 A | 7.481 A | 0.67% | 213.501 V | 210.126 V | 423.627 V | 1.59% |

| 9 A | 9.077 A | 8.979 A | 1.08% | 256.547 V | 254.688 V | 511.235 V | 0.72% |

| 10.5 A | 10.583 A | 10.476 A | 1.01% | 298.008 V | 297.991 V | 595.999 V | 0.01% |

| 12.5 A | 12.576A | 12.498 A | 0.62% | 357.791 V | 356.973 V | 714.764 V | 0.23% |

| 3 A | 1.567 A | 1.449 A | 3.016 A | 7.82% | 45.241 V | 44.744 V | 1.11% |

| 6 A | 3.073 A | 2.917 A | 5.99 A | 5.21% | 88.545 V | 88.026 V | 0.58% |

| 9 A | 4.671 A | 4.335 A | 9.01 A | 7.46% | 133.171 V | 133.411 V | 0.18% |

| 12 A | 6.212 A | 5.765 A | 11.977 A | 7.46% | 177.872 V | 178.241 V | 0.21% |

| 15 A | 7.721 A | 7.224 A | 14.945 A | 6.65% | 222.922 V | 223.813 V | 0.39% |

| 18 A | 9.304 A | 8.703 A | 18.007 A | 6.67% | 268.946 V | 269.741 V | 0.29% |

| 21 A | 10.836 A | 10.138 A | 20.974 A | 6.65% | 312.028 V | 314.963 V | 0.93% |

| 25 A | 13.077 A | 11.926 A | 25.003 A | 9.21% | 374.269 V | 375.429 V | 0.31% |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Benites Quispe, J.B.; Mezaroba, M.; Batschauer, A.L.; de Souza Ribeiro, J.M. A Reconfigurable Phase-Shifted Full-Bridge DC–DC Converter with Wide Range Output Voltage. Energies 2024, 17, 3483. https://doi.org/10.3390/en17143483

Benites Quispe JB, Mezaroba M, Batschauer AL, de Souza Ribeiro JM. A Reconfigurable Phase-Shifted Full-Bridge DC–DC Converter with Wide Range Output Voltage. Energies. 2024; 17(14):3483. https://doi.org/10.3390/en17143483

Chicago/Turabian StyleBenites Quispe, Jhon Brajhan, Marcello Mezaroba, Alessandro Luiz Batschauer, and Jean Marcos de Souza Ribeiro. 2024. "A Reconfigurable Phase-Shifted Full-Bridge DC–DC Converter with Wide Range Output Voltage" Energies 17, no. 14: 3483. https://doi.org/10.3390/en17143483

APA StyleBenites Quispe, J. B., Mezaroba, M., Batschauer, A. L., & de Souza Ribeiro, J. M. (2024). A Reconfigurable Phase-Shifted Full-Bridge DC–DC Converter with Wide Range Output Voltage. Energies, 17(14), 3483. https://doi.org/10.3390/en17143483