Signal Order Optimization of Interconnects Enabling High Electromagnetic Compatibility Performance in Modern Electrical Systems

Abstract

1. Introduction

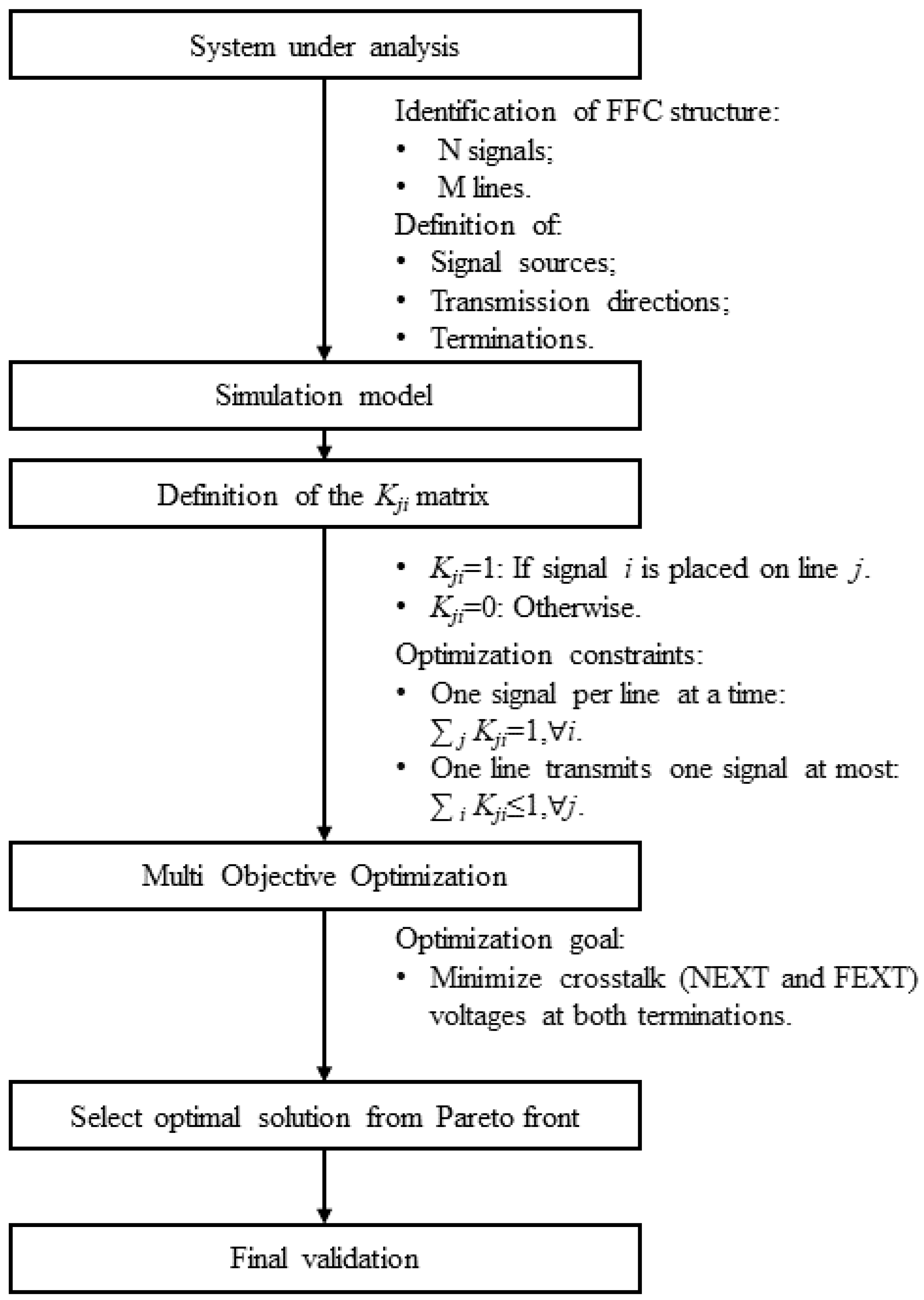

2. Problem Formulation

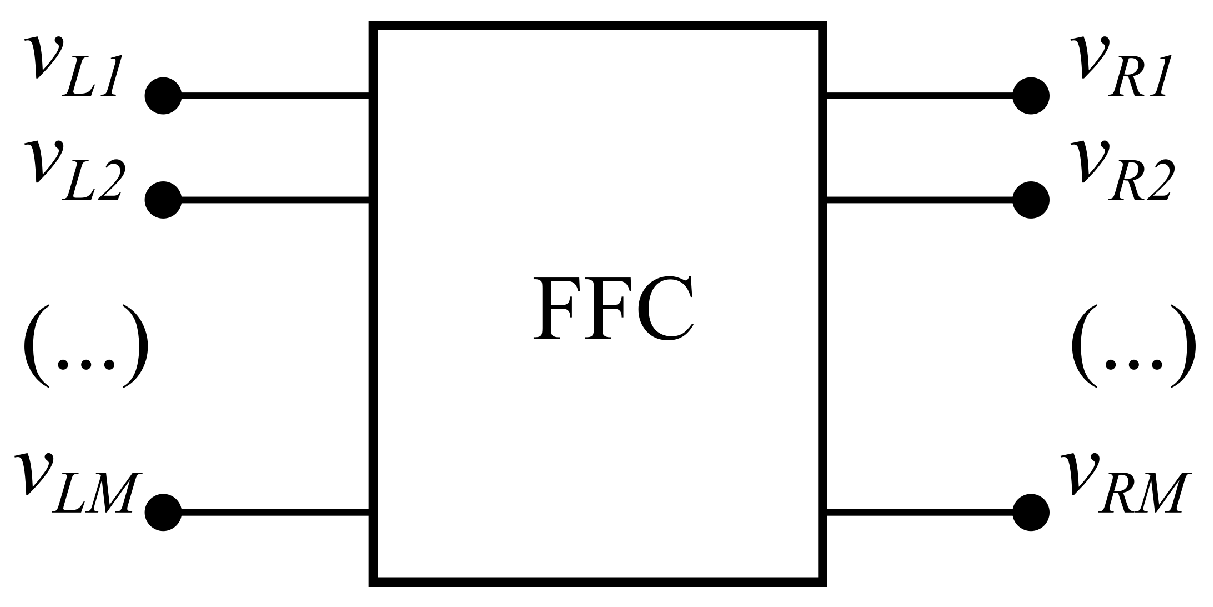

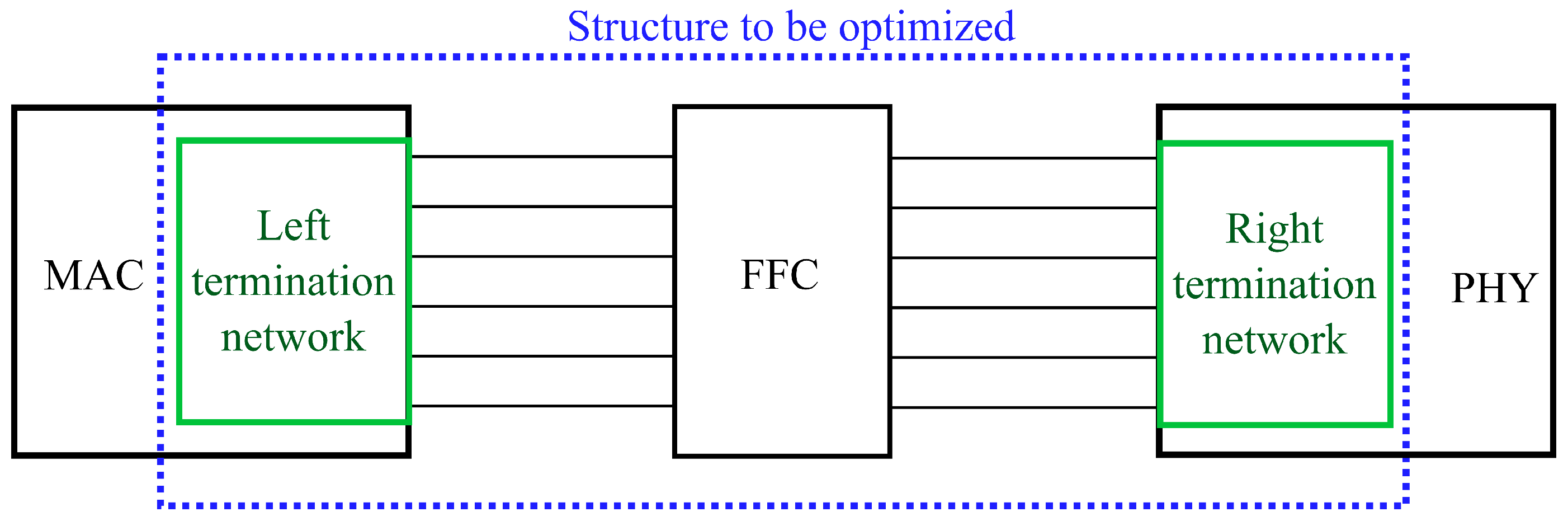

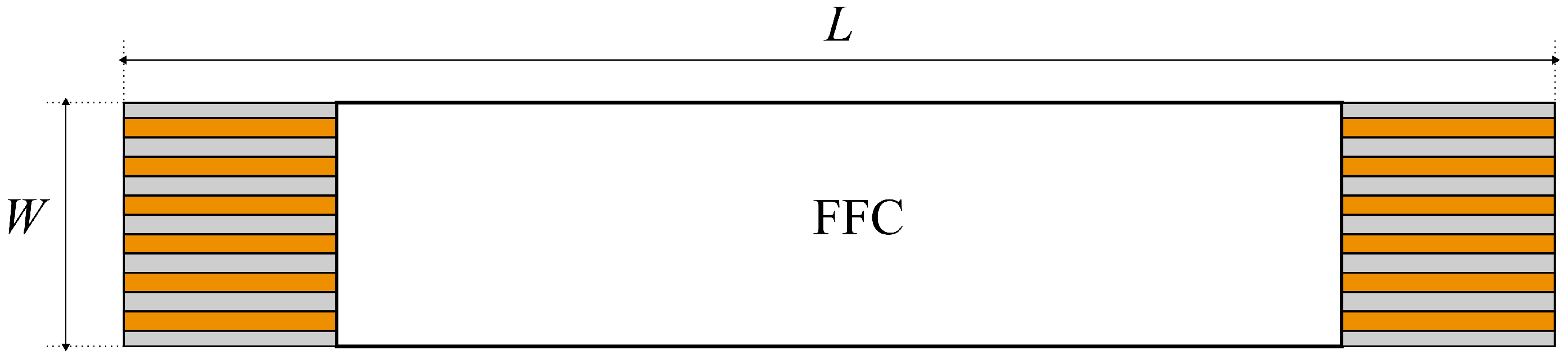

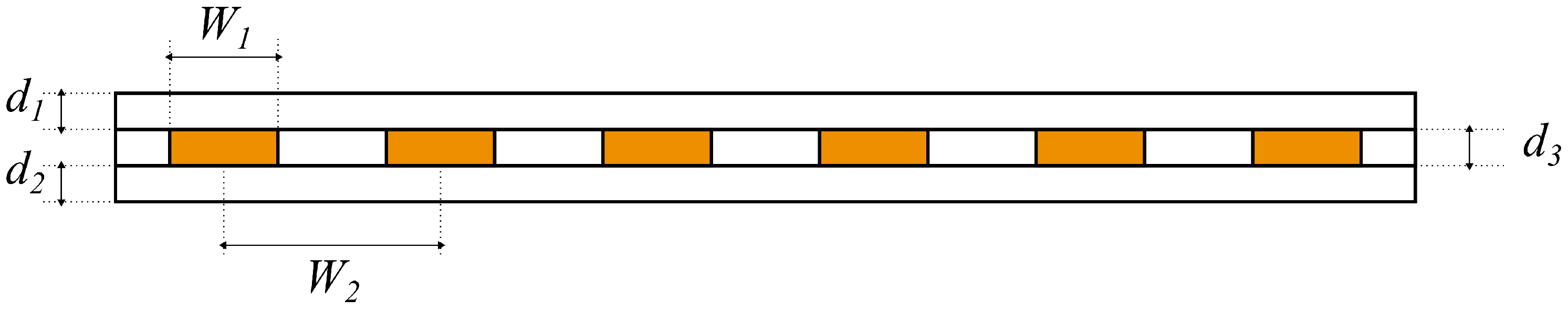

2.1. Structure under Analysis

2.2. Signal Transmission Assumptions

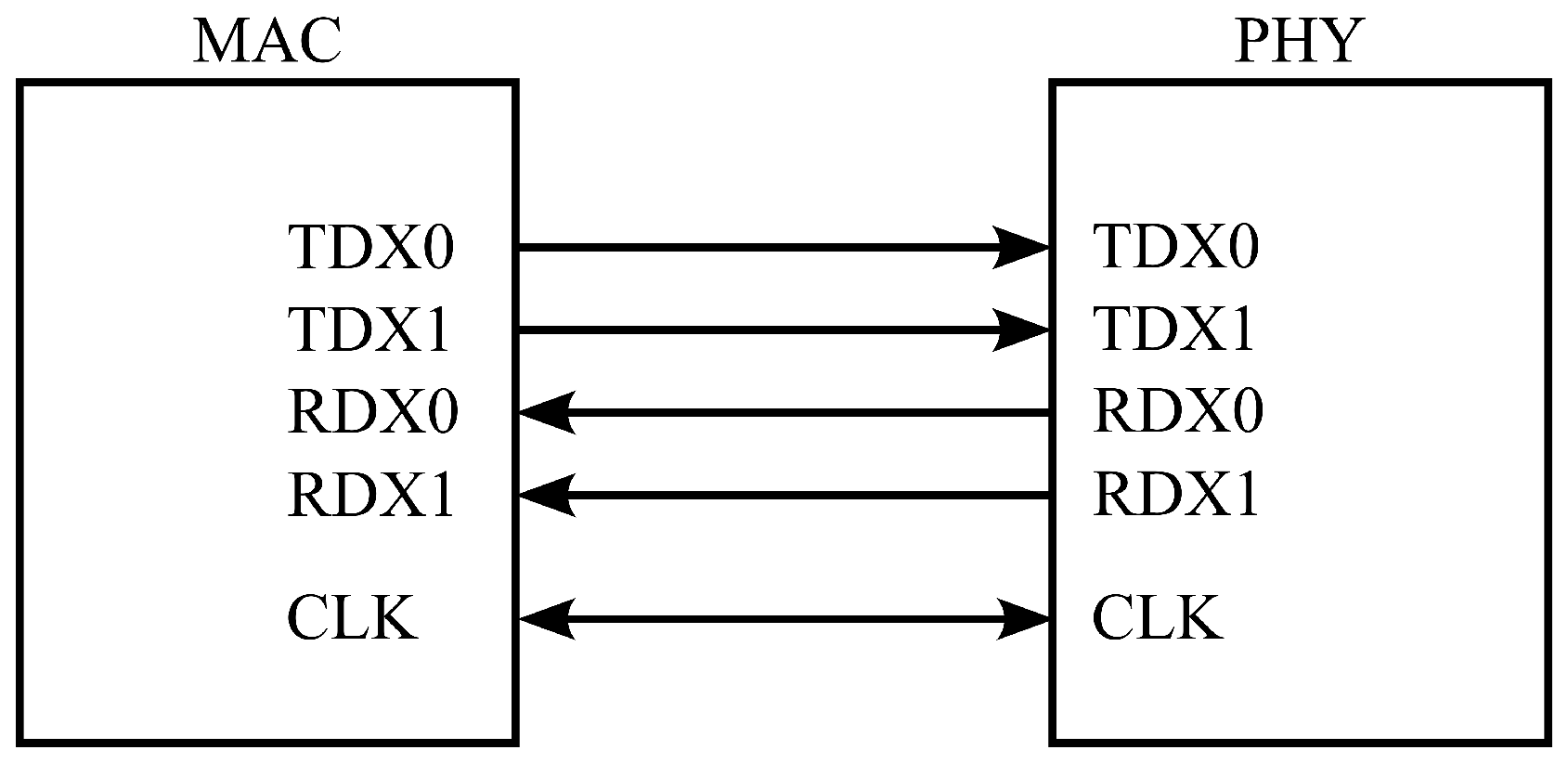

- Signals denote the continuous dataflow to be conveyed from one side to another side of the system, usually on different PCBs (see Figure 1), implying a fixed transmission direction and including power signals.

- Lines are the media inside the FFC used for signal transmission, which are made of good conductors.

3. Proposed Method

3.1. Linear Optimization Problems (LOPs)

3.2. Optimization Problem

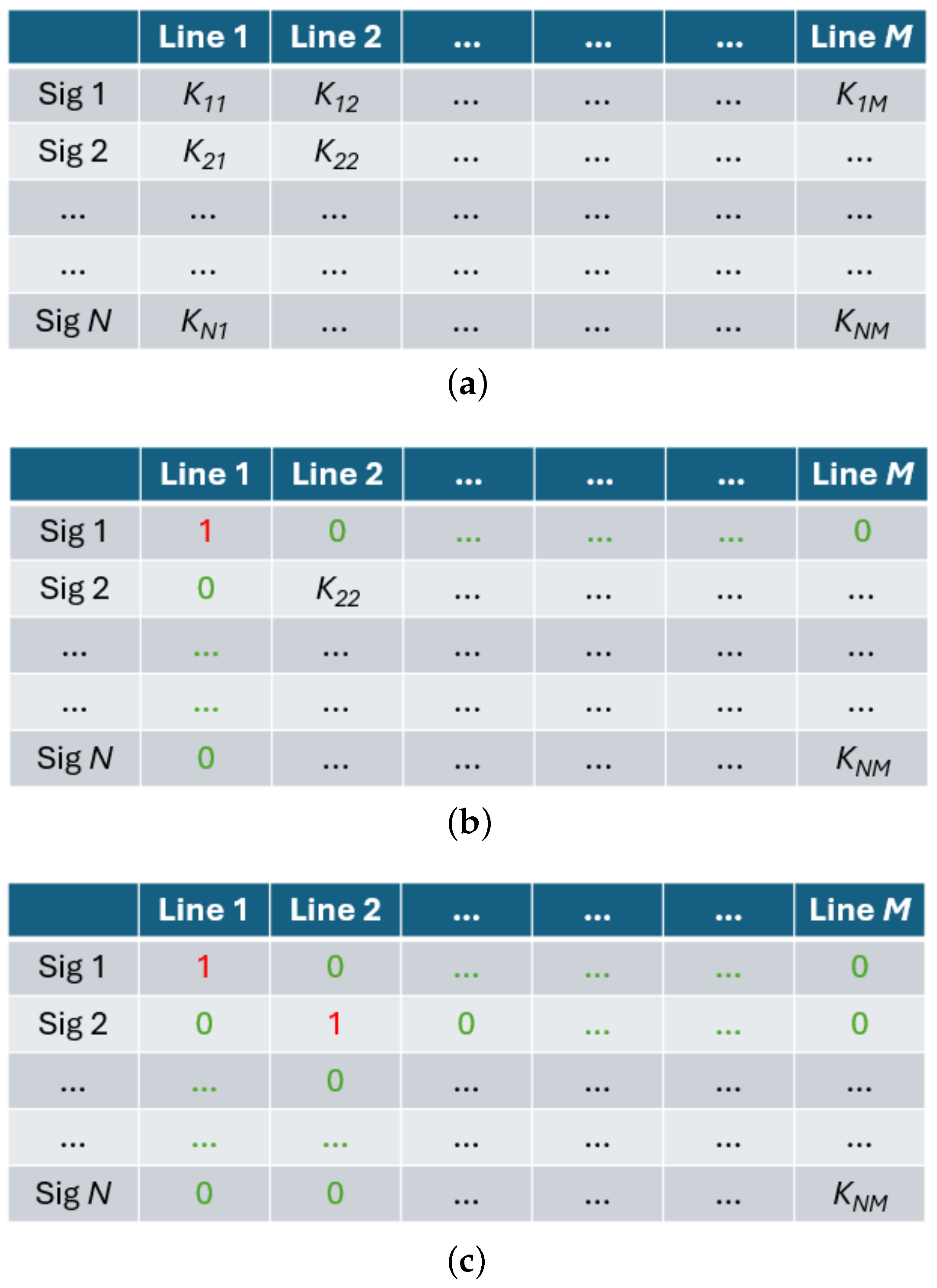

3.2.1. Optimization Variables

- : if signal i is placed on line j;

- : otherwise.

- (a)

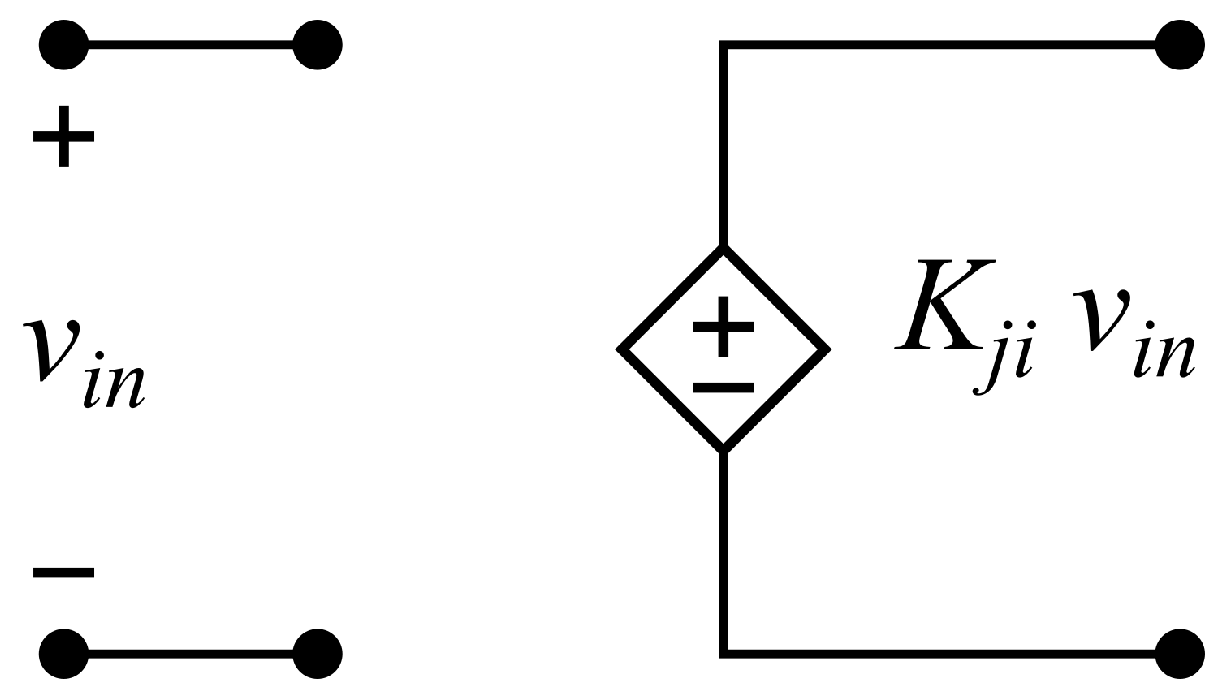

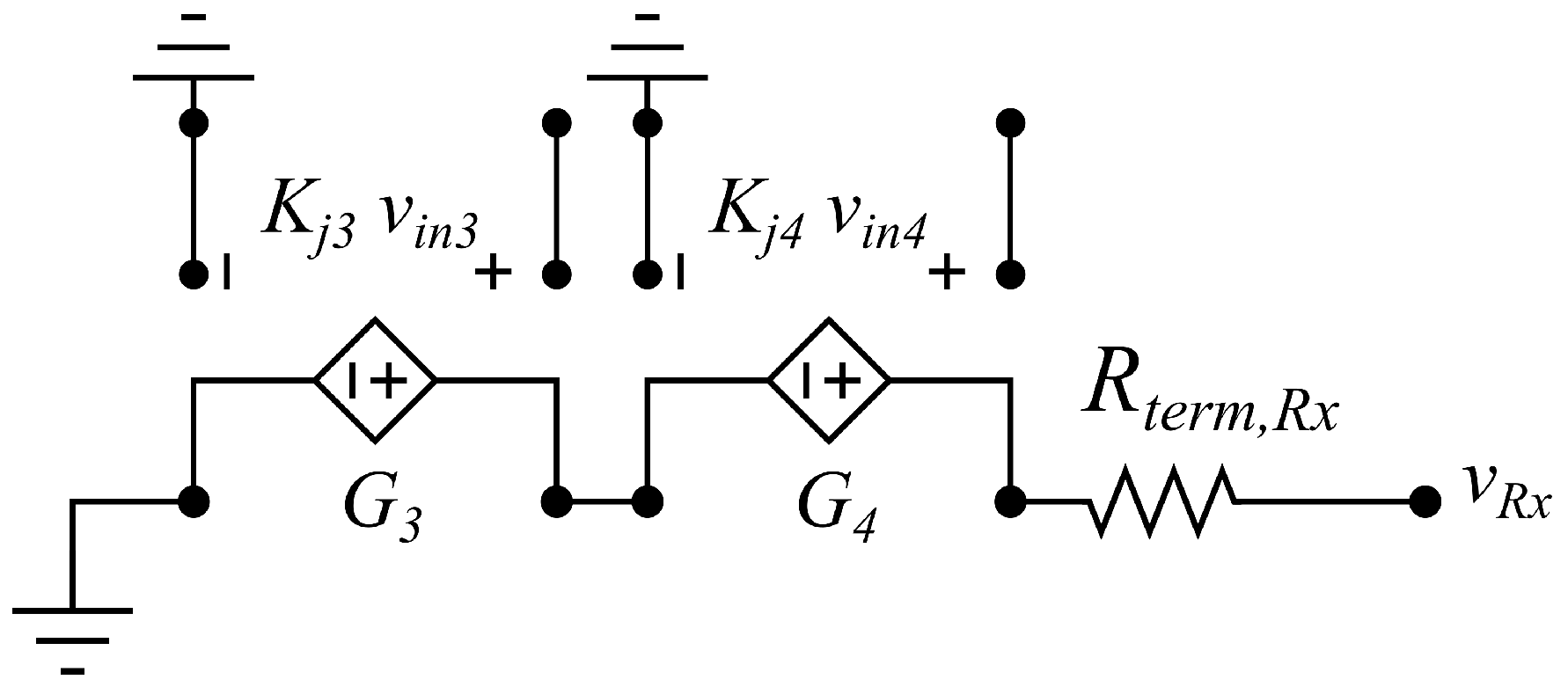

- The placement of the signal source is mainly controlled in the model by ideal voltage-controlled voltage sources (VCVSs) as shown in Figure 3, where represents the signal i placed on line j. The gain of each VCVS varies discretely between 0 and 1. If the gain is 1, the signal i is transmitted through line j; conversely, if the gain is 0, the signal i does not pass through line j. Therefore, binary states are used to define the placement of signals without distortion or time delay. The use of ideal VCVSs ensures that the accuracy of the simulation remains unaffected, allowing for the precise analysis of delay and distortion solely introduced by the system under investigation.

- (b)

- Transmission direction is controlled by using two separate sets of VCVSs, representing sources placed on the left or right sides and therefore controlling signal flow direction as will be illustrated in the following case study.

- (c)

- Termination: Lines that are not crossed by signals are terminated in open circuits (floating). Lines that are crossed by signals are terminated by the termination provided by the implemented standard. It is important to use proper terminations because it helps to ensure signal integrity during transmission through the communication medium. The value of terminations varies depending on the combination analyzed, so it varies with the state of the system. As a result, it is crucial to use a proper corresponding termination depending on the different signals and their transmission properties.

- A high-impedance state that represents the input buffer behavior or no signal transmission behavior;

- A resistor of small value (nearly 33 ohm) that represents the output impedance related to a signal driver.

3.2.2. Optimization Constraints

3.2.3. Optimization Goal

4. Discussion

4.1. Optimization Complexity and Heuristic Method

- Select line position of 1st signal (M choices);

- Select line position of 2nd signal ( choices);

- ...

- Select line position of Nth signal ( choices).

- One variable out of to (e.g., ) will be set to 1, the other variables with the same line number ( in this case) will be set to 0, and the other variables with the same signal number ( in this case) will be set to 0;

- In the submatrix formed by the remaining variables, one variable out of to (e.g., ) will be set to 1, the other variables with the same line number ( in this case) will be set to 0, and the other variables with the same signal number ( in this case) will be set to 0.

- And so on. A table of combinations is defined that includes all possible states of the system. This table is used to develop the parametric analysis. Once the parametric analysis part is defined, the optimization part is defined. An example of heuristic determination of transfer coefficients is shown in Figure 5, where variables in black are undetermined, variables in red are randomly chosen (i.e., independent variables), and variables in green are automatically determined (i.e., dependent variables) once the corresponding independent variables have been chosen.

4.2. Signal Transmission via Multiple Lines

4.3. Various Interconnects Types

5. Case Study

5.1. Reduced Media Independent Interface (RMII)

5.2. Optimization Implementation

- Modeling of signals: A clock generator with a frequency of 50 MHz is used to simulate the CLK signal. To simulate the transmission and reception signals, i.e., TDX0, TXD1, RXD0, and RXD1, independent signal generators that return a bit stream consistent with the communication standard specifications are used, requiring the use of a Pseudo Random Bit Sequence Generator (PRBS) in the circuit simulation. As represented in Figure 11, the transmission signals TDX0 and TXD1 are identified with the designation , the reception signals RXD0 and RXD1 are labeled as , and the clock signal CLK as .

- Modeling of signal directions: The left and right termination networks are composed of six circuit branches, one for each signal line of the FFC. The individual left- and right-side circuit branches are shown in Figure 12 and Figure 13, respectively. The circuit branches thus described are used to simulate the crosstalk impacting the left and right terminations of the cable. The signals at the terminations are enabled through the VCVS depicted in Figure 3. The composition of the signals at the terminations is controlled by a second set of VCVSs as defined in Section 3.2.1. Dimensionless gains, with x varying between 1 and 5, are set equal to 1.

- Modeling of terminations: As described in Section 3.2.1, the terminations of each line, namely and in Figure 12 and Figure 13 expressed in , can take one of two values, either open circuit or a specific resistance value depending on the requirements of the driver. For the RMII interface, the driver terminations commonly used and suggested by the design guidelines are 33 resistors. These resistors serve to maintain the integrity of signals during transmission through the communication medium, reducing the risk of reflections and ensuring that signals reach the receivers with optimal quality. The termination value is selected in an automated way through logic operations: if the transmission coefficient relative to line j is 1, the termination value of line j is set equal to 33 . Conversely, if is equal to 0, line j is terminated in high impedance. The selection of high impedance for idle lines is arbitrary. The results are not influenced by this choice.

5.3. Results

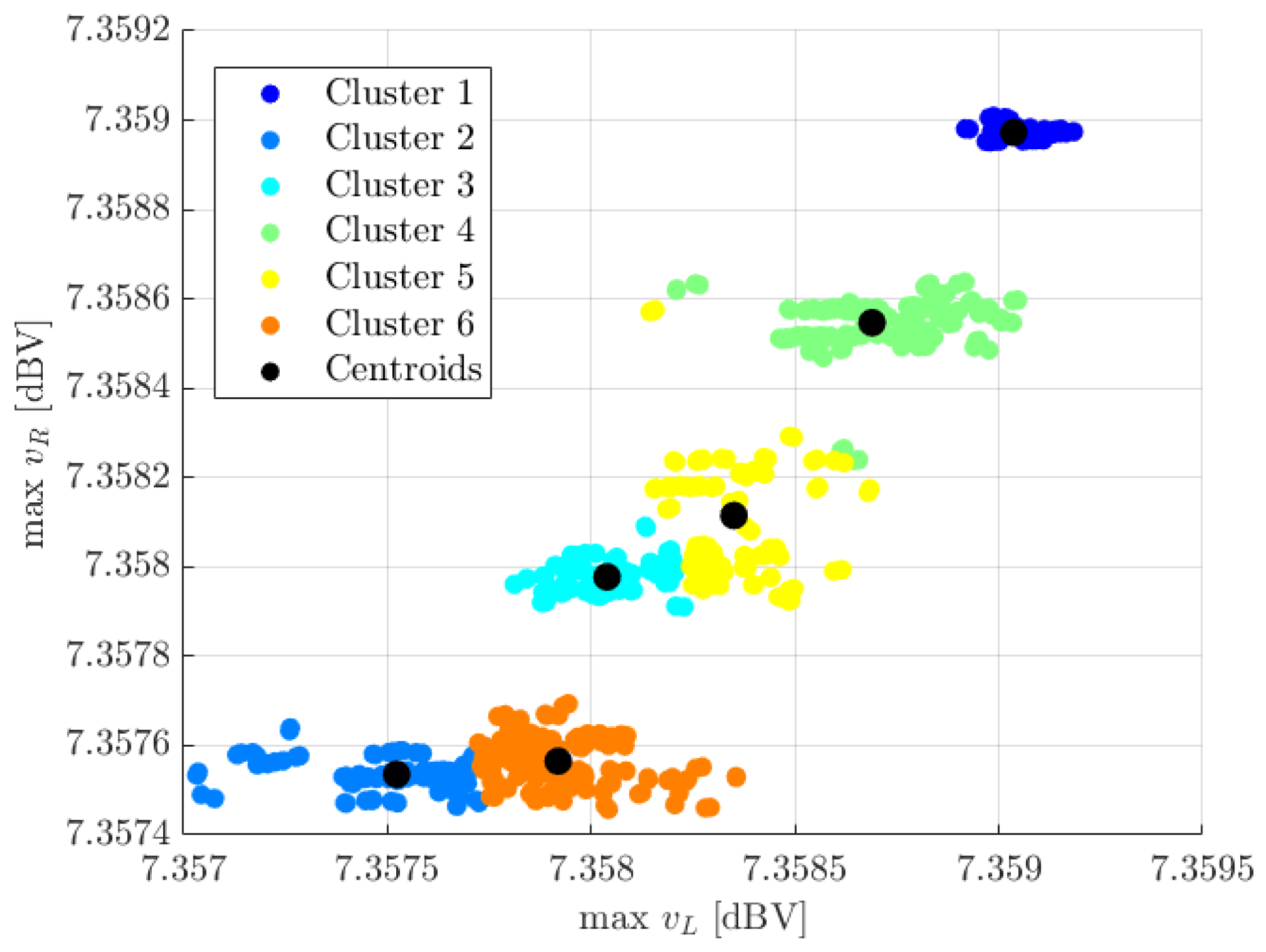

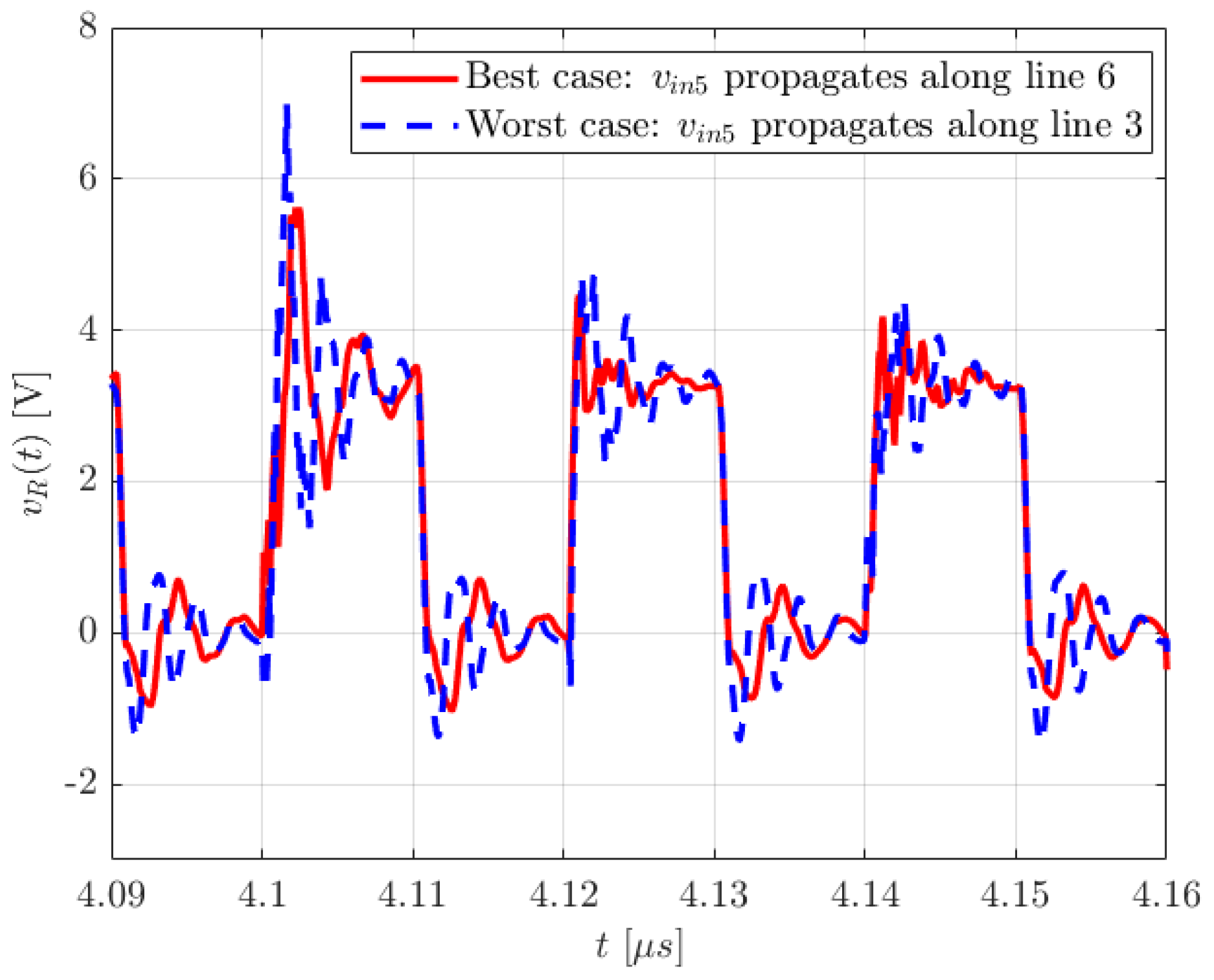

5.3.1. Experiment 1: Effect of Signal Orders

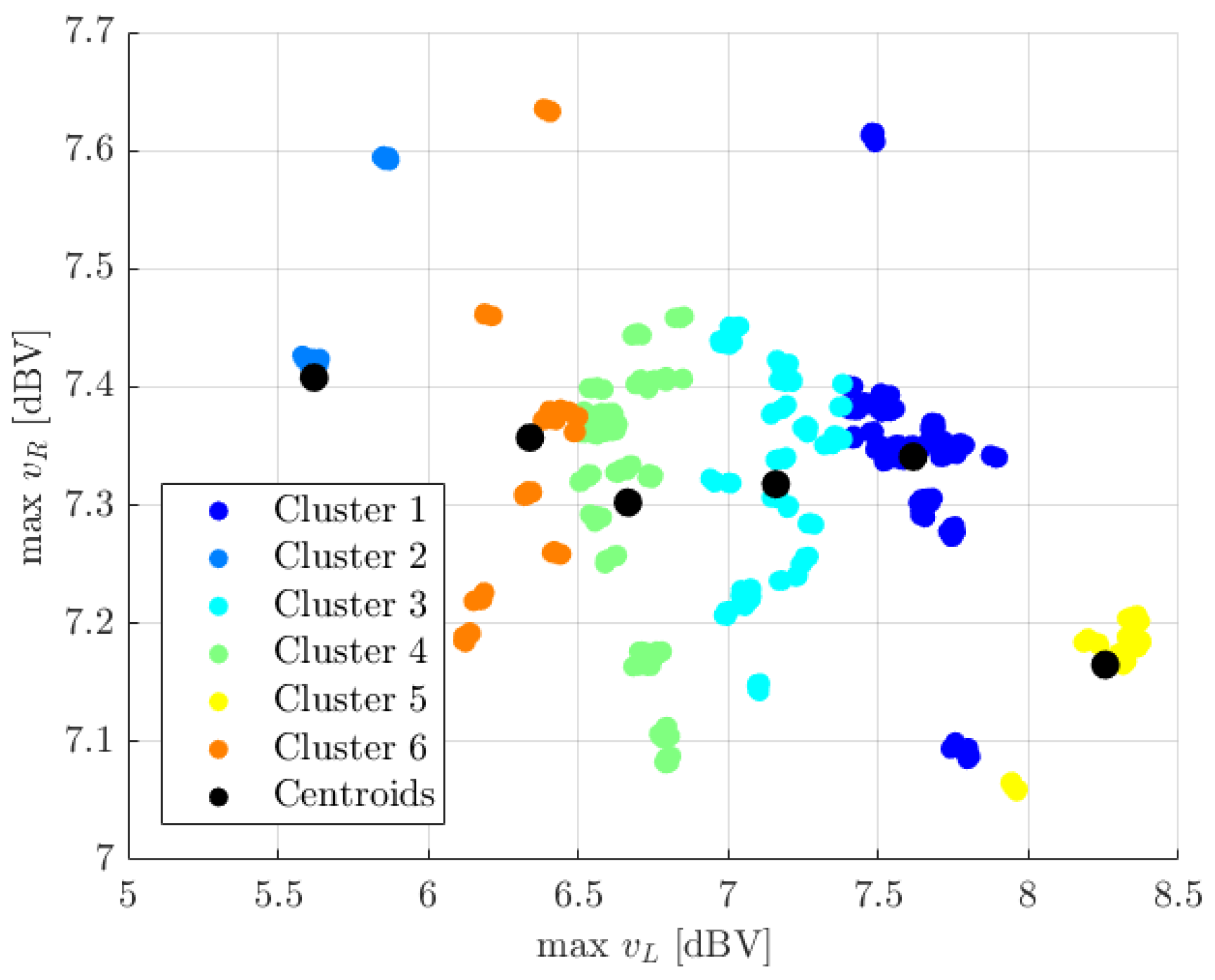

5.3.2. Experiment 2: Effect of FFC Lengths

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Paul, C.R. Introduction to Electromagnetic Compatibility; John Wiley & Sons: Hoboken, NJ, USA, 2006. [Google Scholar]

- Illiano, L.; Wu, X.; Grassi, F.; Spadacini, G.; Pignari, S.A. Review of Mode Conversion and Modal Analysis in Electromagnetic Compatibility. IEEE Access 2024, 12, 65513–65529. [Google Scholar] [CrossRef]

- Wu, T.L.; Buesink, F.; Canavero, F. Overview of Signal Integrity and EMC Design Technologies on PCB: Fundamentals and Latest Progress. IEEE Trans. Electromagn. Compat. 2013, 55, 624–638. [Google Scholar] [CrossRef]

- Schiavinotto, T.; Stützle, T. The linear ordering problem: Instances, search space analysis and algorithms. J. Math. Model. Algorithms 2004, 3, 367–402. [Google Scholar] [CrossRef]

- Moiseev, K.; Kolodny, A.; Wimer, S. Interconnect Optimization by Net Ordering. In Multi-Net Optimization of VLSI Interconnect; Springer: New York, NY, USA, 2014; pp. 167–194. [Google Scholar]

- Wimer, S.; Moiseev, K.; Kolodny, A. On VLSI interconnect optimization and linear ordering problem. Optim. Eng. 2011, 12, 603–609. [Google Scholar] [CrossRef]

- Zhu, Z.M.; Hao, B.T.; En, Y.F.; Yang, Y.T.; Li, Y.J. An interconnecting bus power optimization method combining interconnect wire spacing with wire ordering. Chin. Phys. B 2011, 20, 068401. [Google Scholar] [CrossRef]

- Yan, X.; Wu, C.; Zhang, D.; Jin, S.; Wu, S.; Fan, J.; Hwang, C. EMI Investigation and Mitigation of Flexible Flat Cables and Connectors. In Proceedings of the 2021 IEEE International Joint EMC/SI/PI and EMC Europe Symposium, Raleigh, NC, USA, 26 July–13 August 2021; pp. 515–519. [Google Scholar] [CrossRef]

- Webb, D.P.; Jaggernauth, W.A.; Cottrill, M.W.C.; West, A.A.; Conway, P.P.; Palmer, P.J. Electromagnetic compatibility performance of large area flexible printed circuit automotive harness. Proc. Inst. Mech. Eng. Part J. Automob. Eng. 2004, 218, 667–673. [Google Scholar] [CrossRef]

- Silaghi, A.M.; Pescari, C.; Bleoju, C.; De Sabata, A. Solving Automotive Signal Integrity Issues by EMC Simulation. In Proceedings of the 2021 IEEE 27th International Symposium for Design and Technology in Electronic Packaging (SIITME), Timisoara, Romania, 27–30 October 2021; pp. 33–36. [Google Scholar] [CrossRef]

- Zwillich, V.; Menzel, W.; Roehrig, L.; Leier, H. Odd-mode impedance-controlled shielded flat flexible cables for in-vehicle data transmission. In Proceedings of the 2006 17th International Zurich Symposium on Electromagnetic Compatibility, Singapore, 27 February–3 March 2006; pp. 348–351. [Google Scholar] [CrossRef]

- Kim, J.; Yu, J.K.; Seol, B.S.; Lee, J.; Nah, W. High frequency signal transfer characteristic of a 40-pin FPC connector. In Proceedings of the 2008 8th International Symposium on Antennas, Propagation and EM Theory, Kunming, China, 2–5 November 2008; pp. 917–920. [Google Scholar]

- Huang, S.Y.; Huang, T.Y.; Liu, C.T.; Wu, R.B. Ringing noise suppression for differential signaling in unshielded flexible flat cable. IEEE Trans. Components Packag. Manuf. Technol. 2015, 5, 1152–1159. [Google Scholar] [CrossRef]

- Yang, X.; Zhou, D.; Song, W.; She, Y.; Chen, X. A Cable Layout Optimization Method for Electronic Systems Based on Ensemble Learning and Improved Differential Evolution Algorithm. IEEE Trans. Electromagn. Compat. 2021, 63, 1962–1971. [Google Scholar] [CrossRef]

- Simonovich, B. Driver’s Output Impedance from IBIS. Bert Simonovich’s Design Notes. 2022. Available online: https://blog.lamsimenterprises.com/2010/12/22/drivers-output-impedance-from-ibis/ (accessed on 24 April 2024).

- IEEE Std 802.3-2022; Revision of IEEE Std 802.3-2018. IEEE Standard for Ethernet. IEEE: Piscataway, NJ, USA, 2022. [CrossRef]

- Illiano, L.; Liu, X.; Wu, X.; Grassi, F.; Pignari, S.A. Circuit Modeling of Fast Ethernet Signal for EMC and SI Analysis. In Proceedings of the 2023 International Symposium on Electromagnetic Compatibility–EMC Europe, Krakow, Poland, 4–8 September 2023; pp. 1–6. [Google Scholar]

- Würth Elektronik. WR-FFC Flat Flexible Cable—687606050002. 2021. Available online: https://www.we-online.com/en/components/products/FFC_0_50_TYPE_1_6876XXXXX002 (accessed on 1 May 2024).

- ANSYS. Ansys Q3D Extractor: Multiphysics Parasitic Extraction & Analysis. 2024. Available online: https://www.ansys.com/products/electronics/ansys-q3d-extractor (accessed on 1 May 2024).

| Total Combinations | Total Valid Combinations |

|---|---|

| 720 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Illiano, L.; Liu, X.; Wu, X.; Grassi, F.; Pignari, S.A. Signal Order Optimization of Interconnects Enabling High Electromagnetic Compatibility Performance in Modern Electrical Systems. Energies 2024, 17, 2786. https://doi.org/10.3390/en17112786

Illiano L, Liu X, Wu X, Grassi F, Pignari SA. Signal Order Optimization of Interconnects Enabling High Electromagnetic Compatibility Performance in Modern Electrical Systems. Energies. 2024; 17(11):2786. https://doi.org/10.3390/en17112786

Chicago/Turabian StyleIlliano, Ludovica, Xiaokang Liu, Xinglong Wu, Flavia Grassi, and Sergio Amedeo Pignari. 2024. "Signal Order Optimization of Interconnects Enabling High Electromagnetic Compatibility Performance in Modern Electrical Systems" Energies 17, no. 11: 2786. https://doi.org/10.3390/en17112786

APA StyleIlliano, L., Liu, X., Wu, X., Grassi, F., & Pignari, S. A. (2024). Signal Order Optimization of Interconnects Enabling High Electromagnetic Compatibility Performance in Modern Electrical Systems. Energies, 17(11), 2786. https://doi.org/10.3390/en17112786