Investigation of SiC MOSFET Body Diode Reverse Recovery and Snappy Recovery Conditions

Abstract

1. Introduction

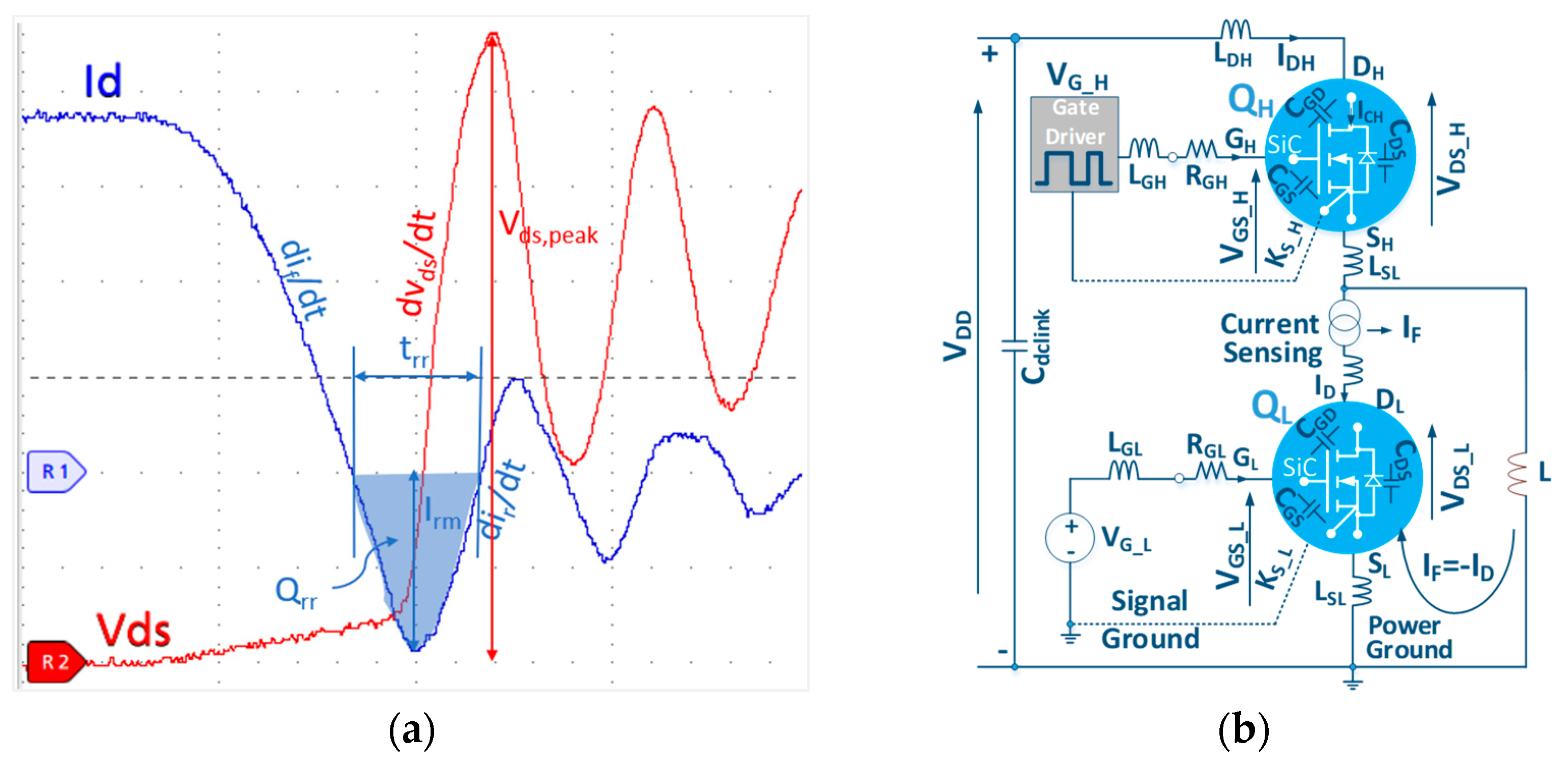

2. Reverse Recovery Theoretical Concepts

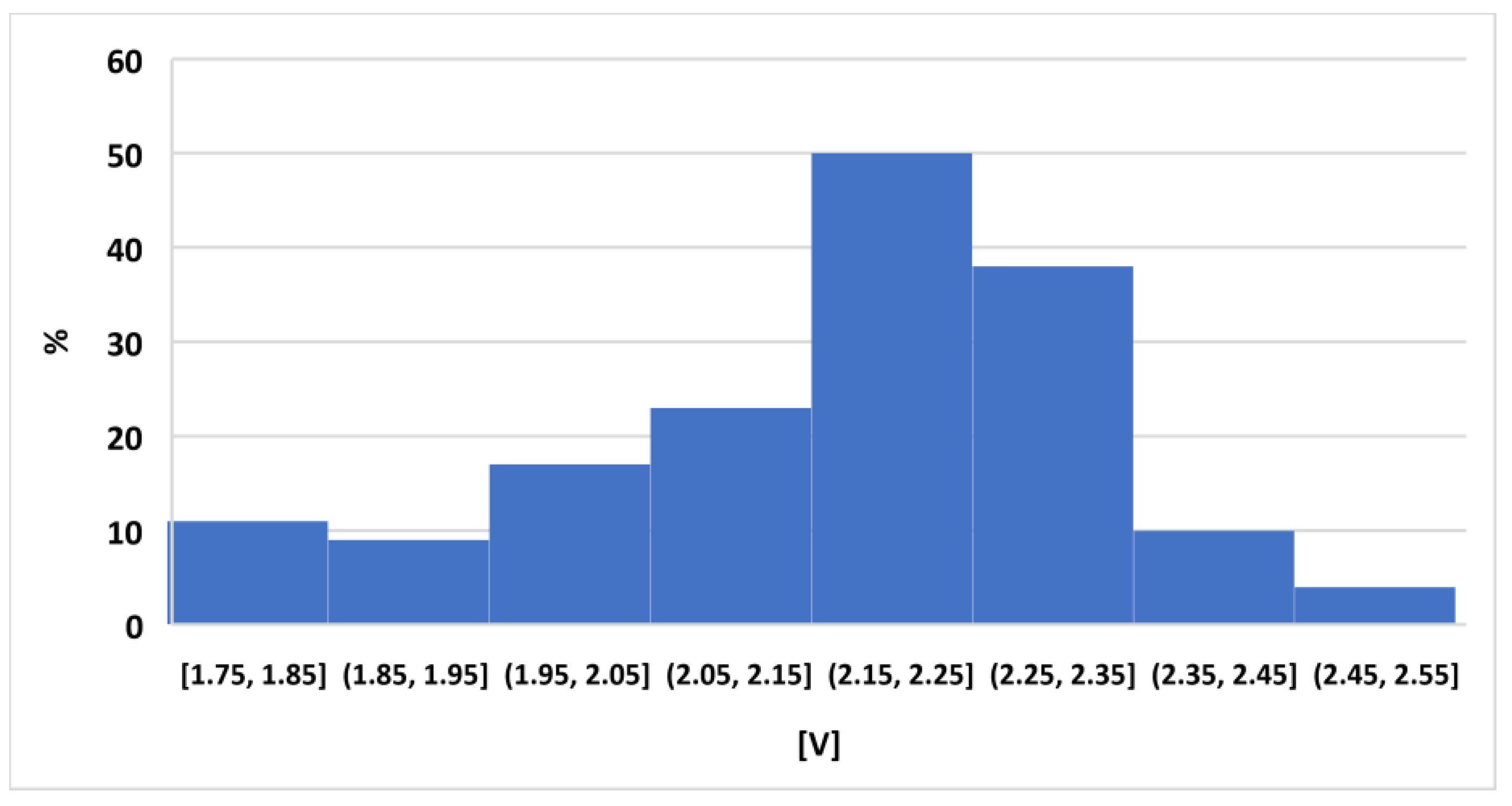

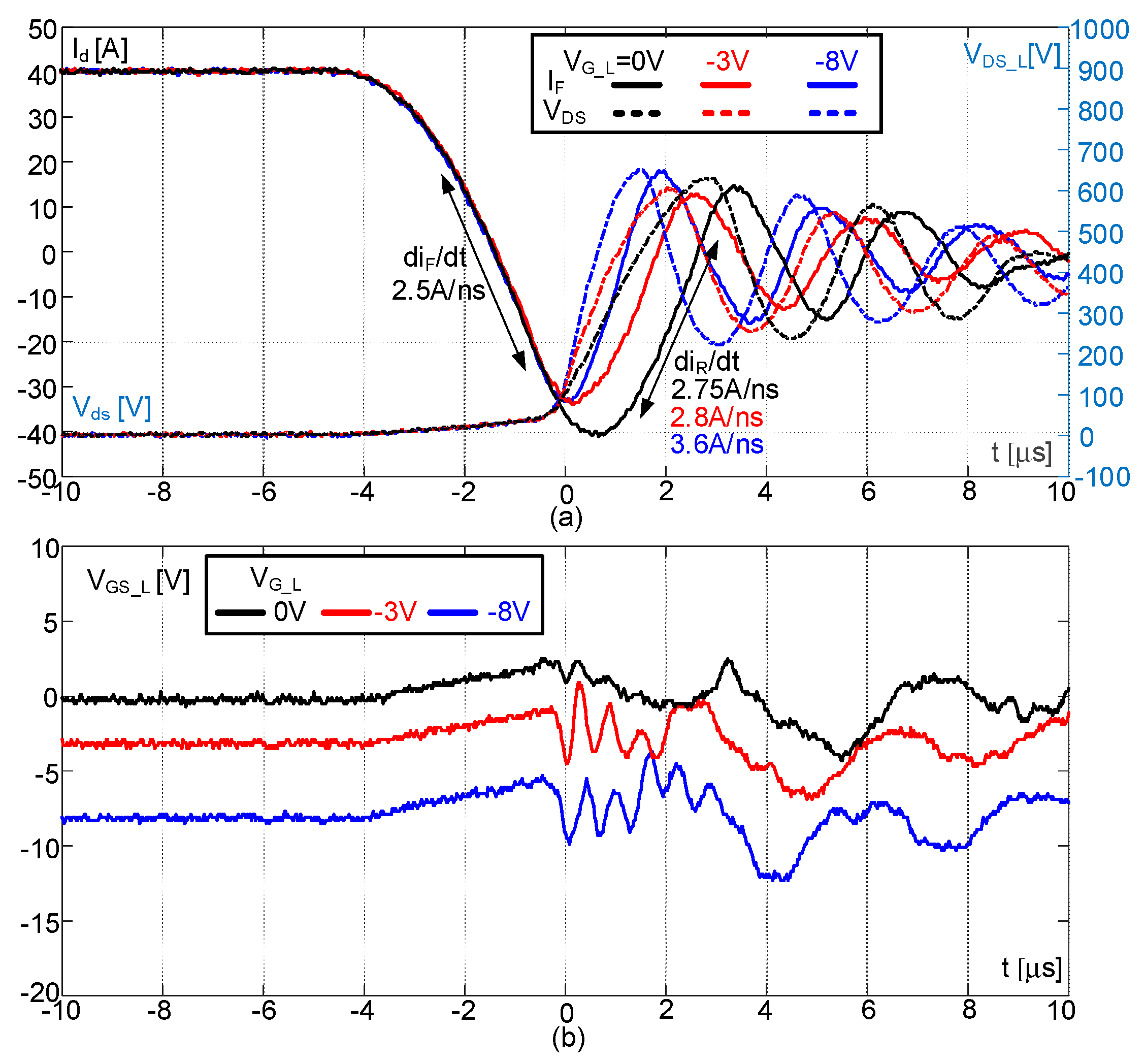

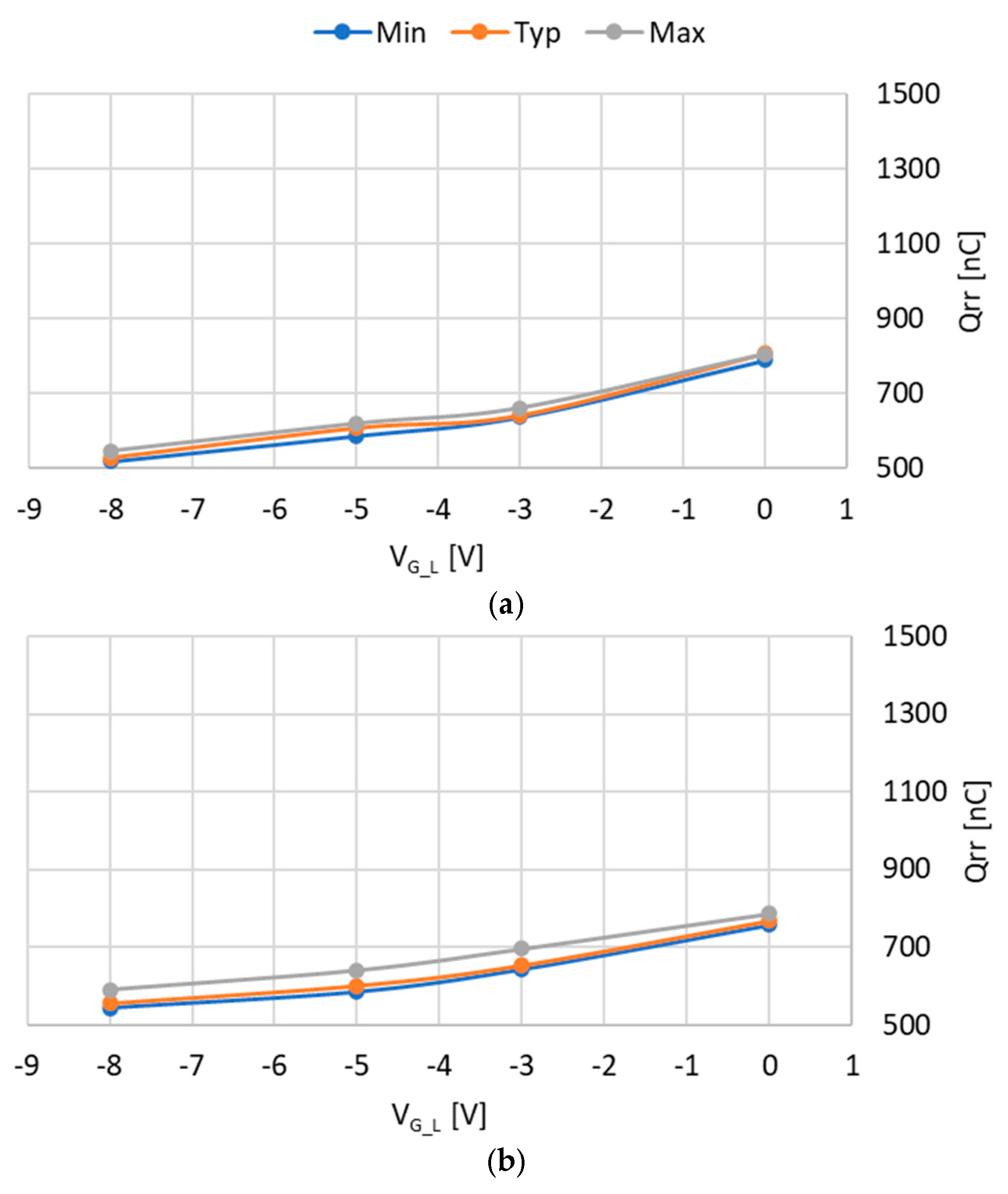

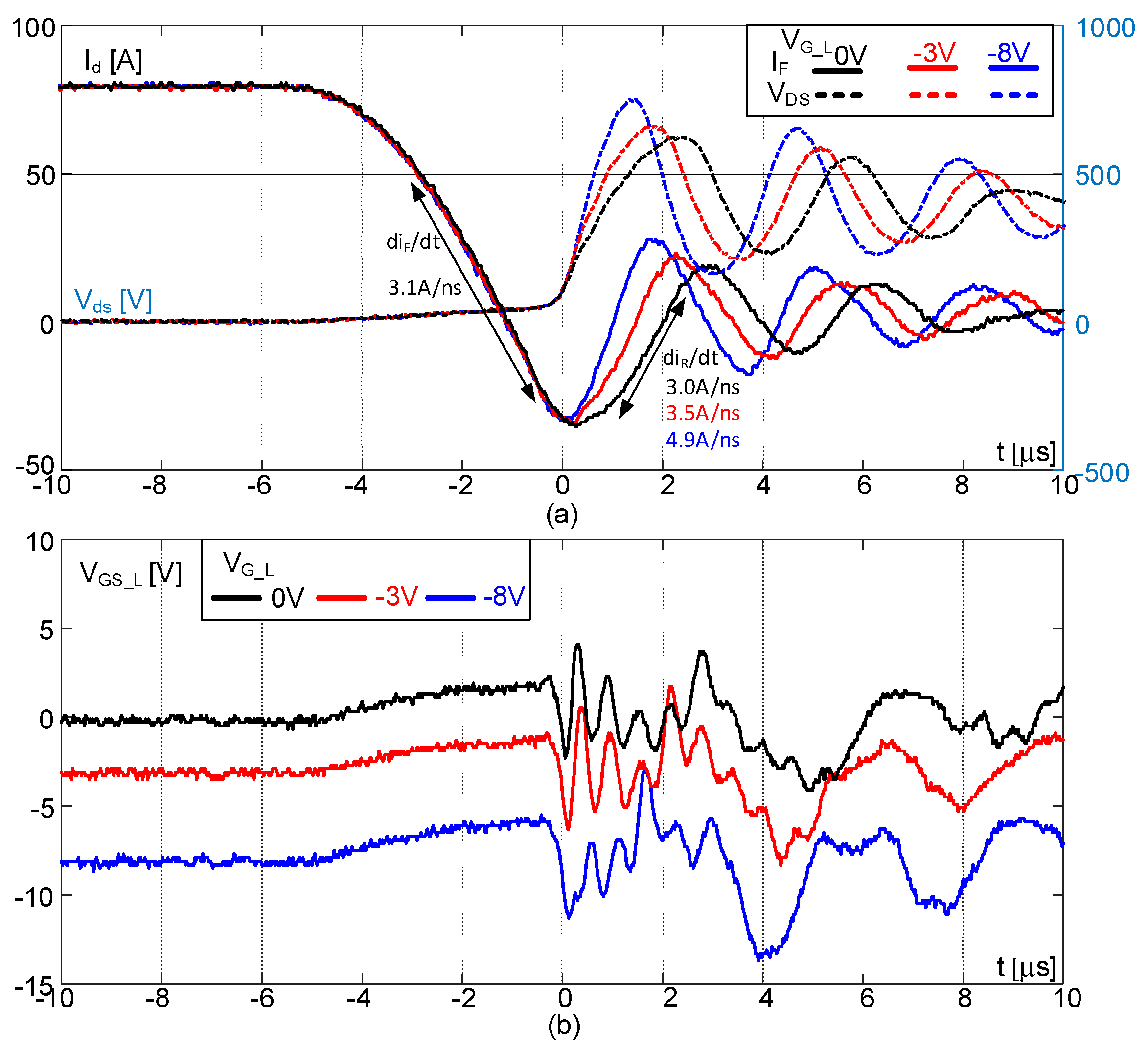

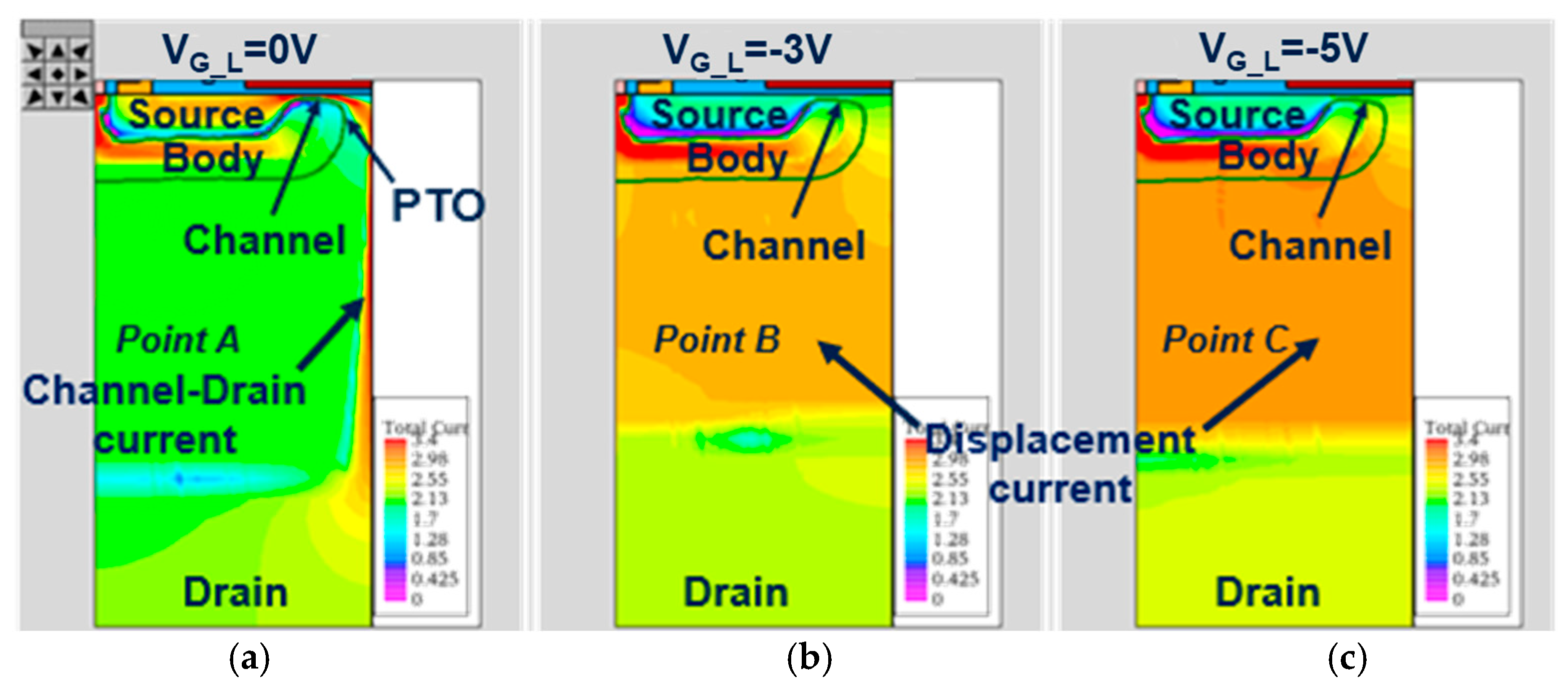

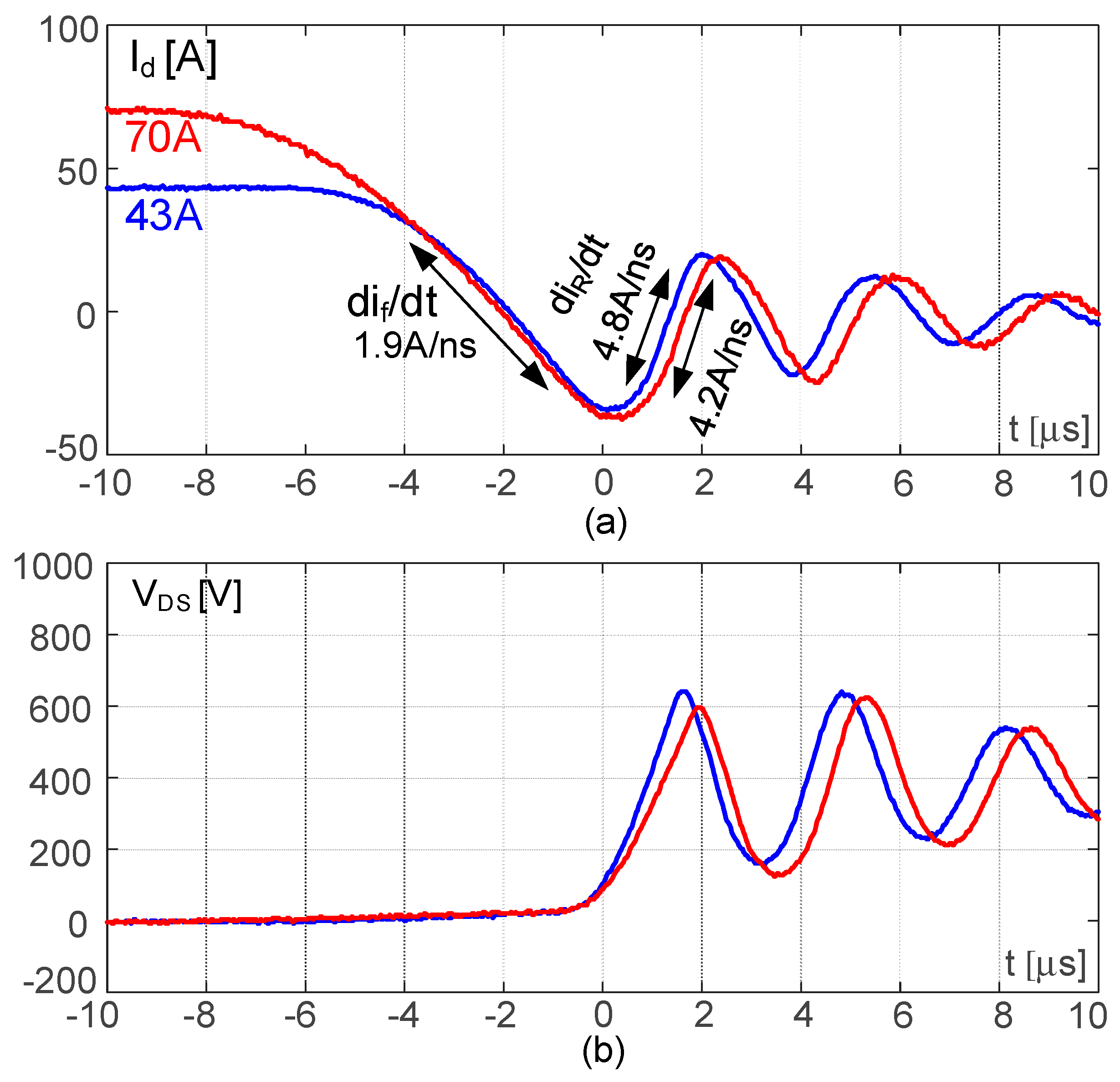

3. Experimental Analysis and TCAD Simulation of Reverse Recovery

- Qrr reverse recovery charge;

- trr reverse recovery time;

- Irm negative peak current;

- Erec reverse recovery losses.

- Temperature, Tc, (25 °C and 175 °C);

- Load current, Id, (40 A, 75 A and 120 A);

- Gate voltage, VG_L, (−8 V, −5 V, −3 V and 0 V).

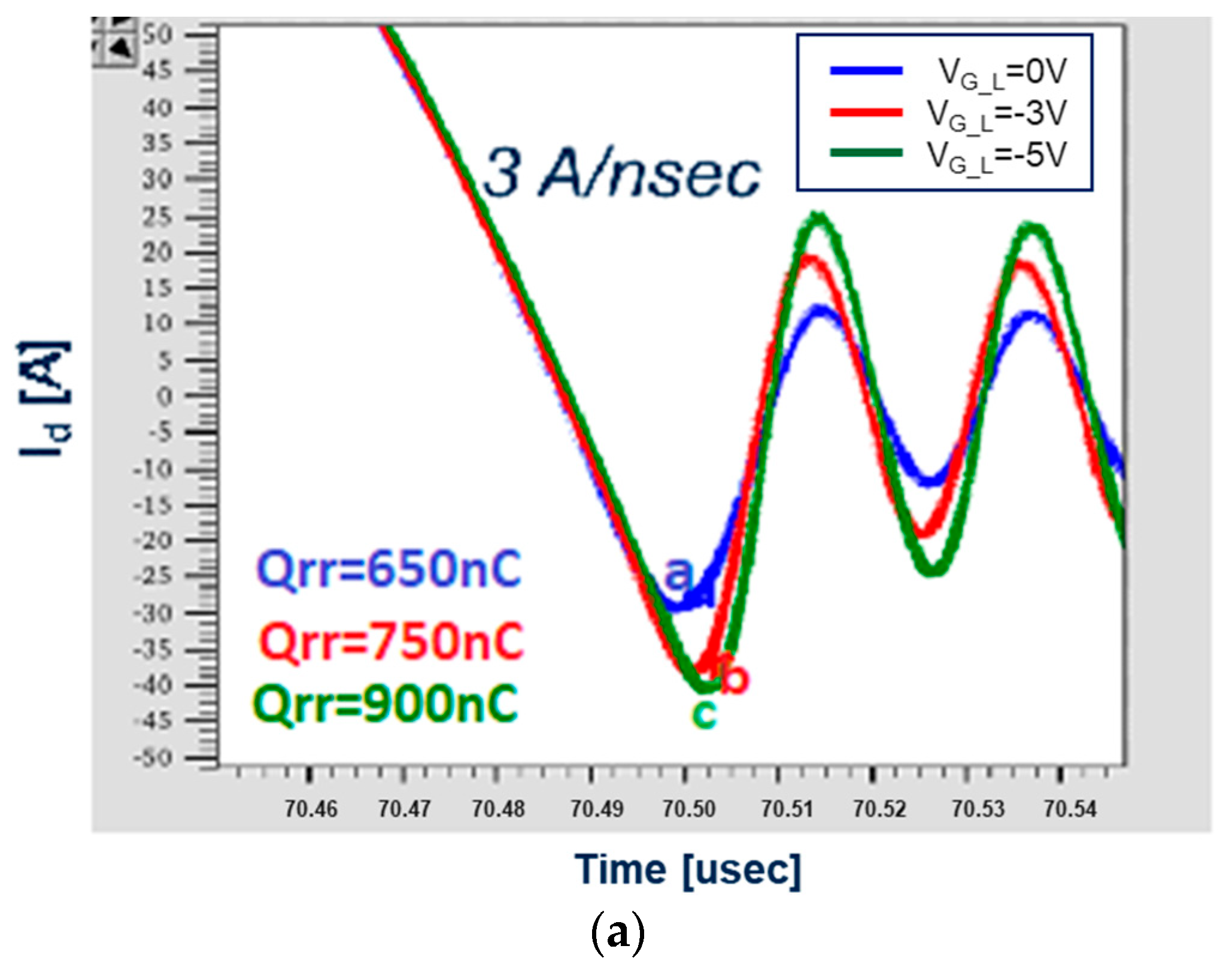

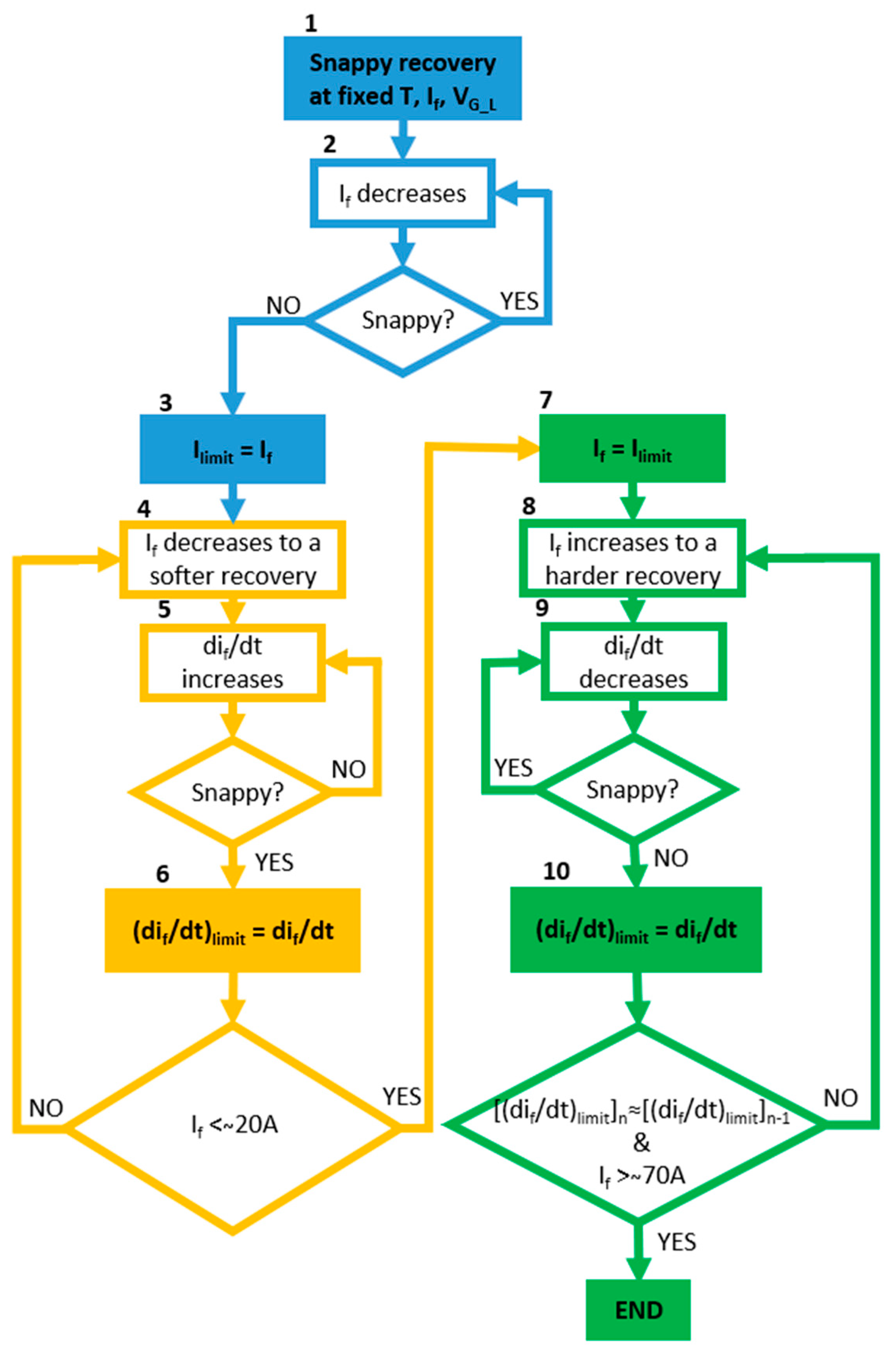

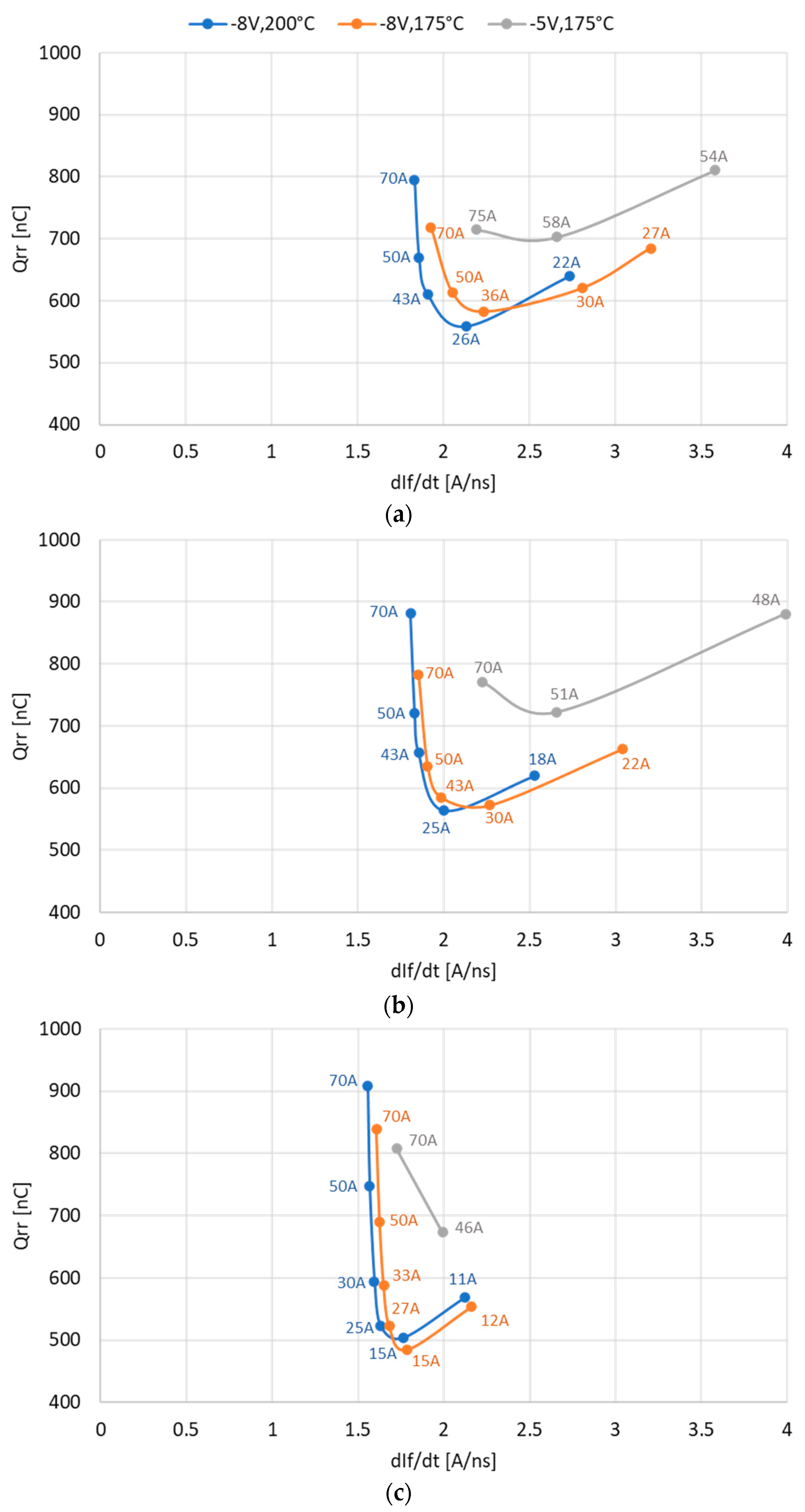

4. Analysis of Snappy Recovery Limits

- -

- Temperature (175 °C and 200 °C);

- -

- Gate-source voltage (−5 V and −8 V).

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Eskandari, S.; Peng, K.; Tian, B.; Santi, E. Accurate Analytical Switching Loss Model for High Voltage SiC MOSFETs Includes Parasitics and Body Diode Reverse Recovery Effects. In Proceedings of the IEEE Energy Conversion Congress and Exposition, Portland, OR, USA, 23–27 September 2018; pp. 1867–1874. [Google Scholar]

- Rahimo, M.T. A comprehensive study of failure mode in IGBT applications due to freewheeling diode snappy recovery. In Proceedings of the Conference Record of 1998 IEEE Industry Applications Conference. Thirty-Third IAS Annual Meeting (Cat. No.98CH36242), St. Louis, MO, USA, 12–15 October 1998; Volume 2, pp. 840–847. [Google Scholar]

- Kumar, A.; Vechalapu, K.; Bhattacharya, S.; Veliadis, V.; Van Brunt, E.; Grider, D.; Sabri, S.; Hull, B. Effect of capacitive current on reverse recovery of body diode of 10 kV SiC MOSFETs and external 10 kV SiC JBS diodes. In Proceedings of the IEEE 5th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Albuquerque, NM, USA, 30 October–1 November 2017; pp. 208–212. [Google Scholar]

- Xue, P.; Maresca, L.; Riccio, M.; Breglio, G.; Irace, A. Self-sustained Oscillation of Superjunction MOSFET Intrinsic Diode During Reverse Recovery Transient. In Proceedings of the 31st International Symposium on Power Semiconductor Devices and ICs (ISPSD), Shanghai, China, 19–23 May 2019. [Google Scholar]

- Khorasani, A.E.; Griswold, M.; Alford, T.L. Gate-Controlled Reverse Recovery for Characterization of LDMOS Body Diode. IEEE Electron Device Lett. 2014, 35, 1079–1081. [Google Scholar] [CrossRef]

- Lindberg-Poulsen, K.; Petersen, L.P.; Ouyang, Z.; Andersen, M.A.E. Practical investigation of the gate bias effect on the reverse recovery behavior of the body diode in power MOSFETs. In Proceedings of the International Power Electronics Conference (IPEC-Hiroshima 2014—ECCE ASIA), Hiroshima, Japan, 18–21 May 2014. [Google Scholar]

- Choo, V.L.; Pfost, M.; Gessner, J.; Heinrich, K.; Eckoldt, U.; Liew, M.; Hao, Y. Reverse Recovery and Carrier Lifetime in Body Diodes of LDMOS Transistors. In Proceedings of the 2021 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Nagoya, Japan, 30 May–3 June 2021. [Google Scholar]

- Ferrara, A.; Siemieniec, R.; Medic, U.; Hutzler, M.; Blank, O.; Henson, T. Evolution of reverse recovery in trench MOSFETs. In Proceedings of the 2020 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Vienna, Austria, 13–18 September 2020. [Google Scholar]

- Xue, Z.; Zhu, M.; Cui, H.; Yang, F.; Pei, Y.; Wang, L. TCAD Modeling of Temperature-Dependent Reverse Recovery Characteristics of 1.2-kV SiC MOSFETs’ Body Diode. In Proceedings of the 2023 IEEE Energy Conversion Congress and Exposition (ECCE), Nashville, TN, USA, 29 October–2 November 2023. [Google Scholar]

- Li, P.; Ma, R.; Yang, Z.; Guo, J.; Lin, Z.; Hu, S. A Novel Approach to Suppress the Inhomogeneous Reverse Recovery Behavior of the Body Diode in Superjunction MOSFET. In Proceedings of the 2022 IEEE 16th International Conference on Solid-State & Integrated Circuit Technology (ICSICT), Nangjing, China, 25–28 October 2022. [Google Scholar]

- Qian, C.; Wang, Z.; Zhou, D.; Ge, Y.; Zhou, Y.; Xingyuan, Y.; Xin, G.; Shi, X. Investigation of Reverse Recovery Phenomenon for SiC MOSFETs in High-Temperature Applications. IEEE Trans. Power Electron. 2023, 38, 14375–14387. [Google Scholar] [CrossRef]

- An, J.; Hu, S. Heterojunction Diode Shielded SiC Split-Gate Trench MOSFET With Optimized Reverse Recovery Characteristic and Low Switching Loss. IEEE Access 2019, 7, 28592–28596. [Google Scholar] [CrossRef]

- Huang, M.; Li, R.; Yang, Z.; Ma, Y.; Li, Y.; Zhang, X.; Gong, M. A Multiepi Superjunction MOSFET With a Lightly Doped MOS-Channel Diode for Improving Reverse Recovery. IEEE Trans. Electron Devices 2021, 68, 2401–2407. [Google Scholar] [CrossRef]

- Liu, F.; Ruan, X. Analysis of the Body Diode Reverse Recovery of MOSFETs in ZVS PWM Combined Three-level Converter. In Proceedings of the 2007 IEEE Power Electronics Specialists Conference, Orlando, FL, USA, 17–21 June 2007. [Google Scholar]

- Bernal, C.; Jimenez, M. Adherence of a high-speed RRP LDMOS characterization setup to JESD 24-10 standard. In Proceedings of the IEEE 8th Latin American Symposium on Circuits & Systems (LASCAS), Bariloche, Argentina, 20–23 February 2017. [Google Scholar]

- Kanemoto, M.; Aoki, M.; Mochizuki, A.; Murakami, Y.; Tsunoda, M.; Yoshinari, G.; Nakano, N. Comparison of thermal stress under TCT between SiC and Si power devices using direct chip-bonding with ag sintered layer on Cu plate. In Proceedings of the 2017 IEEE Electrical Design of Advanced Packaging and Systems Symposium (EDAPS), Haining, China, 14–16 December 2017. [Google Scholar]

- Zhou, X.; Jia, Y.; Hu, D.; Wu, Y. A Simulation-Based Comparison Between Si and SiC MOSFETs on Single-Event Burnout Susceptibility. IEEE Trans. Electron Devices 2019, 66, 2551–2556. [Google Scholar] [CrossRef]

- Chen, J.; Deng, E.; Zhao, Z.; Wu, Y.; Huang, Y. Power Cycling Capability Comparison of Si and SiC MOSFETs under Different Conduction Modes. In Proceedings of the 2020 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Vienna, Austria, 13–18 September 2020. [Google Scholar]

- Naik, H.; Chow, P.T. Comparison of AC I-V characteristic of Si and SiC MOSFETs. In Proceedings of the 2012 Lester Eastman Conference on High Performance Devices (LEC), Providence, RI, USA, 7–9 August 2012. [Google Scholar]

- Qi, F.; Fu, L.; Xu, L.; Jing, P.; Zhao, G.; Wang, J. Si and SiC power MOSFET characterization and comparison. In Proceedings of the 2014 IEEE Conference and Expo Transportation Electrification Asia-Pacific (ITEC Asia-Pacific), Beijing, China, 31 August–3 September 2014. [Google Scholar]

- Bouchetob, E.; Nadji, B.; Mahdi, I. Efficiency comparison of silicon and silicon carbide MOSFETs in a PV system application. In Proceedings of the 2023 International Conference on Advances in Electronics, Control and Communication Systems (ICAECCS), BLIDA, Algeria, 6–7 March 2023. [Google Scholar]

- Sachdev, N.; Bhat, A.K.S. Performance comparison of Si and SiC MOSFETs in a bidirectional dual half-bridge series resonant converter. In Proceedings of the 2018 International Conference on Power, Instrumentation, Control and Computing (PICC), Thrissur, India, 18–20 January 2018. [Google Scholar]

- Kibushi, R.; Hatakeyama, T.; Yuki, K.; Unno, N.; Ishizuka, M. Comparison of thermal properties between Si and SiC power MOSFET using electro-thermal analysis. In Proceedings of the 2017 International Conference on Electronics Packaging (ICEP), Yamagata, Japan, 19–22 April 2017. [Google Scholar]

- Bhat, A.; Bhatt, N. Design and Performance Comparison of Si and SiC MOSFETs for Dual Tank LCL-Type Series Resonant Converter. In Proceedings of the 2019 IEEE Conference on Energy Conversion (CENCON), Yogyakarta, Indonesia, 16–17 October 2019. [Google Scholar]

- Blinov, A.; Chub, A.; Vinnikov, D.; Rang, T. Feasibility study of Si and SiC MOSFETs in high-gain DC/DC converter for renewable energy applications. In Proceedings of the IECON 2013—39th Annual Conference of the IEEE Industrial Electronics Society, Vienna, Austria, 10–13 November 2013. [Google Scholar]

- Jordan, J.; Esteve, V.; Sanchis-Kilders, E.; Dede, E.J.; Maset, E.; Ejea, J.B.; Ferreres, A. A Comparative Performance Study of a 1200 V Si and SiC MOSFET Intrinsic Diode on an Induction Heating Inverter. IEEE Trans. Power Electron. 2014, 29, 2550–2562. [Google Scholar] [CrossRef]

- Gui, H.; Zhang, Z.; Ren, R.; Chen, R.; Niu, J.; Tolbert, L.M.; Wang, F.; Blalock, B.J.; Cositinett, D.J.; Choi, B.B. SiC MOSFET Versus Si Super Junction MOSFET-Switching Loss Comparison in Different Switching Cell Configurations. In Proceedings of the 2018 IEEE Energy Conversion Congress and Exposition (ECCE), Portland, OR, USA, 23–27 September 2018. [Google Scholar]

- Kibushi, R.; Hatakeyama, T.; Yuki, K.; Unno, N.; Ishizuka, M. Comparison of hot spot temperature between Si and SiC power MOSFET using electro-thermal analysis. In Proceedings of the 2017 16th IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (ITherm), Orlando, FL, USA, 30 May–2 June 2017. [Google Scholar]

- Chen, Z.; Boroyevich, D.; Li, J. Behavioral comparison of Si and SiC power MOSFETs for high-frequency applications. In Proceedings of the 2013 Twenty-Eighth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 17–21 March 2013. [Google Scholar]

- Pulvirenti, M.; Sciacca, A.G.; Salvo, L.; Nania, M.; Scelba, G.; Scarcella, G. Body Diode Reverse Recovery Effects on SiC MOSFET Half-Bridge Converters. In Proceedings of the IEEE Energy Conversion Congress and Exposion (ECCE), Detroit, MI, USA, 11–15 October 2020; pp. 2871–2877. [Google Scholar]

- Nayak, D.P.; Yakala, R.K.; Kumar, M.; Pramanick, S.K. Temperature-Dependent Reverse Recovery Characterization of SiC MOSFETs Body Diode for Switching Loss Estimation in a Half-Bridge. IEEE Trans. Power Electron. 2022, 37, 5574–5582. [Google Scholar] [CrossRef]

- Liu, X.; Li, X.; Hermann, C.; Blaser, T. The Impact of the Dead-Time on the Reverse Recovery Behavior of SiC-MOSFET Body Diodes. In Proceedings of the International Symposium on Power Semiconductor Devices and ICs (ISPSD), Hong Kong, China, 28 May–1 June 2023. [Google Scholar]

- Kumar, A.; Bhattacharya, S.; Baliga, J. Influence of the Inverter Dead-time on the Reverse Recovery Characteristics of 3.3-kV SiC MOSFETs and JBSFETs. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Detroit, MI, USA, 9–13 October 2022. [Google Scholar]

- Qi, J.; Tian, K.; Mao, Z.; Yang, S.; Song, W.; Zhang, A. Dynamic Characterization of 1.2 kV SiC Power MOSFET Body Diode at Cryogenic and High Temperatures. In Proceedings of the 1st Workshop on Wide Bandgap Power Devices and Applications in Asia (WiPDA Asia), Xi’an, China, 16–18 May 2018. [Google Scholar]

- Hou, X.; Boroyevich, D.; Burgos, R. Characterization on latest-generation SiC MOSFET’s body diode. In Proceedings of the 4th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Fayetteville, AR, USA, 7–9 November 2016. [Google Scholar]

- Zhang, D.; Horii, K.; Hata, K.; Takamiya, M. Digital Gate Driver IC with Real-Time Gate Current Change by Sensing Drain Current to Cope with Operating Condition Variations of SiC MOSFET. In Proceedings of the 2023 11th International Conference on Power Electronics and ECCE Asia (ICPE 2023—ECCE Asia), Jeju Island, Republic of Korea, 22–25 May 2023. [Google Scholar]

- Roy, S.K.; Basu, K. An Energy based Approach to Calculate Actual Switching Loss for SiC MOSFET from Experimental Measurement. In Proceedings of the 2021 IEEE 12th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Chicago, IL, USA, 28 June–1 July 2021. [Google Scholar]

- Ahmed, M.R.; Todd, R.; Forsyth, A.J. Switching performance of a SiC MOSFET body diode and SiC schottky diodes at different temperatures. In Proceedings of the 2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, USA, 1–5 October 2017. [Google Scholar]

- Cameron, A.; Hopkins, A.; Simpson, N.; Mellor, P. Low Temperature Loss-Analysis of SiC MOSFETs for Integrated Motor Drive Applications. In Proceedings of the 2023 IEEE Energy Conversion Congress and Exposition (ECCE), Nashville, TN, USA, 29 October–2 November 2023. [Google Scholar]

- Sarnowska, A.; Rabkowski, J. Hard and soft switching operation of the half-bridge based on 900V SiC MOSFETs. In Proceedings of the IECON 2016—42nd Annual Conference of the IEEE Industrial Electronics Society, Florence, Italy, 23–26 October 2016. [Google Scholar]

- Chen, X.; Jiang, S.; Chen, Y.; Gou, H.; Xie, Q.; Shen, B. Transient Modeling and Loss Analysis of SiC MOSFETs at Cryogenic and Room Temperatures. IEEE Trans. Appl. Supercond. 2021, 31, 1400404. [Google Scholar] [CrossRef]

- Song, Q.; Wang, W.; Zhang, S.; Li, Y.; Ahmad, M. The analysis of power losses of power inverter based on SiC MOSFETs. In Proceedings of the 2019 1st Global Power, Energy and Communication Conference (GPECOM), Nevsehir, Turkey, 12–15 June 2019. [Google Scholar]

- Rashid, A.U.; Brooks, B.; Manz, S.; Lichtenwalner, D.J.; Ryu, S.-H. Modeling of the Snappy, and Soft Reverse Recovery of SiC MOSFET’s Body Diode. In Proceedings of the IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS), Monterey, CA, USA, 16–18 October 2023. [Google Scholar]

- Di Luca Cardillo, G.; Salvo, L.; Pulvirenti, M.; Sciacca, A.G.; Cascino, S.; Rizzo, S.A.; Scelba, G.; Salerno, N. Investigation of the limit conditions of SiC MOSFET body diode reverse recovery. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Nashville, TN, USA, 29 October–2 November 2023. [Google Scholar]

- Marz, A.; Schonewolf, S.; Nagel, A.; Rauh, M.; Bakran, M.-M. Deadtime optimization eliminating snap-off of 3.3kV SiC MOSFET bodydiodes. In Proceedings of the 2023 25th European Conference on Power Electronics and Applications (EPE’23 ECCE Europe), Aalborg, Denmark, 4–8 September 2023. [Google Scholar]

- Li, X.; Xiao, F.; Luo, Y.; Wang, R.; Duan, Y. Modeling of High-Voltage Nonpunch-Through PIN Diode Snappy Reverse Recovery and Its Optimal Suppression Method Based on RC Snubber Circuit. IEEE Trans. Ind. Electron. 2022, 69, 5700–5712. [Google Scholar] [CrossRef]

- Karout, M.A.; Taha, M.; Fisher, C.A.; Deb, A.; Mawby, P.; Alatise, O. Impact of Diode Characteristics on 1.2 kV SiC MOSFET and Cascode JFET Efficiency: Body Diodes Vs SiC Schottky Barrier Diodes. In Proceedings of the 2023 IEEE Applied Power Electronics Conference and Exposition (APEC), Orlando, FL, USA, 19–23 March 2023. [Google Scholar]

- Awwad, A.E.; Dieckerhoff, S. Operation of planar and trench SiC MOSFETs in a 10kW DC/DC-converter analyzing the impact of the body diode. In Proceedings of the 2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, USA, 1–5 October 2017. [Google Scholar]

- Ahmed, M.R.; Todd, R.; Forsyth, A.J. Predicting SiC MOSFET Behavior Under Hard-Switching, Soft-Switching, and False Turn-On Conditions. IEEE Trans. Ind. Electron. 2017, 64, 9001–9011. [Google Scholar] [CrossRef]

| Quantity | Value |

|---|---|

| Relative permittivity | 9.76 |

| Bandgap Eg (@300 K) | 3.26 eV |

| Affinity | 3.7 |

| Alpha coeff. for temperature dependence of bandgap | 3.3∙102 eV/K |

| Beta coeff. for temperature dependence of bandgap | 105 K |

| Conduction band density (@300 K) | 1.7∙1019 cm−3 |

| Valence band density (@300 K) | 2.5∙10−19 cm−3 |

| Richardson constant for electrons | 146 A/cm2/K2 |

| Richardson constant for holes | 30 A/cm2/K2 |

| Electron/Holes Auger coefficient | 3∙10−29 cm6/s |

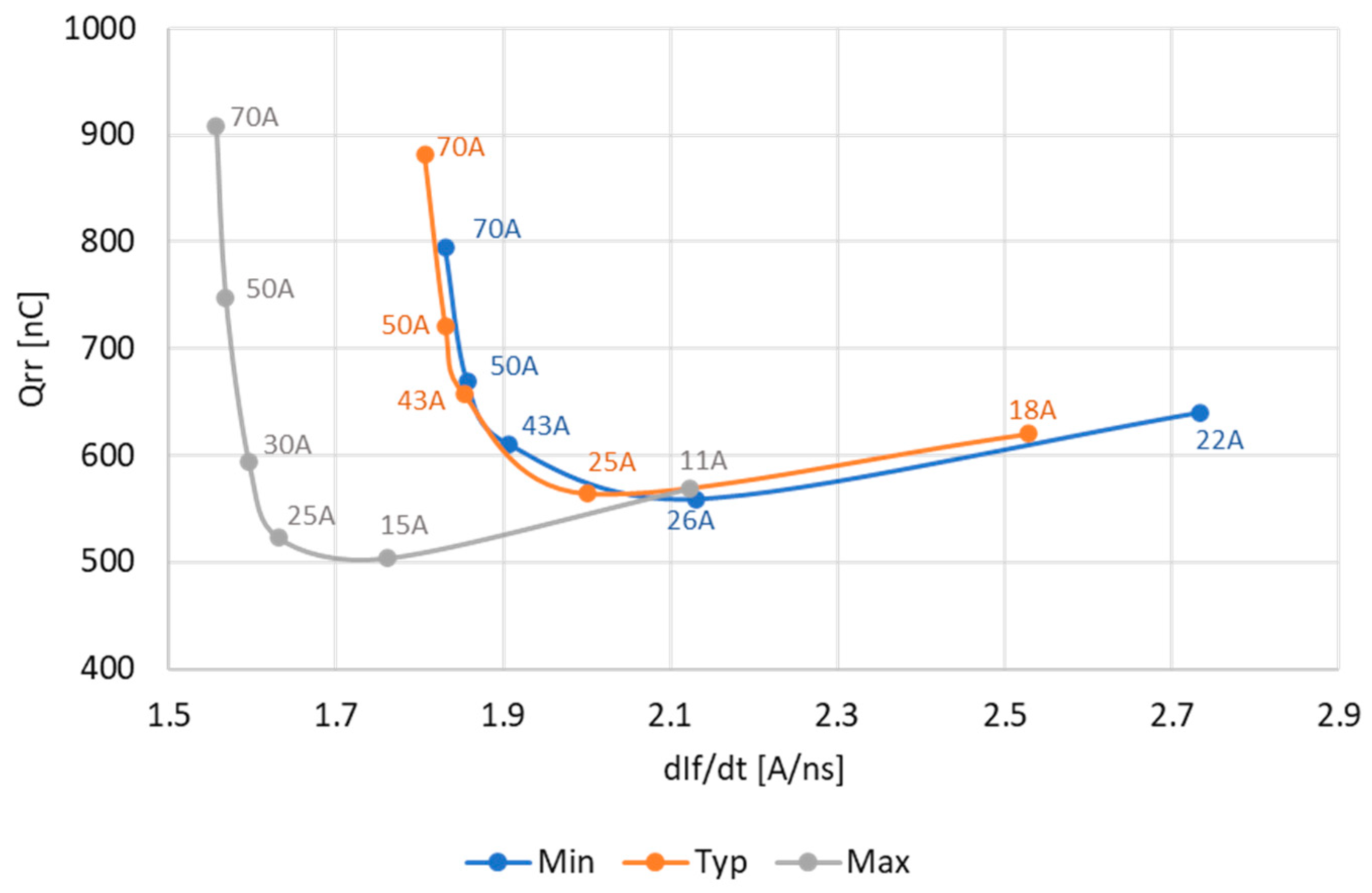

| Device | Tj [°C] | VG_L [V] | Id [A] | Ilimit [A] |

|---|---|---|---|---|

| Min | 175 | −8 | 75 | 36 |

| 200 | 40 | 26 | ||

| 175 | −5 | 75 | 58 | |

| Typ | 175 | −8 | 40 | 30 |

| 200 | 40 | 25 | ||

| 175 | −5 | 75 | 51 | |

| Max | 175 | −8 | 40 | 15 |

| 200 | 40 | 15 | ||

| 175 | −5 | 75 | 70 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Pennisi, G.; Pulvirenti, M.; Salvo, L.; Sciacca, A.G.; Cascino, S.; Laudani, A.; Salerno, N.; Rizzo, S.A. Investigation of SiC MOSFET Body Diode Reverse Recovery and Snappy Recovery Conditions. Energies 2024, 17, 2651. https://doi.org/10.3390/en17112651

Pennisi G, Pulvirenti M, Salvo L, Sciacca AG, Cascino S, Laudani A, Salerno N, Rizzo SA. Investigation of SiC MOSFET Body Diode Reverse Recovery and Snappy Recovery Conditions. Energies. 2024; 17(11):2651. https://doi.org/10.3390/en17112651

Chicago/Turabian StylePennisi, Giuseppe, Mario Pulvirenti, Luciano Salvo, Angelo Giuseppe Sciacca, Salvatore Cascino, Antonio Laudani, Nunzio Salerno, and Santi Agatino Rizzo. 2024. "Investigation of SiC MOSFET Body Diode Reverse Recovery and Snappy Recovery Conditions" Energies 17, no. 11: 2651. https://doi.org/10.3390/en17112651

APA StylePennisi, G., Pulvirenti, M., Salvo, L., Sciacca, A. G., Cascino, S., Laudani, A., Salerno, N., & Rizzo, S. A. (2024). Investigation of SiC MOSFET Body Diode Reverse Recovery and Snappy Recovery Conditions. Energies, 17(11), 2651. https://doi.org/10.3390/en17112651