Universal Input Single-Stage High-Power-Factor LED Driver with Active Low-Frequency Current Ripple Suppressed

Abstract

:1. Introduction

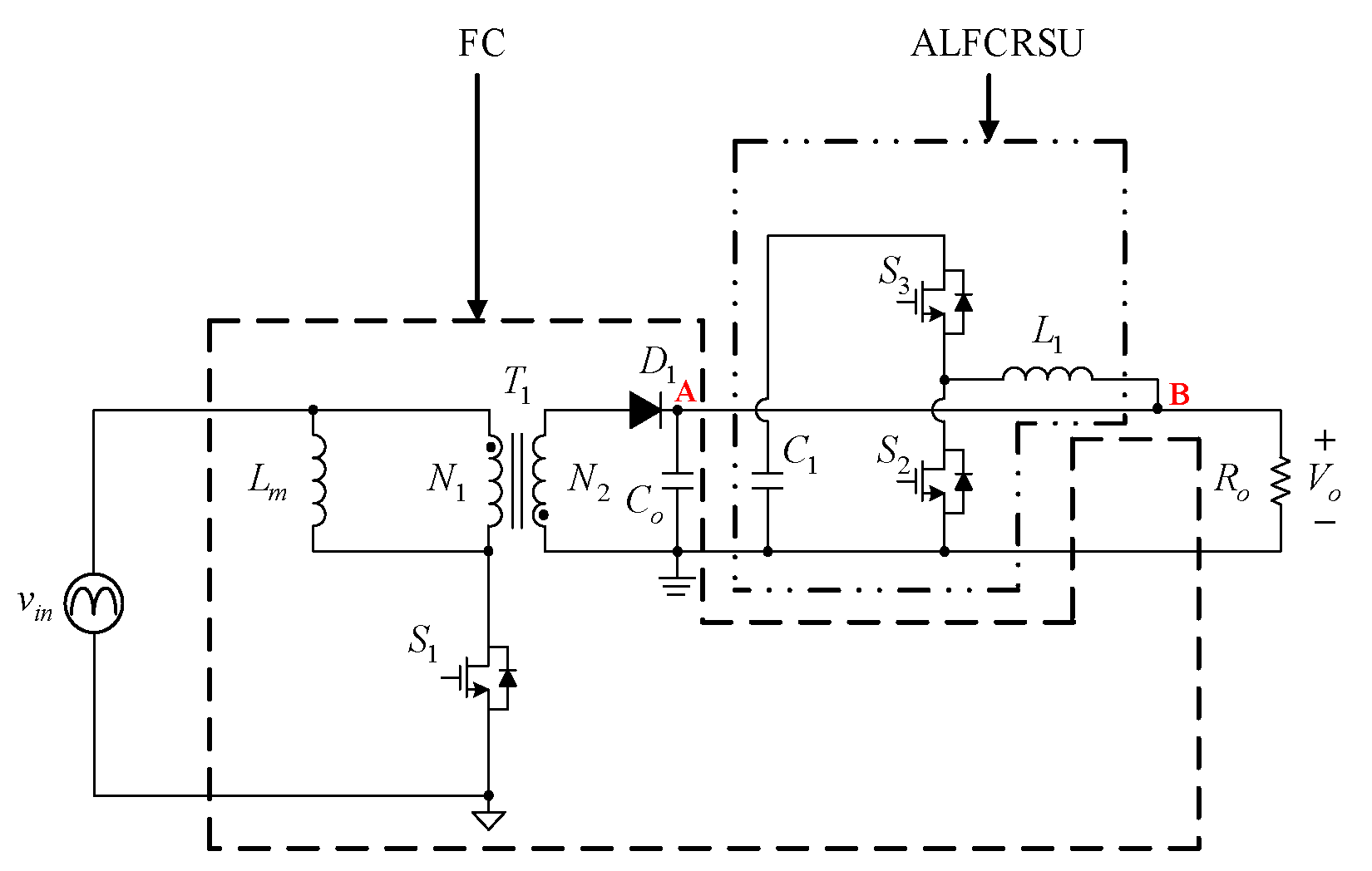

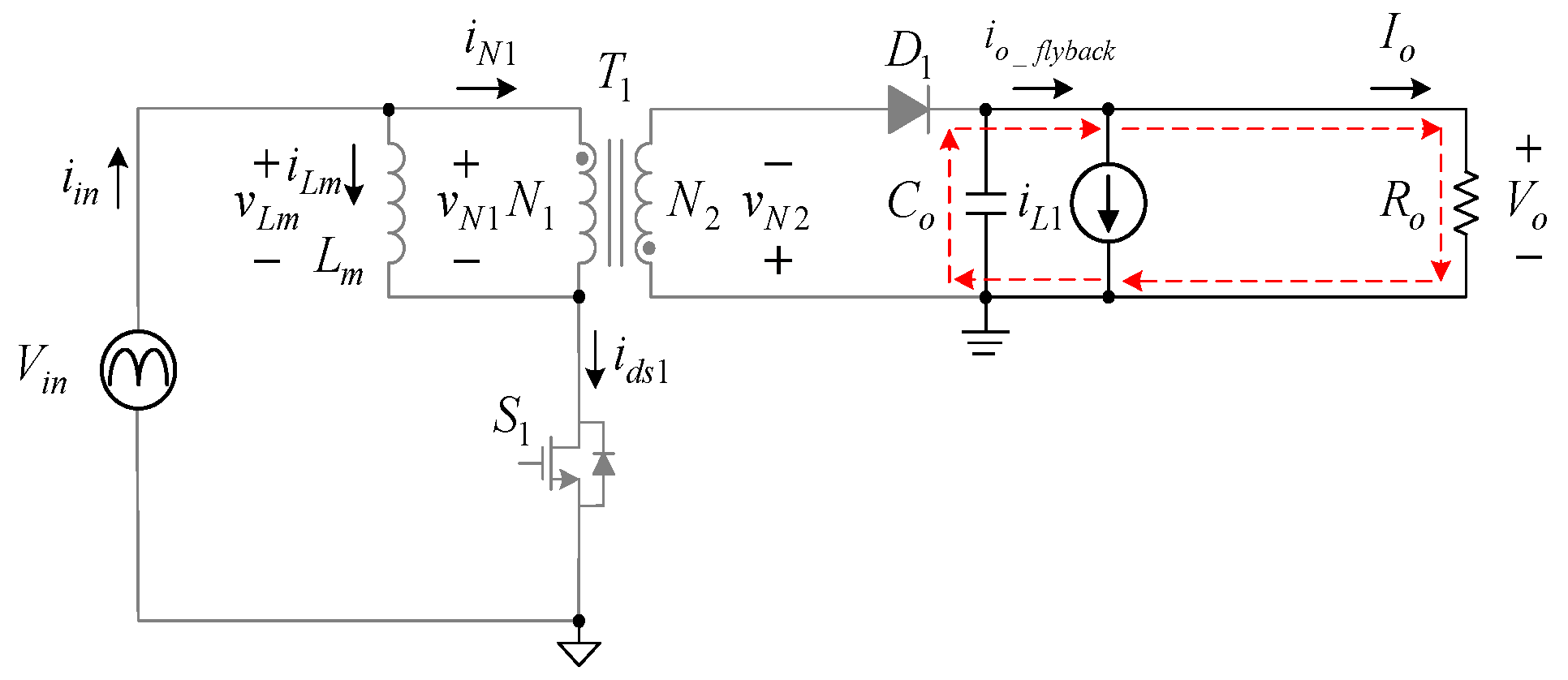

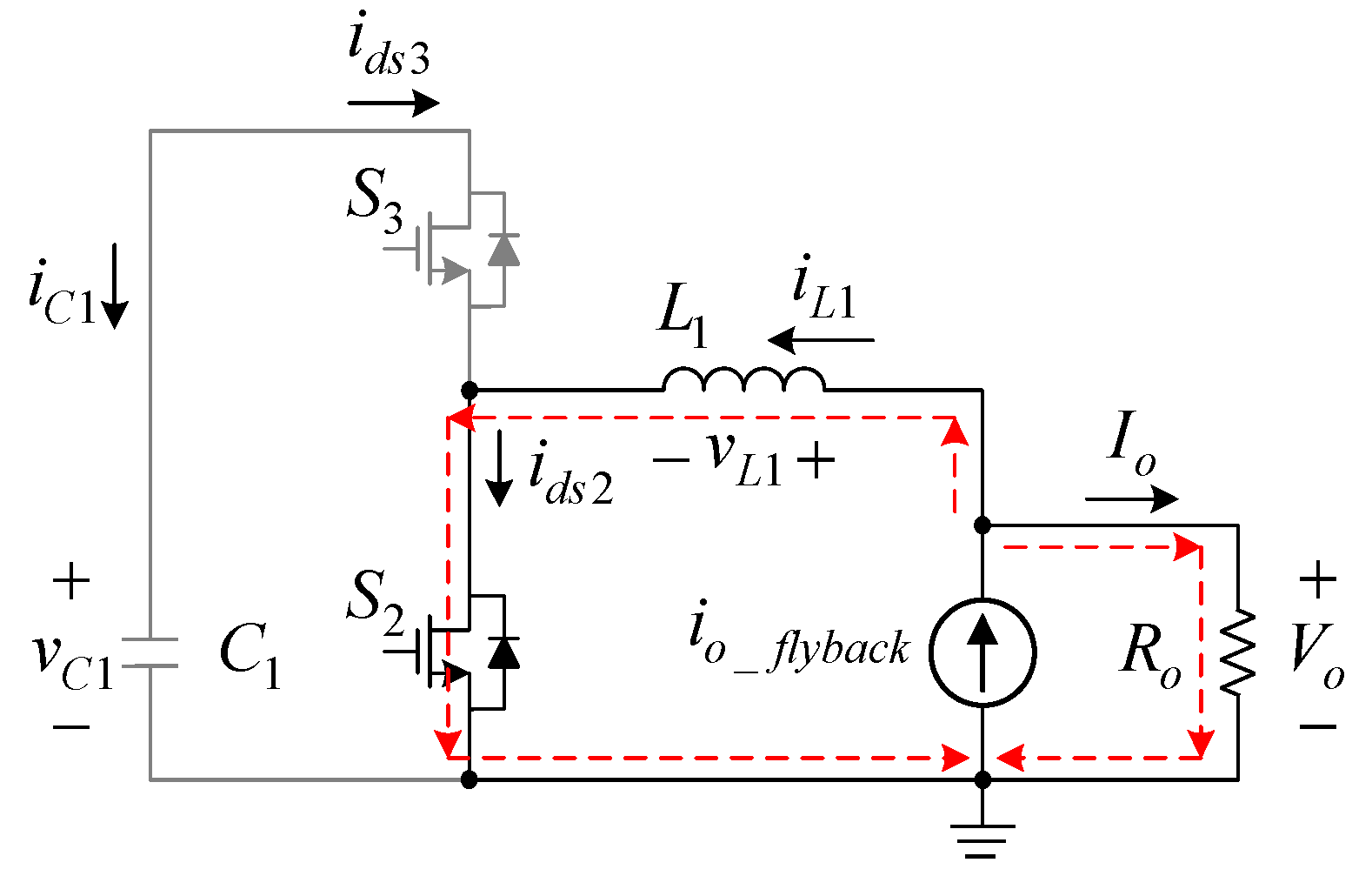

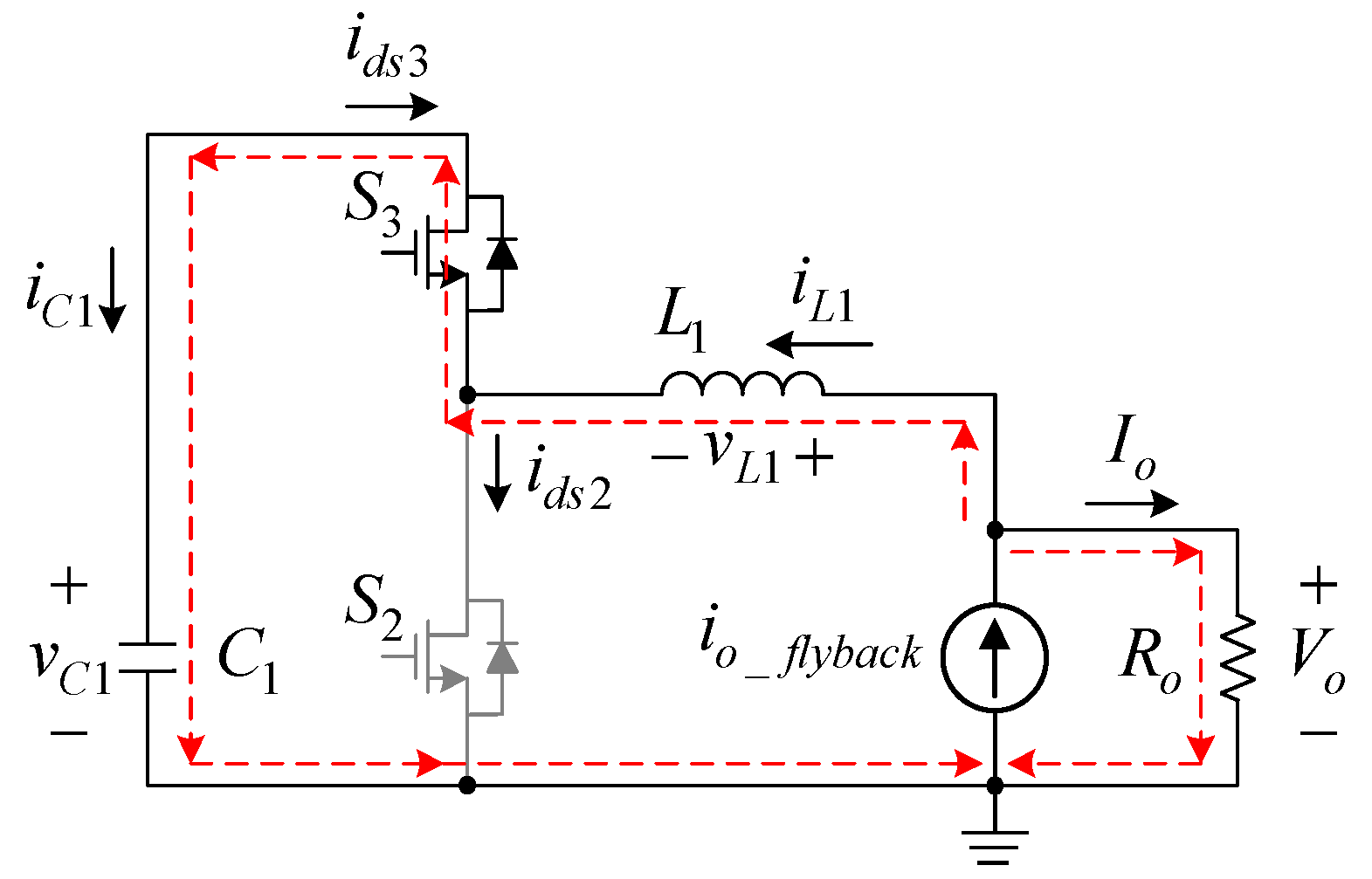

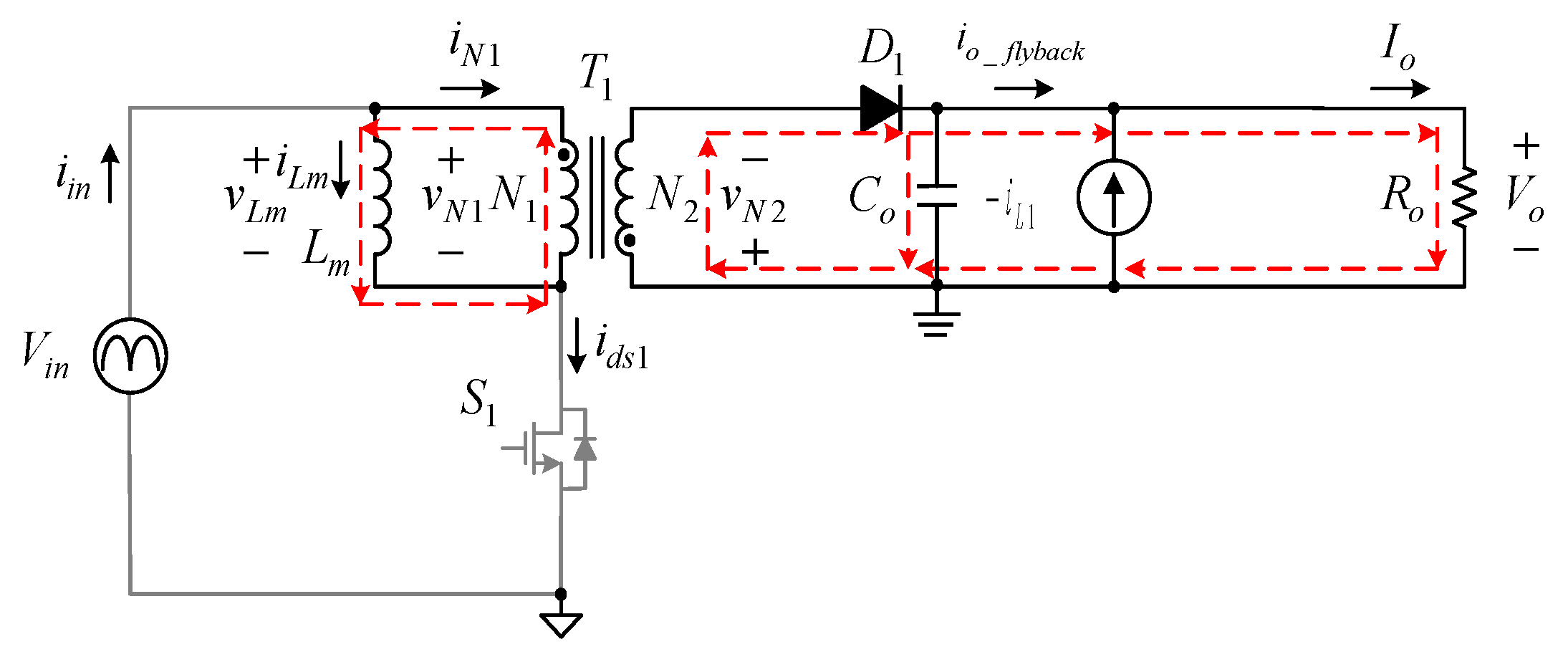

2. Analysis of the Proposed Circuit

- (1)

- vin is the input voltage, Vo is the output voltage, and iin is the input current.

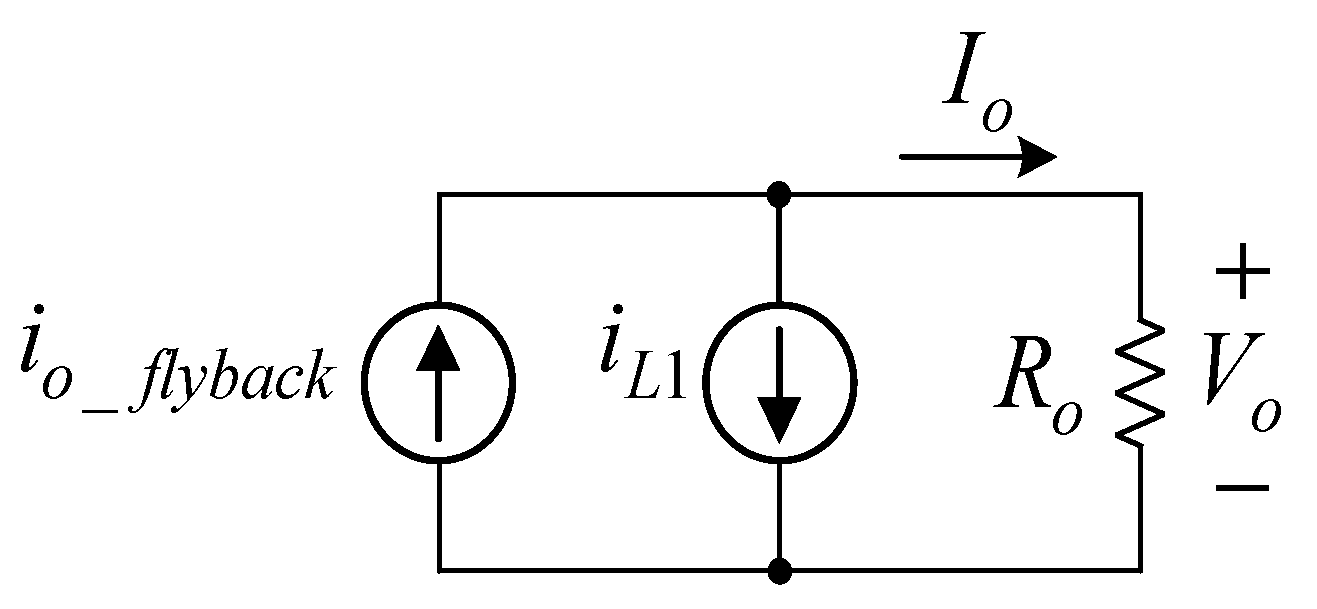

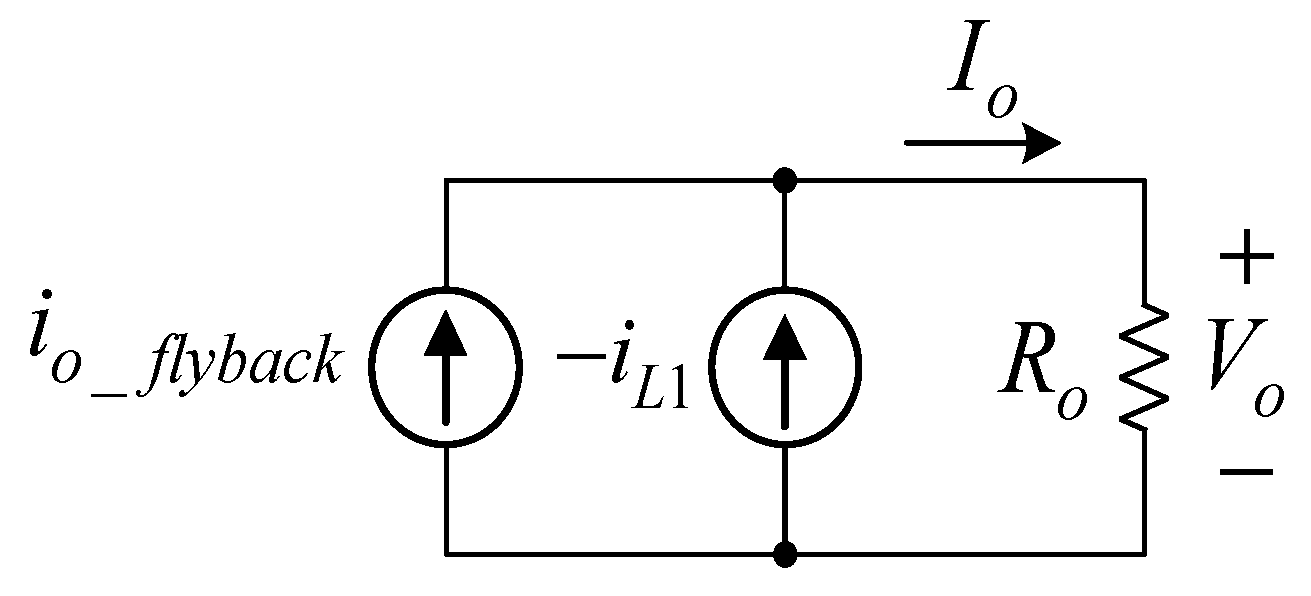

- (2)

- io_flyback is the current flowing from point A to point B, iD1 is the current in the diode D1, ids1 is the current in the switch S1, ids2 is the current in the switch S2, ids3 is the current in the switch S3, iN1 is the current in the coil N1, iLm1 is the current in the magnetizing inductor Lm, iL1 is the current in the inductor L1, iC1 is the current in the capacitor C1, and Io is the current flowing through the output resistor Ro.

- (3)

- vLm is the voltage across the magnetizing inductor Lm, vN1 is the voltage across the coil N1, vN2 is the voltage across the coil N2, vL1 is the voltage across the inductor L1, and vC1 is the voltage across the capacitor C1.

- (1)

- The small-ripple approximation method is used for analysis in the steady state.

- (2)

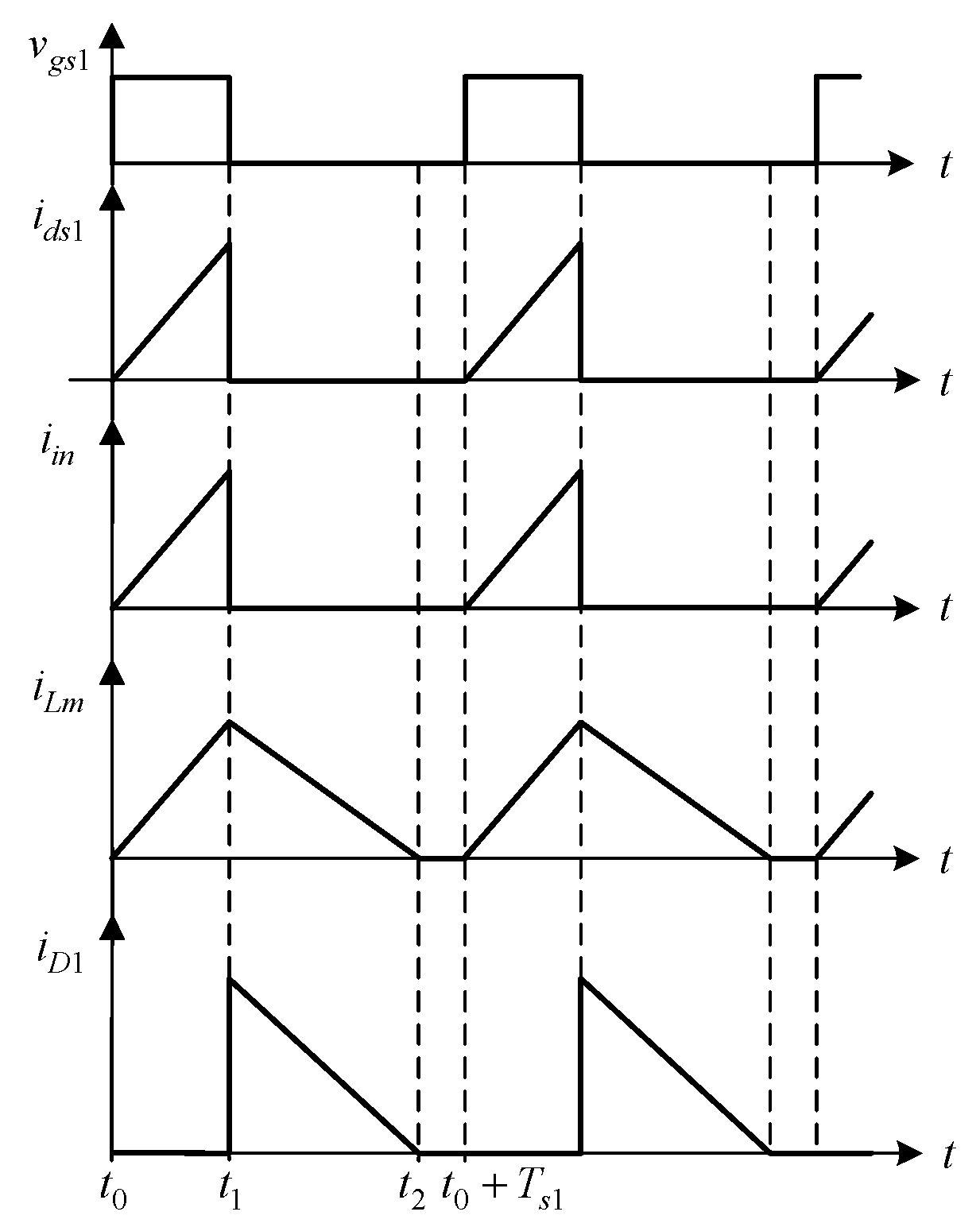

- The FC operates in the discontinuous conduction mode (DCM), and the ALFCRSU operates in the continuous conduction mode (CCM).

- (3)

- The switching period is Ts1, the on-time of the switch S1 is Dx1Ts1, the cutoff time of the switch S1 is (1 − Dx1)Ts1, the switching period of the switches S2 and S3 is Ts2, the on-time of the switch S2 and the cutoff time of the switch S3 are DyTs2, the cutoff time of the switch S2 and the on-time of the switch S3 are (1 − Dy)Ts2; Ts1 is much larger than Ts2, and the blanking time is neglected.

- (4)

- The FC and the ALFCRSU are independent of each other in terms of operation timing, so they can be analyzed separately.

- (5)

- The switches are regarded as ideal.

- (6)

- The inductor L1, the coupled inductor T1, and the capacitors Co and C1 are not considered for their parasitic resistance.

- (7)

- The value of the output capacitor Co is large enough to keep the voltage across it at a constant value, Vo.

- (8)

- The coupling coefficient of the couped inductor T1 is one, i.e., leakage inductances are not considered.

- (9)

- Since the switching frequency is much larger than the line frequency, vin can be considered a DC value over one or more switching periods. The proposed ALFCRSU has two operating states over the line radian frequency ωL, as shown in Figure 3. In addition, state I occurs when the ALFCRSU stores energy, whereas state II occurs when the ALFCRSU releases energy.

- (10)

- The proposed FC and ALFCRSU both operate under negative feedback current control.

- (11)

- The load current is defined as Io.

2.1. ALFCRSU Operating Concept

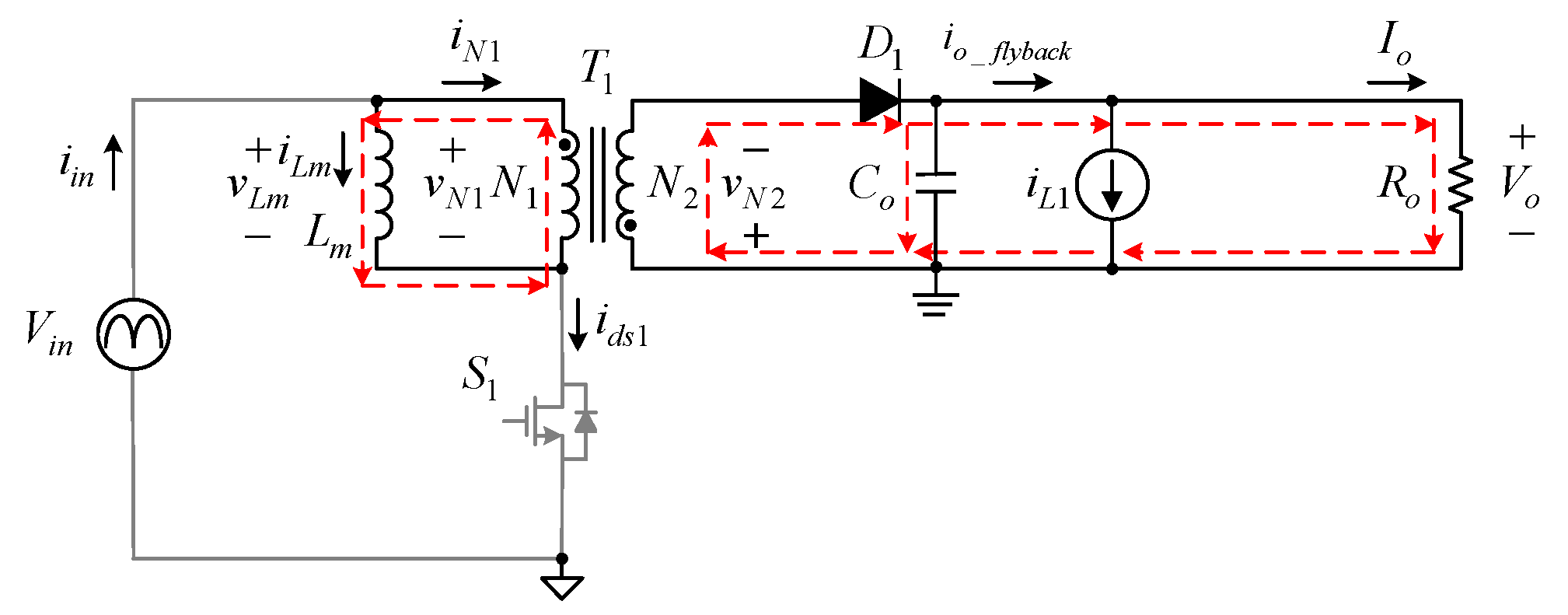

2.2. Operating Behavior of FC and ALFCRSU in State I

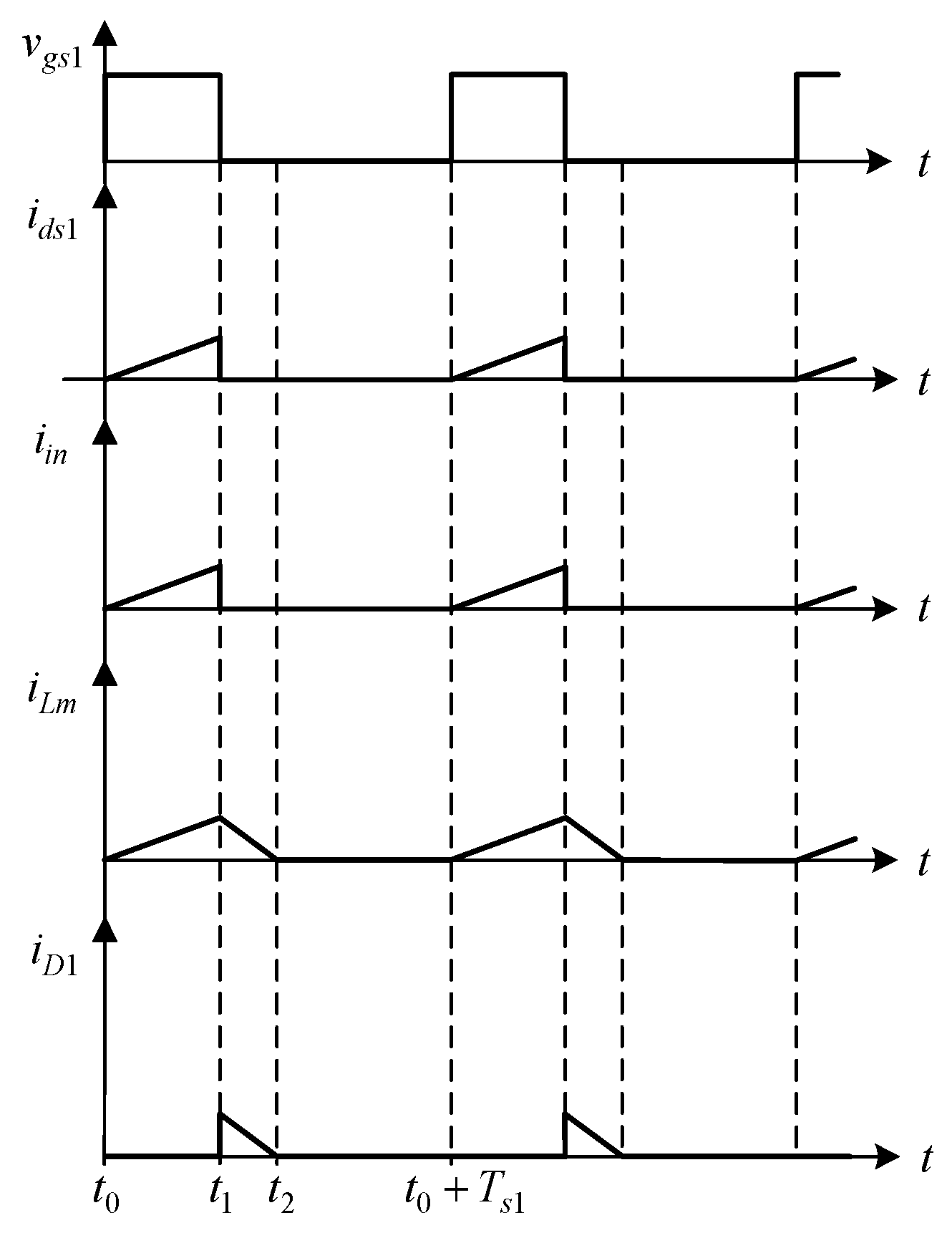

2.2.1. FC Operating Principle in State I

Mode 1: [t0 ≤ t ≤ t1]

Mode 2: [t1 ≤ t ≤ t2]

Mode 3: [t2 ≤ t ≤ t0 + Ts]

Voltage Gain of the FC in State I

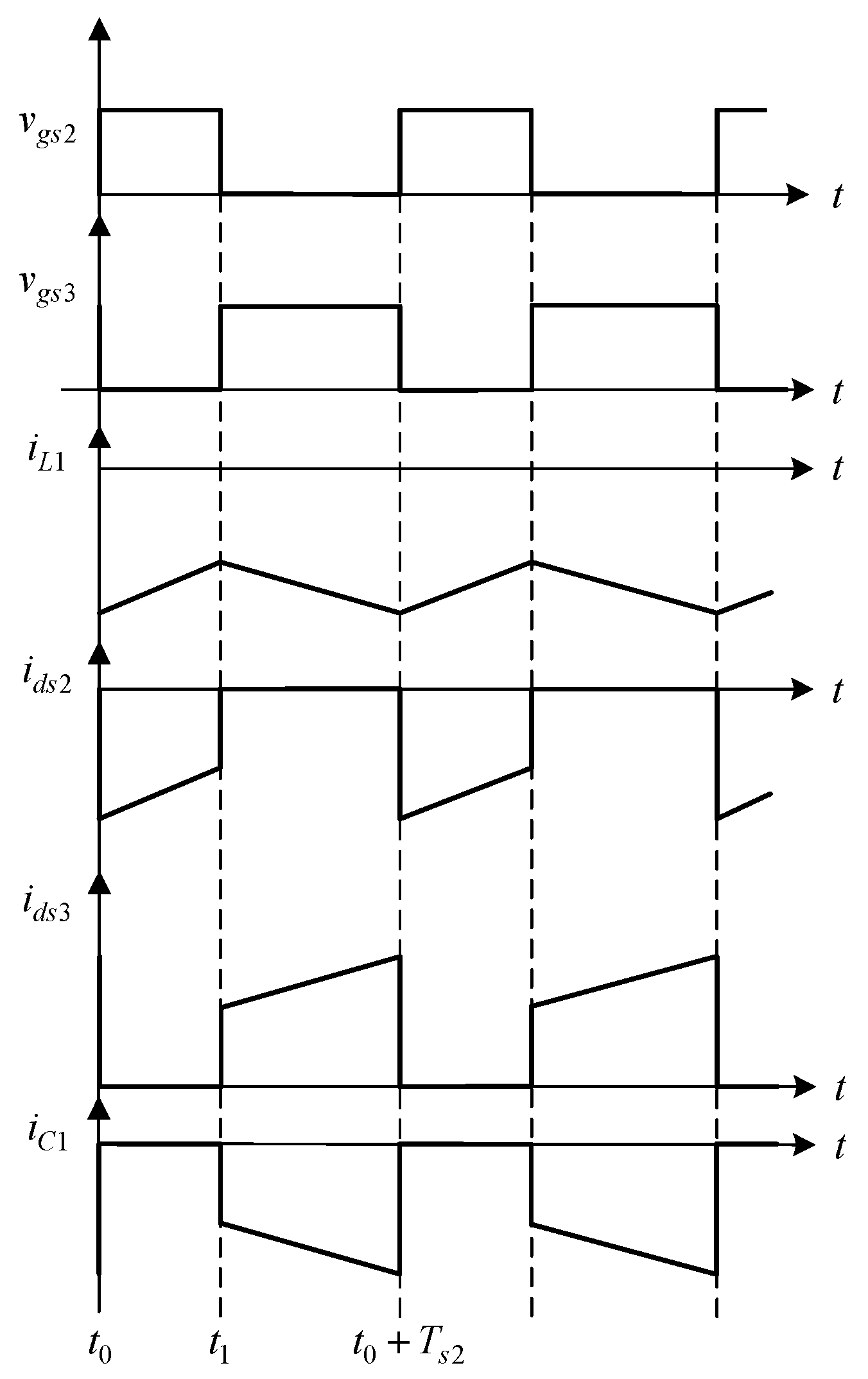

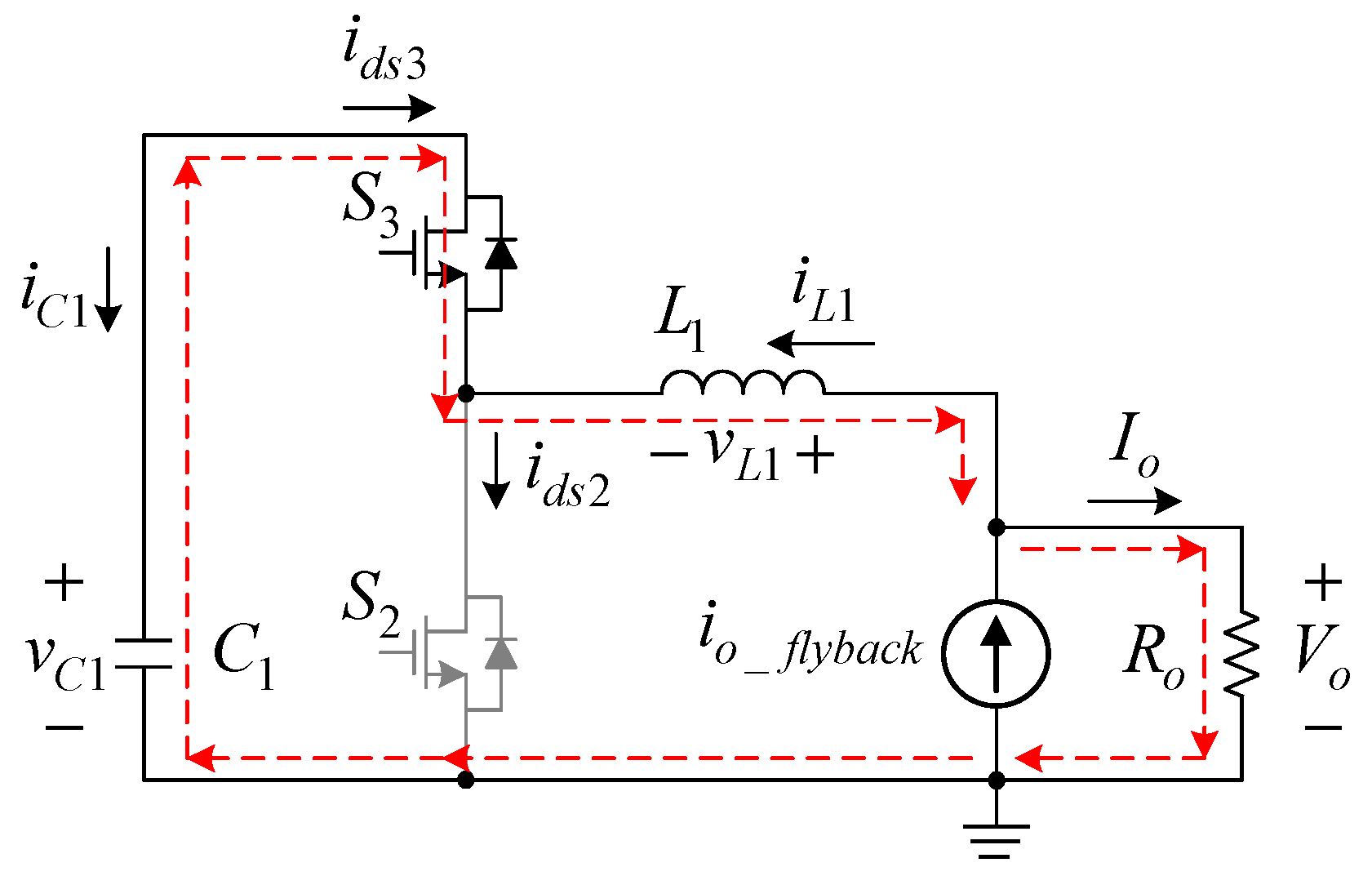

2.2.2. ALFCRSU Operating Principle in State I

Mode 1: [t0 ≤ t ≤ t1]

Mode 2: [t1 ≤ t ≤ t0 + Ts]

Voltage Gain of the ALFCRSU in State I

2.3. Operating Behavior of FC and ALFCRSU in State II

2.3.1. FC Operating Principle in State II

Mode 1: [t0 ≤ t ≤ t1]

Mode 2: [t1 ≤ t ≤ t2]

Mode 3: [t2 ≤ t ≤ t0 + Ts]

Voltage Gain of FC in State II

2.3.2. ALFCRSU Operating Principle in State II

Mode 1: [t0 ≤ t ≤ t1]

Mode 2: [t1 ≤ t ≤ t0 + Ts]

Voltage Gain of the ALFCRSU in State II

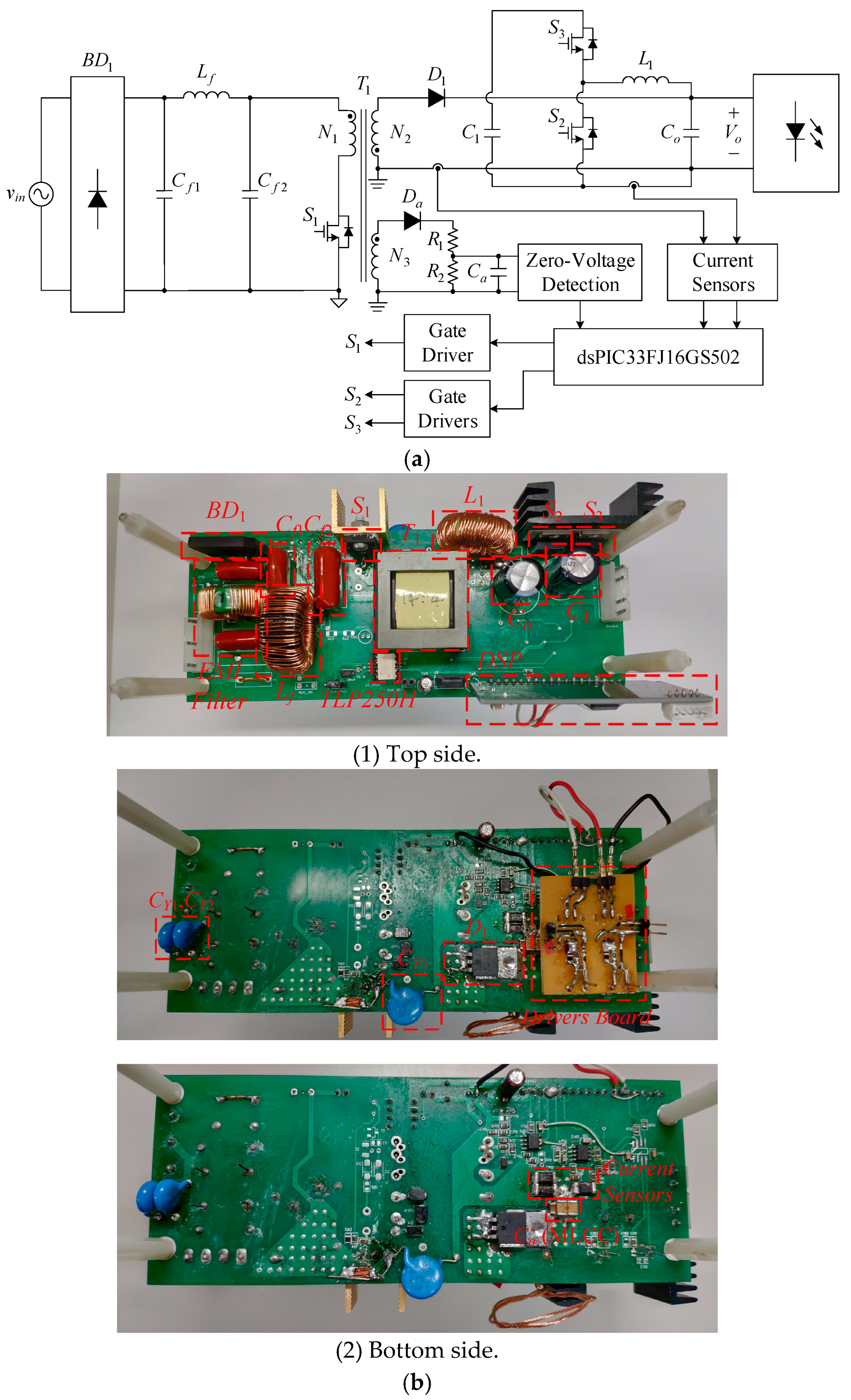

3. System Configuration along with Circuit Component Specifications

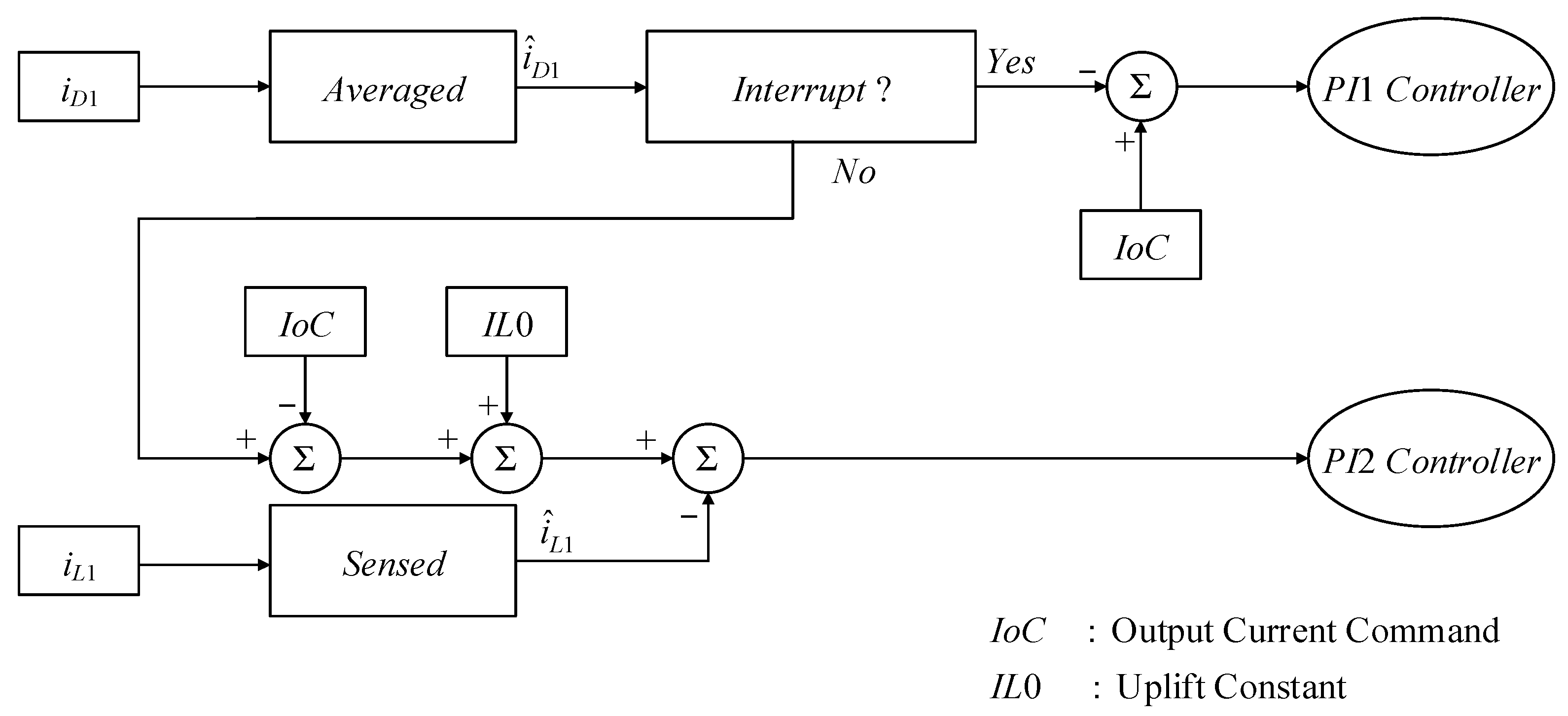

4. Control Strategy

4.1. Input Voltage Waveform Restoration Circuit

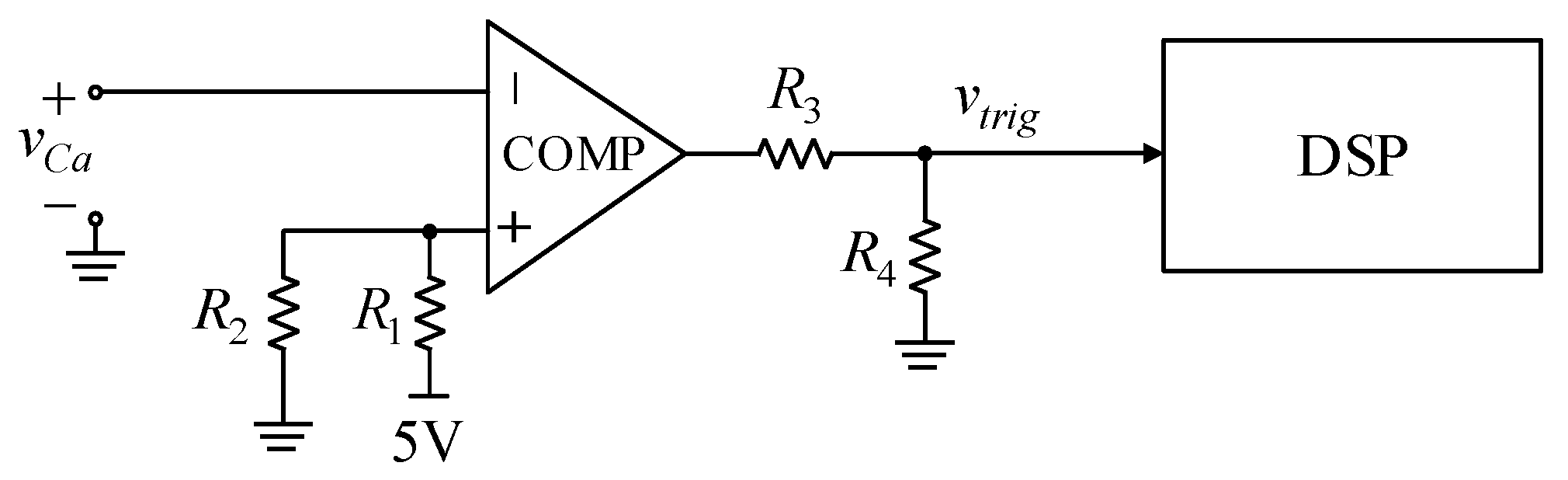

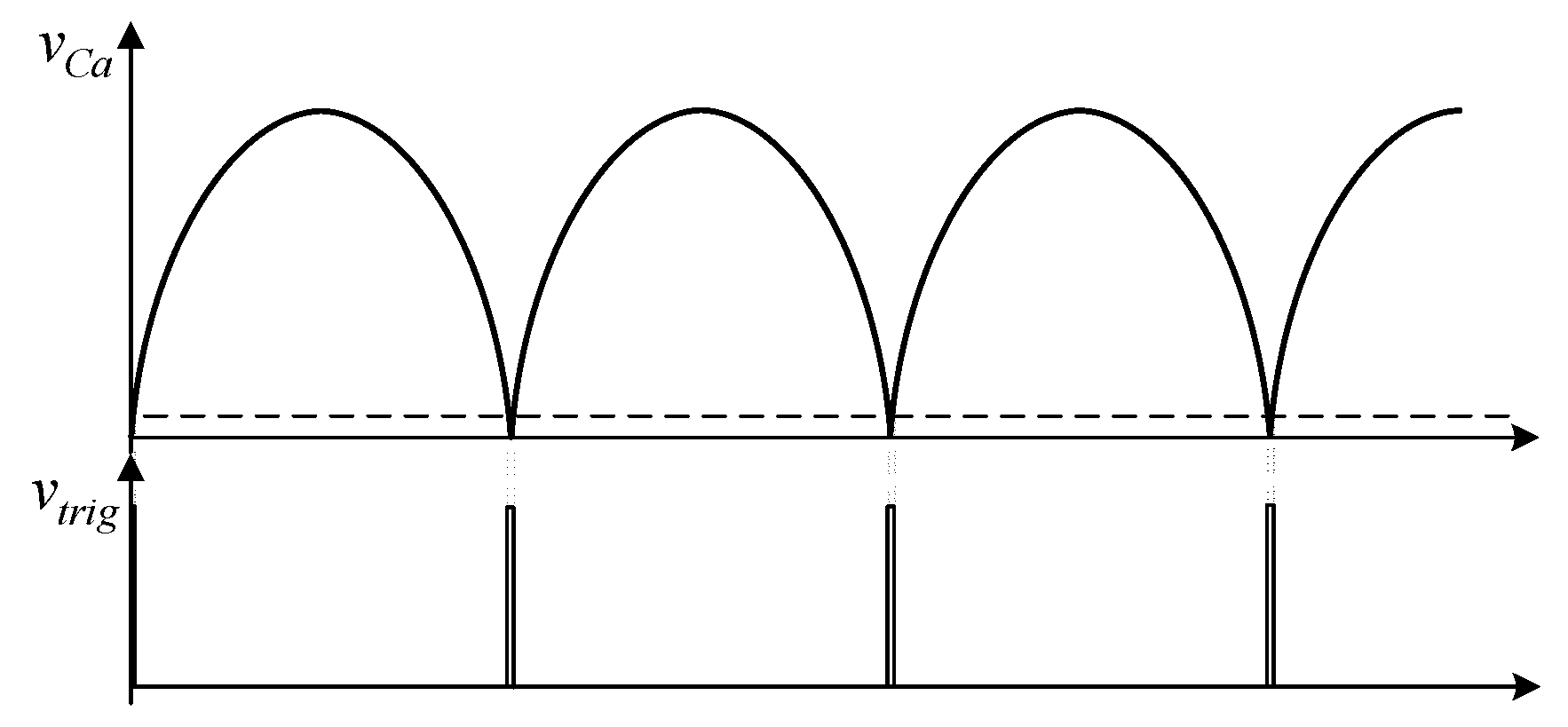

4.2. Zero-Voltage Detection

4.3. Main Program Control Function

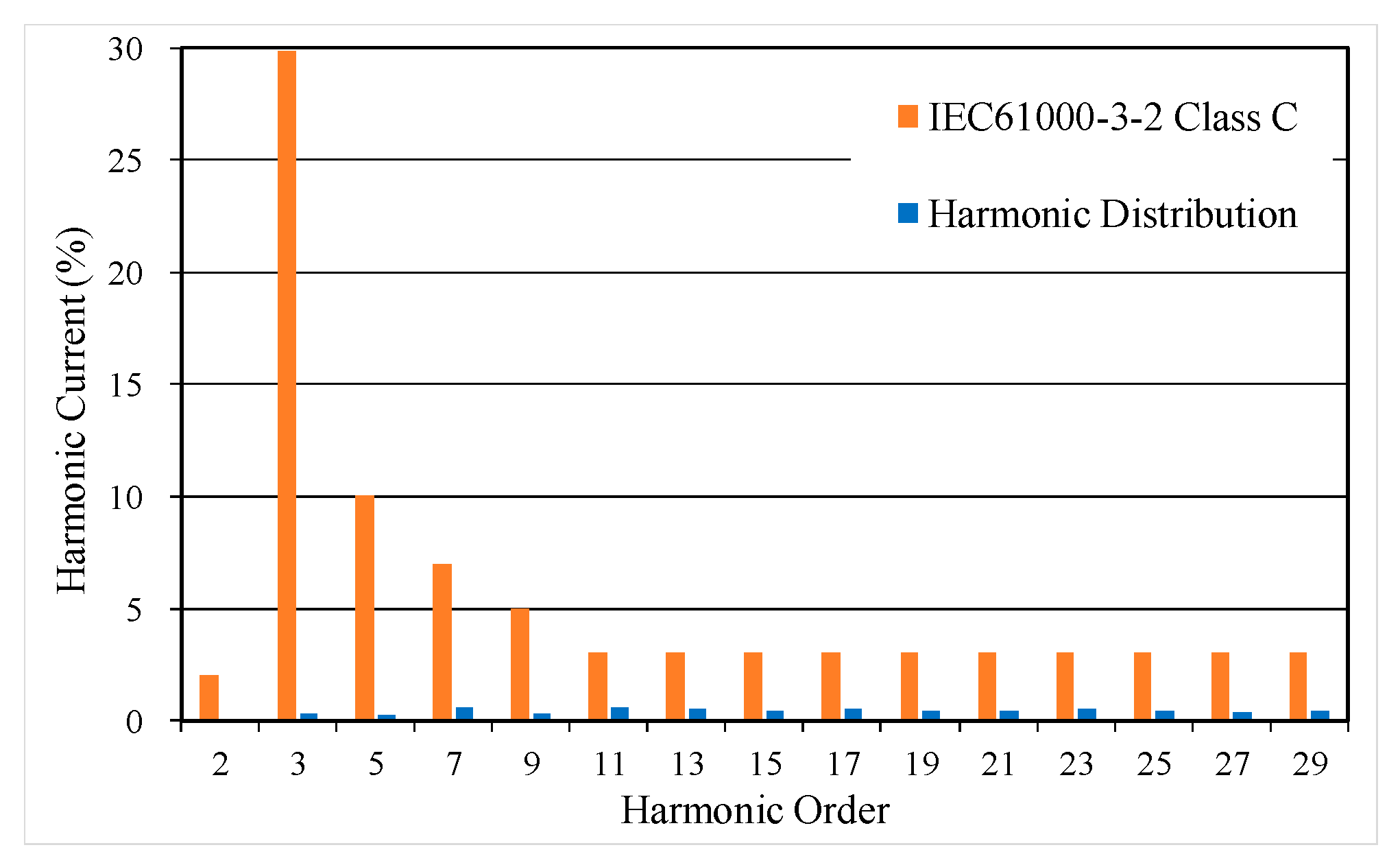

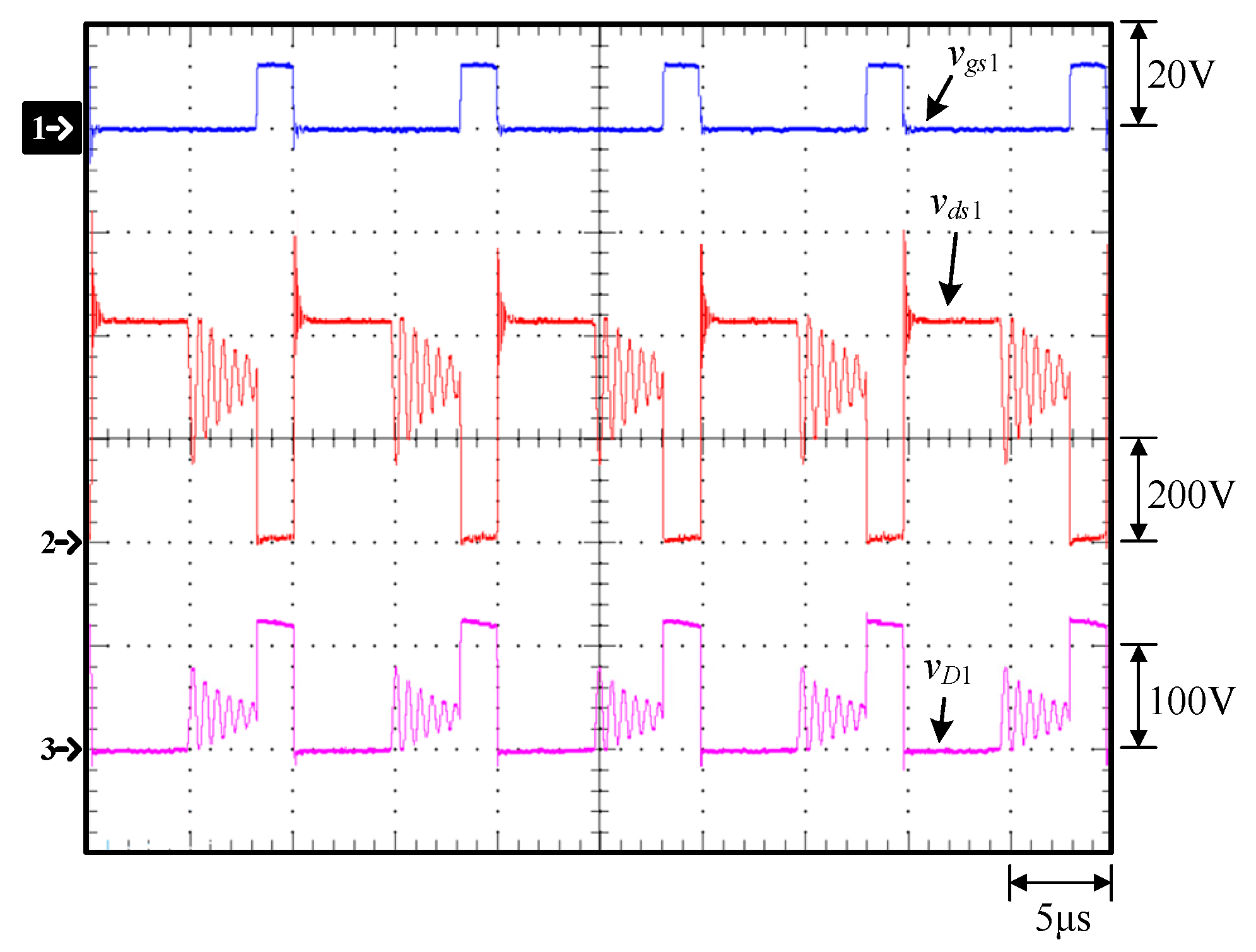

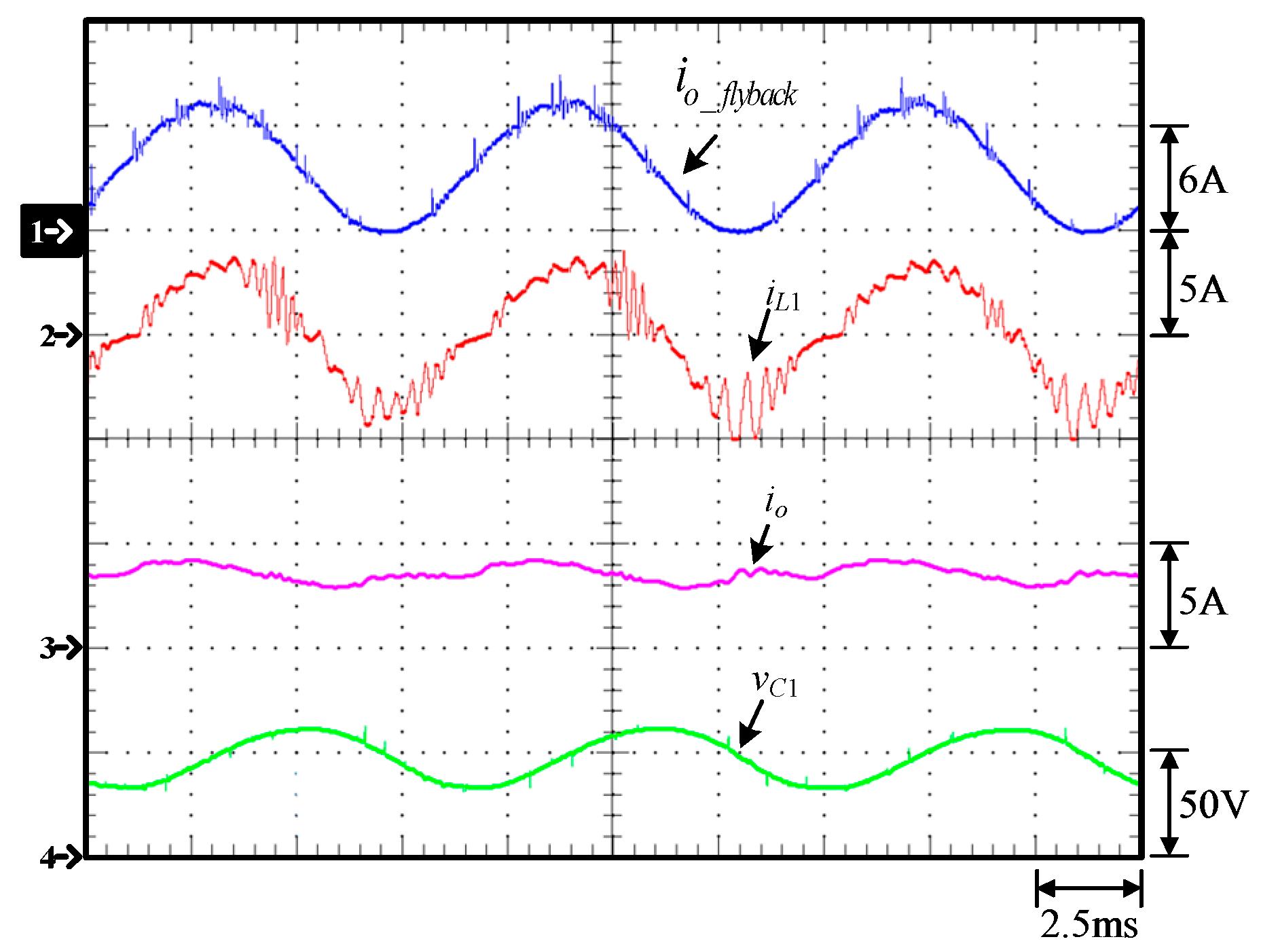

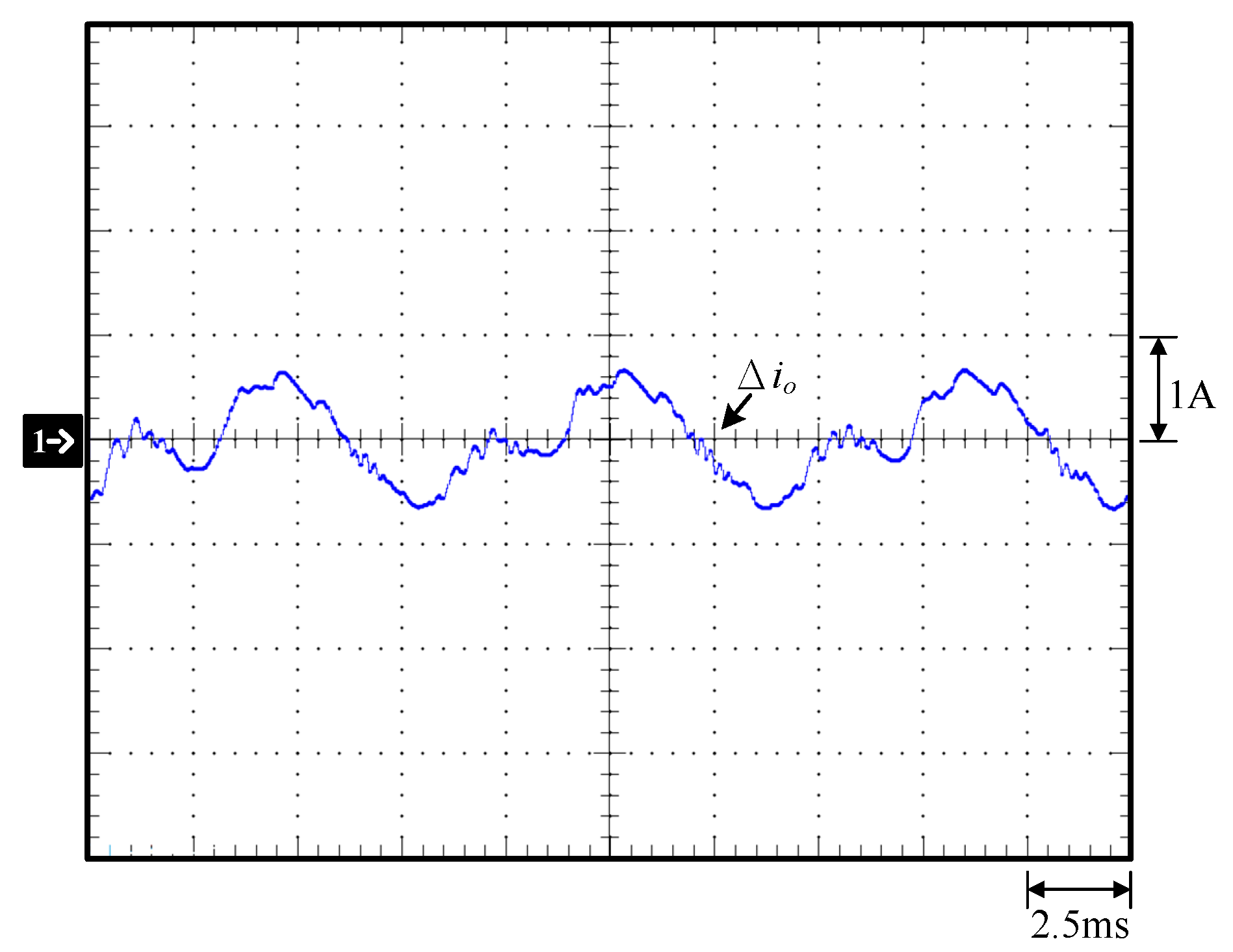

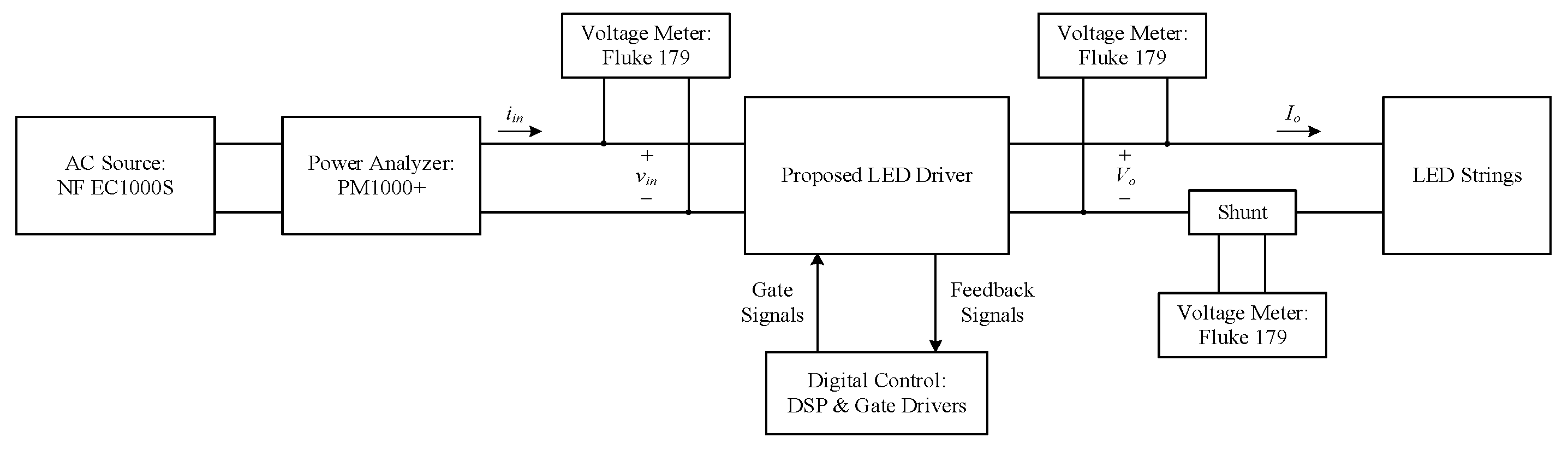

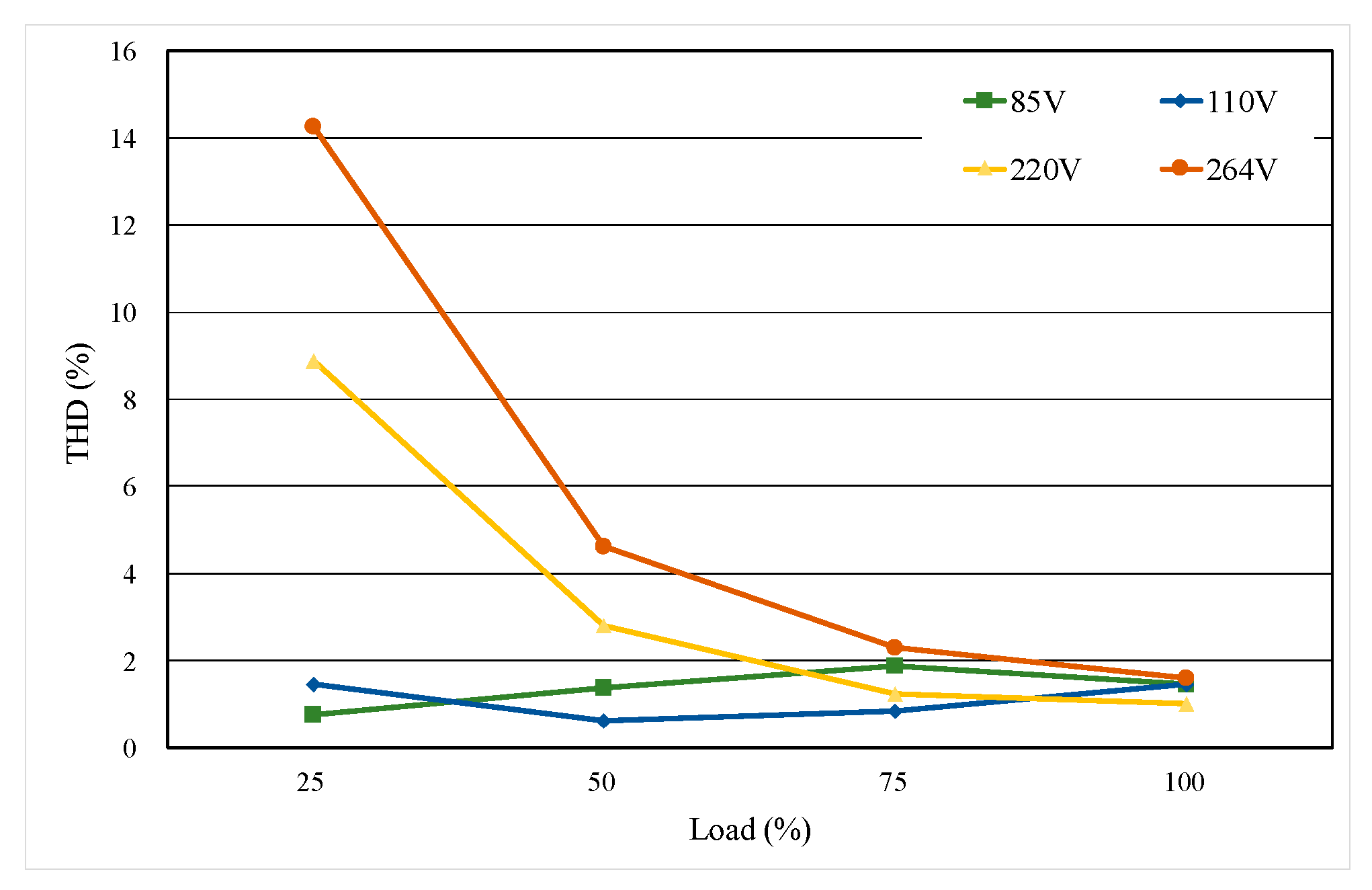

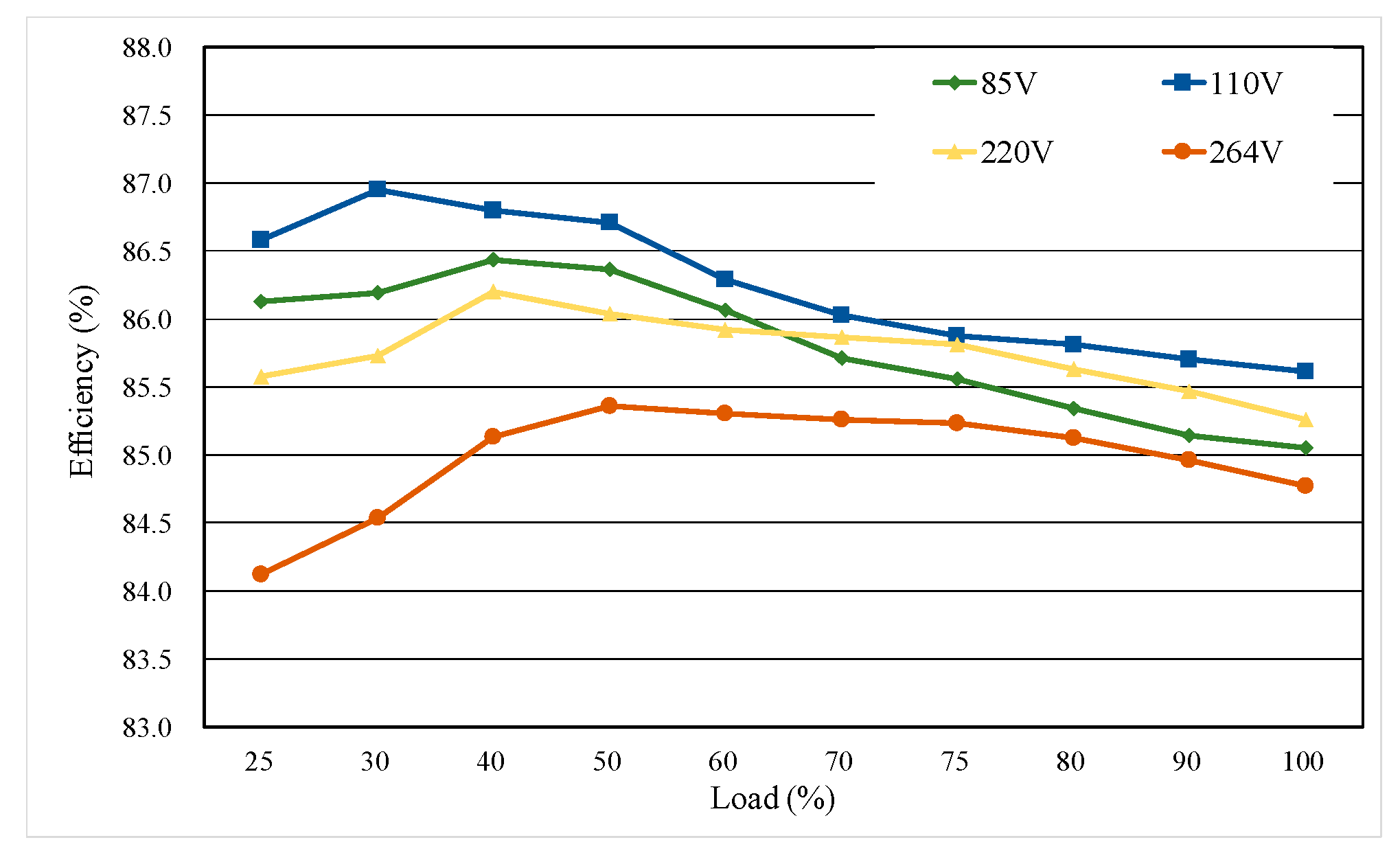

5. Experimental Results

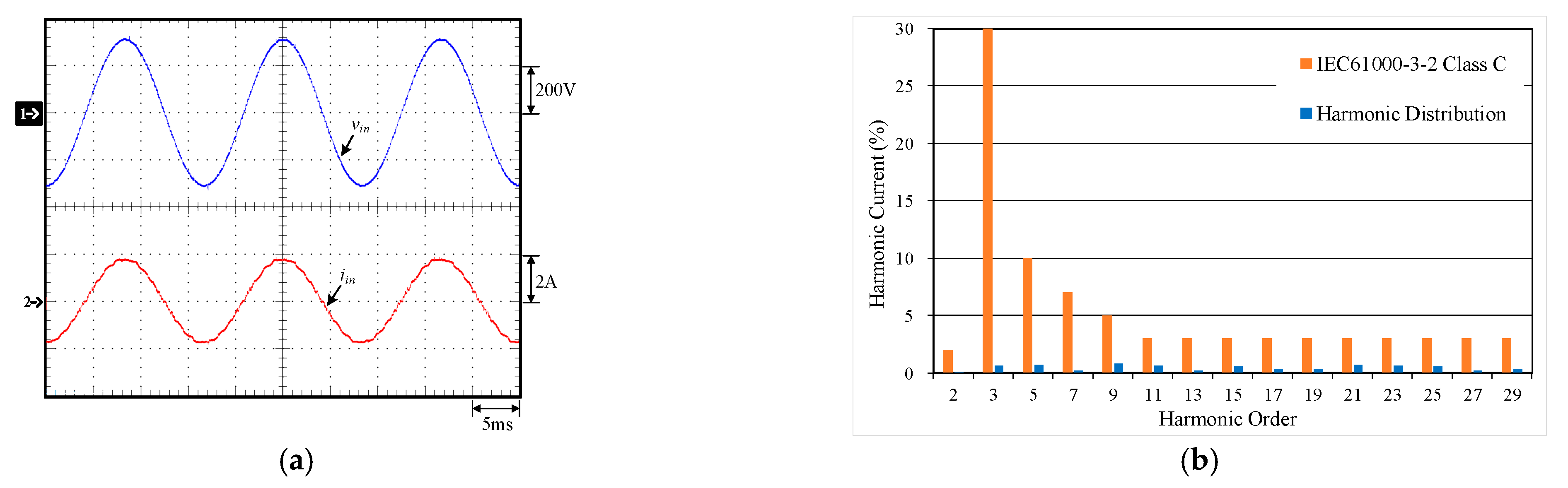

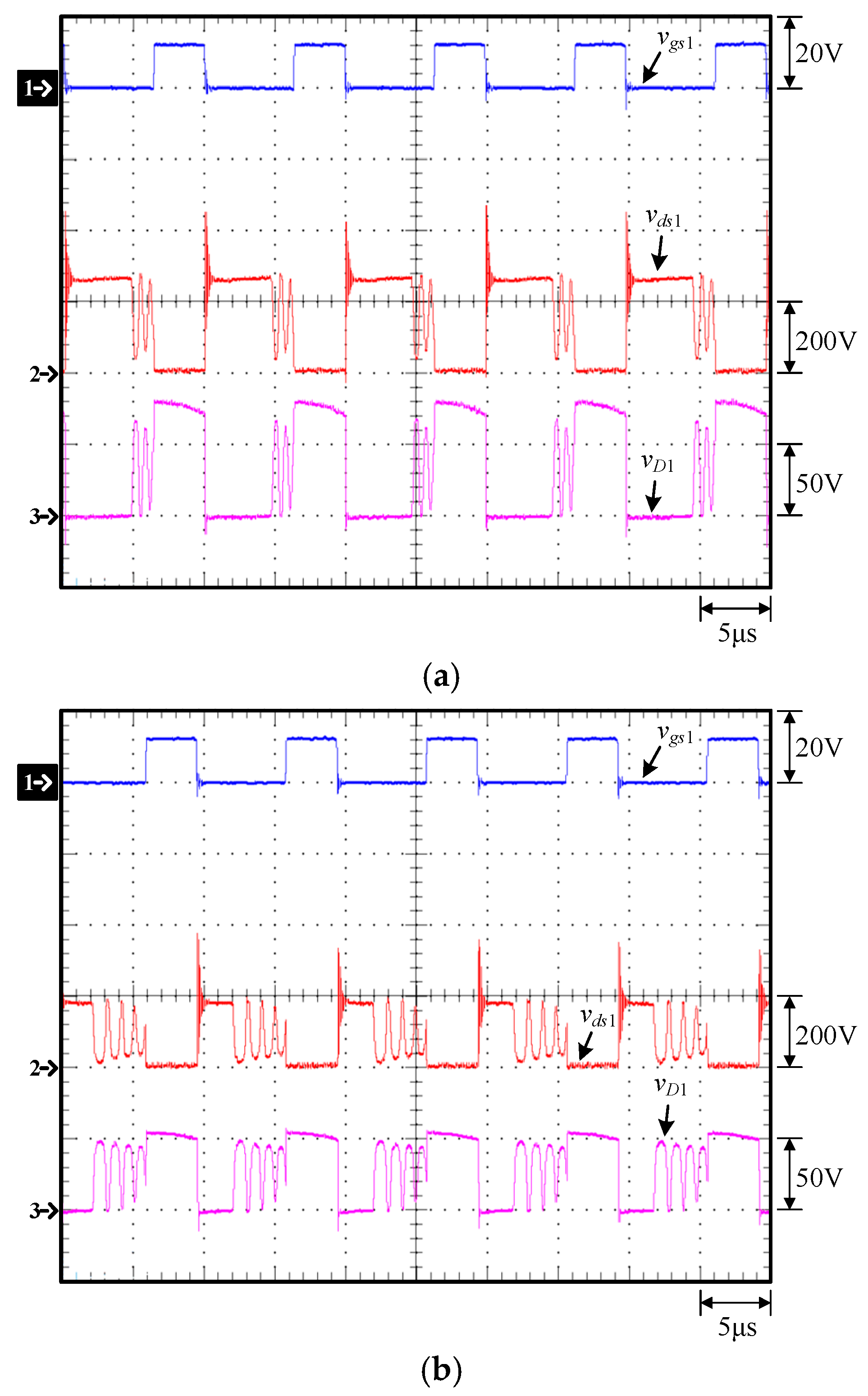

5.1. Input Voltage of 110 V at Rated Load

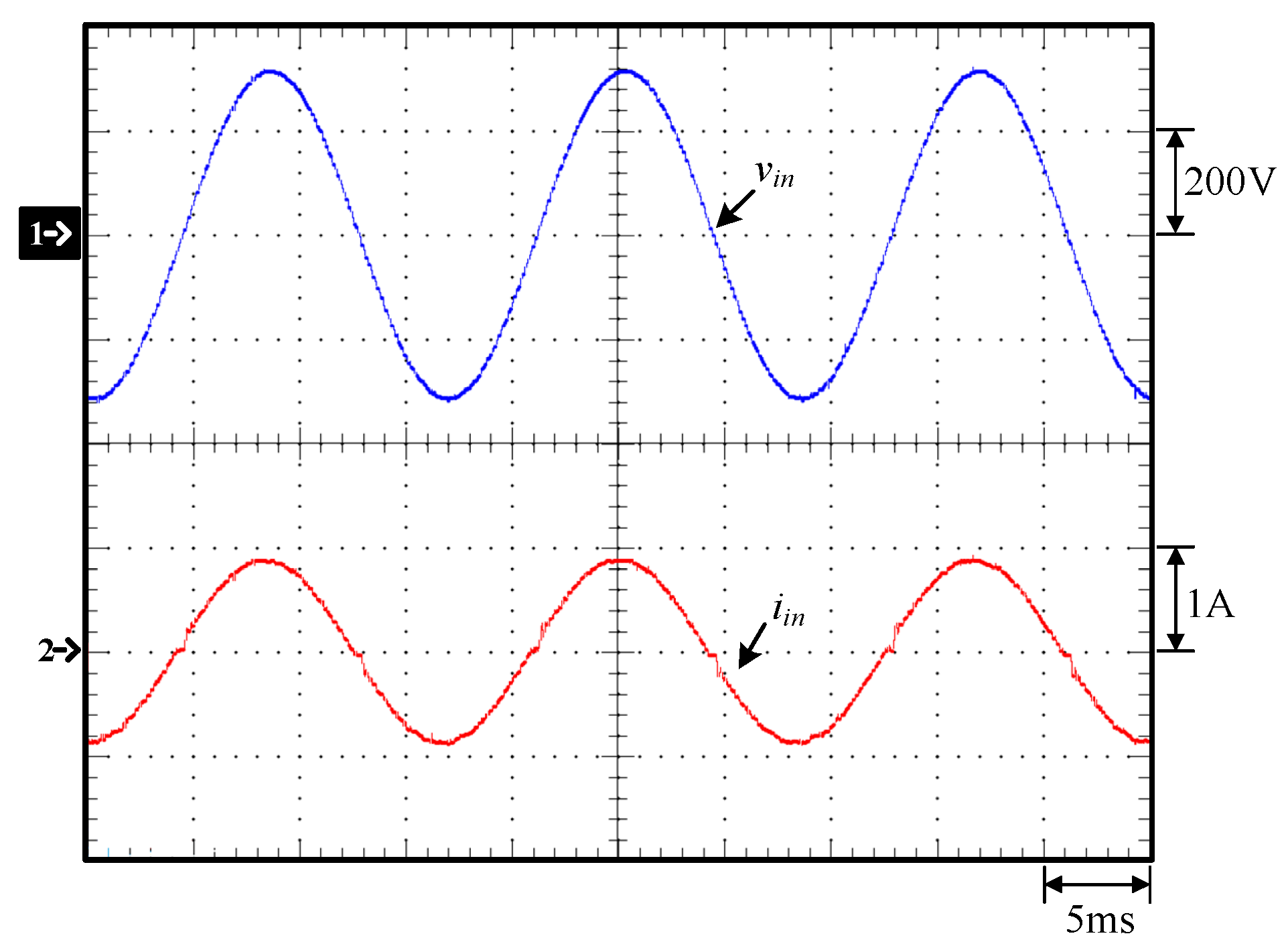

5.2. Input Voltage of 220 V at Rated Load

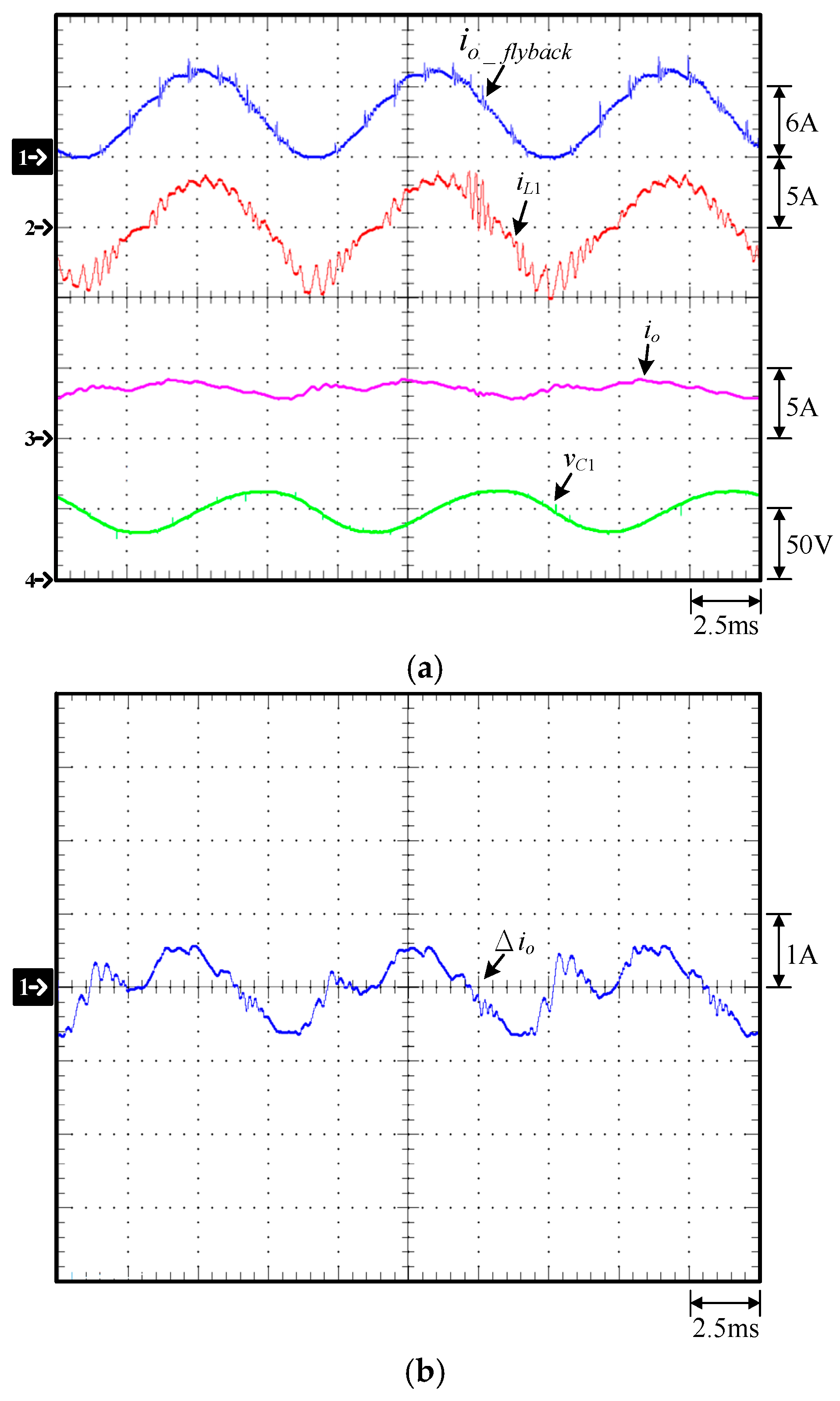

5.3. Output: Current Ripple Suppression

5.4. Other Associated Measurements

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Faizan, M.; Bi, J.; Liu, M.; Wang, L.; Stempitsky, V.; Yousaf, M.Z. Long life power factor corrected LED driver with capacitive energy mechanism for street light applications. Sustainability 2023, 15, 3991. [Google Scholar] [CrossRef]

- Ahn, H.-A.; Seong-Kwan, H.; Oh-Kyong, K. A highly accurate current led lamp driver with removal of low-frequency flicker using average current control method. IEEE Trans. Power Electron. 2018, 33, 8741–8753. [Google Scholar] [CrossRef]

- Ghazali, M.; Adib, E. High performance single stage power factor correction circuit. IET Power Electron. 2022, 15, 145–154. [Google Scholar] [CrossRef]

- Li, Z.; Zhang, Y.; Liu, J.; Wang, Z.; Wu, Y.; Li, N.; Si, J. A second-harmonic suppression method based on differentiated-capacitance design for input-parallel output-series DAB fed single-phase VSI. IEEE Trans. Power Electron. 2022, 37, 11592–11606. [Google Scholar] [CrossRef]

- Mohsen, M.J.E.; Reza, F.M.F.; Beiranvand, B.R. CCM operation of a single-stage boost-flyback converter with active-clamp for LED driver applications. In Proceedings of the 11th Power Electronics, Drive Systems, and Technologies Conference (PEDSTC), Tehran, Iran, 1–4 February 2020. [Google Scholar]

- Satit, M.; Chainarin, E.; Kamon, J.; Phatiphat, T.; Kohji, H.; Marian, K.K. A single-stage LED driver based on ZCDS class-E current-driven rectifier as a PFC for street-lighting applications. IEEE Trans. Power Electron. 2018, 33, 8710–8727. [Google Scholar]

- Kim, H.-C.; Choi, M.C.; Kim, S.; Jeong, D.-K. An AC-DC LED driver with a two-parallel inverted buck topology for reducing the light flicker in lighting applications to low-risk levels. IEEE Trans. Power Electron. 2017, 32, 3879–3891. [Google Scholar] [CrossRef]

- Lee, S.-W.; Do, H.-L. A single-switch AC-DC LED driver based on a boost-flyback PFC converter with lossless snubber. IEEE Trans. Power Electron. 2017, 32, 1375–1384. [Google Scholar] [CrossRef]

- Singh, A.K.; Mishra, A.K.; Gupta, K.K.; Kim, T. Comprehensive review of nonisolated bridgeless power factor. IET Circuits Devices Syst. 2021, 15, 197–208. [Google Scholar] [CrossRef]

- Peng, F.; Samuel, W.; Yang, C.; Yan-Fei, L.; Paresh, C.S. A multiplexing ripple cancellation LED driver with true single-stage power comversion and flicker-free operation. IEEE Trans. Power Electron. 2019, 34, 10105–10120. [Google Scholar]

- Yang, P.; Cao, J.; Shang, Z.; Cai, Y.; Xu, J. Double-line frequency ripple suppression of a quasi-single stage AC-DC converter. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 2074–2078. [Google Scholar] [CrossRef]

- Valipour, H.; Rezazadeh, G.; Zolghadri, M.R. Flicker-free electrolytic capacitor-less universal input offline LED driver with PFC. IEEE Trans. Power Electron. 2016, 31, 6553–6561. [Google Scholar] [CrossRef]

- Qiu, Y.; Wang, L.; Wang, H.; Liu, Y.-F.; Sen, P.C. Bipolar ripple cancellation method to achieve single-stage electrolytic-capacitor-less high-power LED driver. IEEE J. Emering Sel. Top. Power Electron. 2015, 3, 698–713. [Google Scholar]

- Hao, W.; Siu-Chung, W.; Chi, K.T. A PFC single-coupled-inductor multiple-output LED driver without electrolytic capacitor. IEEE Trans. Power Electron. 2019, 34, 1709–1725. [Google Scholar]

- Hao, W.; Siu-Chung, W.; Chi, K.T. A more efficient PFC sigle-couple-inductor multiple-output electrolytic capacitor-less LED driver with energy-flow-path optimization. IEEE Trans. Power Electron. 2019, 34, 9052–9066. [Google Scholar]

| Specifications | Values |

|---|---|

| Forward Voltage (VF) | 2.95V~3.85 V |

| DC Operating Current (IF,max) | 400 mA |

| Pulsed Forward Current | 500 mA |

| Junction Temperature | 125 °C |

| Operating Temperature | −40 °C~85 °C |

| Typical Light Flux Output | 100 lm @ 350 mA |

| Specifications | Values |

|---|---|

| Normal Input Voltage (Vin_nor) | 110 Vrms |

| Maximum Input Voltage (Vin_max) | 264 Vrms |

| Minimum Input Voltage (Vin_min) | 85 Vrms |

| Line Frequency (fline) | 60 Hz |

| Rated Output Voltage (Vo_rated) | 34.5 V (=3.45 V × 10) |

| Rated Output Current (Io_rated) | 350 mA × 10 = 3.5 A |

| System Operation Mode | DCM |

| Switching Frequency (fs1) for FC | 100 kHz |

| Switching Frequency (fs2) for ALFCRSU | 200 kHz |

| LED Specifications | VF = 3.45 V, IF = 0.35 A (Rated Load) VF = 2.9 V, IF = 87.5 mA (Light Load) |

| Number of LEDs on the LED String | 10 |

| Components | Specifications |

|---|---|

| BD1 | T8KB60 |

| S1 | SPA20N60C |

| S2, S3 | SUP85N10 |

| D1 | SBR30300CT |

| Cf1 | 0.1 μF Film Capacitor |

| Cf2 | 0.47 μF Film Capacitor |

| C1 | 220 μF Electrolytic Capacitor |

| Co | 141 μF Multi-Layer Ceramic Capacitor |

| 470 μF Electrolytic Capacitor | |

| T1 | Core: LP3320, Lm = 61.22 μH, n = 3.5 |

| L1 | Core: T94-52 64 μH |

| Lf | Core: T106-45, 800 μH |

| Isolated Gate Drivers | TLP250H |

| Output Current | Suppression | No Suppression | ||

|---|---|---|---|---|

| 110 V | 220 V | 110 V | 220 V | |

| 0.88 A (25%) | 1.73 A | 1.75 A | 0.73 A | 0.8 A |

| 1.75 A (50%) | 3.5 A | 3.55 A | 0.83 A | 1.01 A |

| 3.5 A (100%) | 6.9 A | 6.8 A | 1.2 A | 1.33 A |

| Output Current | 110 V | 220 V |

|---|---|---|

| 0.88 A (25% Load) | 57.8% | 54.3% |

| 1.75 A (50% Load) | 78.29% | 71.55% |

| 3.5 A (100% Load) | 82.61% | 80.44% |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hwu, K.-I.; Shieh, J.-J.; Lin, C.-T. Universal Input Single-Stage High-Power-Factor LED Driver with Active Low-Frequency Current Ripple Suppressed. Energies 2024, 17, 183. https://doi.org/10.3390/en17010183

Hwu K-I, Shieh J-J, Lin C-T. Universal Input Single-Stage High-Power-Factor LED Driver with Active Low-Frequency Current Ripple Suppressed. Energies. 2024; 17(1):183. https://doi.org/10.3390/en17010183

Chicago/Turabian StyleHwu, Kuo-Ing, Jenn-Jong Shieh, and Chien-Ting Lin. 2024. "Universal Input Single-Stage High-Power-Factor LED Driver with Active Low-Frequency Current Ripple Suppressed" Energies 17, no. 1: 183. https://doi.org/10.3390/en17010183

APA StyleHwu, K.-I., Shieh, J.-J., & Lin, C.-T. (2024). Universal Input Single-Stage High-Power-Factor LED Driver with Active Low-Frequency Current Ripple Suppressed. Energies, 17(1), 183. https://doi.org/10.3390/en17010183