1. Introduction

Wide bandgap semiconductor technology is a very popular and growing technology for numerous industrial applications that require a high power density [

1]. SiC-based semiconductors are especially very common with low drain-source resistance, high thermal conductivity, high blocking voltage, and high switching frequency compared to the old semiconductor technology (Si-based) [

2]. However, it is challenging to replace Si-based power components with SiC ones for every customized application due to the unavailability of a wide range of high-power SiC modules. Paralleling discrete SiC MOSFETs is the critical solution to increasing the power and current capability of customized systems.

MOSFET paralleling seems like a straightforward process. Additionally, the positive temperature characteristic of the on-state resistance of the MOSFET helps to balance the steady-state current of the device. However, it is challenging, especially for high current ratings. Fabrication mismatches (, , etc.), parasitic effects, layout differences, and so forth must be handled to balance the currents of the paralleled MOSFETs, particularly in the transient region. Fabrication mismatches of MOSFETs directly affect the switching action, and any distortion of symmetry of the circuit layout results in different parasitic effects. These differences cause an imbalance in the current sharing of the paralleled MOSFETs, resulting in different losses and thermal imbalances. In addition, the system must be thermally balanced to protect current sharing and system performance. At that point, the increased current capacity provided by paralleling makes thermal problems difficult to solve on the PCB. A laminated busbar can be used to prevent the PCB from carrying a high current, which behaves as a heat sink and releases heat. Although the laminated busbar decreases the inductance of the current path, which reduces the voltage overshoot caused by the switching action, an increase in the switching speed of the SiC MOSFETs can also cause voltage overshoot problems.

Studies have been performed on the current sharing of paralleled MOSFETs, which can be categorized into two groups, passive and active current balancing. In general, active current-balancing methods require high-bandwidth sensors and complex current-balancing circuits. Besides that, passive current balancing methods increase the size of the circuit by adding inductors, capacitors, and chokes acting as passive circuit elements. In Ref. [

3], the current imbalance of two paralleled SiC MOSFETs in the transient switching region was compensated with an active current balancing method. In this method, the difference in unbalanced currents is sensed with a differential current transformer. Sensed unbalance is eliminated by the active gate control circuit. According to its results, this method works fine in the transient region; however, the current balance is more distorted in the steady-state region. Furthermore, paralleling more than two MOSFETs with this method seems more complicated. Instead of using a differential current transformer to measure the difference of the magnitude of unbalance in currents, a planar Rogowski coil-based current sensor was proposed in Ref. [

4]. However, using a current sensor circuit increases the complexity of the system. Moreover, in Ref. [

5], the current sharing of paralleled SiC MOSFET modules is balanced with the active gate driver circuit. The edge and slopes of the drain currents are detected with the help of a voltage of source inductance. The gate driver voltage is dynamically adjusted according to the drain currents. This method provides balanced current sharing between SiC modules after a few switching cycles. However, dynamic control of the gate driver voltage increases the complexity of the circuit. In addition, a detailed analysis is required to detect the edges and slopes of the drain current of the parallel units. A passive transient current balancing circuit is used for three parallel SiC half-bridge units in Ref. [

6]. This circuit provides a current balance, but it increases the size of the circuit by adding an inductor to the power line. Additionally, the effectiveness of that current-balancing circuit in paralleling a discrete SiC MOSFET should be further analyzed because it was found in Ref. [

7] that the parallel half-bridge unit has a smaller current imbalance compared to the paralleling of the die. In another study, Ref. [

8], peak currents of paralleled SiC MOSFETs were balanced with the help of drive-source resistance and coupled power inductors. However, detailed analysis is required to select the effective values of the passive elements. Additionally, these elements increase the size of the circuit. On the other hand, the current balance of the paralleled SiC MOSFETs was provided using only the differential mode choke in Ref. [

9]. This method is successful for current balancing in both transient and steady-state regions. However, adding a differential mode choke to the power line increases the circuit size, and paralleling more than two MOSFETs increases the difficulty of the mechanical implementation of chokes. Furthermore, a detailed analysis is required to determine the properties of the differential-mode choke.

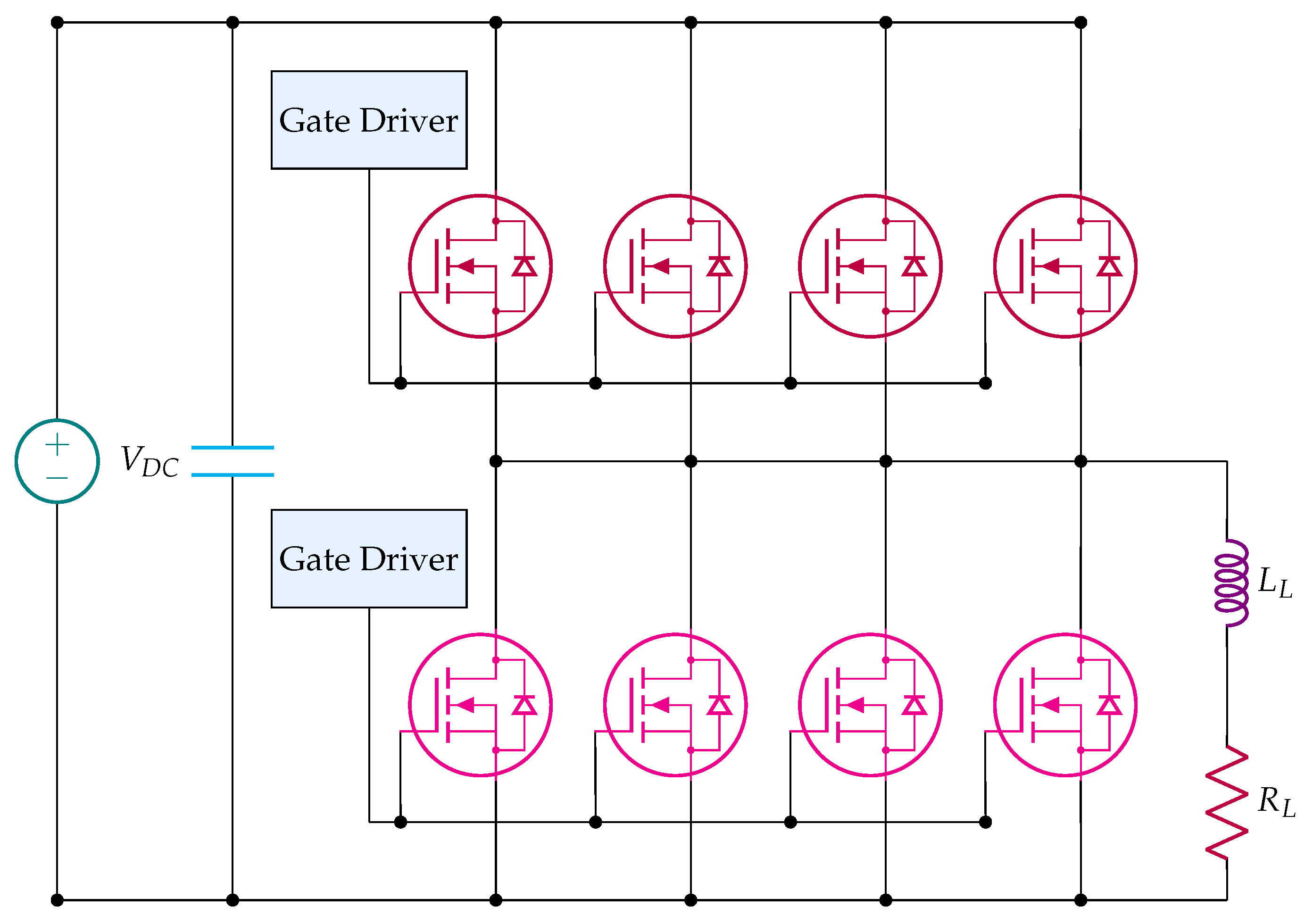

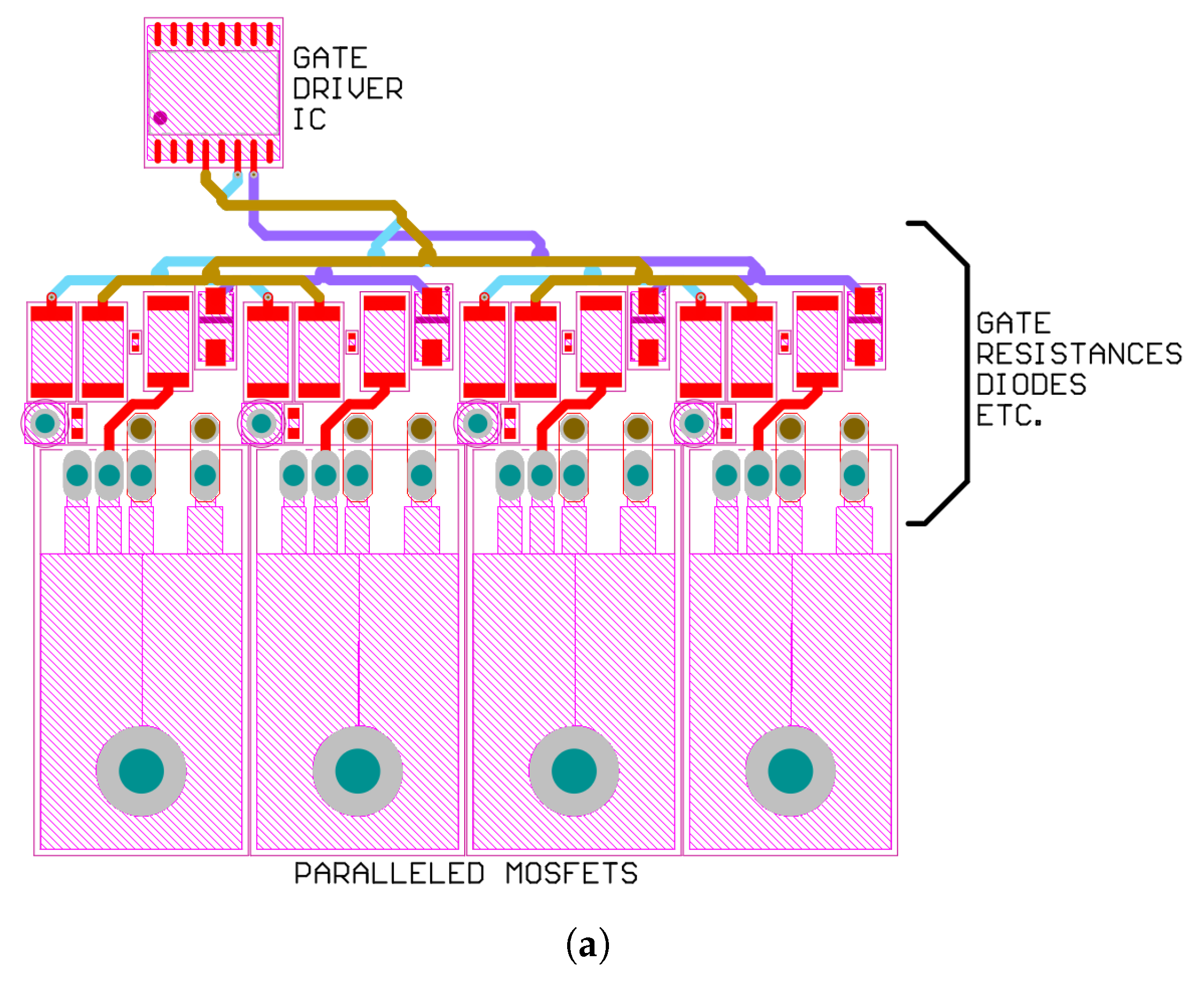

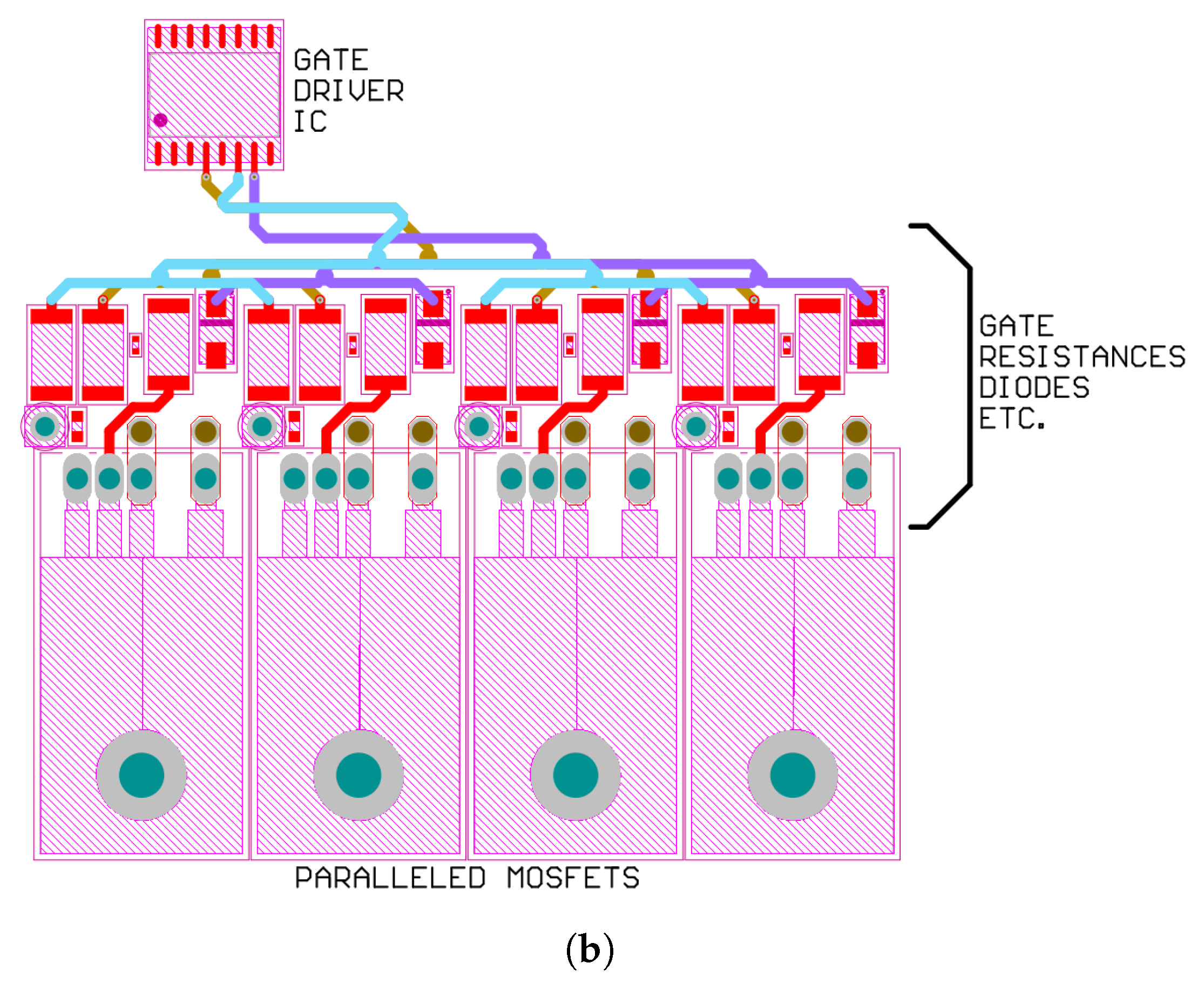

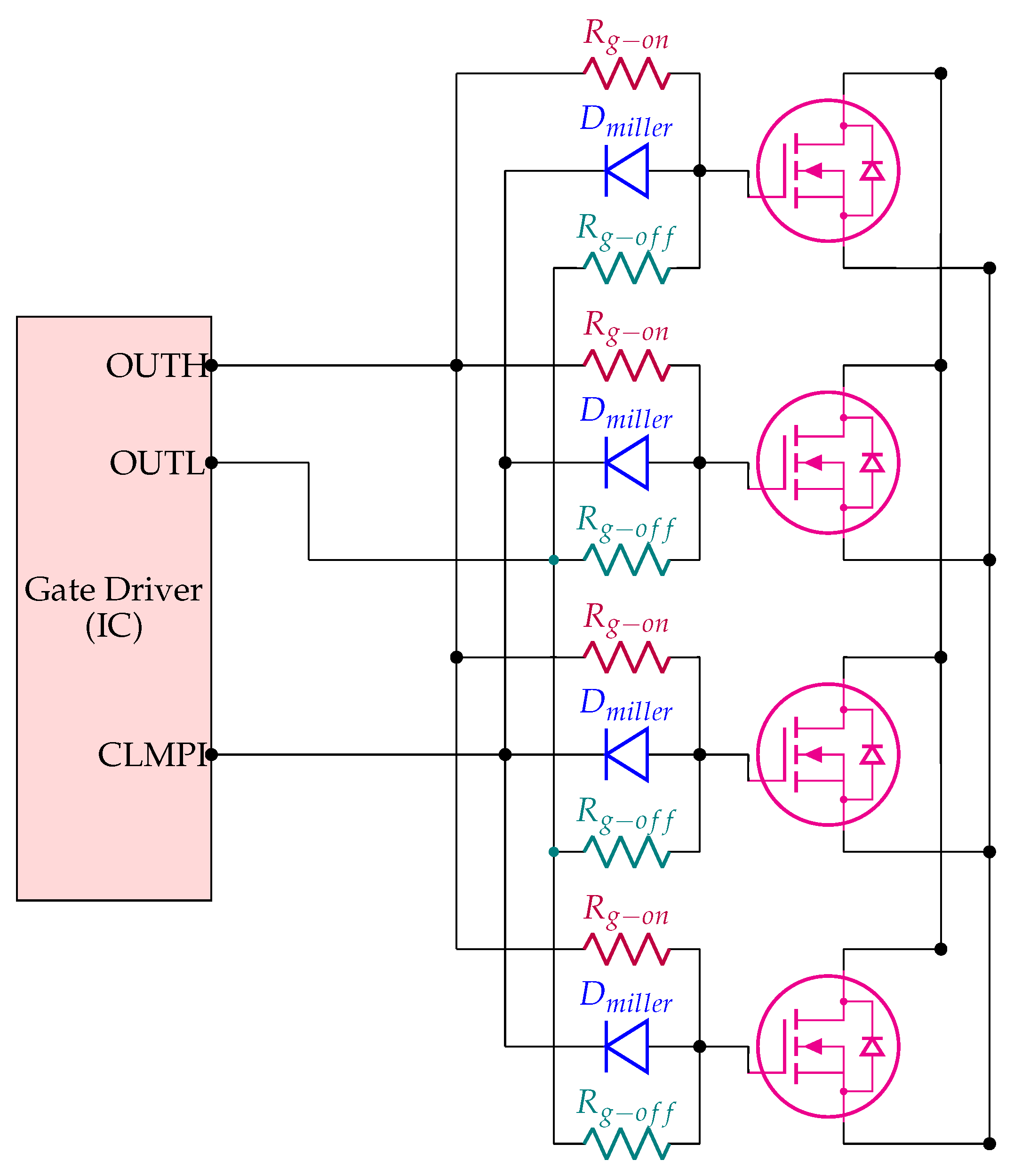

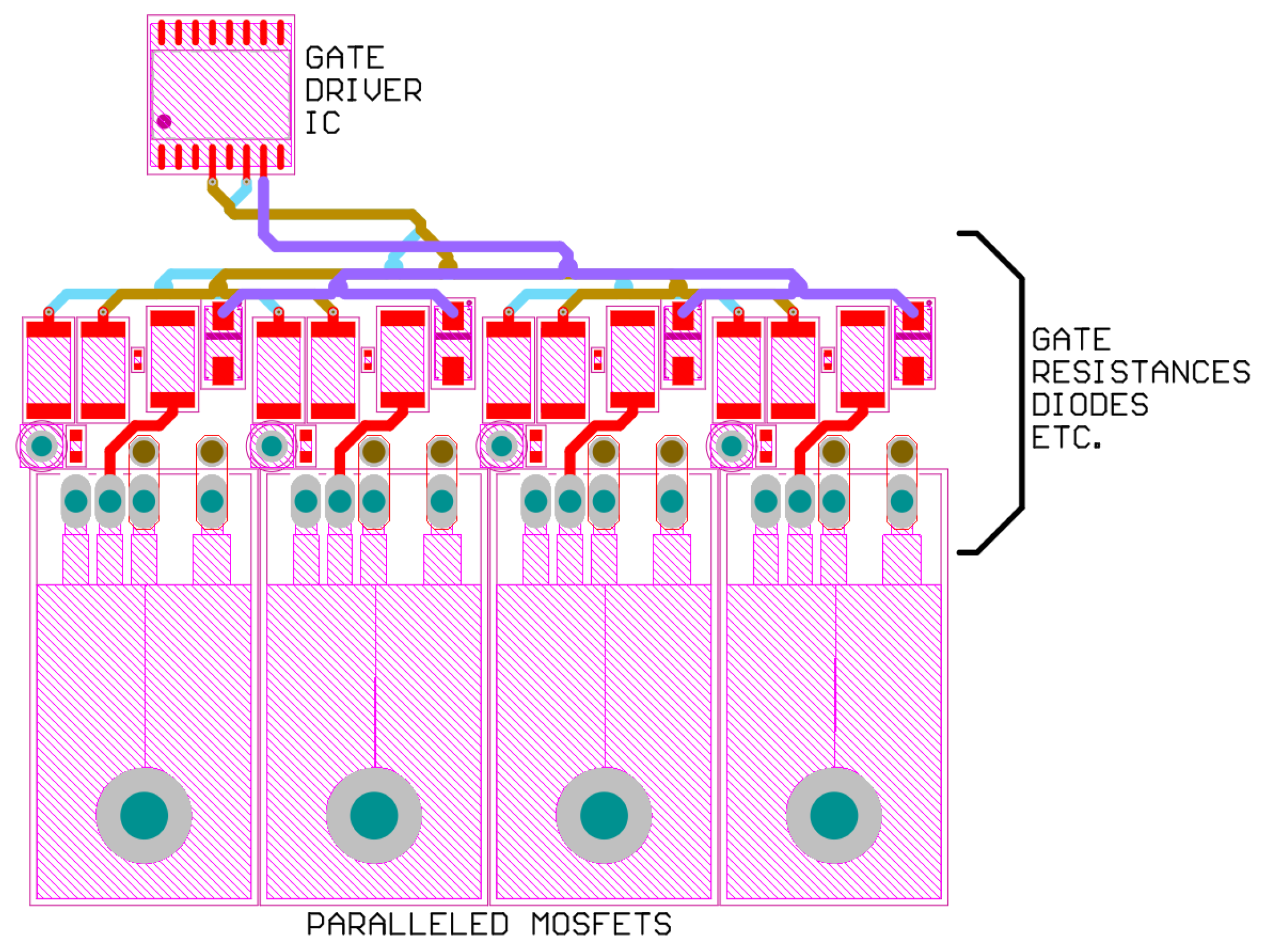

The main purpose of this work is to construct a switching leg composed of paralleled SiC MOSFETs that does not include any passive or active current balancing circuit without any current imbalance. The proposed half-bridge circuit schematic composed of four paralleled SiC MOSFETs is shown in

Figure 1. One gate driver circuit is used for the four parallel connected SiC MOSFETs. For the half-bridge circuit topology, two gate driver circuits are used, one for the high side and one for the low side of the leg. DC source and DC-Link capacitance are connected to the DC side of the circuit. R and L are the passive loads for the circuit. All of the connections are provided on the PCB, except DC and phase connections. These connections are provided with the help of a laminated busbar.

This paper is composed of five sections. In

Section 2, the simulation model of the SiC MOSFET is explained. In

Section 3, the hardware of the system is detailed. Experimental results are shown in

Section 4. Finally,

Section 5 summarizes the critical points of this paper.

2. Simulation Model of SiC MOSFET

Modeling of switching instants for any switching device is difficult for the simulation environment due to the nonlinearity of elements and the limitation of computation performance. In particular, modeling wide-bandgap semiconductors is more difficult due to the high switching speed, which causes a challenging trade-off between computation time and complexity of modeling. Mainly, the modeling of semiconductors can be categorized into two groups: analytical and behavioral models. At this point, behavioral models are more appropriate compared to analytical models because equations of physical modeling that include the nonlinearity of elements require excessive computation. In Ref. [

10], the analytical model of SiC MOSFET in a DPT circuit is explained in detail; however, intensive equations are used. In the same way, a detailed analytical model of the SiC MOSFET for the bridge-leg configuration is constructed in Ref. [

11]. However, it also requires a complicated equation. On the contrary, behavioral models use the I-V and the capacitance curves (C-V) of the device. Both of them can be obtained easily from the datasheet. Data sets can be extracted from datasheet graphs with the help of any curve-fitting tool [

12]. In this research, the Plotdigitizer [

13] program is used to accurately extract data sets from datasheet graphs.

Data sets are obtained from the datasheet of the Wolfspeed CREE-C3M0015065K SiC MOSFET [

14], which is shown in

Table 1,

Table 2,

Table 3 and

Table 4.

Table 2 and

Table 3 show the MOSFET

current with respect to the

&

voltages. The datasheet provides first and third quadrant graphs of

&

for different

voltages. The first quadrant graph includes the range of 0 V–10 V for

and 7 V, 9 V, 11 V, 13 V, and 15 V values for

. Furthermore, the third quadrant graph includes the range of −8 V–0 V for

and values of 0 V, 5 V, 10 V, and 15 V for

. According to

Table 2 and

Table 3, missing parts of the datasets are calculated using a linear interpolation method. Although the

graph is non-linear, the linear interpolation method is a handy tool to obtain the approximated

graph for different

voltages. The reason is that approximated curves are close to each other, and they can be considered parallel. Moreover, it also makes the calculation process easier. Negative

values are added to the bottom of

Table 2 and

Table 3 with zero current value because this part is modeled under the body diode model.

Table 1 shows the body diode

current with respect to the

&

voltages. The body diode current graph from the datasheet provides the range of −7 V–0 V for

and 0 V, −2 V, and −4 V for

. However, 0 V, −2 V values for

are not modeled due to the customization options of a simulation program.

current values for

= −10 V, −9 V, and −8 V are calculated with a linear interpolation method for the body diode.

Table 4 shows the internal capacitance values with respect to

voltage. Internal capacitances are

(input capacitance),

(reverse transfer capacitance), and

(output capacitance).

MOSFET and diode models of Simscape blocks of the MATLAB

®/Simulink

® have many options to customize the model. The obtained datasets are implemented in Simscape blocks using this property; therefore, most of the non-linear parts of the switching instant are modeled. Moreover, a reverse recovery model of the body diode is implemented with the “charge dynamics” option of the Simscape diode model. The peak reversed current, initial forward current, rate of change of current, and charge quantity properties from the datasheet are implemented in the model. However, the datasheet provides these properties only for the

°C junction temperature and 55.8 A initial current value. Therefore, only that condition is modeled for reverse recovery. In addition, sample time and solver type are essential factors for simulation time. The backward Euler solver is used with the

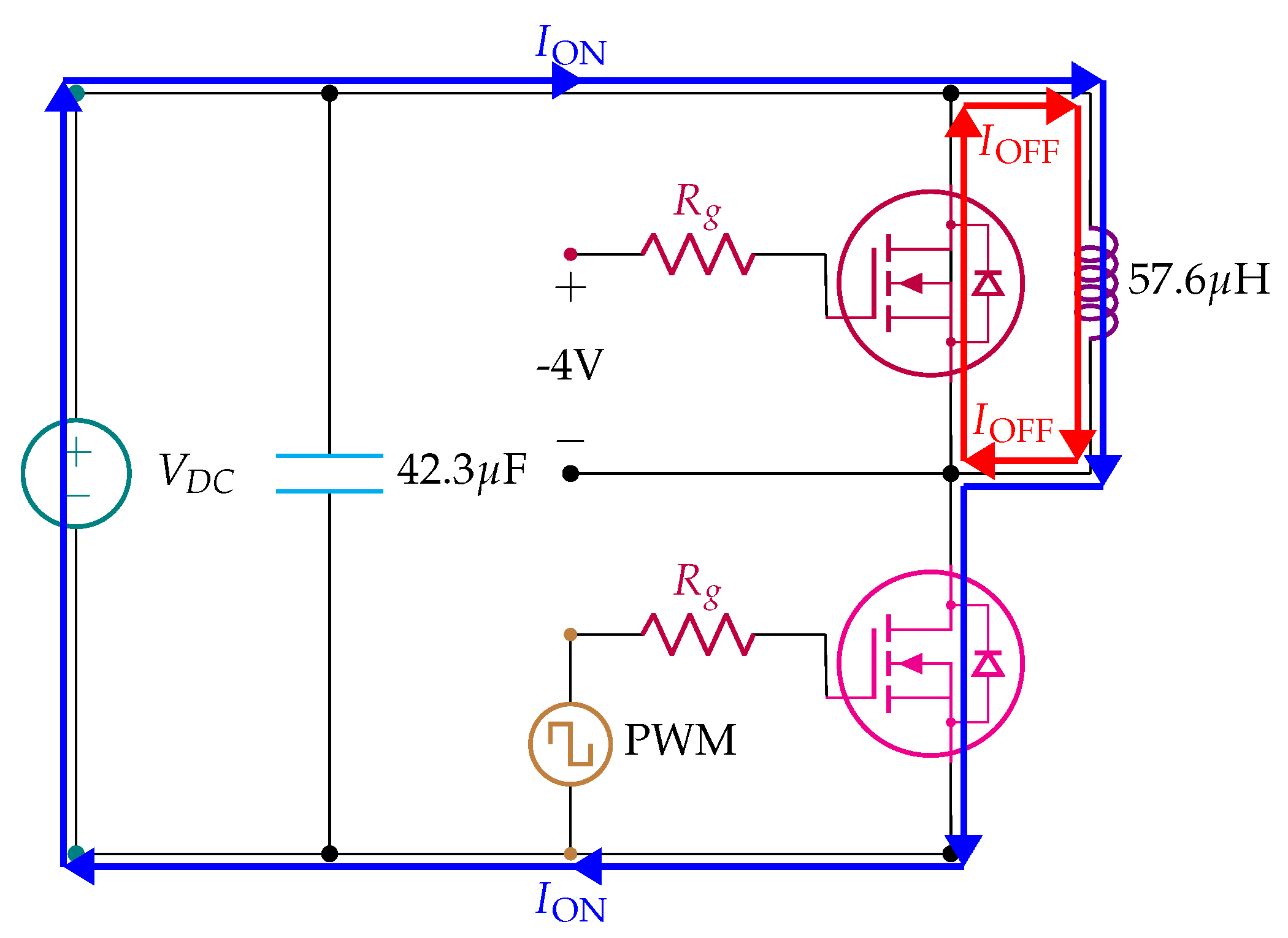

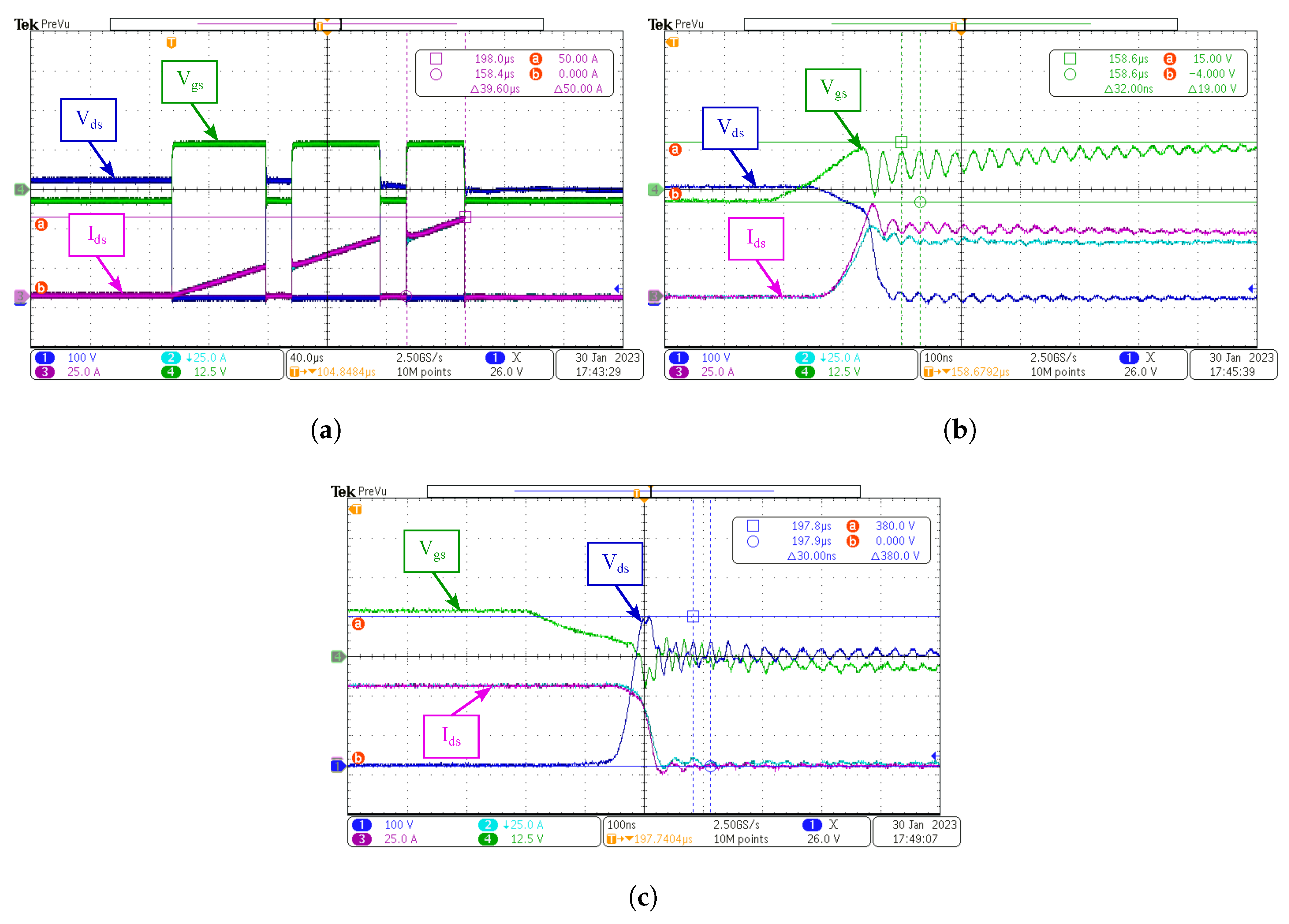

sample time, which many computers can handle. This sample time is obtained with a trial-and-error method according to the trade-off between the processing time and the resolution of the results. It is mainly affected by the switching frequency, which is 12.5 kHz. A double-pulse test (DPT) circuit is used to verify the MOSFET and diode models, shown in

Figure 2. In the DPT circuit, a high-side MOSFET is switched off for the entire switching period. Its body diode is used as a free-wheeling diode for the parallel connected inductor, but low side MOSFET is switched with 15 V/−4 V PWM. The

value is set to 5

, and

is selected as 400 V. Values of passive elements and applied voltages are selected according to the DPT circuit of the MOSFET datasheet to compare the same cases. When the low-side switch is turned on, current flows through the inductor and low-side MOSFET. For that period, the current magnitude is increased according to the well-known formula given in Equation (

1); therefore, the switching current value of the low-side MOSFET is adjusted by modifying the duty cycle. Besides that, the current on the inductor flows through the body diode of the high-side MOSFET when the low-side switch is turned off. In this way, the MOSFET’s turn-on and turn-off losses can be calculated.

where

is the applied

DC voltage,

is the inductor current, and

L is the inductance value.

Comparison of switching losses is a valuable indicator to verify the simulation model. Therefore, switching losses are calculated with the DPT circuit in the simulation program for the low-side MOSFET. The calculated values are compared with the datasheet values; the results are shown in

Table 5. To compare the accuracy of results, total loss error (TLE) calculation is used, which is shown in Equation (

2). As seen in

Table 5, the maximum mismatch of the total error is less than 10% for all current ratings. The turn-on loss mismatch is the significant portion of the mismatch because the turn-off losses are closer to the datasheet values than the turn-on losses. When the low-side MOSFET is switched to turn-on, the current of the inductor and the reverse recovery current of the high-side MOSFET body diode are superposed. Therefore, the main reason behind the mismatch of the turn-on loss is caused by the reverse recovery model of the body diode. As explained above, only the

°C junction temperature and 55.8 A initial current value case of the diode can be implemented. However, the mismatch in the turn-on loss, less than 10% of the total loss mismatch, is in an acceptable range. Furthermore, the current and voltage curves of the MOSFET and diode are implemented in detail in the simulation model. For this reason, the conduction losses calculated in the simulation are the same as the conduction losses in the datasheet based on the value

.

where,

TLE is the total loss error,

and

are the turn-on and turn-off energies of the MOSFET, respectively.

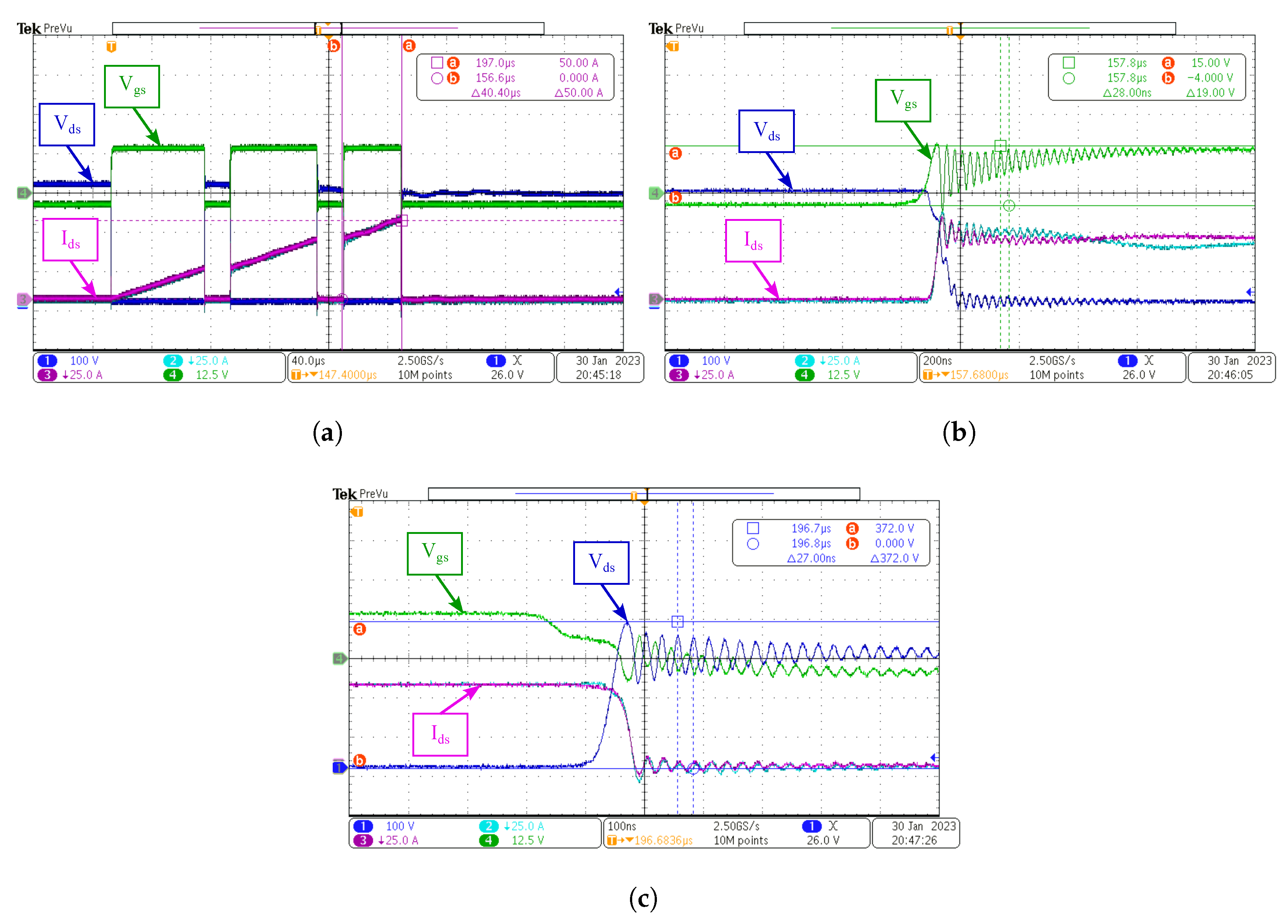

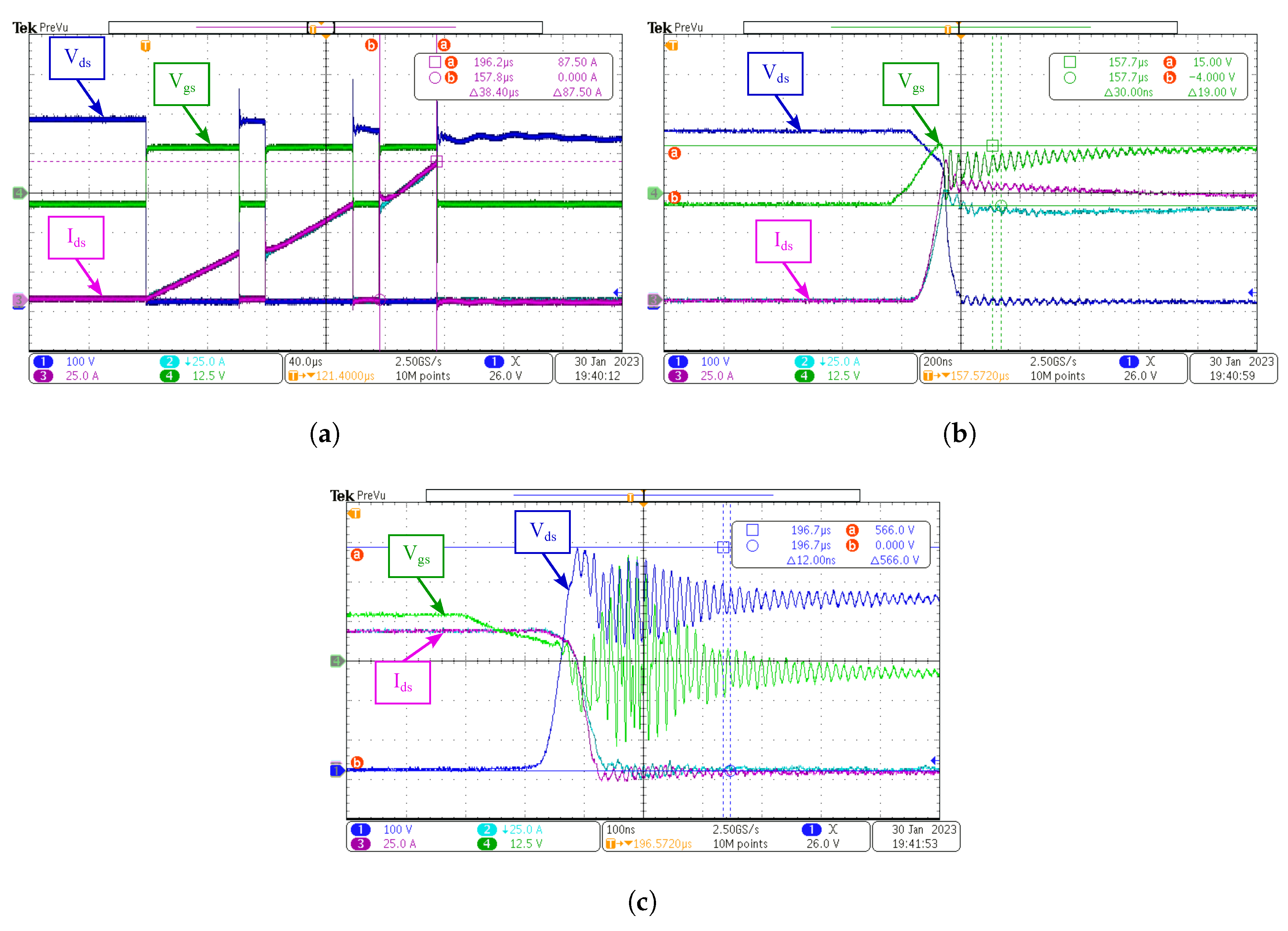

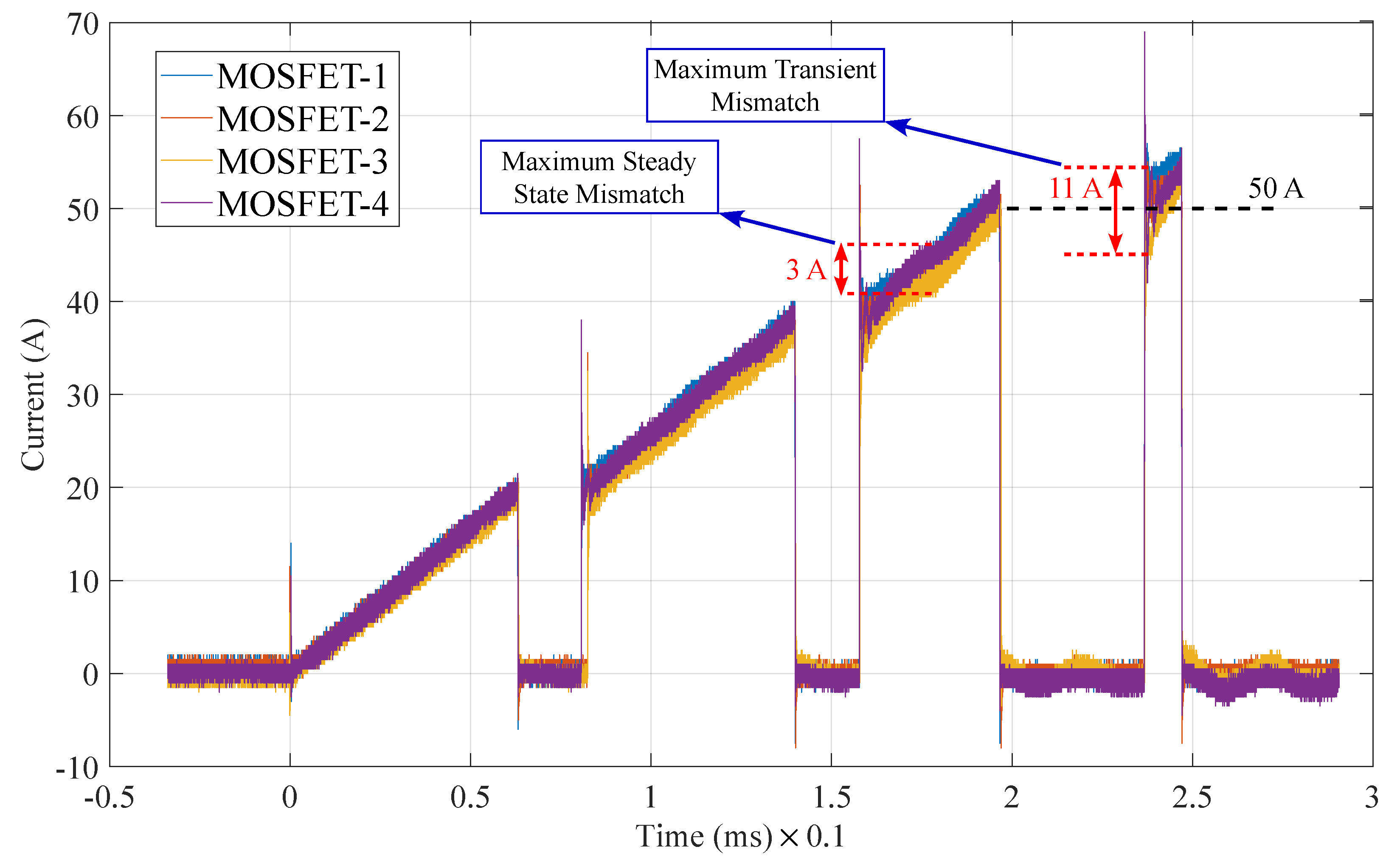

Simulation of Half-Bridge Circuit with Four Paralleled SiC MOSFET

The half-bridge circuit with four paralleled SiC MOSFET, as shown in

Figure 1, is run with the obtained model of the SiC MOSFET in the simulation program. The laminated busbar model is implemented into the simulation model by equivalent resistance, capacitance, and inductance values. These values are obtained by measurement with an LCR meter. The gate resistance of 10

is used for the SiC MOSFETs, and the 220

H inductor is used as a load. Furthermore, 82

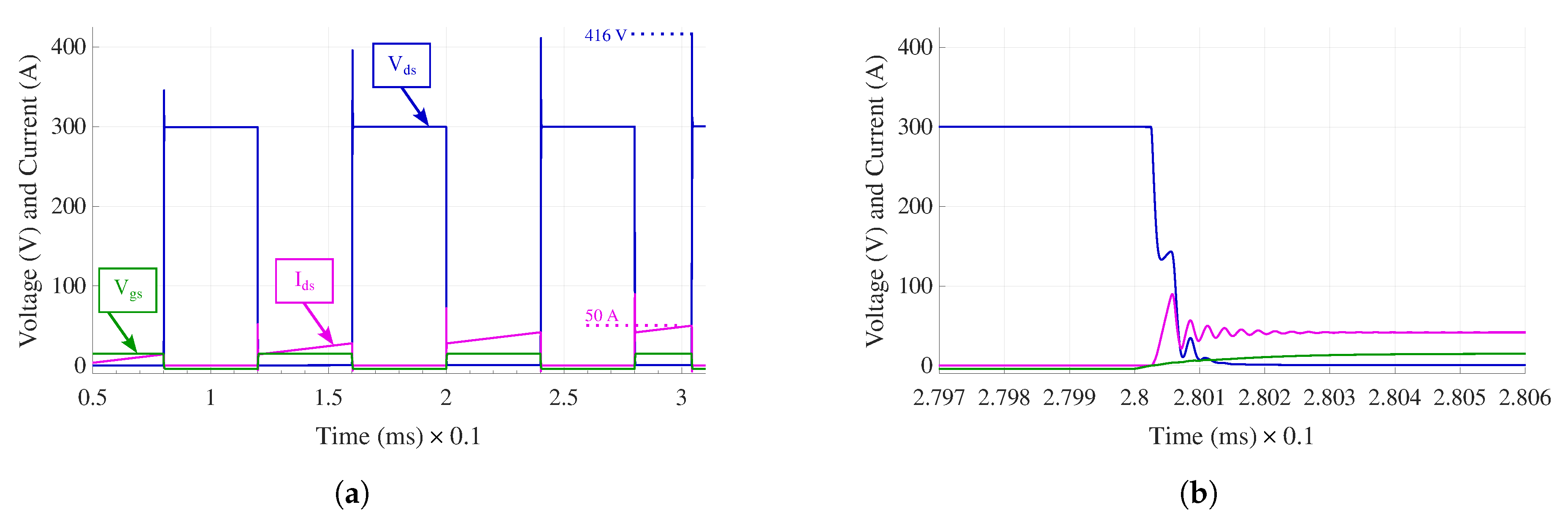

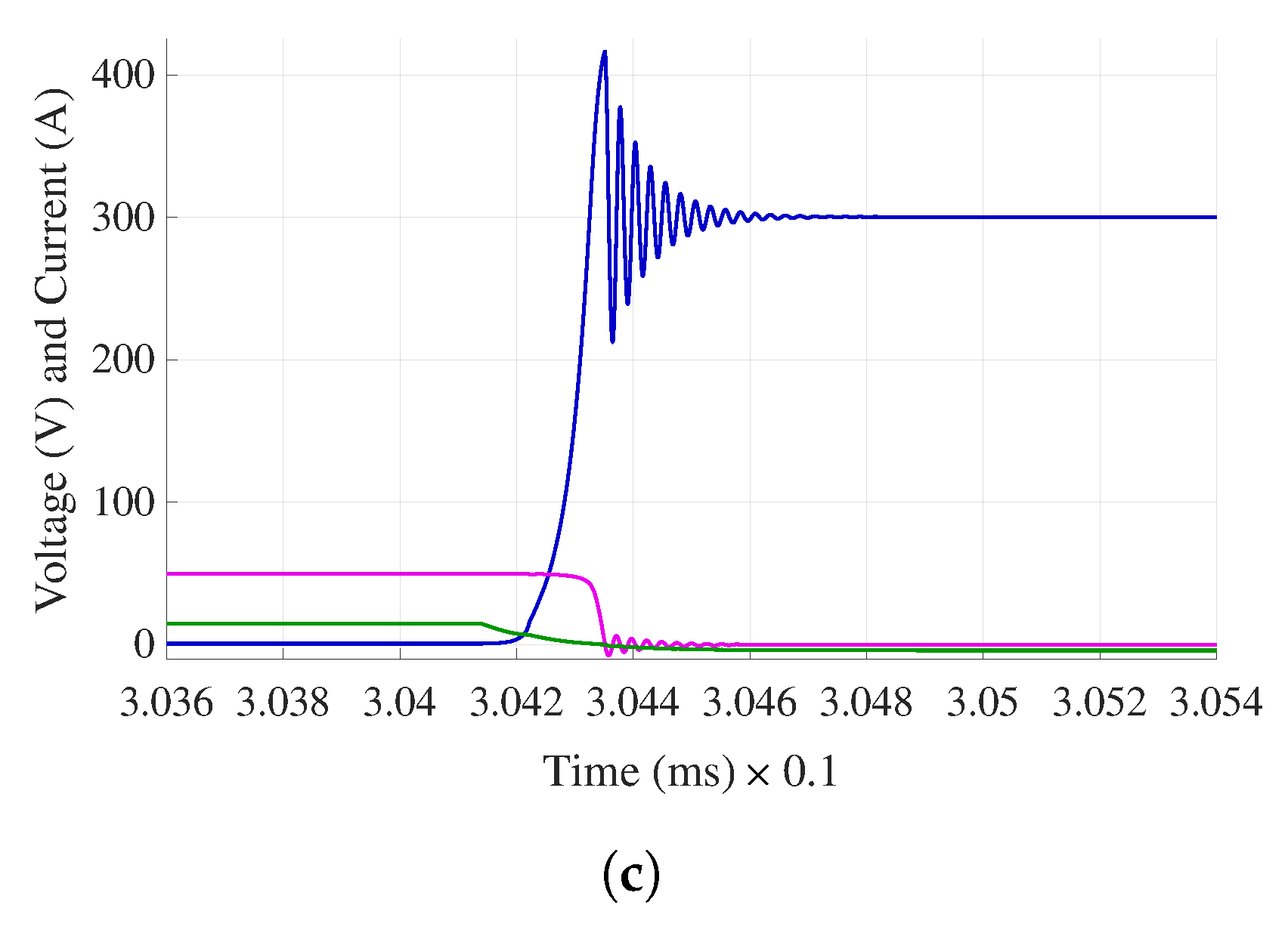

F capacitance is used for the DC-Link. In the simulation, equal current sharing is observed between parallel connected MOSFETs. However, voltage overshoot problems are observed in the

voltage when a turn-off case is applied. For the 50 A

current of MOSFETs, 416 V overshoot is observed for the 300 V switching voltage. That corresponds to 38% voltage overshoot. The applied switching waveform and the voltage overshoot are shown in

Figure 3.