1. Introduction

The phase-locked loop (PLL) is a negative-feedback-closed-loop control system commonly used in grid synchronization and control of grid-tied power converters [

1,

2,

3,

4]. The wide usage of power converters is due to their ability to convert electrical power from one form to another, making it possible to use power from different sources and to power different devices with different requirements. PLLs are also used in sensorless control of electrical machines [

5], power quality indices [

6,

7], and islanding detection [

8].

Among all types of PLL, the most common type used in the three-phase applications is the conventional synchronous reference frame (SRF)-PLL with a proportional-integral (PI) controller as a loop filter due to its structural simplicity and ease of implementation [

9,

10]. In the conventional SRF-PLL depicted in

Figure 1, the PI controller can only mitigate the phase error and estimate the grid parameters precisely under ideal conditions. However, it cannot completely block or attenuate the harmonics, the DC offset, and any possible grid noise.

The DC offset in the grid voltage may be generated because of grid faults [

11], geomagnetic phenomena [

12], the A/D conversion process [

13], and the DC injection by distributed generation systems, specifically PV inverters [

14], to name a few. In addition, the power quality problems related to the presence of the DC components in the grid voltage adversely affect the performance of the synchronization unit, causing oscillatory and offset errors in the estimated grid information [

15].

The bandwidth (BW) of the PLL must be restricted to a low value to attenuate the DC offset using the conventional SRF-PLL. This results in poor dynamic performance and may not be acceptable in most applications. For example, the requirement for settling time in common grid codes is less than two grids’ fundamental cycles [

16,

17].

Recently, several approaches have been proposed to incorporate an additional filtering stage, either in the inner or outer loop of the conventional SRF, to deal with the DC offset problem [

17,

18,

19,

20,

21]. Besides the DC offset rejection, estimating the amplitude and the phase of the fundamental grid voltage components and compensating for the phase lead caused by those additional filters puts another challenge to be solved to synchronize with the grid perfectly.

In [

18], the moving average filter (MAF) is used in the inner loop of the PLL, showing an excellent rejection capability against the harmonics. However, its dynamic response is slow, especially under the frequency drifts, which appear as ripples in the estimated frequency. Moreover, under large frequency drifts, the MAF performance becomes worse. Therefore, the estimation of the grid information is degraded.

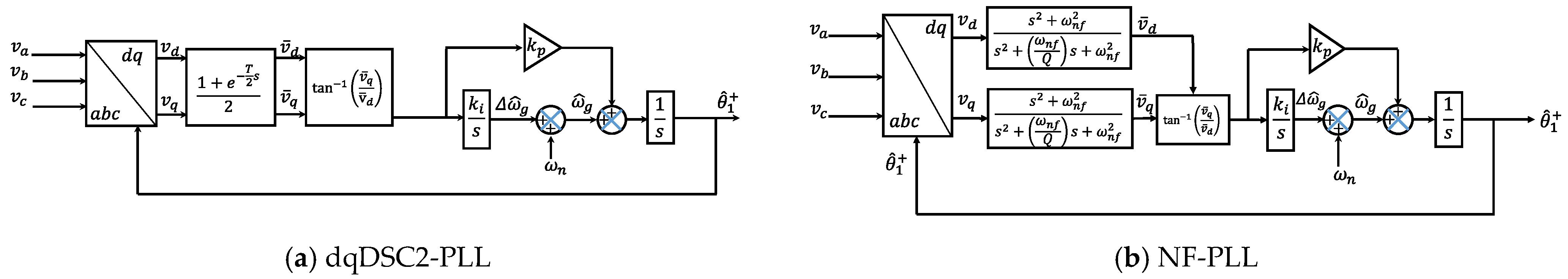

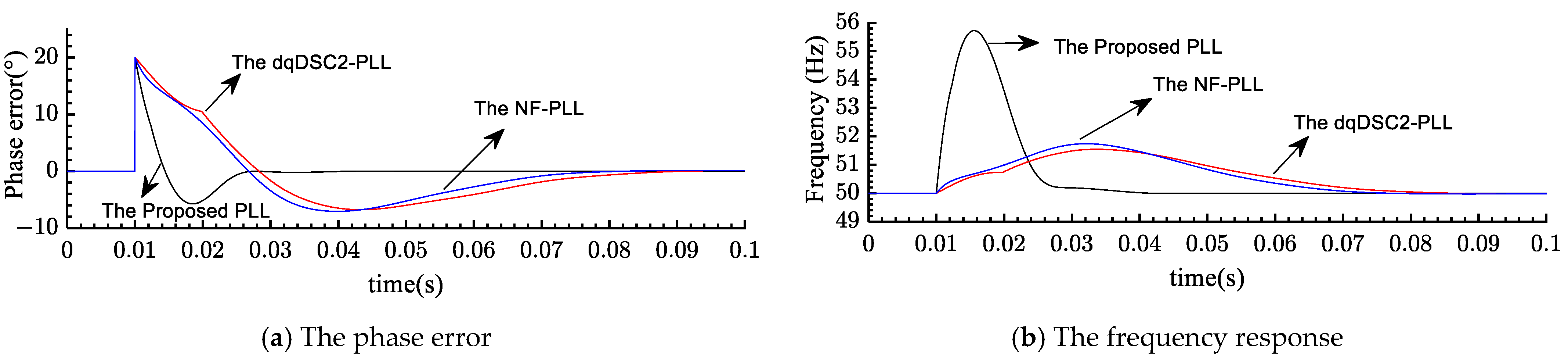

In [

19], a notch filter phase-locked loop (NF-PLL) is proposed for grid synchronization with DC offset rejection technique by replacing the in-loop MAF with a notch filter. This enables the PLL to block the DC offset contaminated with the grid voltages effectively at the cost of slowing down the response. Moreover, the NF-PLL performance becomes worse under large frequency drift, which can be solved by narrowing the bandwidth of the NF; however, this adversely affects the PLL’s performance.

Delayed signal cancellation (DSC) PLL that provides good DC offset filtering capability has been proposed in [

20]. The dqDSC is implemented in the PLL inner loop and has only one decisive parameter: the delay factor. Selecting a specific delay factor to eliminate the DC offset, the dqDSC shows good rejection capability, but its dynamic response is slow. The slow dynamic response caused by the DSC operator can be improved by adding a phase lead compensator in the PLL’s inner loop, which may decrease the DC rejection capability of the PLL, specifically under grid frequency drift.

In contrast, the αβDSC-PLL, implemented in the PLL outer loop, shows a good DC offset rejection capability with a faster transient response than the dqDSC-PLL under the same delayed factor. However, the phase compensation method needed under frequency deviation complicates the PLL design [

21].

In [

22], a specific design parameter is suggested using modified delayed signal cancelation (MDSC) in the inner loop of the SRF-PLL with a specific delay factor. The MDSC based PLL shows good DC offset elimination with rapid response. The lead-in phase caused by the MDSC operator is compensated by computing the lead-in phase and then adding the same angle directly into the PLL output, which is not general for any delay factor selection. Moreover, it does not have a general voltage amplitude estimation technique under the arbitrary delay factor.

Therefore, this paper proposes a generalization to the MDSC-PLL. The proposed PLL is based on general mathematical relationships between the delay factor and the design parameter, eliminating the DC offset and extracting the grid voltage’s fundamental frequency positive sequence (FFPS) under any delay factor. Moreover, the proposed model has simple and general estimation techniques to estimate the grid voltage amplitude, frequency, and phase.

This paper is arranged as follows:

Section 2 presents an overview of DSC and MDSC operators. Then, the proposed PLL with amplitude and phase compensation formulas is derived in

Section 3. In

Section 4, the mathematical model is derived, and the controller gains are designed. In

Section 5, with two selections of the delay factor, the justification for the proposed model and its mathematical model against both compensation formulas are implemented mathematically and throughout the numerical simulation. In

Section 6, experimental results compared with other related PLLs are presented to demonstrate the effectiveness of the proposed PLL. Finally,

Section 7 concludes the paper’s findings.

2. The Modified Delayed Signal Cancellation Operator

The DC offset in the input of the synchronizing unit causes an oscillation in the estimated grid information. The DC component in the

abc-reference frame has a zero-harmonic order; hence, it becomes a negative one in the

dq-reference frame after using Park’s transformation. Therefore, the DC component appears as a sinusoidal wave in the

dq-reference frame and possesses half-wave symmetry. A summation with the delayed versions in the

dq-reference frame can cancel out the DC component, which illustrates the basic topology of the DSC operator. The DSC operator is commonly implemented in the inner loop of the PLL operating in the

dq-reference frame. The general expression for the DSC operator in the s-domain can be described as:

where

T is the fundamental voltage grid period, and

n is an integer that specifies the delay factor.

In Equation (1), the DSC operator has only one design parameter, the

n. This operator is used widely in many approaches since it has excellent rejection capabilities against the DC offset and harmonics, which depends on its selection; each

n has a specific ability to deal with certain harmonics. However, it suffers from slow dynamic performance when used to reject the DC component. Thus, the DSC operator is modified into the MDSC operator, giving the DSC flexibility and improving its dynamic response [

22]. The MDSC operator can be expressed in the s-domain as:

where

ns is a design parameter used to shift the frequency characteristics of the DSC,

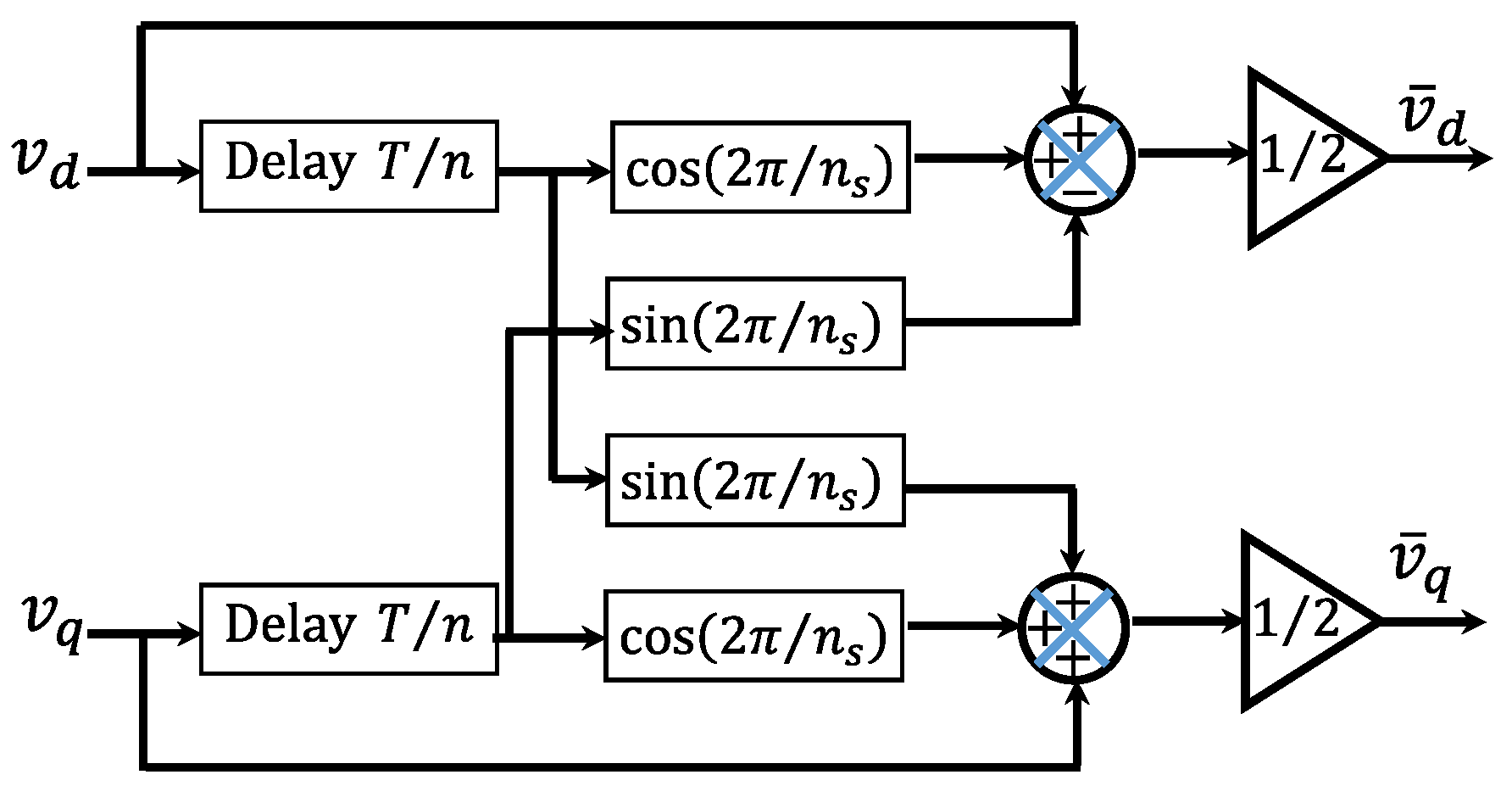

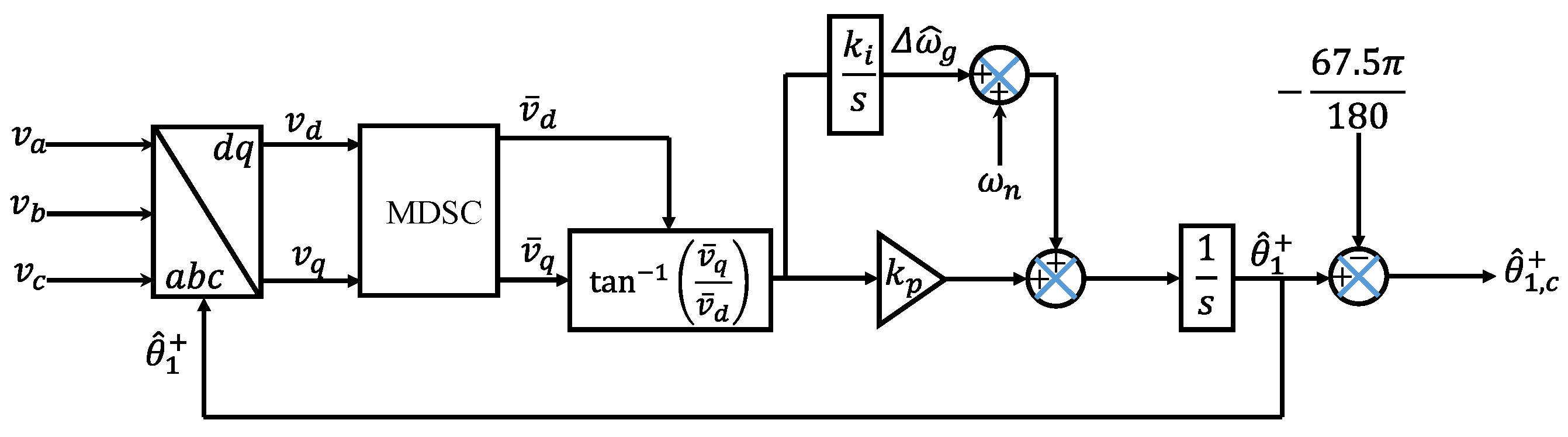

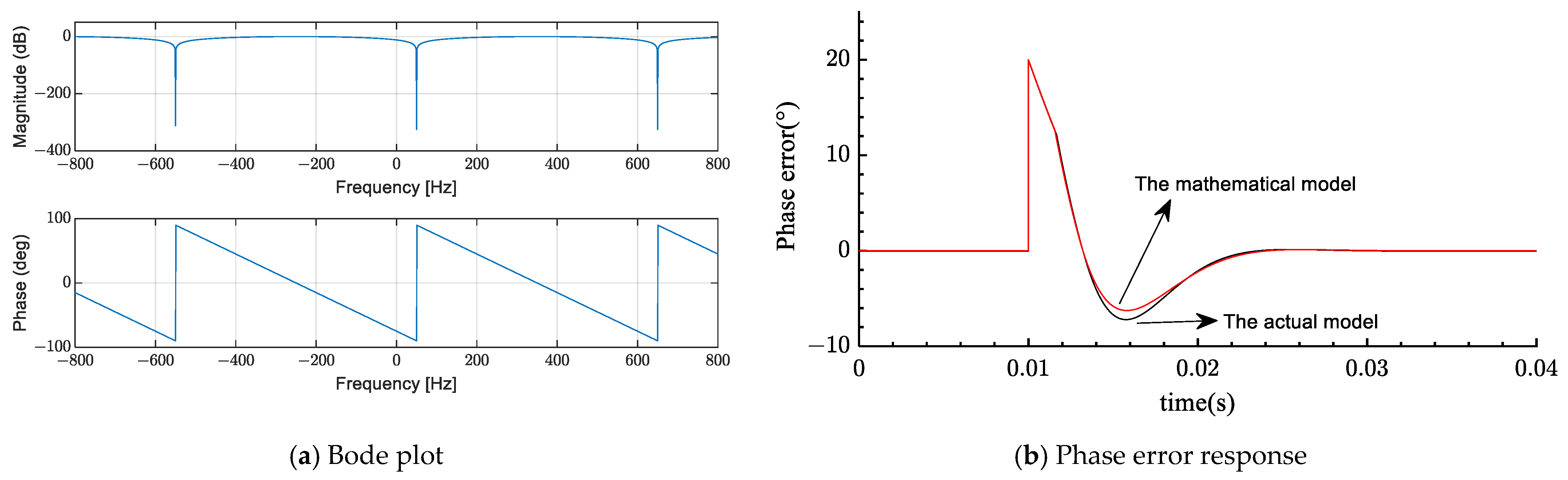

Figure 2 depicts the time-domain implementation of the MDSC operator. In contrast, the schematic diagram of the MDSC-PLL is illustrated in

Figure 3 [

22].

3. The Proposed Phase-Locked Loop

The MDSC-PLL features excellent dynamic performance and DC offset rejection with a shorter delay. However, it does not have an explicit general algorithm for selecting the MDSC operator’s parameters against any delay operator. Moreover, the utilized compensation criteria are based on calculating the phase lead under a specific delayed factor. Hence, the compensation in [

22] is not general and hard to be adopted under an arbitrary delay factor. Moreover, no general voltage amplitude estimation is discussed in [

22].

Therefore, to achieve perfect synchronization with an arbitrary delay factor, the MDSC-PLL is generalized in this paper. The proposed PLL is based on general mathematical relationships between the delay factor and the design parameter. The proposed PLL can eliminate the DC offset and extract the FFPS of the grid voltage precisely and rapidly while estimating the amplitude of the grid voltage and compensating the lead-in phase under any election of the delay factor.

To derive a general expression of the proposed PLL in the

dq-reference frame under any selection of

n, consider the grid voltage that contains some DC offset components:

where:

,

and

. The subscript ‘

’ defines the reference frame of the grid, which is called the natural reference frame,

is the grid voltage amplitude of the FFPS component,

is the grid phase angle of the FFPS component,

is the grid angular frequency,

is the nominal grid fundamental angular frequency,

is the nominal grid fundamental frequency, and

is the grid voltage initial phase angle,

,

, and

are the DC components in the grid voltages.

Applying Park’s transformation to the grid voltage in Equation (3) yields:

where:

and

,

is the estimated phase angle, and

is the estimated angular frequency, and

is the estimated angular frequency variation.

After simplifying the terms in Equation (4) and using the trigonometric identities, the

and

components can be expressed generally in terms of harmonic order as follows:

Equation (6) represents the relationship between the harmonic order in the abc-reference frame and its corresponding harmonic order in the dq-reference frame . According to this relationship, it is important to mention that the DC offset in the abc-reference frame becomes of order (−1) in the dq-reference frame. In contrast, the FFPS in the abc-reference frame becomes a DC quantity in the dq-reference frame. Therefore, the functionality of the proposed MDSC operator is to extract the FFPS and block the DC components in -reference frame while it is operating in the dq-reference frame at any delay factor.

From

Figure 2, the output of the MDSC operator can be expressed as follows:

Taking into account the relationship between

-component and

-component as

Using Equations (7)–(9), the Laplace transform of the MDSC operator can be described as:

Substituting

in Equation (10) yields the following frequency response of the MDSC:

Equation (11) can be rewritten in the following form:

From Equation (12), the cosine term is the gain of the MDSC operator, which corresponds to the

harmonic component, while the angle term represents the phase delay of the MDSC operator of the same harmonic component. Generally, the MDSC operator’s gain that corresponded to that harmonic order must equal zero to block any specific harmonic. Since the gain is a cosine function, it can block multiple harmonics simultaneously, which is considered one of the main advantages of the MDSC operation. Therefore, equating the MDSC operator gain with zero leads to a general mathematical relationship between the delay factor

,

, and the harmonic order

as follows:

which equals zero if and only if:

The frequency characteristics of the MDSC are the same as that in the DSC operator but shifted by (

/

) with a BW of (

. The notch frequencies are shifted along the frequency axis according to the required harmonics to be eliminated, which corresponds to a general formula between the operator’s parameters. The general formula describes the relationship between

, any harmonic order

, and

derived from Equation (14) can be written as:

since

has many choices, more than multiple values of

and

can satisfy Equation (15) for a particular value of

. Similarly, for many choices of

, multiple values of

can be selected for a given value of

and

. This means different MDSC operators can eliminate the same harmonic, while the same MDSC operator can attenuate a group of harmonics. However, in order to select the values for

and

corresponding to minimum phase delay, the design parameter

is inversely proportional to the phase delay caused by the MDSC operator. Therefore, the maximum value of

, which occurs when

, minimum phase delay will be achieved. Thus, substituting

in Equation (15) yields:

From the harmonic rejection capabilities perspective, this paper’s primary concern is to cancel out the DC component injected in the natural reference frame, which turns out to be of order

in the

dq-frame. This means that one of the notch frequencies must be shifted to (−50 Hz) along the frequency axis of the MDSC operator of BW greater than (50 Hz). Therefore, substituting this harmonic order in Equation (16) leads to:

It is important to illustrate the relationship between the delay factor and its corresponding proper design parameter value described in Equation (17). This relation affects the operator’s dynamic response and PLL performance. To achieve a rapid transient response for the proposed PLL against any step change in the input, the phase delay caused by the MDSC operator is inversely proportional to the design parameter , but the design parameter is directly proportional to the delay factor Therefore, by increasing the value of , the value of will be increased accordingly, and hence the phase delay caused by the operator will be decreased, resulting in a fast transient response of the PLL.

Moreover, increasing the value of the delay factor will increase the BW, reducing the MDSC operator’s harmonic rejection capabilities of the MDSC operator. However, since the DC component is the target here, the effect of increasing the BW on the other harmonics will be ignored. Therefore, the only restriction on the BW of the operator is not to be 50 Hz. Equation (17) is used for selecting the value of against the amplitude and phase estimation technique.

The Amplitude and Phase Compensation

Extracting the fundamental frequency component is implemented at zero hertz in

-reference frame, which can be calculated mathematically by substituting

into Equation (11) as follows:

To calculate general compensation methods for the amplitude and the phase in terms of any delayed factor

, Equation (17) is substituted in Equation (18), which yields:

The utilization of the MDSC operator will scale the amplitude by

, which can be obtained from the extracted

-component of the MDSC operator since it has the amplitude information of the fundamental frequency component of the grid voltage. Thus, the amplitude of the extracted

-component must be compensated to estimate the actual amplitude of the grid voltage. The compensation technique can be implemented by dividing the extracted

-component of the MDSC operator with the compensation formula derived in the last equation, which can be re-defined as:

where,

is the compensation voltage gain of the proposed PLL. The amplitude estimation of the fundamental frequency component under any delay factor selection can be expressed as:

The estimated phase lead value caused by the MDSC operator under any selection of the delayed factor can be represented by:

So, in order to compensate for this phase lead, a phase lag will be directly added to the output of the voltage-controlled oscillator (VCO) of the proposed PLL, which can be described in terms of compensated phase

as follows:

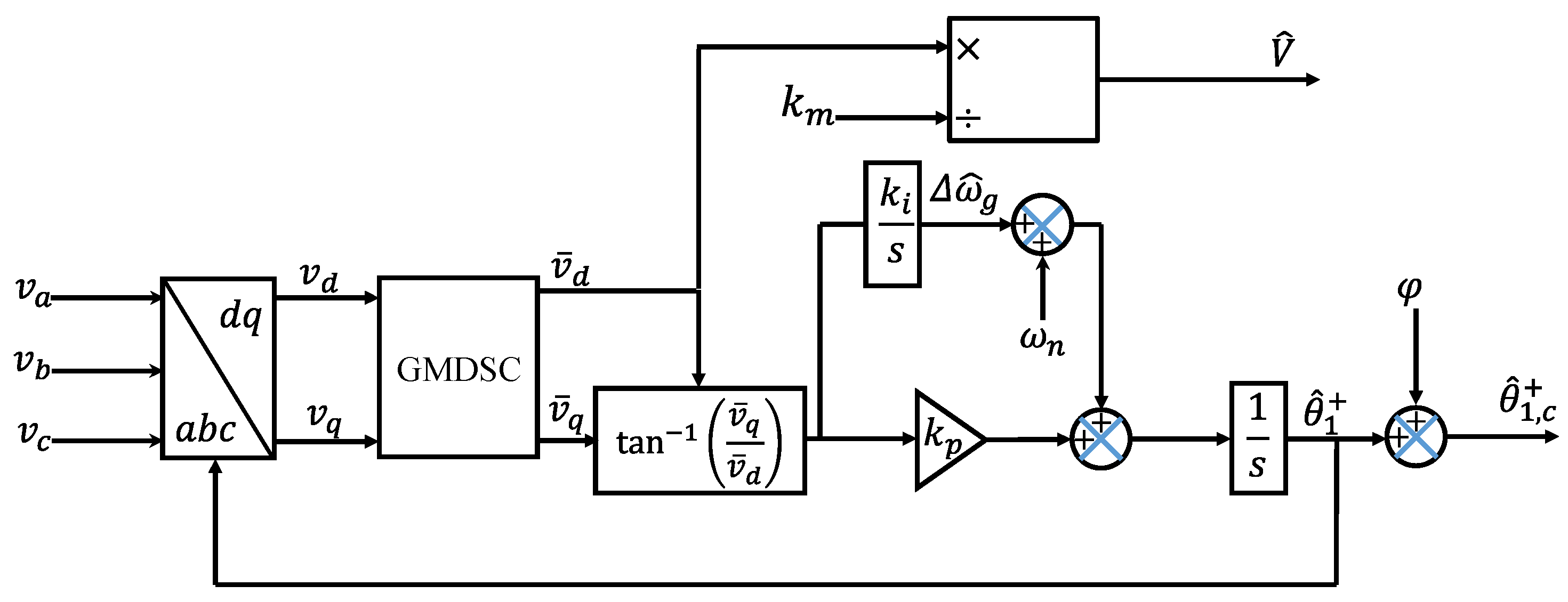

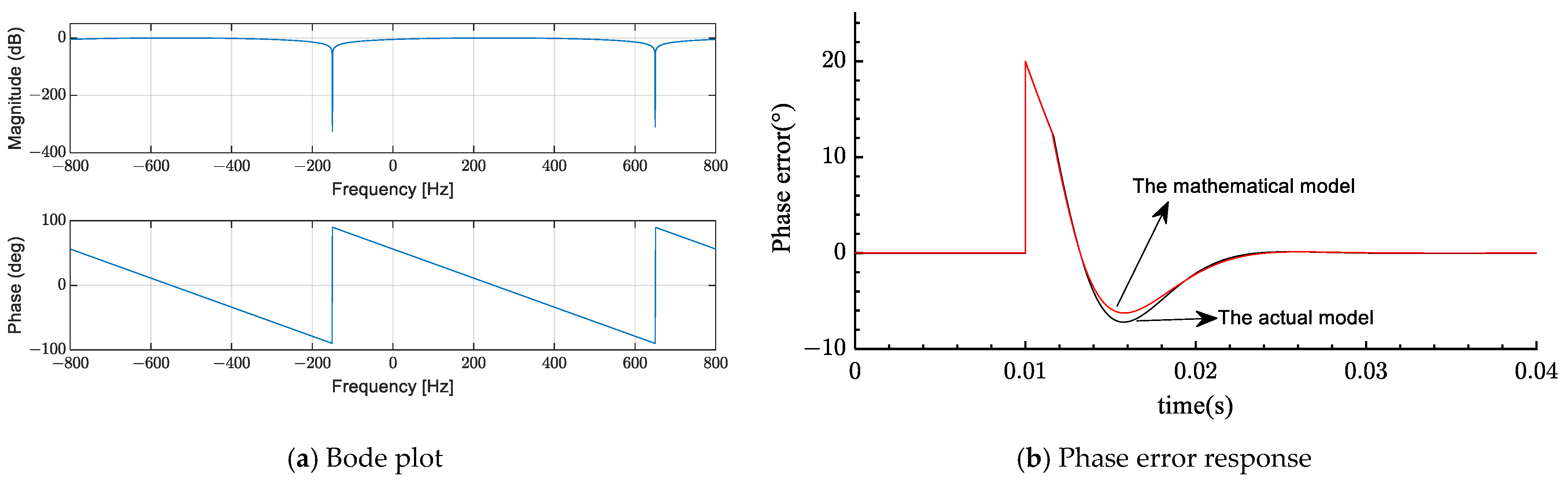

Equation (23) is the compensation formula for the phase error caused by the MDSC operator under any delay factor. Incorporating both derived formulas into the MDSC-PLL will configure the generalized compensated model depicted in

Figure 4.

4. The Mathematical Model of the Proposed PLL

The proposed PLL’s mathematical model will be derived in this section to analyze the stability of the proposed PLL and derive a general design formula against the PI controller’s gains under any delay factor election. The mathematical derivation criteria in this paper follow the guideline of [

23]. The extraction of the FFPS components in the

dq-reference frame is utilized by applying Park’s transformation to the FFPS of the grid voltages as follows:

the FFPS of the grid voltage in the synchronous reference frame can be extracted using the trigonometric identities as follows:

The extracted fundamental components from the MDSC operator derived in Equations (25) and (26) are incorporated into the arctangent operation, which can be described as:

Substituting Equations (25) and (26) into Equation (27) leads to the following:

where:

and

.

Using trigonometric identities, Equation (28) can be simplified into:

which can be written as:

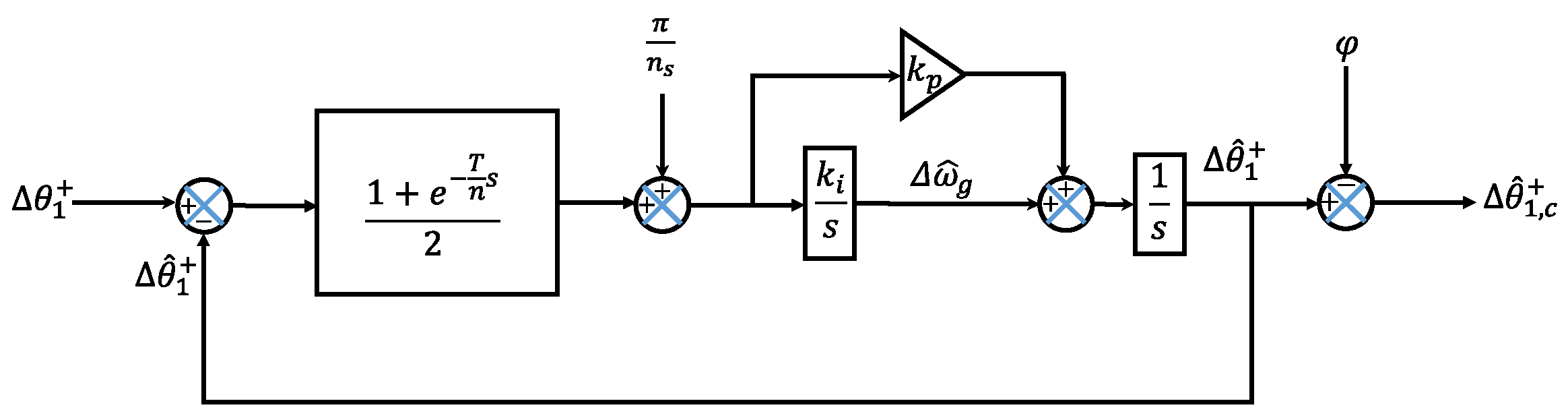

The arctangent function in Equation (30) extracts the phase error directly without any linearization procedure. Taking the Laplace transform of Equation (30) leads to the following:

The last equation represents the mathematical formula for the proposed PLL since it is valid under any selection of the delay factor

, depicted in

Figure 5. The term

, in

Figure 5, represents the DC offset value in the output phase of the proposed PLL. It is equal to the estimated phase formula derived earlier in Equation (22), which justifies the proposed phase compensation model. Moreover, to derive a gain formula against the PI controller in terms of delay factor, it is tackled by taking the open-loop transfer function of the mathematical model of the proposed PLL as follows:

the delay term in Equation (32) is approximated using Padé approximation to simplify the design process:

Substituting Equation (33) into the open-loop transfer function Equation (32) yields:

Applying the symmetrical optimum design method [

24], the PI controller parameters are obtained as follows:

where

c is a design constant that determines the phase margin (PM) of PLL, the PM of the PLL has the following formula:

Equations (35) and (36) represent the formulas for the PI gains of the proposed model that corresponds to any selection of the delay factor , while Equation (37) corresponds to the desired phase margin of the system, which is taken here as in many approaches for fair comparison as results in .