An Analysis and Optimization of the Battery Capacity Difference Tolerance of the Modular Multi-Level Half-Bridge Energy Storage Converter

Abstract

:1. Introduction

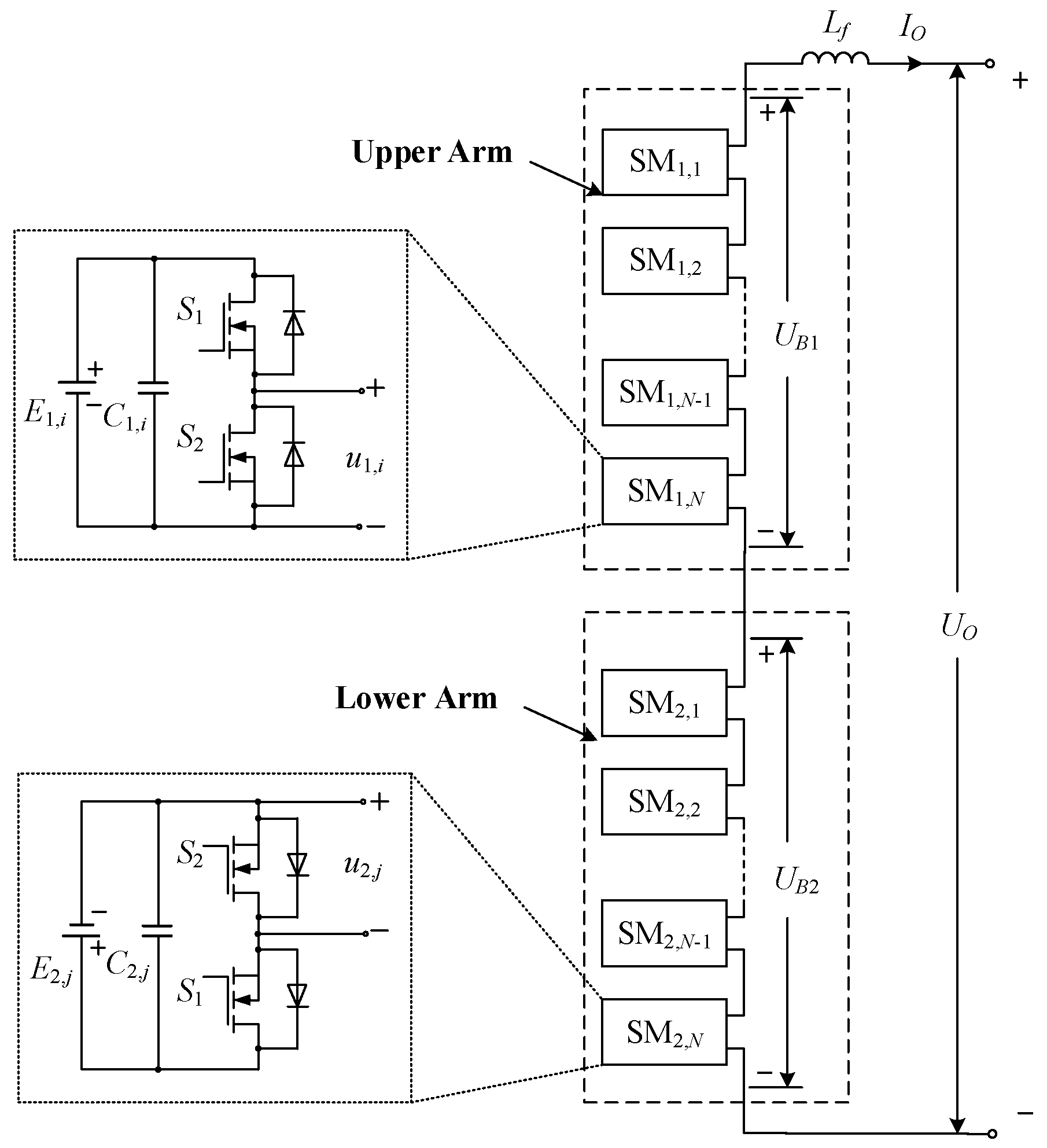

2. Fundamental Principles of the Studied Multi-Level Converter

2.1. Topology of the Studied Multi-Level Converter

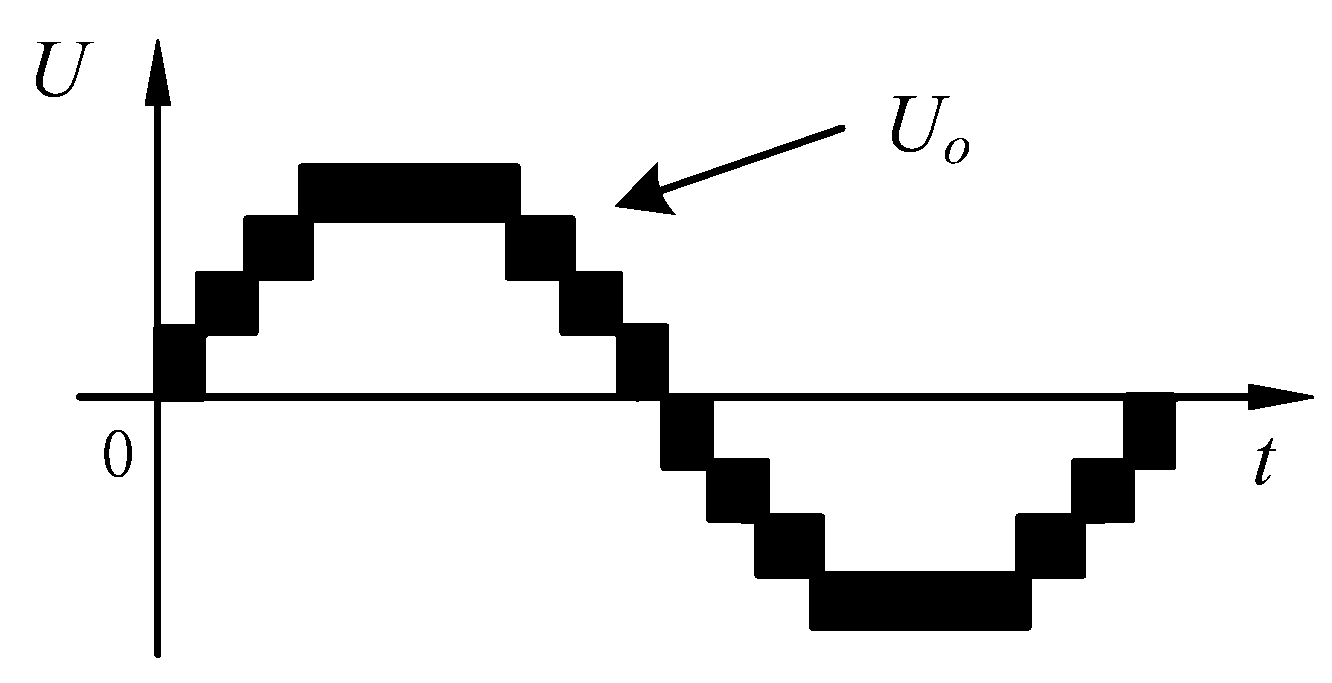

2.2. Pulse Width Modulation Mode

2.3. Battery Balancing Control

3. Analysis of Capacity Difference Tolerance

3.1. Calculation Method

3.2. Calculation Results

4. Optimization of Capacity Difference Tolerance

4.1. Modified Modulation

4.2. Optimized Results

4.3. Simulation and Verification

- Case 1: Q1,1 = Q1,2 = Q1,3 = Q1,4 =1500 mAh, under the modified SHCLS-PWM, L = 1;

- Case 2: Q1,1 = Q1,2 = Q1,3 = 1500 mAh, Q1,4 = 200 mAh, under the modified SHCLS-PWM, L = 1;

- Case 3: Q1,1 = Q1,2 = 1500 mAh, Q1,3 = 800 mAh, Q1,4 = 500 mAh, under the modified SHCLS-PWM, L = 1;

- Case 4: Q1,1 = Q1,2 = 1500 mAh, Q1,3 = 2000 mAh, Q1,4 = 3000 mAh, under the modified SHCLS-PWM, L = 1;

- Case 5: Q1,1 = 2000 mAh, Q1,2 = Q1,3 = Q1,4 = 1500 mAh, under the modified SHCLS-PWM, L = 1;

- Case 6: Q1,1 = 2000 mAh, Q1,2 = Q1,3 = Q1,4 = 1500 mAh, under the modified SHCLS-PWM, L = 2;

- Case 7: Q1,1 = 2000 mAh, Q1,2 = Q1,3 = Q1,4 = 1500 mAh, under the SHCLS-PWM;

- Case 8: Q1,1 = 2000 mAh, Q1,2 = Q1,3 = Q1,4 = 1500 mAh, under the DCCLS-PWM.

5. Conclusions

- MMH-ESC consists of two groups of reverse-connected half-bridges. Under the SHCLS-PWM, the bridge arms generate positive and negative half-wave AC voltages, respectively. In contrast, under the DCCLS-PWM, the bridge arms share the AC voltage to be output, resulting in each SM operating throughout the entire cycle. This leads to greater variation in output currents among SMs under the DCCLS-PWM.

- In the SM battery SOC balancing control strategy based on the LS-PWM, the carriers are arranged according to the battery SOCs. By utilizing the imbalance in battery charge and discharge under the LS-PWM, active SOC balancing control is performed. After obtaining the measured load current values, the SOC change rate for the given battery capacities can be calculated to determine if equilibrium can be achieved. If possible, the time required to reach the balanced state can be predicted through calculations.

- Studying and calculating the tolerance for capacity differences among batteries allows for determining the range of battery capacity values that can maintain a balanced state, without the need to restrict all batteries to the same capacity. This enhances flexibility in battery configuration and utilization.

- Finally, by combining the characteristics of the two existing modulation methods and aiming to improve capacity tolerance, a new bridge arm modulation wave allocation method is proposed. This method significantly expands the range of SM battery capacity selection and provides a high-tolerance modulation method for the converter under extreme or even fault conditions.

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Breyer, C.; Khalili, S.; Bogdanov, D.; Ram, M.; Oyewo, A.S.; Aghahosseini, A.; Sovacool, B.K. On the history and future of 100% renewable energy systems research. IEEE Access 2022, 10, 78176–78218. [Google Scholar] [CrossRef]

- Li, X.; Wang, S. Energy management and operational control methods for grid battery energy storage systems. CSEE J. Power Energy Syst. 2021, 7, 1026–1040. [Google Scholar]

- Khalid, M.R.; Khan, I.A.; Hameed, S.; Asghar, M.S.J.; Ro, J.-S. A comprehensive review on structural topologies, power levels, energy storage systems, and standards for electric vehicle charging stations and their impacts on grid. IEEE Access 2021, 9, 128069–128094. [Google Scholar] [CrossRef]

- Fang, J.; Blaabjerg, F.; Liu, S.; Goetz, S.M. A review of multilevel converters with parallel connectivity. IEEE Trans. Power Electron. 2021, 36, 12468–12489. [Google Scholar] [CrossRef]

- Yuan, X. Ultimate generalized multilevel converter topology. IEEE Trans. Power Electron. 2021, 36, 8634–8639. [Google Scholar] [CrossRef]

- Liu, Y.; Peng, F.Z. A modular multilevel converter with self-voltage balancing part II: Y-matrix modulation. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 1126–1133. [Google Scholar] [CrossRef]

- Zhang, G.; Yu, J. Open-circuit fault diagnosis for cascaded H-bridge multilevel inverter based on LS-PWM technique. CPSS Trans. Power Electron. Appl. 2021, 6, 201–208. [Google Scholar] [CrossRef]

- Jin, Y.; Xiao, Q.; Pou, J.; Jia, H.; Ji, Y.; Teodorescu, R.; Blaabjerg, F. A novel fault-tolerant operation approach for the modular multilevel converter-based STATCOM with the enhanced operation capability. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 10, 5541–5552. [Google Scholar] [CrossRef]

- Liu, J.; Dong, D. A flying capacitor hybrid modular multilevel converter with reduced number of submodules and power losses. IEEE Trans. Ind. Electron. 2023, 70, 3293–3302. [Google Scholar] [CrossRef]

- Tashakor, N.; Iraji, F.; Goetz, S.M. Low-frequency scheduler for optimal conduction loss in series/parallel modular multilevel converters. IEEE Trans. Power Electron. 2022, 37, 2551–2561. [Google Scholar] [CrossRef]

- Ma, Z.; Gao, F.; Gu, X.; Li, N.; Wu, Q.; Wang, X.; Wang, X. Multilayer SOH equalization scheme for MMC battery energy storage system. IEEE Trans. Power Electron. 2020, 35, 13514–13527. [Google Scholar] [CrossRef]

- Guo, P.; Xu, Q.; Yue, Y.; Ma, F.; He, Z.; Luo, A.; Guerrero, J. Analysis and control of modular multilevel converter with split energy storage for railway traction power conditioner. IEEE Trans. Power Electron. 2020, 35, 1239–1255. [Google Scholar] [CrossRef]

- Deng, F.; Lü, Y.; Liu, C.; Heng, Q.; Yu, Q.; Zhao, J. Overview on submodule topologies, modeling, modulation, control schemes, fault diagnosis, and tolerant control strategies of modular multilevel converters. Chin. J. Electr. Eng. 2020, 6, 1–21. [Google Scholar] [CrossRef]

- Vasiladiotis, M.; Rufer, A. Analysis and control of modular multilevel converters with integrated battery energy storage. IEEE Trans. Power Electron. 2015, 30, 163–175. [Google Scholar] [CrossRef]

- Quraan, M.; Yeo, T.; Tricoli, P. Design and control of modular multilevel converters for battery electric vehicles. IEEE Trans. Power Electron. 2016, 1, 507–517. [Google Scholar] [CrossRef]

- Rahman, S.; Meraj, M.; Iqbal, A.; Reddy, B.P.; Khan, I. A combinational level-shifted and phase-shifted PWM technique for symmetrical power distribution in CHB inverters. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 11, 932–941. [Google Scholar] [CrossRef]

- Meraj, M.; Rahman, S.; Iqbal, A.; Al Emadi, N. Novel level shifted PWM technique for unequal and equal power sharing in quasi Z-source cascaded multilevel inverter for PV systems. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 937–948. [Google Scholar] [CrossRef]

- Eroglu, F.; Kurtoglu, M.; Vural, A.M. Bidirectional DC-DC converter based multilevel battery storage systems for electric vehicle and large-scale grid applications: A critical review considering different topologies, state-of-charge balancing and future trends. IET Renew. Power Gener. 2021, 15, 915–938. [Google Scholar] [CrossRef]

- Busquets-Monge, S.; Filba-Martinez, A.; Alepuz, S.; Nicolas-Apruzzese, J.; Luque, A.; Conesa-Roca, A.; Bordonau, J. Multi-battery-fed neutral-point-clamped DC–AC converter with SOC balancing control to maximize capacity utilization. IEEE Trans. Ind. Electron. 2020, 67, 16–27. [Google Scholar] [CrossRef]

- Chen, P.; Xiao, F.; Liu, J.; Zhu, Z.; Ren, Q. Unbalanced operation principle and fast balancing charging strategy of a cascaded modular multilevel converter–bidirectional DC–DC converter in the shipboard applications. IEEE Trans. Transp. Electrif. 2020, 6, 1265–1278. [Google Scholar] [CrossRef]

- Ahmad, A.B.; Ooi, C.A.; Ishak, D. State-of-charge balancing control for optimal cell utilization of a grid-scale three-phase battery energy storage system using hybrid modular multilevel converter topology without redundant cells. IEEE Access 2021, 9, 53920–53935. [Google Scholar] [CrossRef]

- Bi, K.; Yang, W.; Xu, D.; Yan, W. Dynamic SOC balance strategy for modular energy storage system based on adaptive droop control. IEEE Access 2020, 8, 41418–41431. [Google Scholar] [CrossRef]

- Fatih, E.; Mehmet, K.; Ahmet, E.; Ahmet, M.V. A novel adaptive state-of-charge balancing control scheme for cascaded H-bridge multilevel converter based battery storage systems. ISA Trans. 2023, 135, 339–354. [Google Scholar]

- Wang, S.; Du, M.; Lu, L.; Xing, W.; Sun, K.; Ouyang, M. Multilevel energy management of a DC microgrid based on virtual-battery model considering voltage regulation and economic optimization. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 2881–2895. [Google Scholar] [CrossRef]

- Zheng, Z.; Wang, K.; Xu, L.; Li, Y. A hybrid cascaded multilevel converter for battery energy management applied in electric vehicles. IEEE Trans. Power Electron. 2014, 29, 3537–3546. [Google Scholar] [CrossRef]

- Yu, J.; Zhang, G.; Peng, M.; Song, D.; Liu, M. Power-matching based SOC balancing method for cascaded H-bridge multilevel inverter. CPSS Trans. Power Electron. Appl. 2020, 5, 352–363. [Google Scholar] [CrossRef]

- Tashakor, N.; Keshavarzi, D.; Iraji, F.; Banana, S.; Goetz, S. Voltage estimation in combination with level-adjusted phase-shifted-carrier modulation for sensorless balancing of diode-clamped modular multilevel converters. IEEE Trans. Power Electron. 2023, 38, 4267–4278. [Google Scholar] [CrossRef]

- Ye, M.; Peng, R.; Tong, Z.; Chen, Z.; Miao, Z. A generalized scheme with linear power balance and uniform switching loss for asymmetric cascaded H-bridge multilevel inverters. IEEE Trans. Power Electron. 2022, 37, 2719–2730. [Google Scholar] [CrossRef]

- Wang, W.; Ma, K.; Cai, X. Efficient capacitor voltage balancing method for modular multilevel converter under carrier-phase-shift pulse width modulation. IEEE Trans. Power Electron. 2021, 36, 1553–1562. [Google Scholar] [CrossRef]

- Wang, Q.; Hong, Z.; Deng, F.; Cheng, M.; Buja, G. A novel diagnosis strategy for switches with common electrical faults in modular multi-level half-bridge energy storage converter. IEEE Trans. Power Electron. 2023, 38, 5335–5346. [Google Scholar] [CrossRef]

| S1 State | S2 State | UA-SM Output u1,i | LA-SM Output u2,i | SM Working State |

|---|---|---|---|---|

| 1 | 0 | E1,i | −E2,i | Connected |

| 0 | 1 | 0 | 0 | Bypassed |

| Parameter | Value | Parameter | Value |

|---|---|---|---|

| N | 4 | Q1,1 (mAh) | 20~3000 |

| M | 4 | Q1,2 (mAh) | 20~3000 |

| I (A) | 4 | Q1,3 (mAh) | 20~3000 |

| ω (rad/s) | 100π | Q1,4 (mAh) | 1500 |

| φ (rad) | −0.2 | SOC1,0 (%) | 48.3310 |

| fc (Hz) | 10,000 | SOC2,0 (%) | 48.3207 |

| ∆t (s) | 0.000005 | SOC3,0 (%) | 48.3103 |

| T (s) | 10 | SOC4,0 (%) | 48.3000 |

| Case Number | Balancing Time | Error/% | |

|---|---|---|---|

| Calculation Results/s | Simulation Results/s | ||

| 1 | 1.92 | 1.87 | 2.67 |

| 2 | 2.78 | 2.69 | 3.35 |

| 3 | 4.74 | 4.53 | 4.64 |

| 4 | 1.56 | 1.55 | 0.65 |

| 5 | 3.96 | 3.90 | 1.54 |

| 6 | 2.96 | 2.94 | 0.68 |

| 7 | / | / | / |

| 8 | / | / | / |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Pan, Y.; Wang, Q.; Buja, G. An Analysis and Optimization of the Battery Capacity Difference Tolerance of the Modular Multi-Level Half-Bridge Energy Storage Converter. Energies 2023, 16, 7789. https://doi.org/10.3390/en16237789

Pan Y, Wang Q, Buja G. An Analysis and Optimization of the Battery Capacity Difference Tolerance of the Modular Multi-Level Half-Bridge Energy Storage Converter. Energies. 2023; 16(23):7789. https://doi.org/10.3390/en16237789

Chicago/Turabian StylePan, Yuhang, Qingsong Wang, and Giuseppe Buja. 2023. "An Analysis and Optimization of the Battery Capacity Difference Tolerance of the Modular Multi-Level Half-Bridge Energy Storage Converter" Energies 16, no. 23: 7789. https://doi.org/10.3390/en16237789

APA StylePan, Y., Wang, Q., & Buja, G. (2023). An Analysis and Optimization of the Battery Capacity Difference Tolerance of the Modular Multi-Level Half-Bridge Energy Storage Converter. Energies, 16(23), 7789. https://doi.org/10.3390/en16237789