Review, Comprehensive Analysis and Derivation of Analytical Power Loss Calculation Equations for Two- to Three-Level Midpoint Clamped Inverter Topologies with Hybrid Switch Configurations

Abstract

:1. Introduction

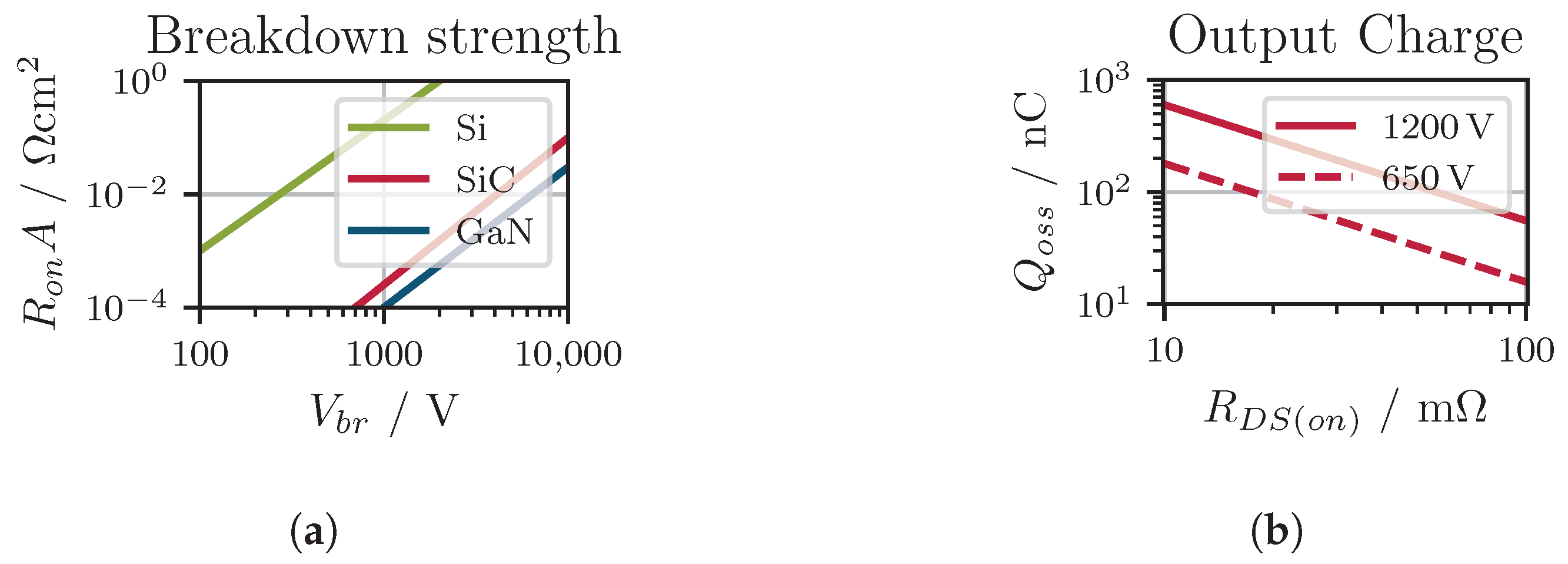

2. Inverter Circuit Topology

2.1. Two-Level Topologies

Standard Two-Level Voltage Source Inverter

2.2. Three-Level Topologies

2.2.1. Neutral-Point Clamped (NPC) Converter

2.2.2. T-Type Neutral-Point Clamped (TNPC) Converter

2.2.3. Active Neutral-Point Clamped (ANPC) Converter

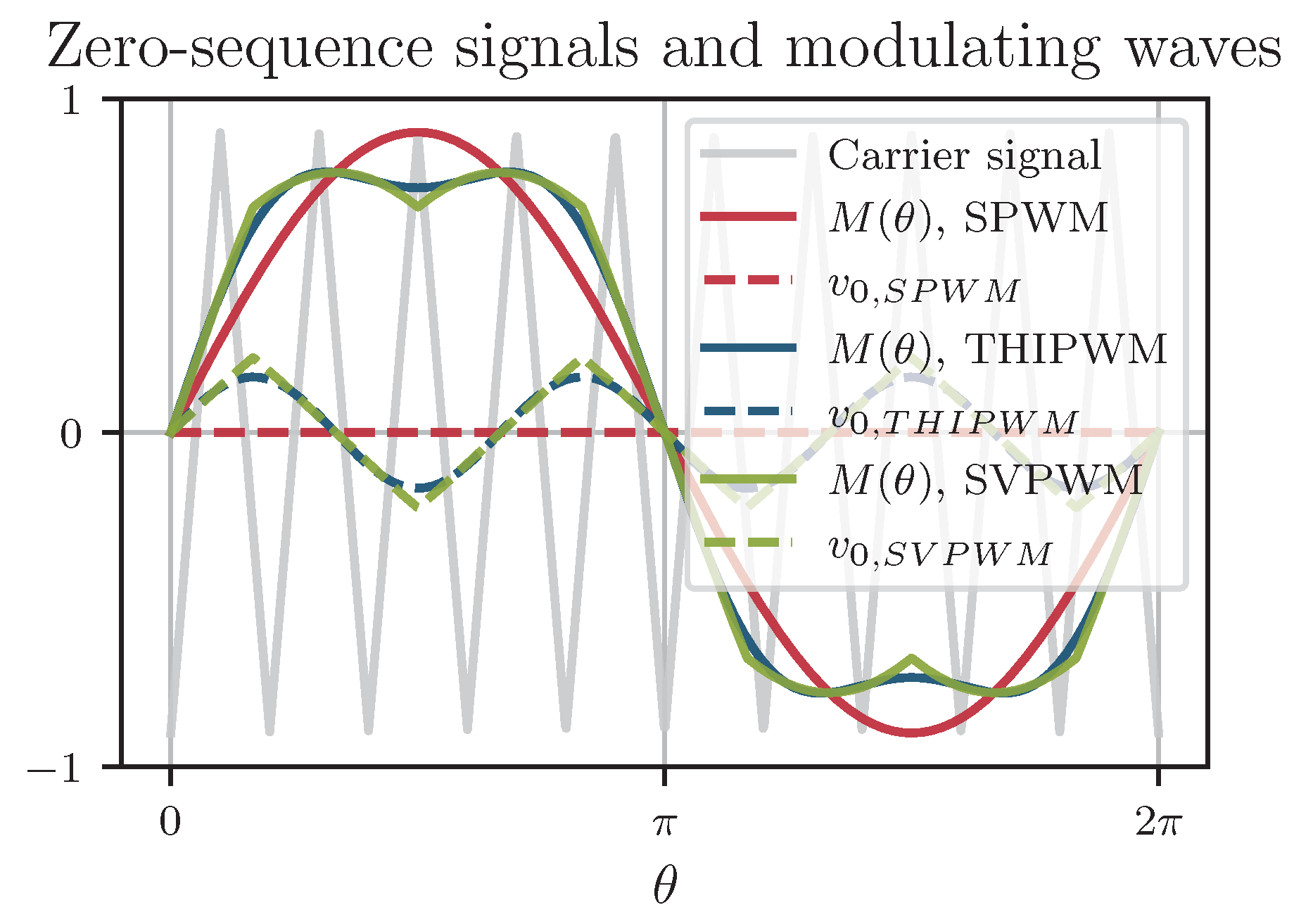

3. Modulation

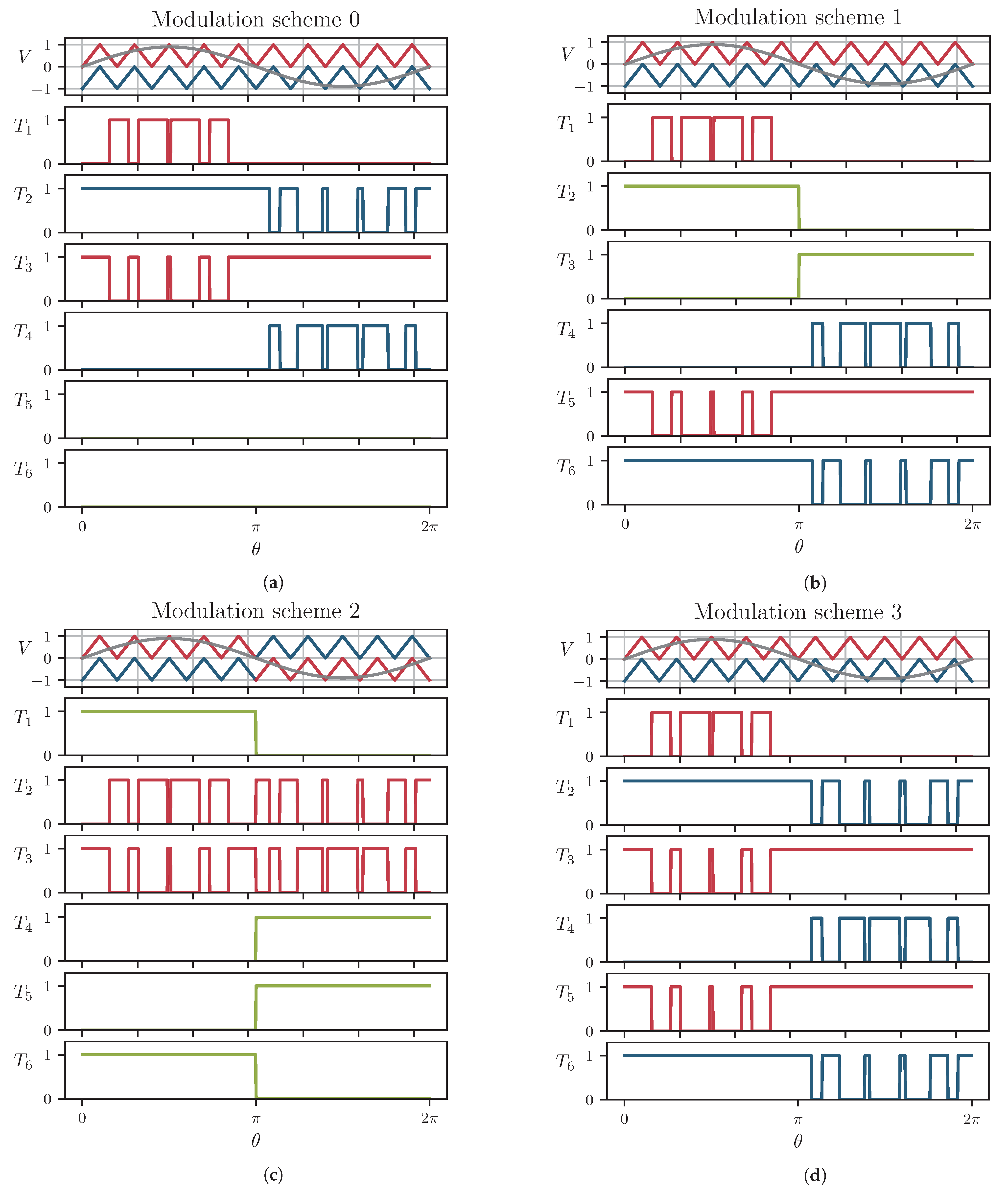

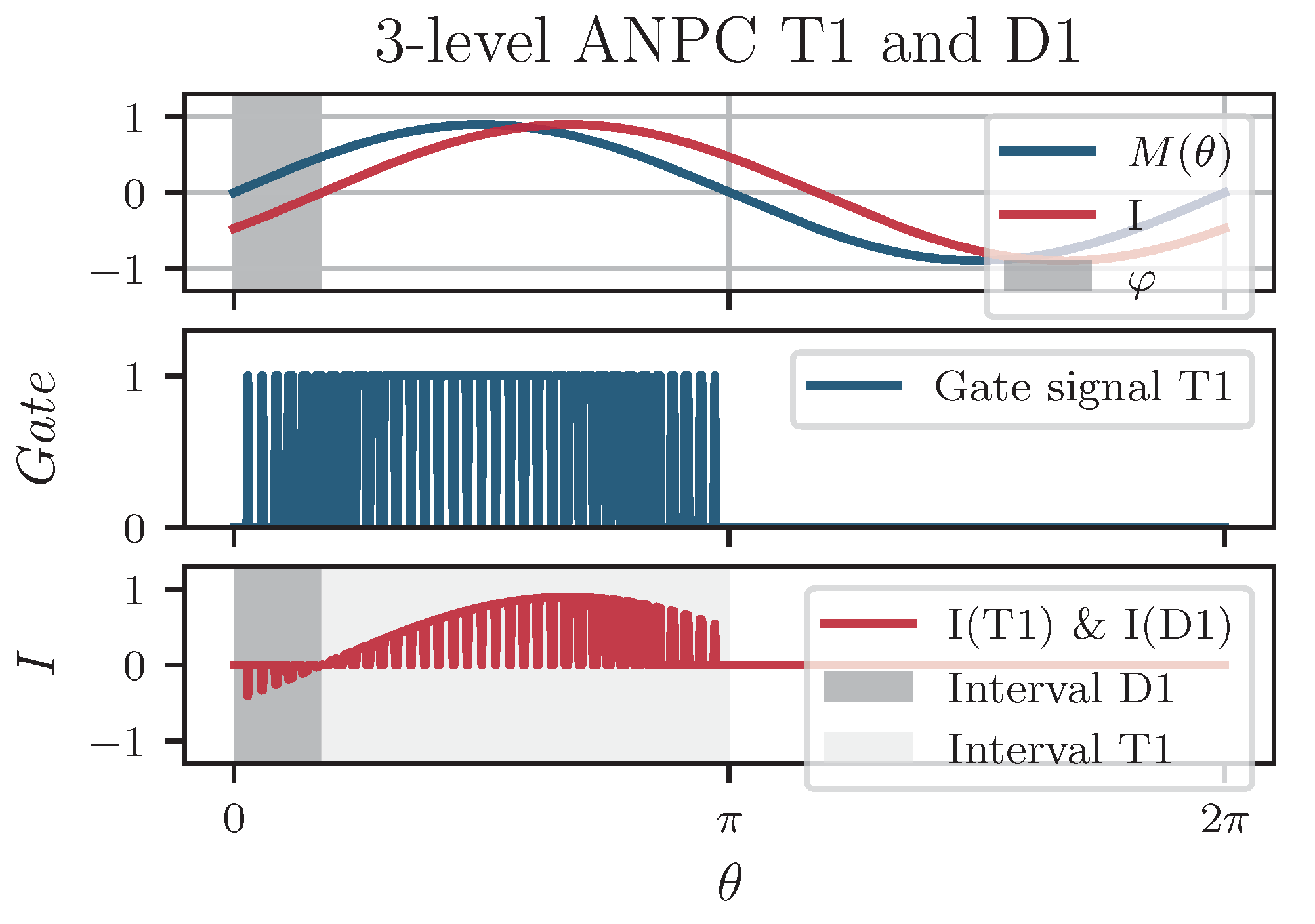

3.1. Modulation Schemes

3.2. Three-Phase Three-Level (A)NPC Modulation

3.2.1. ANPC Modulation Scheme 0

3.2.2. ANPC Modulation Scheme 1

3.2.3. ANPC Modulation Scheme 2

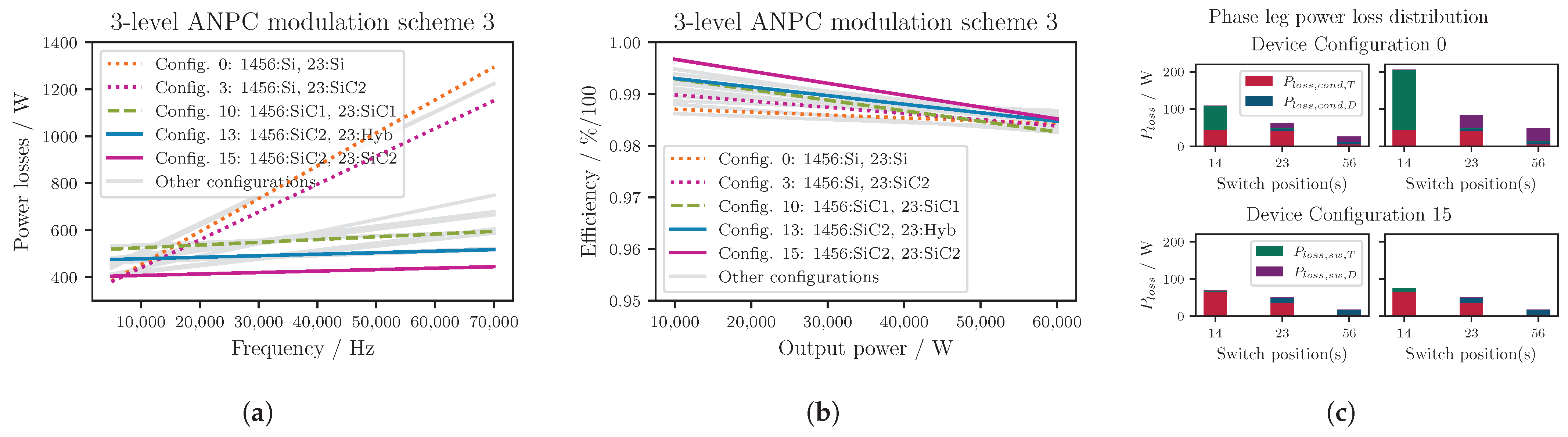

3.2.4. ANPC Modulation Scheme 3

4. Analytical Power Loss Modeling

- The constant switching frequency is assumed to be large in comparison to the fundamental frequency ().

- For the phase current, a sinusoidal waveform is assumed, not considering current ripple.

- Dead times or transistor and diode switching times are not taken into account. This may lead to a systematic underestimation of the total losses.

- There are limitations for reverse conducting power devices such as MOSFETs: current sharing between parallel paths is not taken into account.

4.1. Conduction Losses

4.2. Switching Losses

5. Application Aspects and Results

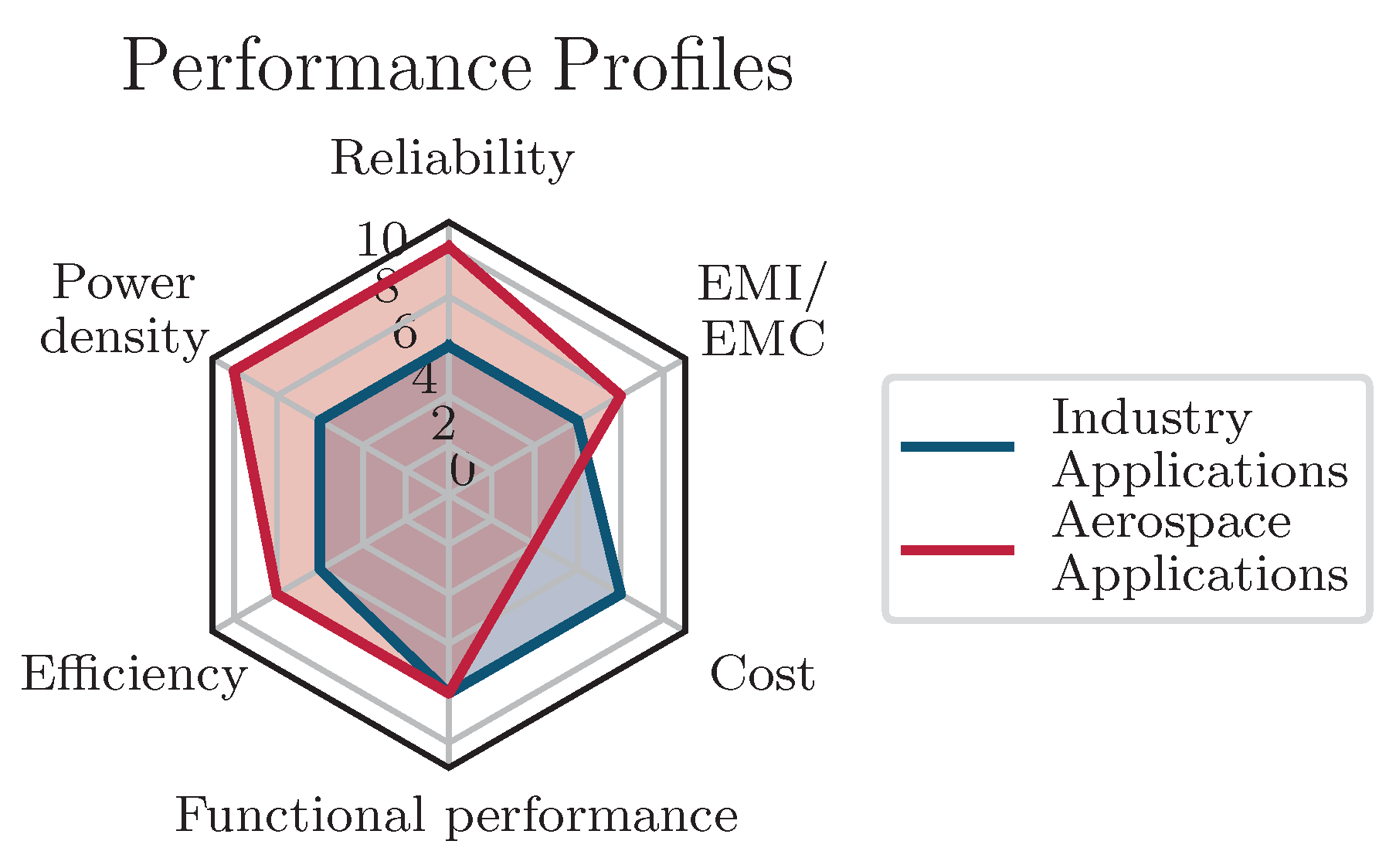

5.1. Design, Packaging, and Thermal Aspects

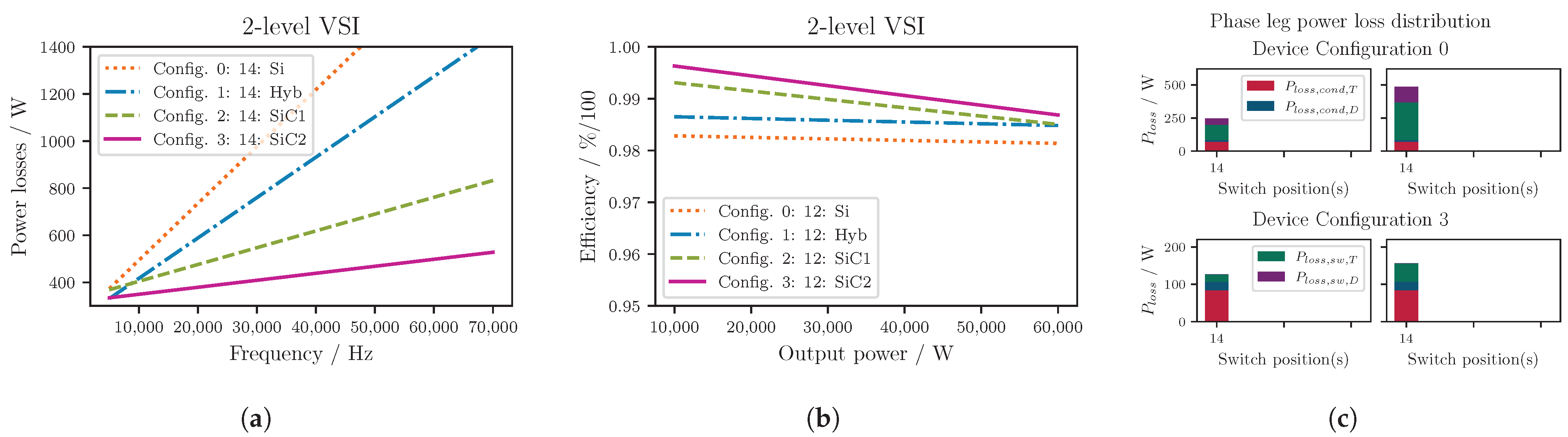

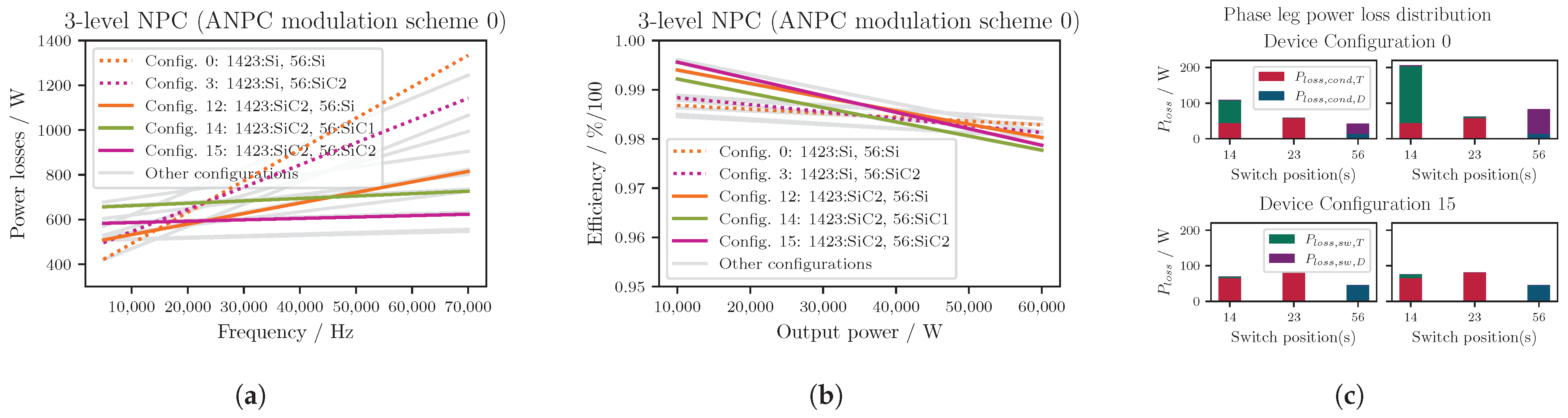

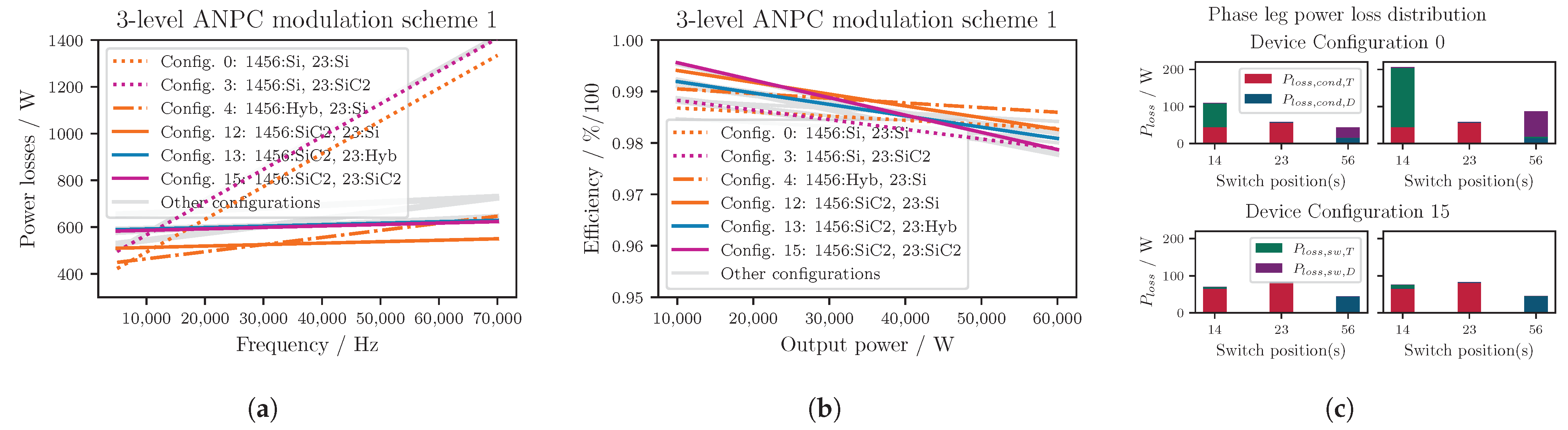

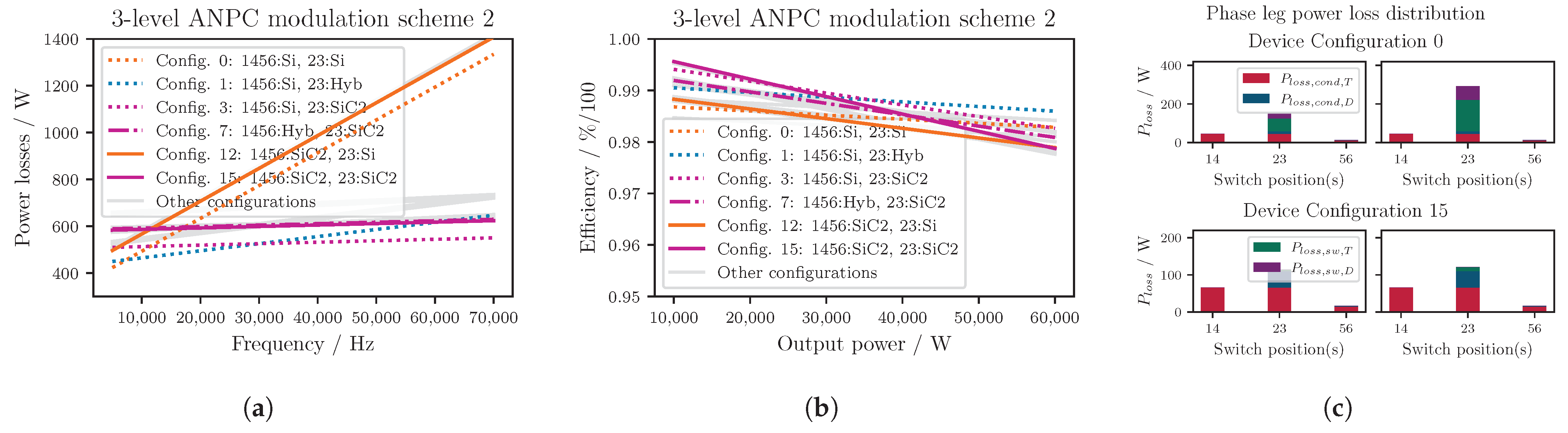

5.2. Exemplary Power Loss Analysis

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Appendix A. Conduction Loss Formulas

| Conduction Loss Formula | |

|---|---|

| B6 | |

| T1T4 | |

| D1D4 | |

| TNPC | |

| T1T4 | |

| D1D4 | |

| T2T3 | |

| D2D3 | |

| NPC | |

| T1T4 | |

| D1D4 | |

| T2T3 | |

| D2D3 | |

| D5D6 | |

| ANPC modulation scheme 1 | |

| T1T4 | |

| D1D4 | |

| T2T3 | |

| D2D3 | |

| T5T6 | |

| D5D6 | |

| ANPC modulation scheme 2 | |

| T1T4 | |

| D1D4 | |

| T2T3 | |

| D2D3 | |

| T5T6 | |

| D5D6 | |

| ANPC modulation scheme 3 | |

| T1T4 | |

| D1D4 | |

| T2T3 | |

| D2D3 | |

| T5T6 | |

| D5D6 | |

Appendix B. Implementation of Power Loss Calculation Equations

# define part one of the integrand def conduction(theta, phi, m, I_peak_phase, V_0, R_0): return (1 / (2 ∗ np.pi)) ∗ ((R_0 ∗ np.square(I_peak_phase ∗ np.sin(theta - phi))) + (V_0 ∗ I_peak_phase ∗ np.sin(theta - phi))) # define modulation function as part two of the integrand def modulation(theta, phi, m, I_peak_phase, V_0, R_0): return (m ∗ np.sin(theta)) # construct function to be integrated from two functions def integrand(∗args): return conduction(∗args) ∗ modulation(∗args) # specify integration limits for theta lower_limit = phi upper_limit = np.pi # integration using the scipy quad integration method P = quad_vec(integrand, lower_limit, upper_limit, args=(phi, m, I_peak_phase, V_0, R_0)) losses.cond, error = P

References

- Burkart, R.M. Advanced Modeling and Multi-Objective Optimization of Power Electronic Converter Systems. Ph.D. Thesis, ETH Zurich, Zurich, Switzerland, 2016. No. 23209. [Google Scholar] [CrossRef]

- Mimura, T.; Hiyamizu, S.; Fujii, T.; Nanbu, K. A New Field-Effect Transistor with Selectively Doped GaAs/n-AlxGa1-xAs Heterojunctions. Jpn. J. Appl. Phys. 1980, 19, L225. [Google Scholar] [CrossRef]

- Victor, M.; Greizer, F.; Bremicker, S.; Hübler, U. Verfahren zum Umwandeln Einer elektrischen Gleichspannung Einer Gleichspannungsquelle, Insbesondere Einer Photovoltaik-Gleichspannungsquelle in Eine Wechselspannung. Patent DE 10 2004 030 912 B3, 19 January 2006. [Google Scholar]

- Bruckner, T.; Bernet, S.; Guldner, H. The active NPC converter and its loss-balancing control. IEEE Trans. Ind. Electron. 2005, 52, 855–868. [Google Scholar] [CrossRef]

- Schefer, H.; Fauth, L.; Kopp, T.H.; Mallwitz, R.; Friebe, J.; Kurrat, M. Discussion on Electric Power Supply Systems for All Electric Aircraft. IEEE Access 2020, 8, 84188–84216. [Google Scholar] [CrossRef]

- Kolar, J.W. Power Electronics Design 4.0. In Proceedings of the IEEE Design Automation for Power Electronics Workshop, Portland, OR, USA, 22 September 2018. [Google Scholar]

- Hanisch, L.V.; Eisele, L.; Lünne, K.; Henke, M. Modeling of Transient Overvoltages in Inverter-fed Machines with Hairpin Winding. In Proceedings of the 2022 International Symposium on Power Electronics, Electrical Drives, Automation and Motion (SPEEDAM), Sorrento, Italy, 22–24 June 2022; pp. 605–609. [Google Scholar] [CrossRef]

- Wintrich, A.; Nicolai, U.; Tursky, W.; Reimann, T. Application Manual Power Semiconductors; SEMIKRON International GmbH: Nuremberg, Germany, 2011. [Google Scholar]

- Ebersberger, J.; Hagedorn, M.; Lorenz, M.; Mertens, A. Potentials and Comparison of Inverter Topologies for Future All-Electric Aircraft Propulsion. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 10, 5264–5279. [Google Scholar] [CrossRef]

- Nawawi, A.; Tong, C.F.; Yin, S.; Sakanova, A.; Liu, Y.; Liu, Y.; Kai, M.; See, K.Y.; Tseng, K.J.; Simanjorang, R.; et al. Design and Demonstration of High Power Density Inverter for Aircraft Applications. IEEE Trans. Ind. Appl. 2017, 53, 1168–1176. [Google Scholar] [CrossRef]

- Wu, B. High-Power Converters and AC Drives; John Wiley & Sons Ltd.: Hoboken, NJ, USA, 2006. [Google Scholar] [CrossRef]

- Meynard, T.; Foch, H. Multi-level conversion: High voltage choppers and voltage-source inverters. In Proceedings of the PESC ’92 Record. 23rd Annual IEEE Power Electronics Specialists Conference, Toledo, Spain, 29 June–3 July 1992; Volume 1, pp. 397–403. [Google Scholar] [CrossRef]

- Krug, D. Vergleichende Untersuchungen von Mehrpunkt-Schaltungstopologien mit zentralem Gleichspannungszwischenkreis für Mittelspannungsanwendungen. Ph.D. Thesis, Dresden University of Technology, Dresden, Germany, 2016. [Google Scholar]

- Rohner, G.; Kolar, J.W.; Bortis, D.; Schweizer, M. Optimal Level Number and Performance Evaluation of Si/GaN Multi-Level Flying Capacitor Inverter for Variable Speed Drive Systems. In Proceedings of the 2022 25th International Conference on Electrical Machines and Systems (ICEMS), Chiang Mai, Thailand, 29 November–2 December 2022; pp. 1–6. [Google Scholar] [CrossRef]

- Hoffmann Sathler, H. Optimization of GaN-Based Series-Parallel Multilevel Three-Phase Inverter for Aircraft Applications. Ph.D. Thesis, Université Paris-Saclay, Gif-sur-Yvette, France, 2021. [Google Scholar]

- Pallo, N.; Foulkes, T.; Modeer, T.; Coday, S.; Pilawa-Podgurski, R. Power-dense multilevel inverter module using interleaved GaN-based phases for electric aircraft propulsion. In Proceedings of the 2018 IEEE Applied Power Electronics Conference and Exposition (APEC), San Antonio, TX, USA, 4–8 March 2018; pp. 1656–1661. [Google Scholar] [CrossRef]

- Hartwig, R.; Hensler, A.; Ellinger, T. Performance Evaluation of a GaN Flying Capacitor Multilevel Inverter for Industrial Applications. In Proceedings of the CIPS 2022—12th International Conference on Integrated Power Electronics Systems, Berlin, Germany, 15–17 March 2022; pp. 1–9. [Google Scholar]

- Fauth, L.; Beckemeier, C.; Friebe, J. A Hybrid Active Neutral Point Clamped Converter consisting of Si IGBTs and GaN HEMTs for Auxiliary Systems of Electric Aircraft. In Proceedings of the 2021 IEEE Energy Conversion Congress and Exposition (ECCE), Virtual, 10–14 October 2021; pp. 1917–1923. [Google Scholar] [CrossRef]

- Bierhoff, M.; Fuchs, F. Semiconductor losses in voltage source and current source IGBT converters based on analytical derivation. In Proceedings of the 2004 IEEE 35th Annual Power Electronics Specialists Conference, Aachen, Germany, 20–25 June 2004; Volume 4, pp. 2836–2842. [Google Scholar] [CrossRef]

- Soeiro, T.B.; Kolar, J.W. The New High-Efficiency Hybrid Neutral-Point-Clamped Converter. IEEE Trans. Ind. Electron. 2013, 60, 1919–1935. [Google Scholar] [CrossRef]

- Dodge, J. 3L-ANPC vs. 3L-NPC Inverters; United Silicon Carbide: Monmouth Junction, NJ, USA, 2021; Revision 3. [Google Scholar]

- Haering, J.; Gleissner, M.; Wondrak, W.; Hepp, M.; Bakran, M.M. Analytical Loss Calculation for ANPC Converters in Electric Drive Applications Using Different Modulation Strategies to Determine Efficiency and Overall Cost. In Proceedings of the PCIM Europe Digital Days 2020—International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Virtual, 7–8 July 2020; pp. 1–8. [Google Scholar]

- Yapa, R.; Forsyth, A.; Todd, R. Analysis of SiC technology in two-level and three-level converters for aerospace applications. In Proceedings of the 7th IET International Conference on Power Electronics, Machines and Drives (PEMD 2014), Manchester, UK, 8–10 April 2014; pp. 1–6. [Google Scholar] [CrossRef]

- Cacciato, M.; Aiello, G.; Gennaro, F.; Mita, S.; Patti, D.; Scelba, G.; Sujeeth, A. Power Loss Modelling of GaN HEMT based 3L ANPC Three Phase Inverter for different PWM Techniques. In Proceedings of the 24th European Conference on Power Electronics and Applications (IEEE EPE 2022 ECCE Europe), Hanover, Germany, 5–9 September 2022. [Google Scholar] [CrossRef]

- Pan, D.; Chen, M.; Wang, X.; Wang, H.; Blaabjerg, F.; Wang, W. EMI Modeling of Three-Level Active Neutral-Point-Clamped SiC Inverter Under Different Modulation Schemes. In Proceedings of the 2019 10th International Conference on Power Electronics and ECCE Asia (ICPE 2019—ECCE Asia), Busan, Republic of Korea, 27–30 May 2019; pp. 1–6. [Google Scholar] [CrossRef]

- Schittler, A.C.; Müller, C.R. Loss-optimized active neutral-point clamped inverter in a low-inductive power-module design. In Proceedings of the PCIM Europe Digital Days 2020—International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Virtual, 7–8 July 2020. [Google Scholar]

- Schweizer, M.; Friedli, T.; Kolar, J.W. Comparative Evaluation of Advanced Three-Phase Three-Level Inverter/Converter Topologies Against Two-Level Systems. IEEE Trans. Ind. Electron. 2013, 60, 5515–5527. [Google Scholar] [CrossRef]

- Gammeter, C.; Krismer, F.; Kolar, J.W. Weight and efficiency analysis of switched circuit topologies for modular power electronics in MEA. In Proceedings of the IECON 2016—42nd Annual Conference of the IEEE Industrial Electronics Society, Florence, Italy, 23–26 October 2016; pp. 3640–3647. [Google Scholar] [CrossRef]

- Sathler, H.H.; Nagano, L.; Cougo, B.; Costa, F.; Labrousse, D. Impact of multilevel converters on EMC filter weight of a 70 kVA power drive system for More Electrical Aircraft. In Proceedings of the CIPS 2020—11th International Conference on Integrated Power Electronics Systems, Berlin, Germany, 24–26 March 2020; pp. 1–8. [Google Scholar]

- Kaminski, N.; Hilt, O. WBG Status and Future Directions. In Proceedings of the ECPE SiC & GaN User Forum: Potential of Wide Bandgap Semiconductors in Power Electronic Applications, Munich, Germany, 30 June–1 July 2021. [Google Scholar]

- Cittanti, D.; Guacci, M.; Mirić, S.; Bojoi, R.; Kolar, J.W. Comparative Evaluation of 800V DC-Link Three-Phase Two/Three-Level SiC Inverter Concepts for Next-Generation Variable Speed Drives. In Proceedings of the 2020 23rd International Conference on Electrical Machines and Systems (ICEMS), Hamamatsu, Japan, 24–27 November 2020; pp. 1699–1704. [Google Scholar] [CrossRef]

- Schweizer, M.; Kolar, J.W. Design and Implementation of a Highly Efficient Three-Level T-Type Converter for Low-Voltage Applications. IEEE Trans. Power Electron. 2013, 28, 899–907. [Google Scholar] [CrossRef]

- Kampen, D.; Parspour, N.; Beyer, S. Efficiency of Motor Side Common Mode (CM) Filtering Techniques for PWM Inverters. In Proceedings of the PCIM Europe 2009 Conference, Nuremberg, Germany, 12–14 May 2009; ISBN 9783800731589. [Google Scholar]

- Kampen, D. Considering mutual impacts of differential mode and common mode emissions in motor filter design for PWM inverters. In Proceedings of the 2009 13th European Conference on Power Electronics and Applications, EPE ’09, Barcelona, Spain, 8–10 September 2009. [Google Scholar]

- Staudt, I. Application Note AN-11001—3L NPC & TNPC Topology; Technical Report; SEMIKRON International GmbH: Nuremberg, Germany, 2015. [Google Scholar]

- Jayakumar, V.; Chokkalingam, B.; Munda, J.L. A Comprehensive Review on Space Vector Modulation Techniques for Neutral Point Clamped Multi-Level Inverters. IEEE Access 2021, 9, 112104–112144. [Google Scholar] [CrossRef]

- Nabae, A.; Takahashi, I.; Akagi, H. A New Neutral-Point-Clamped PWM Inverter. IEEE Trans. Ind. Appl. 1981, IA-17, 518–523. [Google Scholar] [CrossRef]

- Rodriguez, J.; Bernet, S.; Steimer, P.K.; Lizama, I.E. A Survey on Neutral-Point-Clamped Inverters. IEEE Trans. Ind. Electron. 2010, 57, 2219–2230. [Google Scholar] [CrossRef]

- Hava, A.; Kerkman, R.; Lipo, T. A high-performance generalized discontinuous PWM algorithm. IEEE Trans. Ind. Appl. 1998, 34, 1059–1071. [Google Scholar] [CrossRef]

- Mendes, C.C.; Sathler, H.H.; Cougo, B.; Stopa, M.M.; Costa, F.; Labrousse, D. Impact of PWM Techniques in Efficiency and Power Density of a 70kVA Multilevel Inverter for More Electric Aircrafts. In Proceedings of the 2021 23rd European Conference on Power Electronics and Applications (EPE’21 ECCE Europe), Virtual, 6–10 September 2021. [Google Scholar] [CrossRef]

- Chokkalingham, B.; Padmanaban, S.; Blaabjerg, F. Investigation and Comparative Analysis of Advanced PWM Techniques for Three-Phase Three-Level NPC-MLI Drives. Electr. Power Components Syst. 2018, 46, 258–269. [Google Scholar] [CrossRef]

- Kersten, A.; Oberdieck, K.; Bubert, A.; Neubert, M.; Grunditz, E.A.; Thiringer, T.; De Doncker, R.W. Fault Detection and Localization for Limp Home Functionality of Three-Level NPC Inverters With Connected Neutral Point for Electric Vehicles. IEEE Trans. Transp. Electrif. 2019, 5, 416–432. [Google Scholar] [CrossRef]

- Cao, Y.; Fauth, L.; Mertens, A.; Friebe, J. Comparison and Analysis of Multi-State Reliability of Fault-Tolerant Inverter Topologies for the Electric Aircraft Propulsion System. In Proceedings of the 2021 24th International Conference on Electrical Machines and Systems (ICEMS), Gyeongju, Republic of Korea, 31 October–3 November 2021; pp. 766–771. [Google Scholar] [CrossRef]

- Lenze, A.; Levett, D.; Zheng, Z.; Mainka, K.; Technologies, I. Hard Paralleling SiC MOSFET Based Power Modules; Bodo’s Power Systems: Laboe, Germany, 2020; pp. 26–28. [Google Scholar]

- Langmaack, N. Optimierung leistungselektronischer Wandler in Fahrzeugantriebssträngen basierend auf Siliziumkarbidleistungshalbleitern. Ph.D. Thesis, Institute for Electrical Machines, Traction and Drives, Technische Universität Braunschweig, Braunschweig, Germany, 2022. [Google Scholar]

- Tareilus, G.H. Der Auxiliary resonant commutated pole inverter im Umfeld schaltverlustreduzierter IGBT-Pulswechselrichter. Ph.D. Thesis, Institute for Electrical Machines, Traction and Drives, Technische Universität Braunschweig, Braunschweig, Germany, 2002. [Google Scholar]

- Volke, A.; Hornkamp, M. IGBT Modules Technologies, Driver and Application; Infineon Technologies AG: Munich, Germany, 2015. [Google Scholar]

- Poorfakhraei, A.; Narimani, M.; Emadi, A. A Review of Multilevel Inverter Topologies in Electric Vehicles: Current Status and Future Trends. IEEE Open J. Power Electron. 2021, 2, 155–170. [Google Scholar] [CrossRef]

- Schittler, A.C.; Heer, D.; Mueller, C.R. Interaction of power-module design and modulation scheme for active neutral-point-clamped inverters. In Proceedings of the PCIM Europe 2019; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 7–9 May 2019; pp. 1–7. [Google Scholar]

- Infineon Technologies. F3L11MR12W2M1_B74 EasyPACK™ Module. 2022. Revision 0.20. Available online: https://www.infineon.com/dgdl/Infineon-F3L11MR12W2M1_B74-DataSheet-v00_20-DE.pdf?fileId=8ac78c8c80f4d32901814c8e7865287b (accessed on 1 September 2023).

- Schefer, H.; Canders, W.R.; Hoffmann, J.; Mallwitz, R.; Henke, M. Cryogenically-Cooled Power Electronics for Long-Distance Aircraft. IEEE Access 2022, 10, 133279–133308. [Google Scholar] [CrossRef]

- Fischer, D.; Rohn, R.; Mallwitz, R. Comparative Implementation of a two-stage DC-Link. In Proceedings of the PCIM Europe 2022—International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 10–12 May 2022; pp. 1–8. [Google Scholar] [CrossRef]

- Qasim, M.M.; Otten, D.M.; Spakovszky, Z.S.; Lang, J.H.; Kirtley, J.L.; Perreault, D.J. Design and Optimization of an Inverter for a One-Megawatt Ultra-Light Motor Drive. In Proceedings of the AIAA AVIATION 2023 Forum, Manchester, UK, 12–16 June 2023. [Google Scholar] [CrossRef]

- Li, Y.; Gong, L.; Xu, M.; Joshi, Y. Thermal Performance Analysis of Biporous Metal Foam Heat Sink. J. Heat Transf. 2017, 139, 052005-1–052005-8. [Google Scholar] [CrossRef]

- Lv, Y.G.; Zhang, G.P.; Wang, Q.W.; Chu, W.X. Thermal Management Technologies Used for High Heat Flux Automobiles and Aircraft: A Review. Energies 2022, 15, 8316. [Google Scholar] [CrossRef]

- AG, S. Siemens eAircraft—Disrupting the Way You Will Fly! 2018. Available online: https://www.ie-net.be/sites/default/files/Siemens%20eAircraft%20-%20Disrupting%20Aircraft%20Propulsion%20-%20OO%20JH%20THO%20-%2020180427.cleaned.pdf (accessed on 1 September 2022).

- Piessens, R.; de Doncker-Kapenga, E.; Überhuber, C.W.; Kahaner, D.K. Guidelines for the Use of QUADPACK. In Quadpack: A Subroutine Package for Automatic Integration; Springer: Berlin/Heidelberg, Germany, 1983; pp. 75–111. [Google Scholar] [CrossRef]

| Available Voltage Classes | Switching Frequency Range | Output Power Range | |

|---|---|---|---|

| Si IGBTs | up to 6.5 kV | up to 100 kHz | up to several hundred kilowatts |

| Si SJ MOSFETs | up to 950 V | up to 1 MHz | up to several kilowatts |

| SiC MOSFETs | 650 V up to 3.3 kV | up to 1 MHz | up to several hundred kilowatts |

| GaN eHEMTs | up to 650 V | up to 10 MHz | up to several kilowatts |

| Switch | B6 | TNPC | NPC (ANPC MS0) | ||||

|---|---|---|---|---|---|---|---|

| T1T4 | Conduction interval | ||||||

| Modulation function | |||||||

| D1D4 | Conduction interval | ||||||

| Modulation function | |||||||

| T2T3 | Conduction interval | ||||||

| Modulation function | 1 | ||||||

| D2D3 | Conduction interval | ||||||

| Modulation function | |||||||

| T5T6 | Conduction interval | ||||||

| Modulation function | |||||||

| D5D6 | Conduction interval | ||||||

| Modulation function | |||||||

| Switch | ANPC MS1 | ANPC MS2 | ANPC MS3 | ||||

|---|---|---|---|---|---|---|---|

| T1T4 | Conduction interval | ||||||

| Modulation function | |||||||

| D1D4 | Conduction interval | ||||||

| Modulation function | |||||||

| T2T3 | Conduction interval | ||||||

| Modulation function | 1 | ||||||

| D2D3 | Conduction interval | ||||||

| Modulation function | |||||||

| T5T6 | Conduction interval | ||||||

| Modulation function | |||||||

| D5D6 | Conduction interval | ||||||

| Modulation function | |||||||

| Switch | B6 | TNPC | NPC | ANPC MS1 | ANPC MS2 | ANPC MS3 | |

|---|---|---|---|---|---|---|---|

| T1T4 | Switching Loss Interval | - | |||||

| Resulting Factor | 0 | ||||||

| D1D4 | Switching Loss Interval | - | |||||

| Resulting Factor | 0 | ||||||

| T2T3 | Switching Loss Interval | - | |||||

| Resulting Factor | 0 | ||||||

| D2D3 | Switching Loss Interval | - | - | ||||

| Resulting Factor | 0 | 0 | |||||

| T5T6 | Switching Loss Interval | - | |||||

| Resulting Factor | 0 | ||||||

| D5D6 | Switching Loss Interval | - | |||||

| Resulting Factor | 0 |

| Transitor Parameters | Diode Parameters | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Config. | Description | Device | |||||||||||

| V | A | V | m | mJ | mJ | A | V | m | mJ | V A | |||

| 650 | Si | Si IGBT with copacked Si FRD | Infineon IKW75N65ET7 | 79 | 0.8 | 9 | 3.45 | 2.05 | 74 | 1.0 | 7.50 | 1.76 | 400 75 |

| 650 | Hyb | Si IGBT with copacked SiC SBD | Infineon IKW75N65RH | 75 | 1.5 | 7 | 0.45 | 0.40 | 31 | 0.7 | 27.5 | 0.00 | 400 37.5 |

| 650 | SiC1 | SiC MOSFET and its body diode | Wolfspeed C3M0025065K | 70 | 0.0 | 33 | 0.12 | 0.05 | 52 | 5.2 | 25.7 | 0.12 | 400 33.5 |

| 650 | SiC2 | SiC MOSFET with additional SiC SBD | Wolfspeed C3M0025065K and Wolfspeed C3D16065A | 70 | 0.0 | 33 | 0.07 | 0.08 | 39 | 0.8 | 80.0 | 0.00 | 400 33.5 |

| 1200 | Si | Si IGBT with copacked Si FRD | Infineon IKZA75N120CH7 | 94 | 1.5 | 6 | 3.16 | 4.04 | 75 | 1.7 | 11.5 | 2.93 | 600 75 |

| 1200 | Hyb | Si IGBT with additional SiC SBD | Infineon IKZA75N120CH7 and Infineon IDWD40G120C5 | 94 | 1.5 | 6 | 3.16 | 4.04 | 51 | 0.9 | 21.7 | 0.00 | 600 75 |

| 1200 | SiC1 | SiC MOSFET and its body diode | Wolfspeed C3M0021120K | 74 | 0.0 | 38 | 1.58 | 0.34 | 90 | 4.1 | 14.0 | 0.74 | 800 50 |

| 1200 | SiC2 | SiC MOSFET with additional SiC SBD | Wolfspeed C3M0021120K and Wolfspeed C4D20120A | 74 | 0.0 | 38 | 0.69 | 0.42 | 55 | 0.7 | 76.0 | 0.00 | 800 50 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Radomsky, L.; Mallwitz, R. Review, Comprehensive Analysis and Derivation of Analytical Power Loss Calculation Equations for Two- to Three-Level Midpoint Clamped Inverter Topologies with Hybrid Switch Configurations. Energies 2023, 16, 6710. https://doi.org/10.3390/en16186710

Radomsky L, Mallwitz R. Review, Comprehensive Analysis and Derivation of Analytical Power Loss Calculation Equations for Two- to Three-Level Midpoint Clamped Inverter Topologies with Hybrid Switch Configurations. Energies. 2023; 16(18):6710. https://doi.org/10.3390/en16186710

Chicago/Turabian StyleRadomsky, Lukas, and Regine Mallwitz. 2023. "Review, Comprehensive Analysis and Derivation of Analytical Power Loss Calculation Equations for Two- to Three-Level Midpoint Clamped Inverter Topologies with Hybrid Switch Configurations" Energies 16, no. 18: 6710. https://doi.org/10.3390/en16186710

APA StyleRadomsky, L., & Mallwitz, R. (2023). Review, Comprehensive Analysis and Derivation of Analytical Power Loss Calculation Equations for Two- to Three-Level Midpoint Clamped Inverter Topologies with Hybrid Switch Configurations. Energies, 16(18), 6710. https://doi.org/10.3390/en16186710