1. Introduction

The Internet of Things, or IoT, is typically perceived as a system of a large number of interrelated computing devices, often constituting a kind of cyberphysical system. It is often made up of elements (IoT nodes) that are inexpensive terminals, with an important feature of optimized energy efficiency of operation [

1]. The general concept of the IoT includes many possibilities for designing the hardware and software of the system. There is no single unified IoT architecture, and there is no common definition of communication protocols for IoT parts. While developers use existing technologies to build the IoT, research groups are still working to adapt protocols and improve communication quality and energy efficiency [

1,

2].

The IoT nodes that make up the bottom level of the system are typically battery-powered devices based on embedded low-power processors (microcontrollers) with limited processing capabilities. When the system requires a wireless communication protocol, the energy efficiency of such embedded devices could be highly dependent on the energy efficiency of the data communication protocol. Since the messages sent from/to constrained IoT nodes are typically relatively short, the important factor is also the activity time of the CPU and radio modem, in relation to the inactivity time (when the device is in sleep mode). Due to the limited resources of the processing units of the IoT nodes, efficient communication protocols are desired to enable communication with reasonable energy efficiency.

The effectiveness and reliability of communication depend heavily on the error control coding (ECC) mechanism used. Numerous effective coding schemes, such as LDPC coding [

3], turbo coding [

4] and polar coding [

5], have been developed in recent years. One problem with the implementation of these schemes is that they they require computationally demanding iterative algorithms for decoding. These coding schemes are typically utilized in complex communication protocols such as WiFi, WiMAX and 5G, with high-performance computing hardware required for implementation.

In the case of a time-varying communication channel, additional improvement in the uplink transmission efficiency can be obtained if a properly designed rate-adaptive or rateless system is employed, because of the two limitations of the traditional fixed-rate coding, inherently designed for a specific channel noise level (or SNR, signal-to-noise ratio). First, if the SNR is significantly higher than the level that the fixed-rate code has been designed for, then the rate-adaptive code can correct error with higher rate, which means a lower number of coded bits must be encoded and delivered. Second, if, on the other hand, the SNR is significantly lower than expected, then the fixed-rate code fails to provide sufficient redundancy to combat channel corruptions, while the rate-adaptive code can adapt and provide such additional redundancy.

Rateless codes are a class of ECC that can generate an unlimited number of coded bits given a finite number of information bits. It is the core of Hybrid ARQ (HARQ) protocols, which allows for efficient transmission of signals over a channel that changes over time. The system’s transmitter first sends the high-rate codeword of the necessary size over the channel. If the receiver cannot decode the received noisy codeword, the transmitter then sends repeated or additional parity symbols to the receiver to allow the receiver to attempt another round of decoding, but now with a higher redundancy level. The process continues until the decoder successfully decodes the received codewords. HARQ can be classified into two main types: type-I with chase-combining (CC) and type-II with incremental redundancy (IR). The type-II IR provides superior throughput performance to CC-HARQ, due to the retransmission of only incremental parity bits, when required [

6,

7]; therefore, we consider IR HARQ in this research.

The important and well-investigated case of rateless codes is Raptor coding [

8]. A Raptor code is a concatenation of a high-rate LDPC outer code and a rateless Luby transform (LT) inner code. Raptor codes are shown to achieve the capacity of the binary erasure channel (BEC), while research to design them for the additive white Gaussian noise (AWGN) channel is already quite advanced [

9,

10,

11]. While LT codes and Raptor codes share some similarities with LDPC codes, more closely related to LDPC are protograph-based Raptor-Like (PBRL) LDPC codes [

12,

13]. Unlike the Raptor codes, in the PBRL scheme, a high-rate LDPC codeword is transmitted directly as the initial block, and additional parity symbols are sent only if necessary. PBRL-LDPC codes are well suited for low-complexity encoder implementation, because the well-known LDPC and QC-LDPC efficient encoding schemes can be adapted [

14,

15].

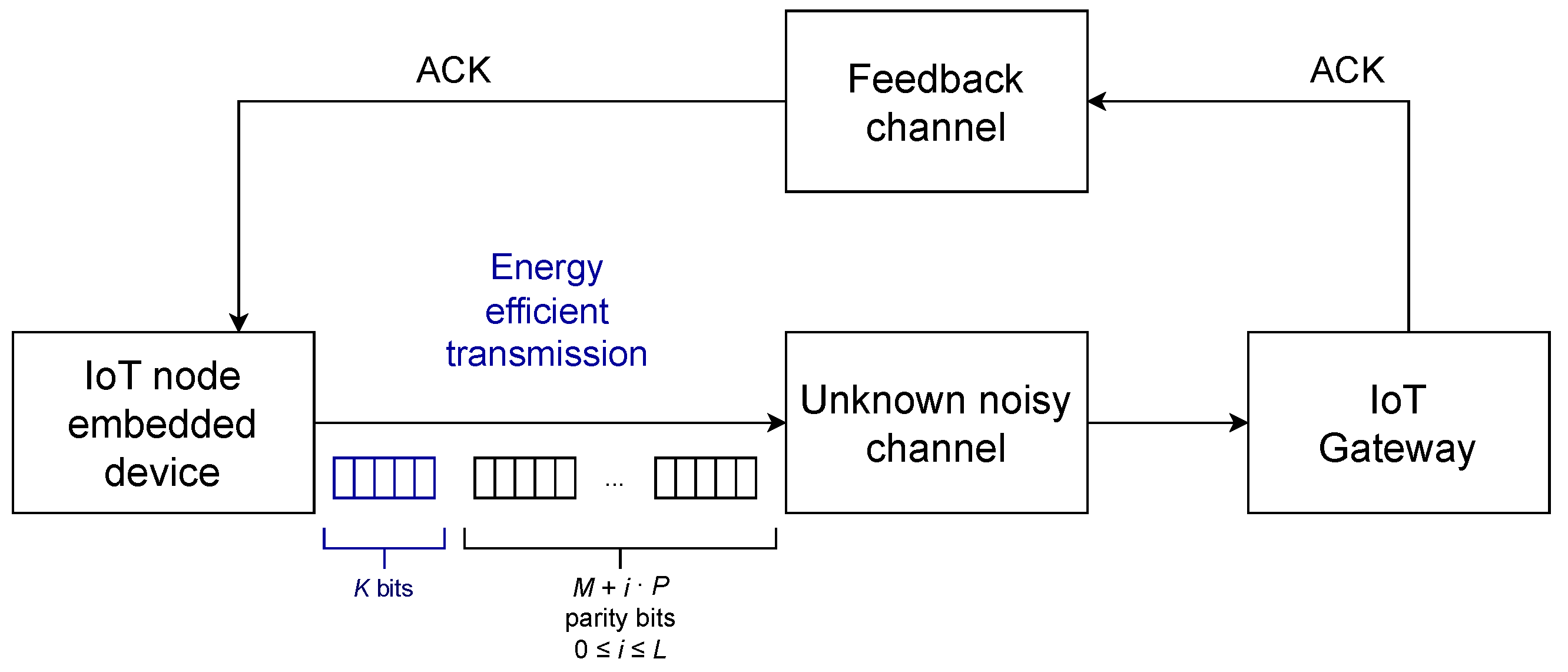

The general rate-adaptive communication system model that we consider in our research is presented in

Figure 1. We investigate a system based on a low-complexity embedded device that acts as an IoT node and can function in a variety of noisy environments, regardless of the communication channel. The communication scheme automatically adapts to the channel; hence, the system can work properly in a wide range of noisy environments. The developed system is classified as a type II hybrid automatic repeat request (HARQ) [

6], which involves an initial transmission of a length-

K block, followed by transmissions of shorter length-

P chunks. The receiver combines these chunks in a decoding scheme, which signalizes the successful decoding by sending positive acknowledge (ACK), after receiving as many chunks as are needed for correct decoding. The coding scheme that we employ is PBRL-LDPC, constrained to quasi-cyclic (QC) submatrices, which we refer to as QC Raptor-like (RL) coding (QC-RL-LDPC).

Since the gateway in

Figure 1 is assumed to possess significantly more computational resources, it is possible to consider an ECC scheme with high decoding complexity for data blocks sent in an uplink direction. Therefore, we claim RL-LDPC coding to be a good choice due to its great correction performance, which can potentially also reduce the transmission power needed, and in consequence, enhance the transmitter energy efficiency. However, in the proposed system, the QC-RL-LDPC encoder must still be implemented with an embedded CPU in an IoT node.

In this context, the research presented in this paper is initiated. Although there have been many research efforts in the implementation of LDPC and Raptor-like encoding and decoding, most of them involve high-throughput FPGA or ASIC hardware implementations, while CPU codec investigations are missing. However, we show that with some effort, the encoding side can be designed in a way that also enables implementation in low-power processors with limited processing capabilities. Moreover, for the system designed according to the outline in

Figure 1, the energy efficiency of the IoT node operation is very important. We note that the energy efficiency of the node radio transmitter can be enhanced by using a modern and well-performing ECC, such as the LDPC coding scheme, and additional enhancement in the case of unknown channel corruption can be achieved by a rate-adaptive scheme devoted from LDPC.

Therefore, this paper concerns the design of the entire system, including the construction of flexible QC-RL-LDPC codes and the implementation of the encoding scheme in the IoT node of

Figure 1, as well as the experimental investigation of the uplink transmission system performance and the energy efficiency, especially by comparing the incremental redundancy system with the standard fixed-rate coding. This comparison is made in terms of energy efficiency of message transmissions, which is dependent on both the encoding energy consumption and the transmitter energy consumption, which are experimentally assessed in this research.

Our focus in energy efficiency assessment is on the IoT node (transmitter) procedures that have been formulated and implemented in a microcontroller CPU device. Other details of the communication protocol are abstracted as a typical digital modulation scheme and noisy communication channels; however, for complete system description, we also provide the decoding algorithm, based on modified message-passing flow. The detailed particular contributions of this paper can be listed as follows.

With regard to implementation, we show how the QC-RL-LDPC encoding can be efficiently implemented in a CPU device, by decomposing the encoding into simple cyclic shifts and addition operations, in direct correspondence to the CPU program instructions.

We verify the designed CPU implementation of the encoder, with several QC-RL-LDPC matrix representations, measuring the encoding time and providing measurement results.

We provide a concise procedure for a QC-RL-LDPC binary code design, which is based on the PEG construction of base graph [

16] of the HR code; an IR part optimization with reciprocal channel approximation, as in [

13]; and then combined lifting of protographs with a proprietary computer search algorithm.

For the receiver side of the system, we provide an effective decoding scheme, based on LDPC belief propagation (BP) decoding, with incremental redundancy.

We perform a number of experiments of the entire system operation, providing the results in the form of simulated transmission goodput, which is defined as the ratio of the number of information bits transmitted to the total number of modulation symbols utilized in the IR, required for successful decoding. Several different designed QC-RL-LDPC codes with different code lengths are experimentally tested. Moreover, we also simulate rate-adaptive coding based on state-of-the-art 5G codes [

17,

18] and compare them with our designed codes.

Taking into account the timing results and system simulation goodput results, we assess the energy consumption of the encoder plus radio transmitter in a typical IoT wireless transmission scenario, and provide the results in the form of energy consumption normalized per transmitted information bit, which allows for an energy efficiency comparison with a fixed-rate coding system, as well as with a 5G coding system. The experimental results show the energy efficiency gain that can be achieved in comparison to fixed-rate coding.

2. Research Methods

The QC-RL-LDPC encoder is implemented in low-power microcontroller unit from the STM32 family, as will be presented in

Section 5 and

Section 8.1. All the remaining parts of the communication model considered, presented in

Figure 1, are implemented as software models developed in the Matlab environment. The research methodology is outlined in

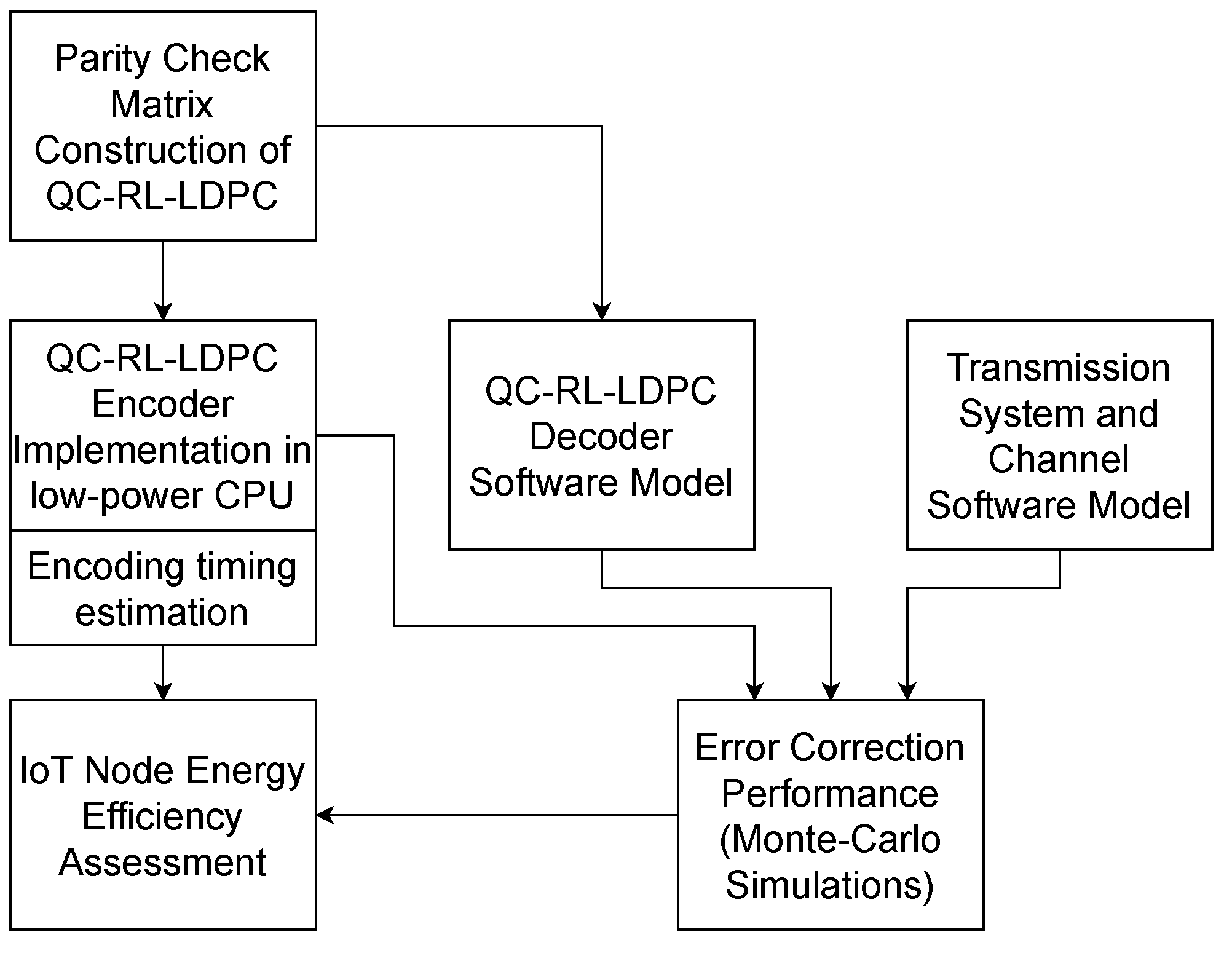

Figure 2.

The parity check matrix construction is a flexible algorithm that enables construction of QC-RL-LDPC code with any code length, base rate, submatrix size and chunk size, as is presented in

Section 7. The developed decoding algorithm is presented in

Section 6, and in general, it can be used in software or hardware implementations; however, for this research, the software model created in Matlab is used. Similarly, the transmission system with QAM/QPSK modulation and communication channel are modeled with software.

The models are then used in Monte-Carlo simulations that provide, as a result, the estimated error correction performance of the system, in the function of channel corruption level represented by signal-to-noise ratio (SNR). The simulation results are provided in

Section 8.3. The second part of the experimental design is the encoding timing estimation, which is conducted by injection into the encoder source code, a time measurement unit based on one of the hardware timers in the STM32 microcontroller. The timer is executed for as long as the encoding and the measurement are read by an interface with PC computer and then converted into time units. The results of these experiments are presented in

Section 8.1.

Finally, both the system performance results and the encoding timing results are used to assess energy consumption of the coding and transmission module in an IoT node, and the results are provided in

Section 8.4.

3. LDPC Coding—Preliminaries

The low-density parity check coding was initially proposed by Robert Gallager in [

19], and later recalled by MacKay [

3,

20], and demonstrated that irregular LDPC codes can asymptotically approach the Shannon limit [

21] of lossless transmission. In the last decade, LDPC codes have become very popular as a powerful error correction coding method with the possibility of algorithm parallelization that enables the development of hardware codecs with optimized algorithms and very high throughput [

22,

23,

24,

25], typically for high-speed industrial communication standards [

26,

27].

The particular LDPC code is defined by its parity check matrix (PCM)

, which defines the specific parity checks involving the transmitted message bits. The important feature of PCM, which is its sparseness, allows LDPC codes to be iteratively decoded using low-complexity message passing algorithms [

3]. Moreover, low-complexity encoding algorithms have also been well recognized [

14]. Recent research in the field also involves nonbinary coding algorithms, as well as code design and implementation [

28,

29,

30].

3.1. LDPC Codes

The binary parity check matrix of a binary LDPC code has a size , where N is the length of the code vector (encoded message), is the length of an information vector, and represents the number of parity bits in the code vector. The measure of coding redundancy is the code rate, defined as . In the systematic encoding process, M parity bits are added to the information vector , forming the code vector . All vectors are binary, and it is convenient to consider them to be defined over the Galois finite field .

In the decoder, the data received

, which is a vector of length

N, are corrupted by channel imperfections. If—and only if—the hard decisions made from

meet the parity check equation, it will be recognized as a correct, (error-free) vector

. The parity check equation is expressed as

, where the matrix operation is in

arithmetic. If the equation is not satisfied, the iterative decoding algorithm is started that can correct errors, with soft decisions as the algorithm input, which are usually in the form of log-likelihood ratio (LLR) vector:

Alternatively to matrix representation, LDPC codes can also be represented by the associated bipartite Tanner graph [

3,

31]. In the Tanner graph, the variable nodes (VN) representing codeword bits are associated with columns of

and the check nodes (CN) representing parity checks are associated with rows of

. The nonzero elements in

correspond to edges in the code graph. This means that the graph nodes are divided into two distinct sets (VNs and CNs), and that the edges only connect two different types of nodes. For an

LDPC code with block length

N, the graph consists of

N variable nodes and

check nodes.

The most popular LDPC decoding algorithms are all algorithms involving belief propagation (BP), including sum product (SPA) algorithms and several simplified versions operating on LLR beliefs, such as min-sum algorithms (MSA), offset min-sum algorithms (OMSA), or normalized min-sum algorithms (NMSA) [

32,

33,

34].

Since the message length in our assumed IoT system is assumed to be relatively short, the block lengths of codes that are considered and investigated in this article are short-to-medium. We investigate such codes constructed with a developed procedure that will be briefly presented in one of the next sections.

3.2. Quasi-Cyclic LDPC Codes

Many communication systems use the quasi-cyclic (QC) subclass of LDPC codes [

15]. These codes have properties that make them suitable for efficient encoder and decoder designs, as well as for industrial implementations [

17,

24,

35,

36]. The PCM of QC-LDPC codes has a distinct structure composed of circulant permutation matrices (CPMs):

where

is either a

all-zero submatrix (by convention, it is indicated by

) or an

-CPM of size

, that is, a matrix obtained by cyclically shifting every row of an identity matrix

by

positions to the right [

37]. The particular code can be unambiguously defined by its size and the values of

, for macrorows

, and macrocolumns

.

The design of QC-LDPC codes can be treated as an important special case of the protograph-based LDPC code construction process [

38]. In essence, this construction process is based on the copying and edge permuting of a smaller graph (protograph, base graph) to achieve a larger Tanner graph of a QC-LDPC code.

3.3. Raptor-like LDPC Codes

In contrast to block coding with a fixed code rate, rateless coding is an error correction scheme that, given a fixed information vector, generates a (potentially unconstrained) series of redundant bits [

39], making use of IR decoding on the receiver side. However, constructing good rateless codes with the possibility of efficient encoding and decoding requires some effort. One of the recently achieved solutions is protograph-based Raptor-like (PBRL) LDPC coding [

12,

13].

The PBRL-LDPC code can be considered to be a concatenation of a high-rate code (HRC), which is an LDPC code with a parity check matrix

of size

and an incremental redundancy code (IRC) characterized by a low-density generator matrix (LDGM)

[

13]. In this paper, we employ the QC subclass of PBRL-LDPC codes, which will be called QC-RL-LDPC codes.

The matrices defining the QC-RL-LDPC code

and

both have a structure consisting of CPMs, as in (

2). The size of matrix

is

, which means that it has

L macrorows of

circulants, giving a total of

parity checks in the incremental redundancy scheme. The Tanner graph of such a QC-RL-LDPC code can be illustrated as presented in

Figure 3, where the blocks denoted by

and

are edge permutators according to the matrices’ structures.

4. The Developed System

This coding system is specifically created for a low-complexity IoT embedded device that communicates using a radio transmission protocol, with an energy-efficient ECC. The IoT node must meet certain criteria, such as being low-complexity and embedded-MCU-based, requiring a wireless communication system for various conditions and prioritizing energy efficiency of the radio transmitter during the design process. With these considerations in mind, it is suggested that a modern incremental-redundancy-based transmission could be advantageous.

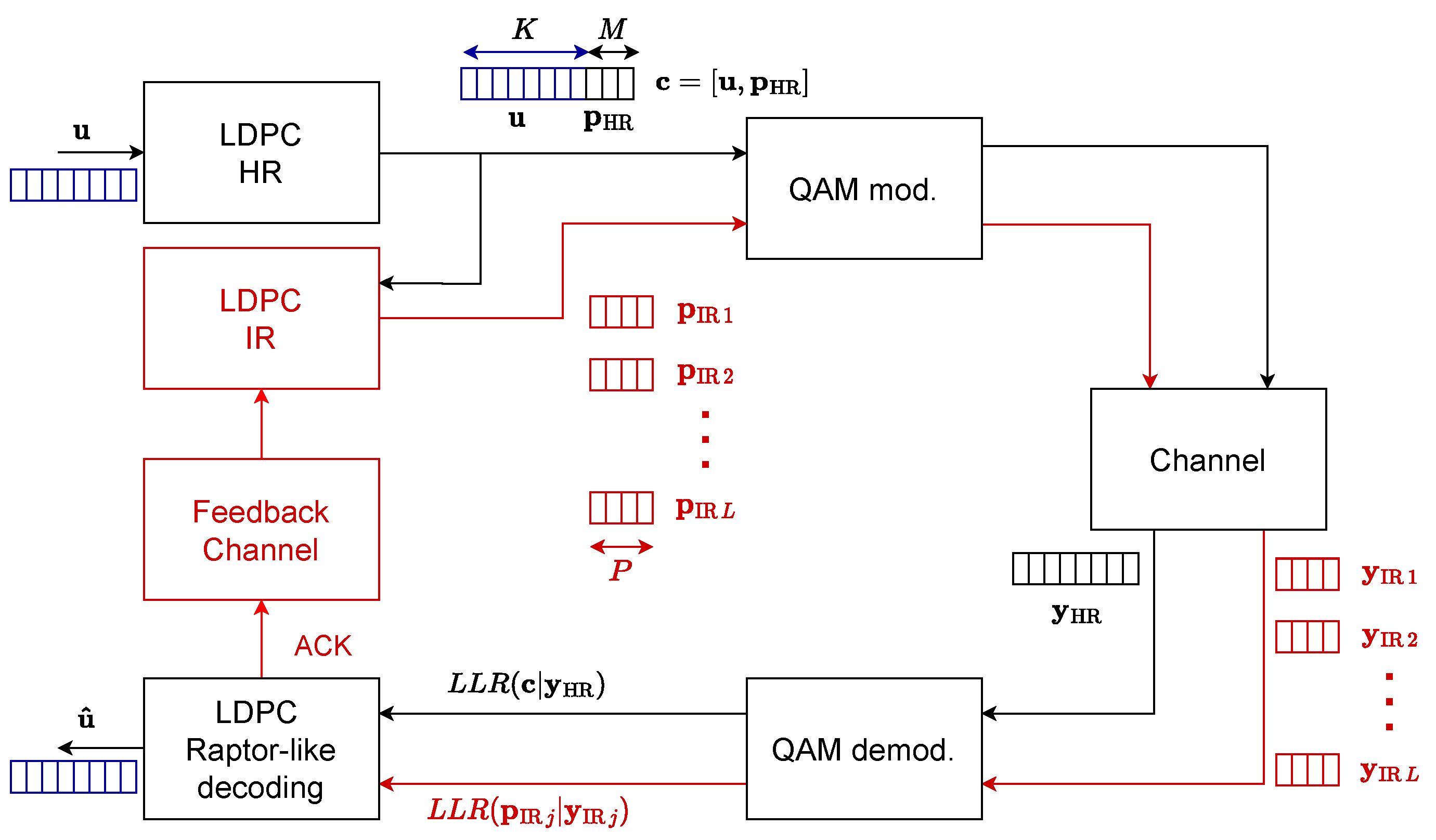

The model of the proposed communication system employing incremental redundancy is presented in

Figure 4. On the transmitter side, the HR (high-rate) and IR (incremental redundancy) parts of coded message are distinguished. The HR parity bits vector

is an element of the codeword

that is initially transmitted, with a chosen transmission method. In the model presented in

Figure 4, we assume that QAM modulation over a wireless communication channel is used; however, other transmission techniques and mediums can also be supported. After the initial transmission of

, the transmitter generates and subsequently transmits IR parity bits in vectors

,

as long as it receives an acknowledgment (ACK) of successful decoding. The IR vectors are of length

P, and will also be called IR chunks.

The developed system is a kind of adaptive-rate scheme, in which the coding rate of the transmission system is variable in the range

, with the highest rate corresponding to the HR code being as in (

3), and the lowest rate (

4) reflecting the situation where the maximum number of chunks is required for correct transmission. If decoding is still unsuccessful after sending

L IR chunks, the message can be retransmitted, either immediately or scheduled for later retransmission.

We performed an analysis of the energy efficiency of a developed transmitter embedded in an IoT device, with microcontroller (MCU) hardware. The receiver is assumed to be implemented with any device (CPU/GPU/hardware) with significantly greater computational power. It is assumed that either:

The computational resources of the receiver (gateway) are far greater than the resources of the transmitter (IoT node), to the extent that IR decoding is performed in a fraction of the encoding time, as well as the feedback channel latency can be neglected; or

The CPU that implements encoding in the transmitter, after encoding a chunk enters a sleep state for a specified time needed to receive a feedback message, in which state the energy consumption is negligible.

If one of these points is satisfied, the ACK can be assumed to be received virtually immediately after transmitting only as many chunks as are needed for correct decoding. This assumption is important for the energy efficiency calculations we made.

In the following sections, we provide the details of the whole designed system: the encoder design for a CPU; the decoding algorithm that was developed based on LDPC iterative decoding; and the code construction algorithm that can be used to design QC-RL-LDPC codes of arbitrary lengths and submatrix sizes. We provide experimental results in the form of encoding and decoding timings, and then energy consumption. We show that, in the case of unknown channel SNR, the implemented scheme can achieve a greater transmission energy efficiency than a fixed-rate coding system.

We also present the developed decoding scheme, based on the iterative LDPC decoding algorithm, that can be utilized in an incremental redundancy QC-RL-LDPC system. While the receiver (gateway) hardware is undefined but usually possesses a great computing power, a QC-RL-LDPC decoder in a CPU has also been developed for possible use in the reverse (gateway to IoT node) direction. We also provide the results of the decoder implementation for the same CPU as on the encoder side.

5. QC-RL-LDPC Encoding

The encoding of QC-RL-LDPC codes, as shown in

Figure 4, always involves the HR part and then as many chunks in the IR part as are required to efficiently decode the message in the receiver.

The encoding of the HR part, that is, determining

, can be performed with one of the known efficient LDPC encoding algorithms, utilizing the QC feature. In [

36], we presented a CPU-based QC-LDPC encoder implementation, which can also be used as an HR part encoder implementation in the QC-RL-LDPC system presented in this article. If this implementation is used, for the sake of code construction, it is important to note that the parity check matrix

, in addition to being in QC form, should follow the ALT (almost lower-triangular) form, as in the Richardson–Urbanke encoding [

14], that is,

where

is a lower-triangular matrix and all submatrices are CPMs. Cyclic changes in CPMs should preferably be selected so that

is an identity matrix,

, which can be achieved by fulfilling a condition originally proposed in [

37]. As a result of the encoding of the HR information vector

, the code vector

is obtained. The Details of the encoding algorithm for QC-LDPC and its microcontroller implementation can be found in [

14,

36,

37].

The IR encoding is based on the

parity check matrix, which can be expressed as follows:

where each macrorow

defines the parity checks (

7) in

arithmetic for the

lth chunk of incremental redundancy,

.

The consecutive chunks for

can be computed as in the following expression:

Every chunk calculation as in (

8) requires elementary operations of the type

, as well as additions over GF(2), where every

is either:

a zero matrix, in which case the product is ;

or a circular shift of an identity matrix by positions, in which case it can be easily verified that the product is a circular shift of by positions.

Therefore, computing (

8) for the QC case requires elementary operations of circular shifts of binary length-

P subvectors in

, as well as modulo-2 additions of length-

P subvectors. Implementation in the microcontroller can be developed in C language, in which modulo-2 additions are realized with an “

” operator, and the circular shifts can be realized by using a bitwise shift operation and a bitwise OR operation, as in the following example:

| output = (input << offset) | (input >> (size − offset)); |

where

offset is the cyclic shift value and

size is equivalent to the submatrix size

P. Using this instruction for the circular shift, the input value can be represented in

uint32_t type (if

), while the

size and

offset can be represented in any unsigned type, for example,

uint8_t. The output value is in the same format as the input.

6. Raptor-like Decoding of QC-RL-LDPC Codes

The decoding can be based on the belief propagation (BP) scheme with messages (beliefs) calculated as in the LDPC decoding with an SPA algorithm, or one of its LLR variants. In accordance with the proposal in [

13], the overall concept is to decode the HRC and IRC parts together. The joint parity check matrix of both parts, corresponding to the whole Tanner graph of the QC-RL-LDPC code (as in

Figure 3), is given as

where

is an identity matrix. BP generally proceeds according to the graph in

Figure 3. The decoding algorithm calculates the LLR messages for every edge of the graph in every iteration. However, it can be noted that it is inefficient to initialize the decoding process with a priori beliefs every time the decoder receives a new IR chunk. Therefore, we have developed the decoding procedure, in which the iterative process is suspended if the correct vector is not found after some number of iterations and then resumed after receiving a new chunk with LLR-input IR information. Other than IR, beliefs (messages exchanged between nodes) remain as obtained in the previous iteration. The decoding algorithm is presented in

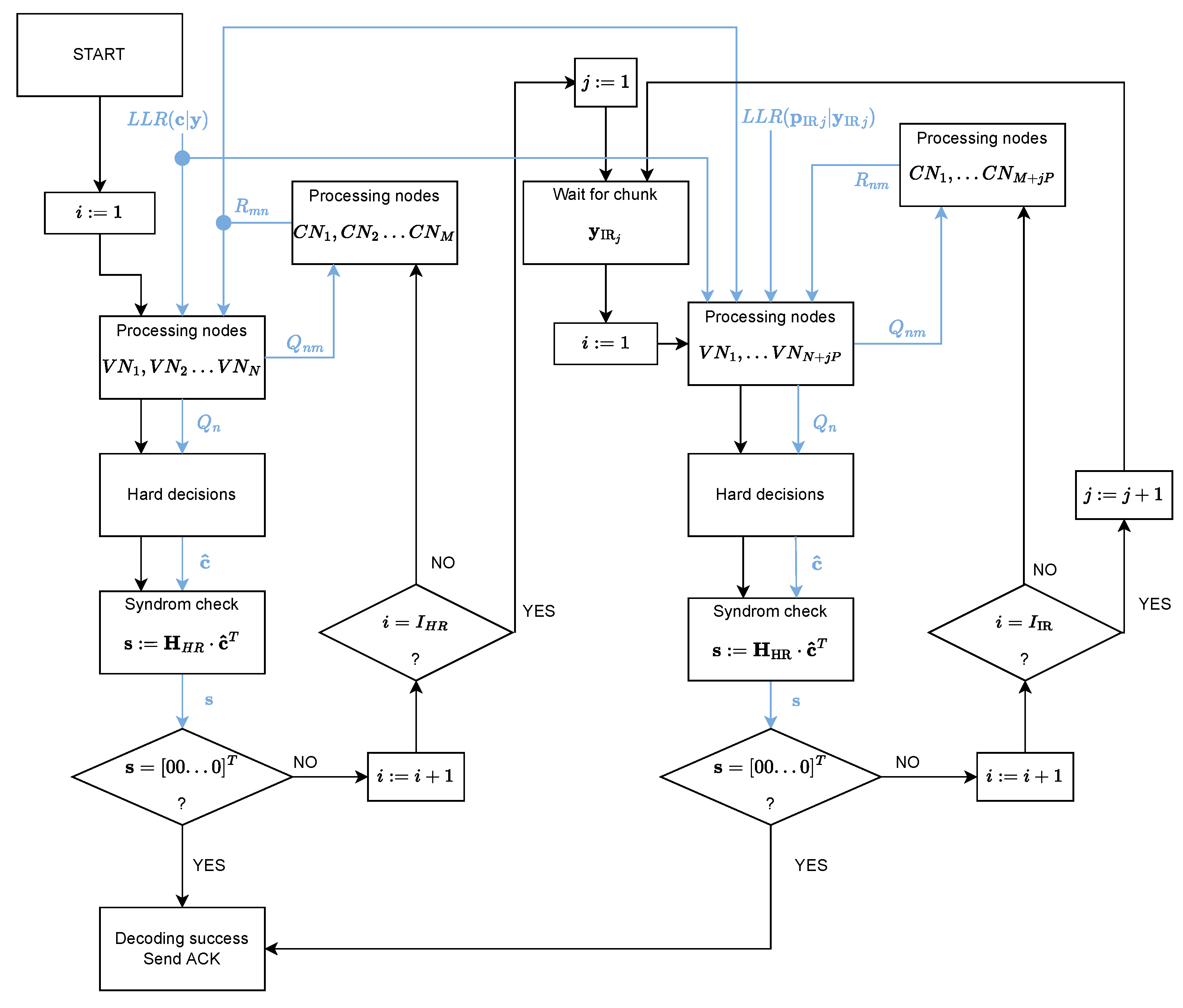

Figure 5, where the processing sequence as well as the data flow (in blue lines) are shown. The algorithm can be summarized as follows.

Soft input decisions of the HR part, , are delivered first to the decoder, which proceeds with a number of iterations, computing variable node messages, denoted as , and check node messages, denoted as , for and .

In every iteration, based on the total beliefs for the HR codeword symbols , the error syndrome is checked, and if a correct codeword is obtained, the decoding ends with success.

After

iterations, the decoder waits for the next IR chunk. The chunk counter is denoted as

j, while the iteration counter is

i in

Figure 5. After every subsequent chunk reception, the decoding is resumed for

iterations, but the initial check-to-variable messages

are taken from the previously suspended decoding part.

The computations of beliefs

,

, for

and

, can be done with one of the well-known BP message calculation methods, such as min-sum or normalized min-sum [

34]. In our experiments, we used a computer model of the corrected min-sum algorithm [

34]. An important choice of the number of iteration limits

and

can be made experimentally. The experimental results of the decoding performance will be provided in

Section 8.

For a highly erroneous initial HR code block, the information calculated during initial decoding iterations is not enough to correct errors, but all iteratively enhanced beliefs are saved. Based on it, the next iterations are started, with additional soft information received. The point is that there is no need to calculate the beliefs from the beginning after every chunk transmission.

7. QC-RL-LDPC Codes Construction for the Proposed System

Numerous methods for the construction of QC-LDPC have already been proposed, and a majority of finite code designs are centered around creating a Tanner graph structure with advantageous features, for example, in [

40,

41,

42,

43,

44]. However, in this investigation, in order to design the entire QC-RL-LDPC coding scheme, we integrated the base graph construction by progressive edge growth (PEG, [

40]) with protograph optimization for PBRL codes using density evolution [

13] and proprietary algorithms to determine CPMs [

36]. This allowed us to create a single, comprehensive method that gives both

and

as a result.

The proposed approach to the construction of the QC-RL-LDPC can be summarized as in the following steps:

The crucial characteristic of the designed algorithm is that after determining base matrices (protographs) for both parts and , with appropriate methods previously known for rate-fixed LDPC codes, the whole graph of the QC-RL-LDPC coding scheme is optimized with a joint algorithm.

8. System Implementation Experimental Studies

Our research has been validated through experimental studies that examine various aspects of the developed QC-RL-LDPC system. These include encoding time; memory utilization of the encoder implemented with a microcontroller; investigation of decoding time and decoding parameter selection; error correction performance; and finally, normalized energy consumption estimation of the developed QC-RL-LDPC system. Due to the specifics of the design objective, which is an energy-efficient IoT uplink transmission scheme design, we investigated relatively short codes of length within . We provide the microcontroller implementation results and a performance simulation for the channel with an unknown corruption level, represented by a wide range of SNRs (signal-to-noise ratios).

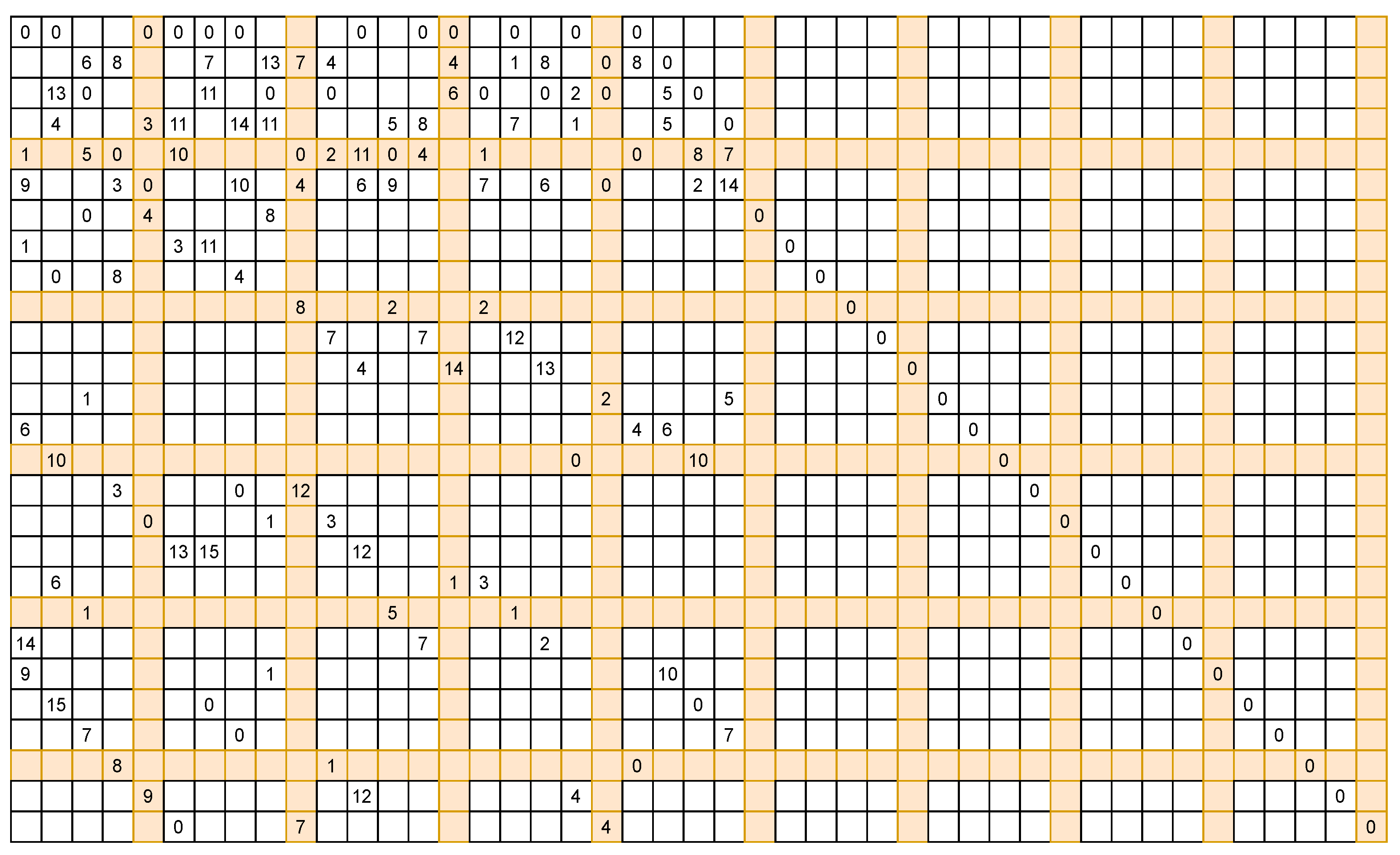

Several different codes (

) with diversified block lengths, chunk sizes and minimum rates, as listed in

Table 1, were designed and used for this experimental study. As an example,

Figure 6 shows a whole parity check matrix

of the code

.

The parts of the designed communication system were implemented specifically with an STM32L476 microcontroller, for which we present the implementation results, including a case study of the power consumption and the energy efficiency calculations.

8.1. Encoder Implementation

The encoder was designed with a C language implementation of the encoding algorithm presented in

Section 5. Parts of the parity check matrix

and

are stored in the microcontroller flash memory in the form of positions (indexes) of nonzero submatrices together with corresponding circular shifts, as illustrated by an example in

Figure 6.

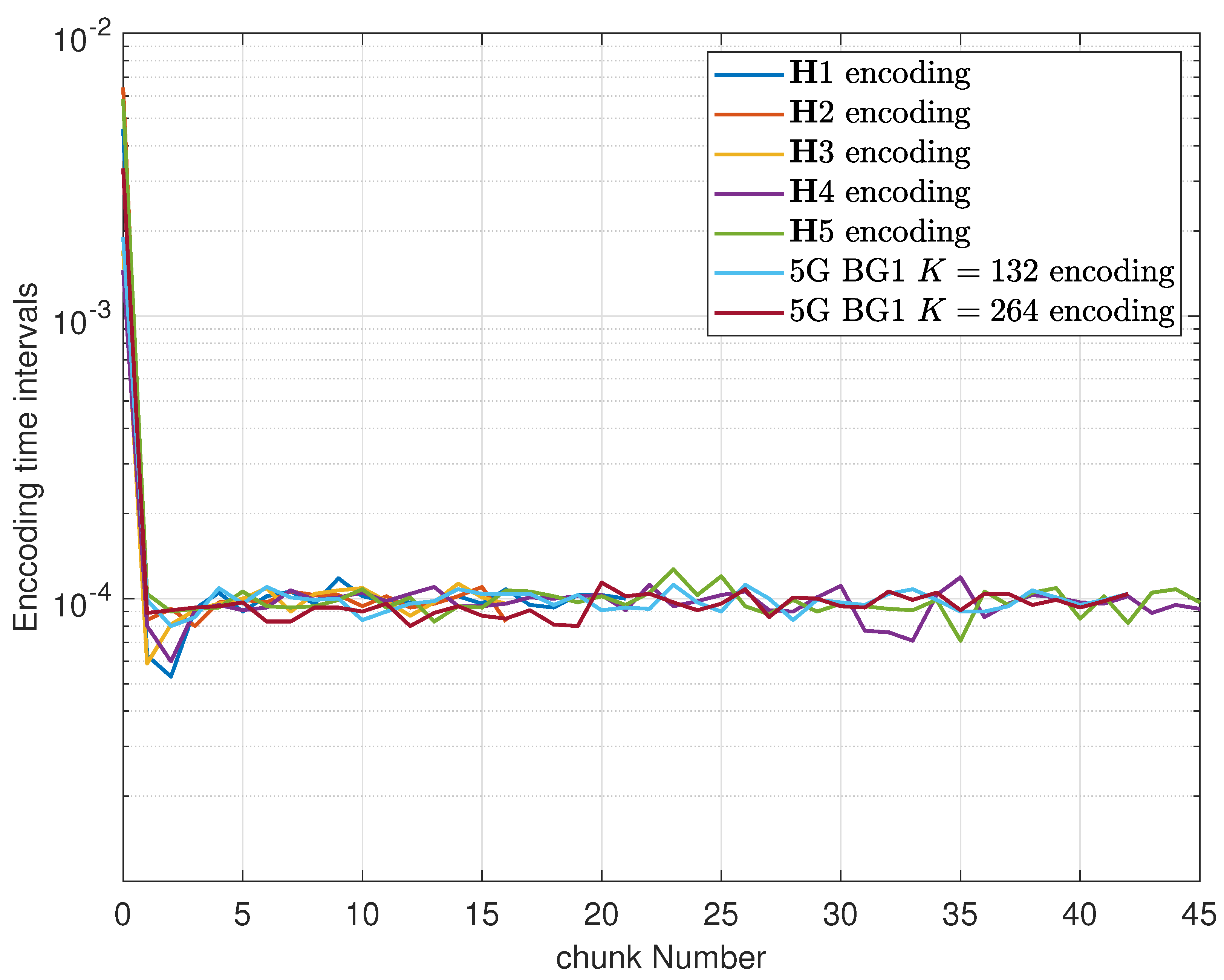

We measured the encoding time in the QC-RL-LDPC system with the developed encoder, which was compiled and implemented in the STM32 low-power microcontroller unit. The results are presented in

Figure 7. Note that the first part of the encoding (the HR part, shown as chunk-0 in

Figure 7) takes a significantly longer time period than the subsequent encoding iterations of the following chunks (the IR part). We also implemented encoders for selected 5G codes, with Base-Graph-1 (BG1, see [

17]) and submatrix sizes of 6 and 12, giving codes with information block lengths of 132 and 264, which are similar to our designed codes

,

and

, respectively. The presented time measurements were then used to assess the energy consumption of the encoder, which is presented in

Section 8.4.

The QC-RL-LDPC encoder stores the parity check matrices in memory using static allocation. Its memory utilization is comparable to the efficient QC-LDPC encoder previously presented by us in [

36]. The maximum memory requirement for QC-RL codes is related to the maximum code size, with all chunks. The utilized microcontroller is able to allocate the needed memory and process the encoding.

8.2. Decoder Implementation

The developed Raptor-like decoding algorithm, presented in

Section 6, can be implemented on any computing platform utilized in the system gateway (

Figure 1), including CPU, GPU, ASIC or FPGA. For the the experimental investigation in this paper, Matlab software implementation on a personal computer was used. However, additionally, we developed the C language implementation for the STM32 microcontroller, the same as that used for the encoder. In

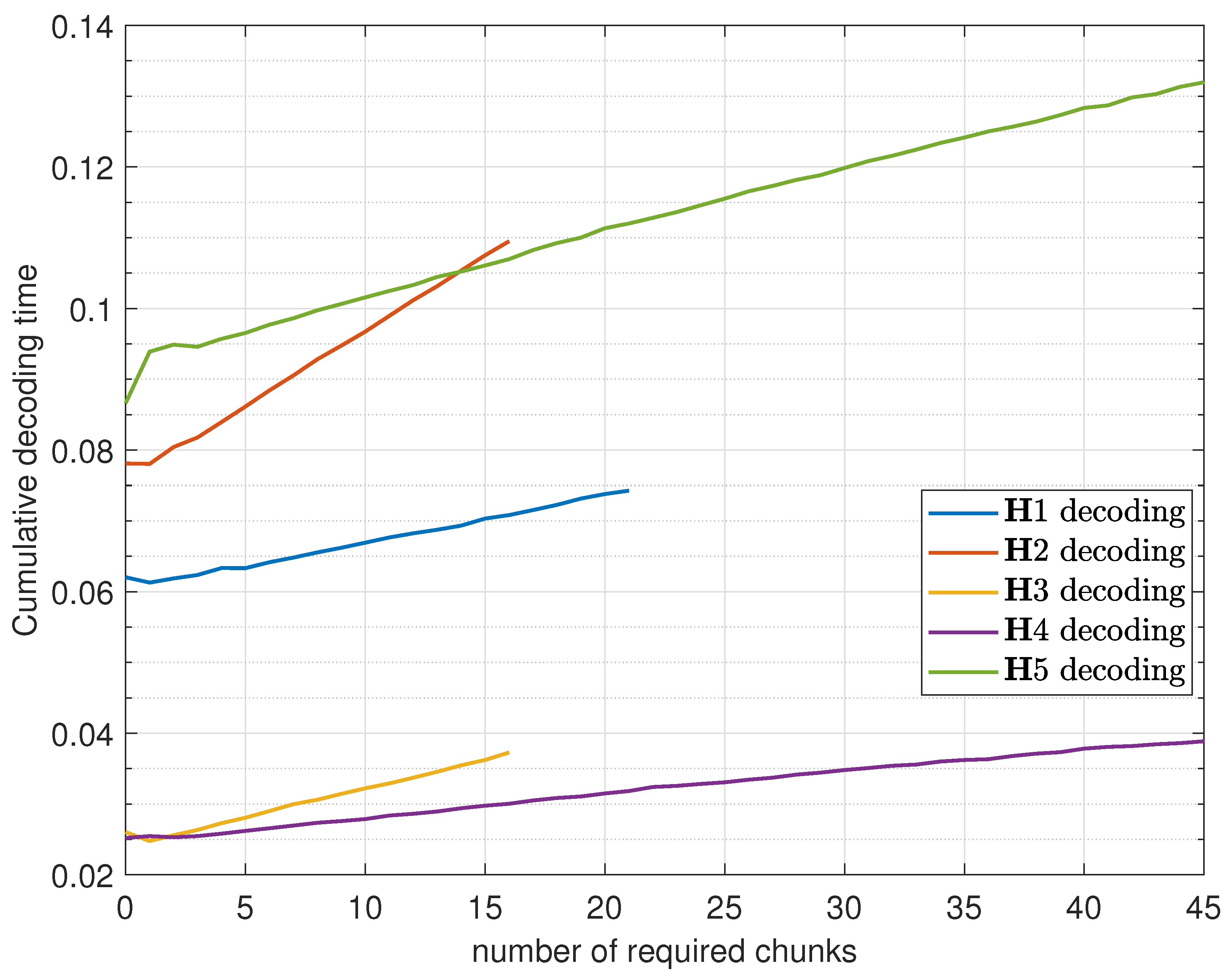

Figure 8, we present the decoding time measurements of this implementation.

The microcontroller with the developed decoding algorithm is able to decode information portions efficiently, with lower computing time requirements if the received signal is of high quality (with small number of errors) and higher computing time consumption if the received signal is of low quality. In case of an erroneous received signal, the algorithm adapts and continues decoding until the correct result is achieved. During decoding, subsequent parity checks are used from

. With every additional chunk, the total (cumulative) decoding time increases, as shown in

Figure 8. The figure provides averaged measured cumulative decoding time versus the number of chunks required for successful decoding. This means that the first (leftmost) point in every curve presents the time of decoding just the core HR part (with 0 additional chunks), and then the subsequent points present the total decoding times if the number of required chunks increases.

8.3. System Simulation Results

The experimental verification of error decoding performance that can be achieved with the proposed QC-RL-LDPC implementation was carried out by simulating a system as in

Figure 4. In the results presented in this section, we assume a QPSK modulation (two bits per symbol) and an additive white Gaussian noise (AWGN) channel, with a broad range of simulated signal-to-noise ratios (SNRs). Correction performance is evaluated with Monte Carlo simulations, with the number of messages such that at least 100 of them are in error after HR part decoding, for every SNR.

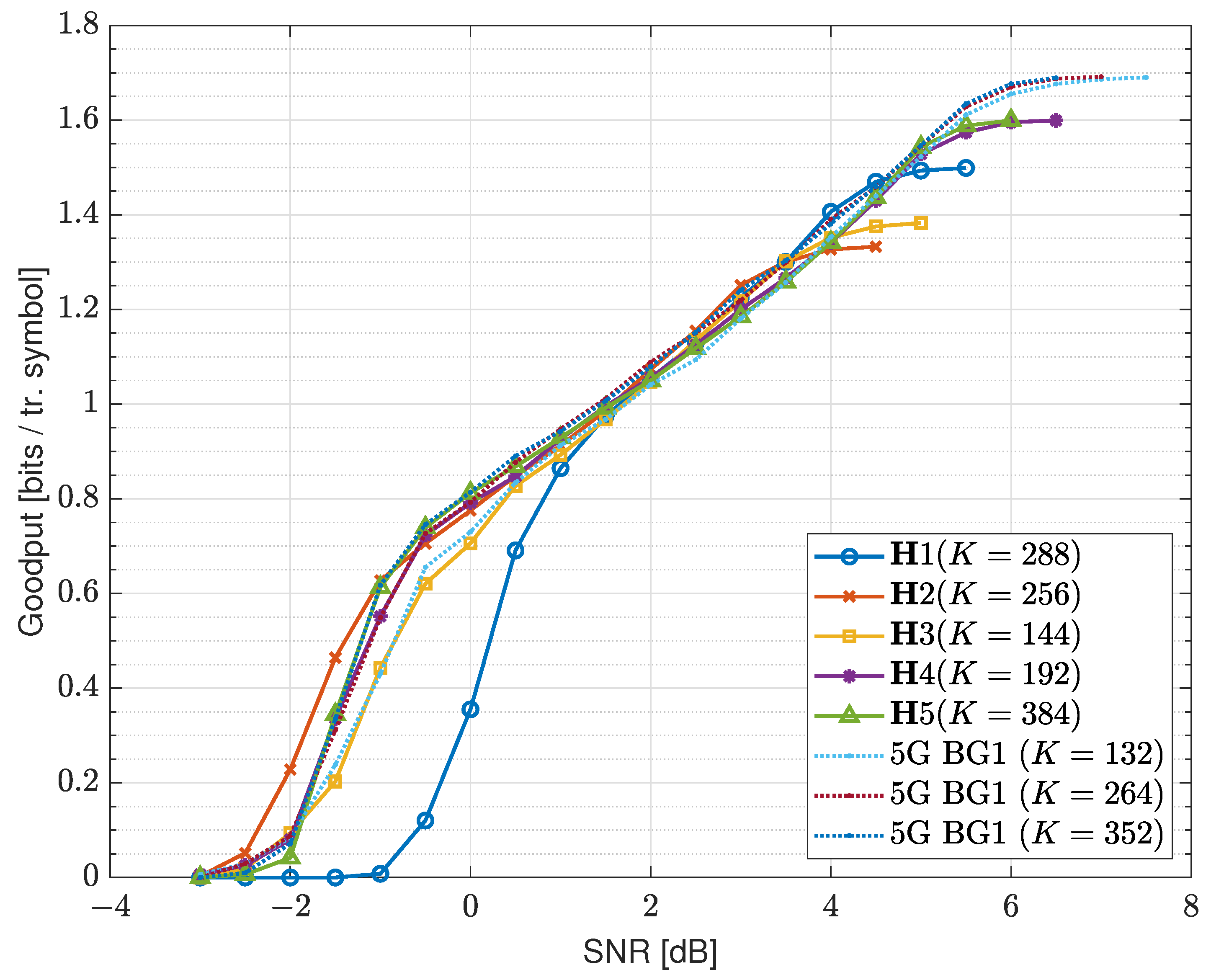

In

Figure 9, we provide simulation results in the form of goodput performance, which is defined as the ratio of the number of information bits correctly delivered to the total number of QPSK symbols transmitted, required for successful decoding [

11]. Obviously, the higher the SNR, the lower the number of average transmitted chunks needed, which means the goodput is higher. The upper limit of goodput for QPSK is

, since if only the initial HR coded vector is transmitted, then

information bits are successfully delivered per every QPSK symbol. The chunk size is assumed to be equal to

P, because the encoding is performed in blocks of

P bits.

We obtained the parity check matrix

by lifting the protograph taken from [

13] (Equations (11) and (12) therein), with submatrix size

. Since the minimum achievable rate of this code is relatively high,

, the correction performance of the code

in the low-SNR regime can be improved by proposing codes with more chunks (or rows in the IR part). To address this, we constructed matrix

using the procedure outlined in

Section 7, with an increased number of chunks and lower

. This code can successfully correct errors with SNR well below 0dB, which is shown in

Figure 9. Some other matrices that we also designed are

, which can be used for shorter messages, with information vector length

but slightly underperforming

; as well as

and

, with an increased initial rate

, which provides a greater maximum goodput of 1.6.

As a point of comparison to other methods, we conducted simulations of a rate-adaptive scheme that utilizes 5G codes. Specifically, we examined BG1 with information block lengths of 132, 264 and 352. It can be observed in

Figure 9 that the performance is similar to our designed codes

,

and

, respectively. This proves that the code construction part of this research provides codes that are not worse than state-of-the-art industrial LDPC codes. However, the advantage of the proprietary QC-RL-LDPC design is that the code parameters of HR code rate, information block length and submatrix size are flexible and can be freely chosen, while the 5G code family offers only two HR code configurations (BG1/BG2) and a discrete set of submatrix size/block length pairs.

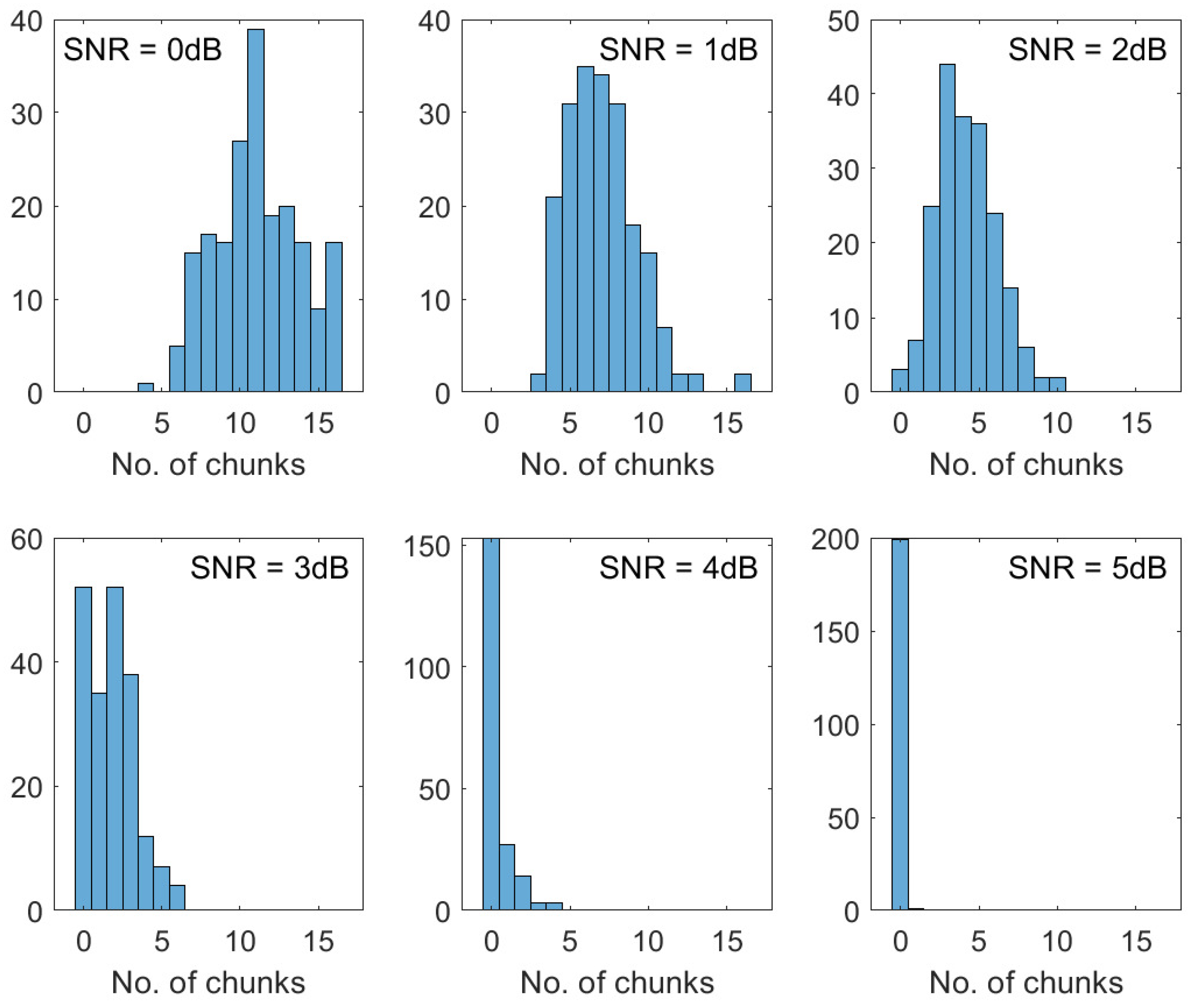

The designed QC-RL-LDPC codes successfully achieve the objective of the rate self-adaptability processing. As shown in

Figure 10, the number of chunks required for error-free reception increases as the SNR decreases. The code should be selected for a specific use case, and the algorithm developed can design codes for diversified needs of information block length

K, rates

,

and chunk sizes

P.

Another decision that needs to be made in the system design is choosing the iteration limits for decoding,

and

(as defined in

Section 6). This selection involves a trade-off between computational burden and decoding performance. However, as illustrated in

Figure 11, which shows results for the same set of received input vectors, decoded with different parameters

and

, the choice of these parameters does not have a very significant impact on the performance. For the system simulation in this paper, we used

and

.

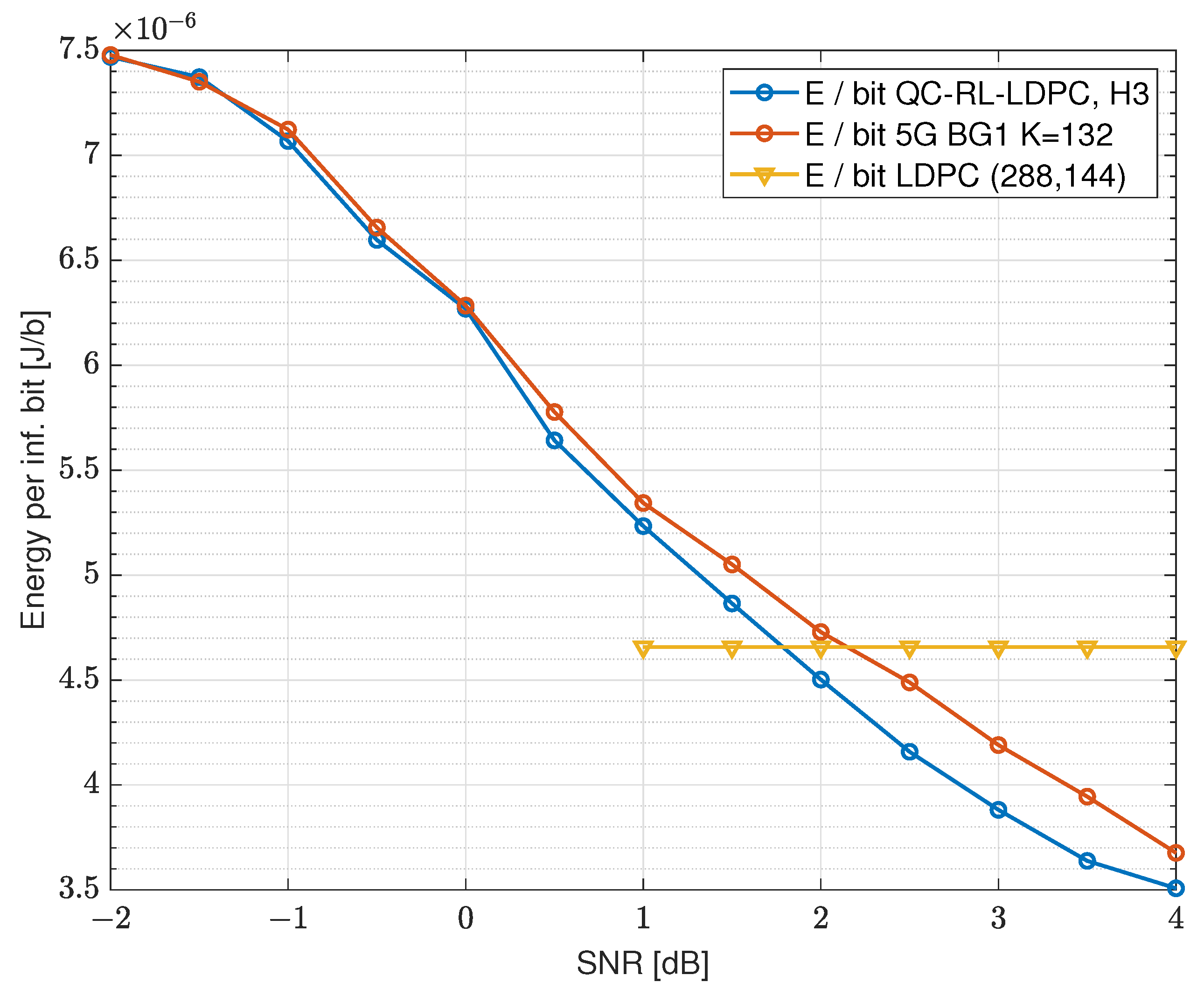

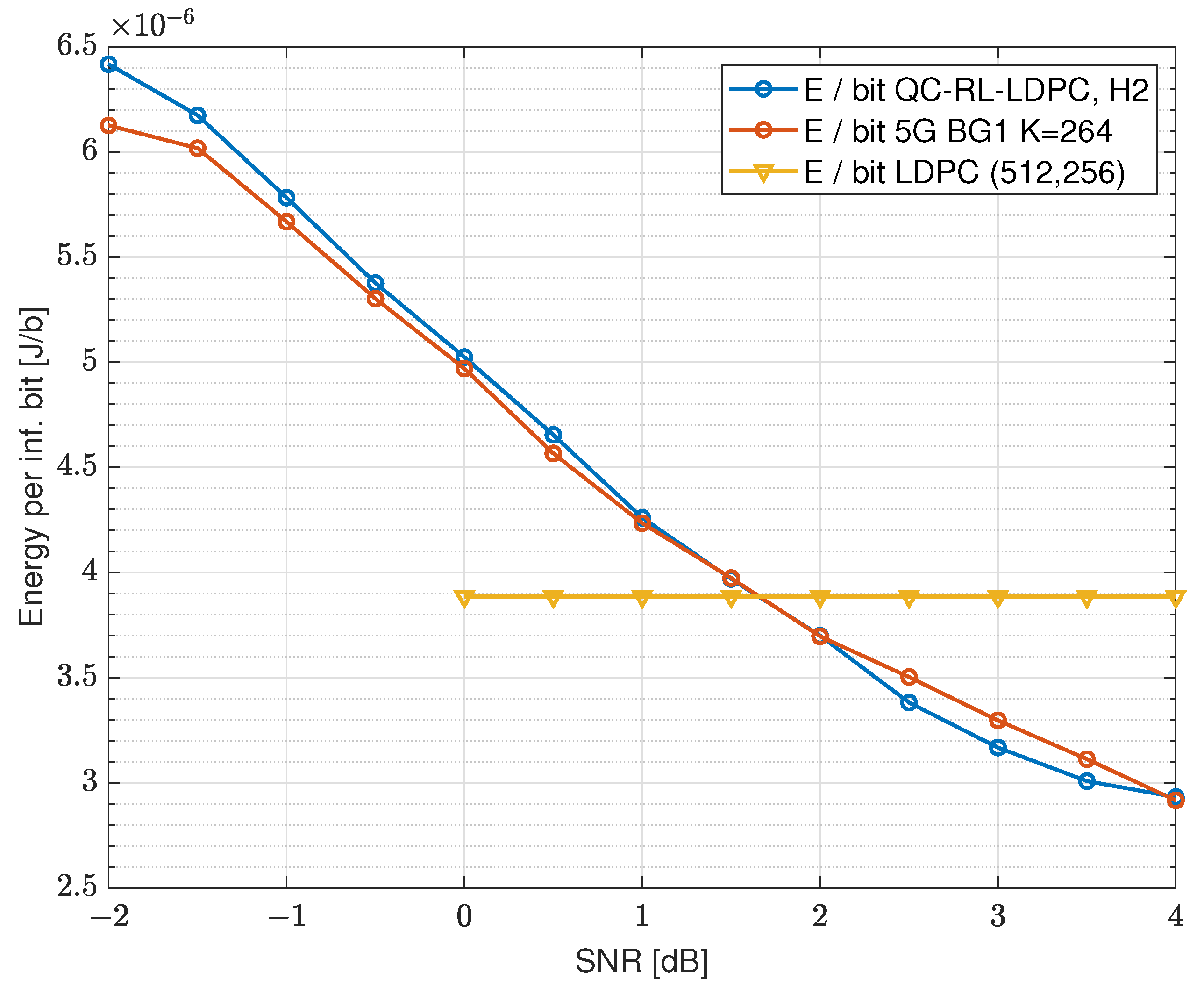

8.4. Energy Consumption Case Study

Based on the experimentally determined transmission performance (goodput) and encoding efficiency (time required for encoding) presented in previous subsections, we aimed to compare the designed system with the fixed-rate coded transmission system, as well as a system employing selected 5G coding configurations, in terms of the IoT transmitter energy efficiency. Since the calculations presented in this section are based on several assumptions, they should be treated as assessments of the energy consumption that can be expected in a real implementation. However, the results illustrate well the gains that can be achieved in the rate-adaptive system.

We assess the portion of the transmitter energy consumption that depends on the utilized coding system, that is, the sum of consumption by the encoding performed in a microcontroller plus consumption by the transmitter module. In the calculations, we have made the following assumptions:

The encoder is implemented in the STM32L476 microcontroller, with a supply voltage of 3.3 V and an active mode current draw of 10.7 mA.

The radio signal power is 25 mW (equal to the uplink limit in LoRa radio), the RF (radio frequency) module power efficiency is 50% and the transmission rate is 12,000 QPSK symbols per second (also comparable to LoRa limits).

The RF transmitter is active only during initial message bits and chunk bits transmissions.

By adding up the radio transmit energy and the encoding energy, factoring in the average number of chunks for the given SNR, we can determine the overall transmitter energy consumption. In the QC-RL-LDPC system, the energy consumption of the transmitter is dependent on the SNR, because with the change in the number of chunks needed, the total encoding time and the radio signal transmission time are also changing. This is illustrated by the evaluation results in

Figure 12 and

Figure 13 for our designed codes of information block lengths of

and

, respectively, as well as codes taken from 5G standard [

17] with BG1 and similar block lengths of

and

, respectively. The energy consumption provided is normalized and presented as one energy per one correctly decoded information bit.

In contrast, the energy consumption of the fixed-rate encoding is independent of the SNR. In

Figure 12 and

Figure 13 we also include the energy consumption of the LDPC coding system, calculated with the same assumptions, for the same information block lengths

and

, respectively, and the coding rate

. It can be observed that:

In the high-SNR regime (higher than about 2 dB), the normalized energy consumption is lower for the QC-RL-LDPC coding than for LDPC fixed-rate coding.

In the regime just above 0 dB, the LDPC fixed-rate coding is more energy-efficient than QC-RL-LDPC coding. This is the regime for which an LDPC rate-0.5 code would be used under conditions that it was designed for; therefore, its advantage in this regime is as expected.

For SNRs lower than about 1 dB for for and lower than about 0 dB for , the fixed-rate LDPC code can no longer correct errors with reasonable BER, while QC-RL-LDPC consumes more energy, but can still be used for transmission and correctly decoded.

The developed transmission system, with the same IR redundancy scheme, but utilizing the state-of-the-art 5G codes, has very similar energy efficiency to the developed QC-RL-LDPC codes in the case of

(264) block length (

Figure 13), and a little worse energy efficiency in the case of

(132) bits (

Figure 12).

The justification for this slight difference between the designed QC-RL-LDPC codes and 5G codes is that the code has the submatrix size , while the 5G code has , which means that more smaller chunks need to be encoded for a given parity vector size; the efficient QC encoding in a CPU can compute a chunk with similar speed, for different chunk sizes. This result emphasizes the flexibility of the submatrix size selection that is given by the proprietary QC-RL-LDPC design framework.

It can be inferred that the QC-RL-LDPC system exhibits higher energy efficiency compared to fixed-rate LDPC in high-SNR scenarios. This is due to its reduced transmission rate and encoding time. Additionally, it surpasses LDPC in low-SNR scenarios (below approximately 0 dB) since it can still effectively correct errors while utilizing more parity bit chunks. It should be especially desired to use rate-adaptive coding in situations where the channel SNR is not known in advance. It then improves not only the error correction possibilities, but also the energy efficiency.

9. Concluding Remarks

This paper discusses a complete design procedure and provides implementation results for a QC-RL-LDPC coding system, specifically tailored for IoT uplink transmission. Our focus is on creating an energy-efficient encoding procedure for IoT nodes built with microcontroller devices, without strict throughput requirements, but where the energy efficiency is an important factor. To achieve this, we implemented a short-block-length Raptor-like LDPC scheme that is efficiently encodable. We showed that LDPC coding, commonly used in high-throughput communication systems and advanced protocols, is also applicable to such computationally constrained devices. Our experimental results showed that Raptor-like QC-RL-LDPC coding can be beneficial in terms of energy efficiency, in comparison with fixed-rate LDPC coding, and not worse that state-of-the-art 5G coding. Then, the developed design procedure, including QC-RL-LDPC code design, encoder implementation and the proposed decoding scheme for Raptor-like decoding, can be used in a rate-adaptive uplink transmission, with flexible parameter selection: block length, code rate and submatrix size.

The entire proposed system was implemented and validated for several designed binary QC-RL-LDPC parity check matrices, as well as compared with a similar design based on 5G codes. The comparison shows that the designed codes have at least similar efficiency to the 5G codes, while in some configurations, the flexible submatrix size choice can provide a slight energy efficiency improvement, even over 5G codes. The coding system can still evolve, and future work will be concentrated on the very promising extension of the proposed concepts to the nonbinary (NB) case, that is, the development of NB QC-RL-LDPC codes and the respective codec implementations.