The controllers are developed in Matlab/Simulink environment and executed in a dSpace MicroLabBox control platform, which is also used for data acquisition at the same sampling rate. This platform has a dual-core PPC microprocessor as well as an FPGA. For controller execution, only the dual-core PPC microprocessor is used with the control algorithm of each UPS being assigned to a core.

For the experimental tests, different types of loads are used. For the LSC neutral leg current analysis presented in

Section 4.1, a balanced linear load is used, which consists of three resistors connected to each phase (

per phase). On the other hand, to test the robustness of the proposed techniques, in

Section 4.2 and

Section 4.3, a highly unbalanced load consisting of three distinct single-phase loads is used: a full-bridge rectifier feeding an RC parallel circuit (

and

) is connected to phase A; an RL load is linked to phase B (

and

); and a resistor of

is connected to phase C. This load configuration was also used for the power quality analysis in

Section 4.4. In

Section 4.5 and

Section 4.6, different types of loads are used, which are explained in the respective sections.

4.1. LSC Neutral Leg Currents Analysis

This section provides an analysis of the LSC neutral leg currents in regard to the magnitude difference that can exist between these currents and other load-side currents, namely LSC phase currents and load neutral currents. In this test, a balanced set of three single-phase linear loads is used in order to generate a practically null load neutral current, with both UPS systems supplying half of the load power ( per phase).

Figure 4 illustrates the load voltage, the absorbed load phase currents, the load neutral current, the neutral leg current of each LSC, and the ZSCC.

Firstly, as

Figure 4a shows, in these conditions, a high-quality load voltage waveform is obtained, with a THD of approximately 1.2%. With the balanced linear load connected, practically sinusoidal currents are absorbed from the UPS system with a peak value of approximately

A, as shown in

Figure 4b. Hence, the load neutral current presented in

Figure 4c is practically null.

Figure 4d,e show the LSC phase currents, which are directly controlled, in order to ensure the respective load phase voltage waveforms, as discussed in

Section 3.4. As can be seen in these two subfigures, the LSC phase currents present a peak value of approximately 5 A, which corresponds to twice the load phase currents’ peak.

Regarding the neutral leg current of a given LSC, as demonstrated in (

21), it depends on the sum of the respective LSC phase currents as well as on the ZSCC that flows between the paralleled UPS systems. Thus, since each LSC phase current is directly controlled to ensure the respective load phase voltage waveform, there can be situations in which the sum of LSC phase currents results in a higher value than that of the peak of the LSC phase currents, significantly increasing the converter neutral leg current. Moreover, from (

21), it can be observed that the ZSCC can also increase the LSC neutral leg currents even more. Hence,

Figure 4f,g show that despite the balanced linear load being connected to the UPS systems, with the load neutral current being practically null, the currents that circulate in the neutral legs of both LSCs are significantly different from zero, clearly reaching peak values even higher than those seen in the LSC phase currents. In the tested conditions, as demonstrated in

Figure 4h, the ZSCC is controlled, consisting of a ripple current around zero and, hence, having a small effect on the neutral legs’ current values. However, when not controlled, the ZSCC can significantly increase the LSC neutral leg currents, as is demonstrated in

Section 4.2.

These results show that even when supplying a balanced linear load that generates a load neutral current that is practically null, due to the required LSC control and ZSCC (

21), the currents in the neutral legs of these converters can be significantly different from zero. Even though the RMS value of the neutral leg currents is significantly smaller than that of the LSC phase currents, these can reach significantly higher peak values. This occurs even when the load power is equally divided between the UPS systems.

This analysis allows the conclusion that the semiconductors to be used in the neutral legs of the proposed paralleled UPS system topology must be able to support higher currents than the semiconductors of the LSC phase legs.

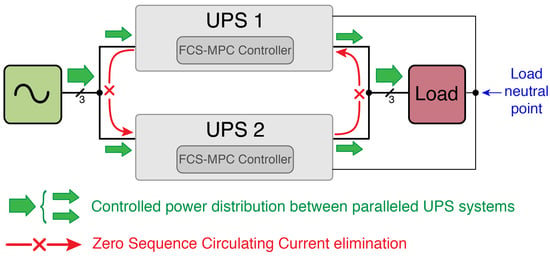

4.2. Zero-Sequence Circulating Current Elimination

Figure 5 shows the importance of ZSCC elimination as well as the effectiveness of the proposed strategy in suppressing this undesired circulating current. This figure shows the ZSCC, input UPS systems currents, LSC phase currents, LSC neutral leg currents, and the generated load voltage. In this test, the highly unbalanced non-linear load is used, with both UPS systems supplying half of the power to this load. Until

36 ms, the ZSCC suppression technique is active, and then it is deactivated. This means that the ZSCC is considered as a converter objective only until that instant, and after that, the elimination of this current is no longer a control objective (

). Hence, from

Figure 5a, it can be observed that after ZSCC suppression deactivation, the ZSCC starts to rise, reaching a maximum absolute value of roughly 7.5 A. Hence, as presented in

Figure 5b,c both UPS input currents are significantly affected, becoming highly distorted and reaching higher values compared to those observed while the ZSCC elimination mechanism is active.

Figure 5d,e demonstrate that the existence of a considerable circulating current has practically no impact on the LSC phase currents. However, by observing the neutral leg currents in both UPS systems, in

Figure 5f,g, it can be seen that their magnitude is significantly increased. When the LSC1 neutral leg current reaches 30 A (

ms), the corresponding overcurrent protection is triggered (30 A is the predefined maximum admissible current at the converter neutral legs). It can be seen that this is a significantly higher value in comparison with the LSC neutral currents that were observed while ZSCC elimination was active.

To fully protect the prototype, when overcurrent protection is triggered, all converters of both UPS systems are switched off.

As

Figure 5h shows, at

ms, all power converter IGBTs are deactivated, and as a consequence of this, the load voltage is no longer ensured. In an industrial or medical application, this would lead to a supply interruption of extremely important loads, which could result in negative social and economic consequences.

These results show the importance of ZSCC elimination as well as the effectiveness of the proposed control technique in its suppression.

4.3. System Analysis for Different Load-Sharing Conditions

The capability of the proposed control techniques in simultaneously ensuring a high-quality load voltage and distributing the load power between the two UPS systems, while keeping their overall stability, is shown in

Figure 6 and

Figure 7.

The load used in this section is the same as the load used in the previous section: a full-bridge rectifier feeding an RC parallel circuit ( and ) is connected to phase A, an RL load is linked to phase B ( and ), and a resistor of is connected to phase C.In these results, initially, UPS1 provides 75% of the load power, whereas UPS2 supplies the remaining 25%. Then, the percentage of the load power assigned to each UPS is determined to be 50%, and, finally, the power assigned to UPS1 is decreased to 25% with the UPS2 supplying the remaining 75%.

Figure 6 presents the generated load voltage, load phase currents, load neutral current, LSC phase currents, LSC neutral leg currents, and, finally, the average UPS system output power and total power, respectively.

Firstly, from

Figure 6a, it is observed that a high-quality load voltage waveform is permanently ensured by the paralleled UPS systems during all different load-sharing conditions with a THD of approximately 1.2%. It is worth mentioning that this THD value is below the maximum value (8%) recommended by the IEC Standard 62040-3. The currents absorbed by the three-single phase loads connected to the UPS systems (full-bridge rectifier feeding an RC circuit + RL load + R load) are presented in

Figure 6b. From this subfigure, it can be observed that for the different load power distributions, even when the load-sharing condition changes, the total current absorbed by the load remains practically unchanged.

The load neutral current, which corresponds to the sum of all load phase currents, is presented in

Figure 6c. It can be seen that this current corresponds to a very irregular waveform with a peak value of approximately 7 A.

Figure 6d presents the LSC1 phase currents, whereas

Figure 6e demonstrates the current in the neutral leg of this converter. From

Figure 6d, it can be seen that the magnitudes of the LSC1 phase currents clearly change for the different tested load-sharing conditions. Similarly, from

Figure 6e, it is observed that as the UPS1 supplies a lower value of power to the load, the current that flows in the converter neutral leg also decreases. In

Figure 6f,g, a similar behavior is observed for the LSC2 phase and neutral leg currents. In this case, as the power supplied by UPS2 to the load is increased, the LSC2 phase currents become higher. In turn, the neutral leg current of this converter also increases, as demonstrated in

Figure 6g.

Once again, from

Figure 6e,g, it can be seen that the neutral leg currents reach higher peak values than the LSC phase current values. For example, note that when a given UPS supplies 75% of the load power, the peak value observed in the LSC phases is roughly 10 A. The peak value reached by each LSC neutral current is clearly higher than this value (≈

). This is also verified for the other load-sharing conditions, in which the neutral leg currents reach a higher value than the LSC phase current peak. Hence, these results show that the LSC neutral leg current peaks are higher than the LSC phase current peaks, even for asymmetric load power distributions.

From

Figure 6d,f it can be observed that the output power of each UPS rapidly changes to the new target value, with slower changes being observed in the calculated average powers presented in

Figure 6h, only because a time horizon of one period (20 ms) is required in their calculation. Thus, after roughly only 20 ms, all presented average powers stabilize at the new value.

Figure 7 presents the ZSCC, the input currents of both UPS systems, and the DC buses capacitor voltage for the same load-sharing conditions presented in

Figure 6.

Firstly, from

Figure 7a, it is observed that the ZSCC is effectively suppressed, presenting a ripple near zero for any load-sharing condition. With the ZSCC eliminated, the UPS systems have correct operation. Hence, as shown in

Figure 7b,c both UPS systems present near-sinusoidal input currents for the different load-sharing conditions, even supplying a highly unbalanced load.

During all these power distribution changes, as shown in

Figure 7d,e, the DC bus capacitor voltage balancing is ensured in both UPS systems, which is also crucial for the correct UPS system operation. Moreover, even for different load-sharing conditions, the UPS controllers are able to maintain the voltage of both DC buses near the defined reference of 220 V.

These results show that the proposed techniques allow the UPS systems to simultaneously supply a highly unbalanced load, with the absorbed load power being distributed between these systems, a high-quality voltage waveform being ensured, and the undesired ZSCC being effectively eliminated.

4.4. Power Quality Analysis

In this section, a power quality analysis is presented for the proposed system. When UPS systems are installed in a given facility, they must respect certain power quality requirements, namely regarding the harmonic distortion of the generated load voltage and current that the UPS absorbs from the power grid. Typically, the load voltage generated by a UPS system must present a maximum THD value lower than 8% as defined in the IEC Standard 62040-3. On the other hand, the absorbed grid current should have low harmonic distortion and therefore low THD value.

All presented results in this section were obtained using a YOKOGAWA WT3000 power analyzer.

Figure 8 shows power analyzer results when both UPS systems supply half of the power to the load used in

Section 4.2 and

Section 4.3. In the figure, the three generated load phase voltage waveforms (upper three), a grid line-to-line voltage, and a phase current waveform (lower two) are presented. Relevant measurements regarding these voltage and grid waveforms are also shown in this figure, including RMS and THD values.

Regarding the RMS value of the generated voltages, as shown in

Table 3, the line-to-line RMS voltage is set to 120 V, and, therefore, the RMS phase voltage reference is

. As seen in

Figure 8, the RMS of the generated load phase voltages corresponds approximately to this reference, with a value of

V in phase A,

V in phase B, and

V in phase C, corresponding to deviations of −0.88%, −3.70%, and 2.55%, respectively. These small deviations are observed mainly due to the fact that a highly unbalanced load is connected to the UPS systems. As for the load voltage harmonic distortion, it can be seen that in all phases, a very low THD value is observed. The mean THD value is roughly 1.23%, which corresponds to a value well below the maximum limit of 8% recommended by the IEC Standard 62040-3.

As for the total absorbed grid current (phase R, grey waveform), for these test conditions, it has an RMS value of roughly A with a low THD of approximately 2.03%. To avoid redundancy in the results, since the other two absorbed grid currents present similar waveform, RMS and THD values, only the phase R grid current is analyzed here.

In the following, an analysis is presented to evaluate if low THD values can be ensured even when wrong filter parameter values are considered in UPS controllers. Typically, this can occur for two main reasons: filter parameter deviation (e.g., due to component aging) or wrong filter parameter characterization. Hence, there can be situations in which filter parameter values above or below the real values are wrongly considered in UPS controllers. These two situations were considered in the analysis.

The load voltage THD behavior was studied with UPS controllers considering a wrong load-side filter inductance or capacitance, while the grid current THD behavior was analyzed with UPS controllers considering wrong grid-side filter values. To evaluate the impact of each filter component, the same error was simultaneously considered in UPS1 and UPS2 controllers.

The influence that considering wrong load-side filter inductance values in UPS controllers has on the load voltage THD is demonstrated in

Table 4. As shown in this table, when the actual inductance value (

mH) is considered, a load voltage THD of roughly 1.2% is obtained. When an inductance 10% higher than the real parameter value is considered in UPS controllers, the load voltage THD increases to 1.5%. Similarly, by considering the load-side filter inductance 20% higher than its real value (

mH), the THD increases even more, to 2.0%. When a value 30% above the real inductance value is considered in the controllers (

mH), the load voltage THD corresponds to 2.6%. This THD value is more than twice the original, 1.2%. Nevertheless, this is a significantly lower value than the recommended maximum THD of 8%.

On the other hand, when controllers consider a lower inductance than their actual value, the load voltage THD remains practically unchanged, with a constant value of roughly 1.2%, as seen in

Table 4. This THD value is observed even when a value 30% below the real inductance (3.15 mH) is considered in the UPS controllers. Hence, for the tested conditions, it can be seen that when the considered load-side filter inductance value in UPS controllers is below the real parameter value, no tangible impact is observed on the load voltage THD.

These results allow the conclusion that even for a significant error between the load-side filter inductance value considered in UPS controllers and its real value, a load voltage with low THD is generated, which is significantly below 8% for all conditions demonstrated in

Table 4.

In

Table 5, the impact of considering wrong load-side filter capacitance values on load voltage THD is shown. As demonstrated in this table, when the real capacitance value is considered in UPS controllers, a THD of approximately 1.2% is obtained. When the considered load-side filter capacitance is 10% above the real value (66 μF), the load voltage THD slightly increases to 1.3%. If the considered capacitance value is 20% higher than the real value (72 μF), then the THD increases even more to roughly 1.5%. Finally, with an error of 30%, the load voltage THD reaches 1.9%.

As for the observed load voltage THD behavior when a capacitance below the real parameter value is considered in the UPS controllers, a similar behavior to the previous presented analysis is observed regarding the load-side filter inductance. Thus, as demonstrated in

Table 5, even when a capacitance 30% below the real capacitance is considered, the load voltage THD remains at 1.2%. Hence, it can be observed that for the tested conditions, when the considered load-side filter capacitance value is below the real parameter, no impact is observed on the load voltage THD.

These results show that even when a significant error exists between the considered and real capacitance value, a high-quality load voltage waveform is generated with a THD significantly below 8%.

Finally,

Table 6 shows the grid current THD behavior when wrong grid-side filter inductance values are considered in UPS controllers. As shown in this table, when the real inductance value (10 mH) is considered in UPS controllers, a grid-current THD of 1.9% is obtained. In this analysis, from

Table 6, it can be seen that the grid current harmonic distortion increases when inductance values below the real are considered in the UPS controllers. In fact, for the tested conditions, when the considered grid-side inductance is higher than its actual value, slight decreases are observed in the THD. However, it was observed that in these cases, the overall system efficiency also slightly decreases.

The highest THD value (3.5%) is observed when an inductance value 30% below the real inductance is considered in UPS controllers. This THD value corresponds to almost twice the grid current THD value obtained with the real inductance value being considered; however, this is still an acceptable THD value.

In sum, these results show that even when significant deviations exist between real and considered filter parameters values in UPS controllers, the proposed controllers and UPS systems absorb grid currents and ensure load voltage waveforms with low harmonic distortion.

4.5. System Dynamic Response under Load Changes

In this section, the dynamic response of the proposed controllers when an additional load is connected to the UPS systems in operation is demonstrated.

Figure 9 and

Figure 10 present the behavior of the system when both UPSs are initially supplying a three-phase three-wire linear load and at a given instant a non-linear unbalanced load is connected to the UPS systems. In the tested conditions, UPS1 supplies 75% of the power to the load, and UPS2 supplies the remaining 25%. The linear load has a 100

resistance per phase, whereas the second load consists of the rectifier + RC circuit in phase A and RL load in phase B, which is connected to the UPS systems at

ms.

Figure 9 shows the generated load phase voltage, load phase currents, LSC phase currents and average UPS system output power, and total load power.

From

Figure 9a, it can be seen that even when the unbalanced non-linear load is connected to the UPS systems, a high-quality load voltage is permanently generated by both UPS controllers. Particularly, no disturbance is observed in the load voltage even with the behavior change in the load currents after connection of the second load (

Figure 9b).

It can be seen that the LSC phase currents rapidly adapt in order to maintain a high-quality output voltage waveform, as shown in

Figure 9c,d.

Figure 9e shows the behavior of UPS system output power and total load power. After the load connection, the UPS systems start to supply a higher power level, and, thus, the presented powers start to rise. As shown in this subfigure, the load-sharing condition is kept even after the connection of the rectifier + RC circuit in phase A and RL load in phase B is made.

Figure 10 shows the DC bus capacitor voltage, GSC1 and GSC2 phase currents, total currents absorbed from the grid, and the ZSCC during the same test.

Figure 10a,b demonstrate that the connection of the additional load has little impact on the DC bus of both UPS systems with the DC buses’ capacitor voltage balancing being ensured even at the instant in which the second load is connected. On the other hand, the DC buses have a small voltage drop, which is rapidly compensated, with no overshoot. This voltage drop is observed because the GSC current references are not instantaneously updated since they are computed by considering the balancing of average active power in the UPS system instead of instantaneous active power.

The GSC1 and GSC2 currents are presented in

Figure 10c,d, respectively. From these two subfigures, it can be seen that after the connection of the second load, the magnitude of both GSC1 and GSC2 clearly increases with the UPS systems absorbing a higher power value from the grid. Hence, as shown in

Figure 10e, the total absorbed grid current magnitude also increases after the second load connection.

Finally, from

Figure 10e, it is observed that the ZSCC is effectively eliminated. The connection of the additional load does not affect the suppression of this current, which is crucial for the overall stable operation of both UPS systems.

These results show that with the proposed control techniques, the UPS systems show an overall good dynamic response, even when abrupt changes in the behavior of the critical load occur.

4.6. System Simulation for a High-Power Application

In the previous sections, experimental results were shown considering a low power lab-oriented prototype, which, in turn, is operated at low voltage due to safety and material protection reasons. However, UPS systems usually supply high-power loads with higher voltage and current levels than those previously considered. In this section, the operation of the proposed UPS systems feeding high-power loads at higher voltage and current levels is demonstrated with simulation results. Hence, instead of considering an RMS grid and load voltages of 120 V as used in the previous sections, for the following results, a 400 V RMS value is considered for the line-to-line grid and load voltages. On the other hand, instead of considering a DC bus with 220 V, in this case, the DC bus voltage reference is 700 V. All filter parameters and control weighting factors are equal to the values presented in

Table 2 and

Table 3.

Figure 11 shows the response of the system when both UPS systems supply half of the power to a three-phase resistor (

R = 10

per phase); at a given instant, a second load consisting of a single-phase rectifier + RC (

R = 20

and

C = 200 μF) circuit is connected to phase A, and an RL (

R = 10

and

L = 20 mH) load is connected to phase B.

The figure presents the generated load phase voltage, load phase currents, LSC phase currents, DC bus capacitor voltages, average UPS system output power and total load power, and the circulating current.

As previously mentioned, for the presented conditions, the RMS line-to-line voltage reference is set to 400 V. Hence, the load phase voltages, which are presented in

Figure 11a, should have an RMS voltage of

and a peak value of

. As seen in this subfigure, the generated load voltage waveform has higher distortion in comparison to all previously presented results. However, as previously mentioned, for these simulation results, considering a high-power level, the filter parameters are the same as those used in the experimental results for lower power/voltage levels. This may suggest that for higher voltage/power levels, filter parameter redesign may have to be considered.Nevertheless, even by using the presented filter parameters, near-sinusoidal load voltages are still observed with a THD value of approximately 4% (well below the maximum limit of 8% defined in IEC Standard 62040-3). Note that this THD value is obtained even when supplying unbalanced and non-linear currents to the load, as demonstrated in

Figure 11b.

The LSC phase currents are presented in

Figure 11c,d, in which a higher ripple than in the previous sections can be seen. This is observed mainly because UPS systems are operating with high voltages at their output and DC buses, and, consequently, considerably high voltages can be applied in the load-side filter inductor, which leads to this high ripple in LSC currents. However, in comparison to the previous sections, a similar relation between the ripple and fundamental frequency magnitude of these currents is observed.

From

Figure 11e,f it can be seen that each DC bus capacitor voltage is roughly 350 V, which indicates that these capacitor voltages are balanced and that the DC bus voltage is roughly 700 V, which corresponds to the defined reference value. These two subfigures also show that even in high-power applications, the connection of the additional load has little impact on the DC bus of both UPS systems, with the voltage drop being compensated with no overshot in DC buses.

Figure 11g shows the behavior of UPS system output power and total load power. The UPS systems supply an average active power slightly over

kW, which gives a total power supplied to the load of roughly 15 kW. After the connection of the additional load, the load-sharing condition is kept with the total power supplied, reaching roughly 22 kW.

Finally, from

Figure 11h, it is observed that even when supplying high-power loads, the circulating current is effectively eliminated.

The importance of the elimination of this current is emphasized in

Figure 12. This figure also demonstrates the effectiveness of the proposed ZSCC suppression mechanism in a high-power application. The undesired ZSCC effects on UPS systems operation phenomena were previously demonstrated in

Section 4.2. Nevertheless, in simulation environment, since no overcurrent protections are considered for UPS systems protection, these undesired effects can be better demonstrated. The figure presents the ZSCC, GSC currents, LSC phase currents, LSC neutral leg currents, and the generated load voltage when the high-power unbalanced load previously described is supplied by the UPS systems. In this test, the ZSCC suppression mechanism is deactivated at

ms (

).

As

Figure 12a shows, after the deactivation, the ZSCC magnitude significantly rises, reaching a maximum absolute value of roughly 25 A. Hence, as presented in

Figure 12b,c both UPS input currents are highly distorted and reach peak values that correspond to roughly twice the peak value observed in normal operation (ZSCC suppression ON).

The existence of ZSCC has practically no impact on the LSC phase currents, as seen in

Figure 12d,e. However, similarly to the GSCs currents, the neutral leg currents in both LSCs rise to values roughly twice the peak value observed in normal operation, reaching values of 100 A.

Nevertheless, as seen in

Figure 12h, the circulating current has no tangible impact on the total current absorbed from the the power grid. Even when a high ZSCC exists, near-sinusoidal currents are absorbed.

Finally, as

Figure 12i demonstrates, the load voltage is also ensured by the UPS systems, even with a high circulating current. However, as seen in

Section 4.2, in a real-world application, the ZSCC can increase the current values of GSCs and neutral legs to hazardous values. This increases losses in the systems and causes additional stress to the components of the UPS, reducing their lifetime and possibly causing their failure. Additionally, overcurrent protections can be triggered, leading to the deactivation of the UPS system and consequently compromising the critical load.

These simulation results show that with the proposed control techniques, the proposed UPS systems can be used to feed not only low-power critical loads but also high-power critical applications.