Analysis of Instability Behavior and Mechanism of E-Mode GaN Power HEMT with p-GaN Gate under Off-State Gate Bias Stress

Abstract

:1. Introduction

1.1. Gate-Lag Effect

1.2. Prolonged Negative Gate Bias Stress

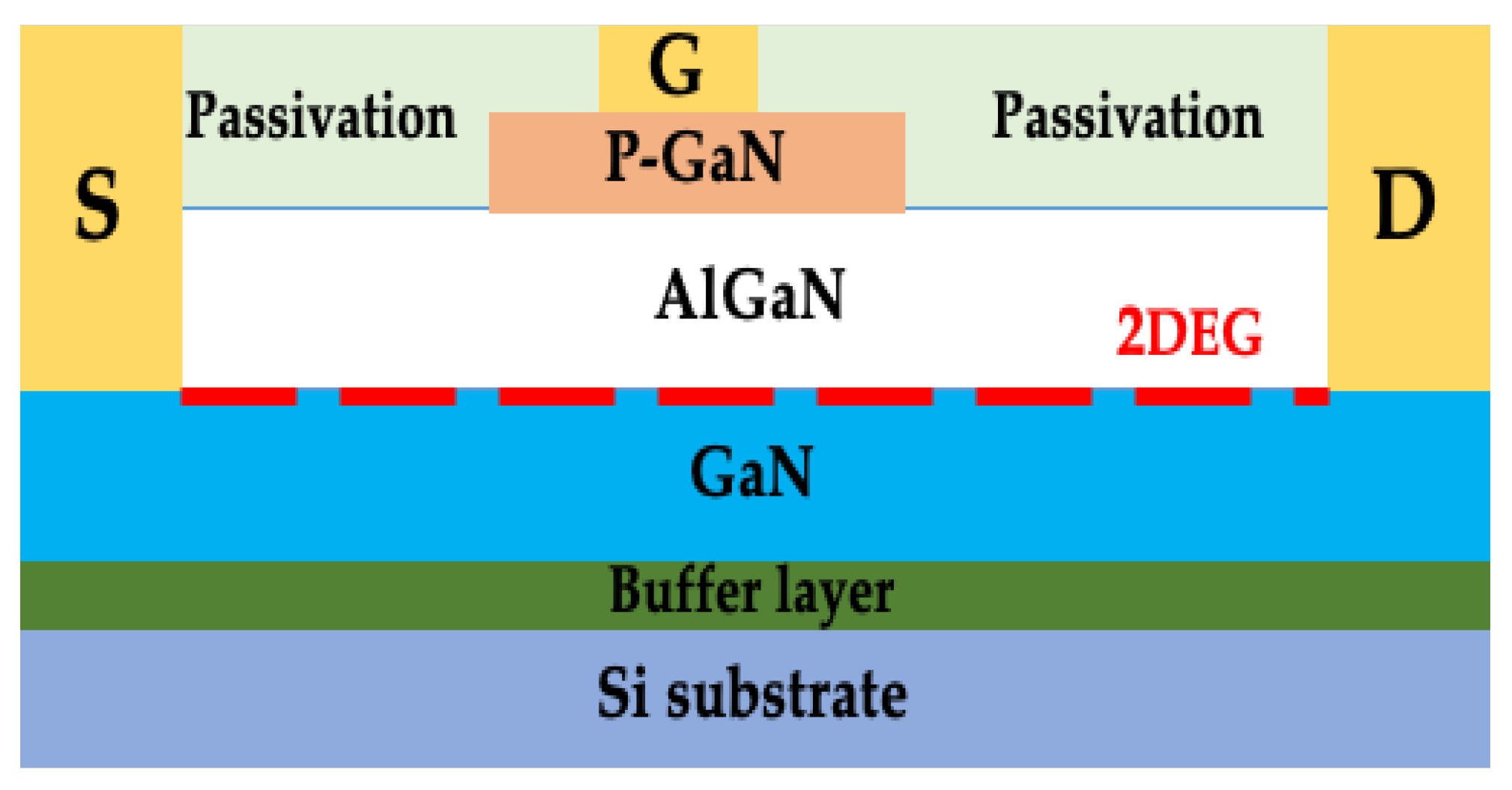

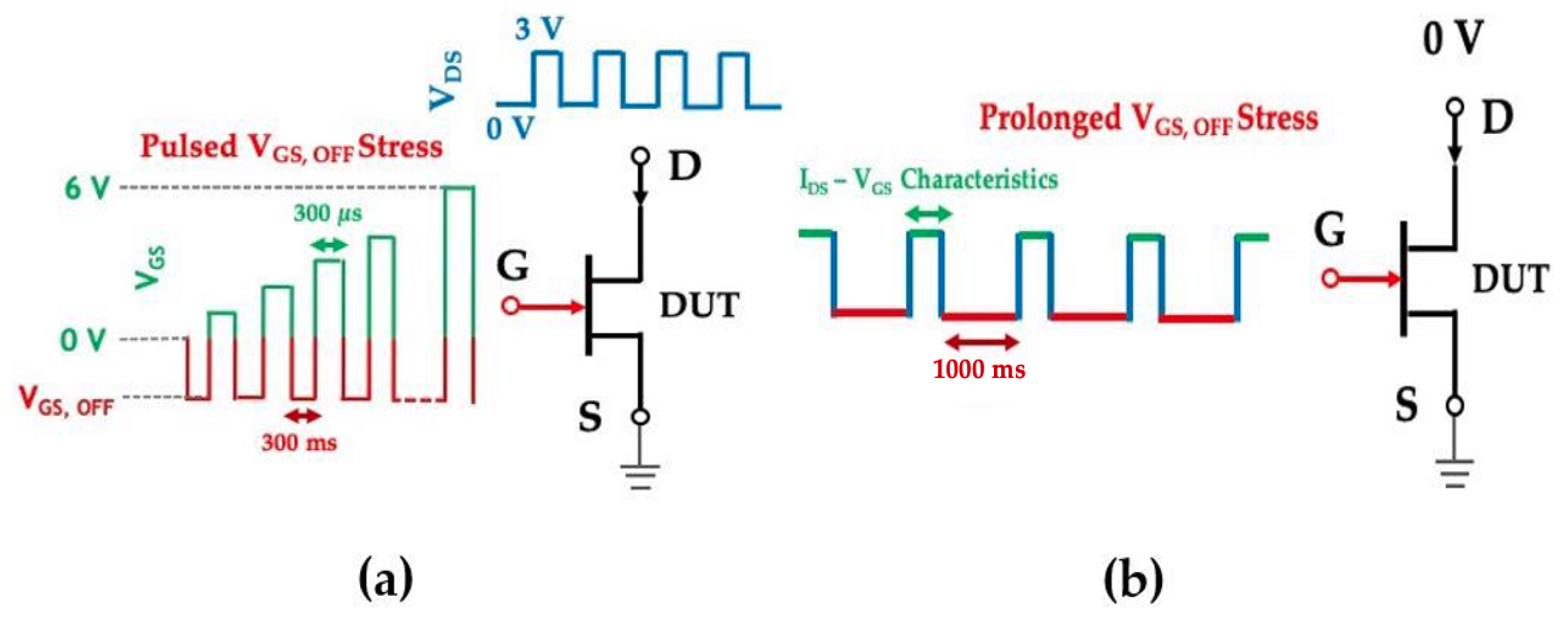

2. Experimental Details

3. Results and Discussion

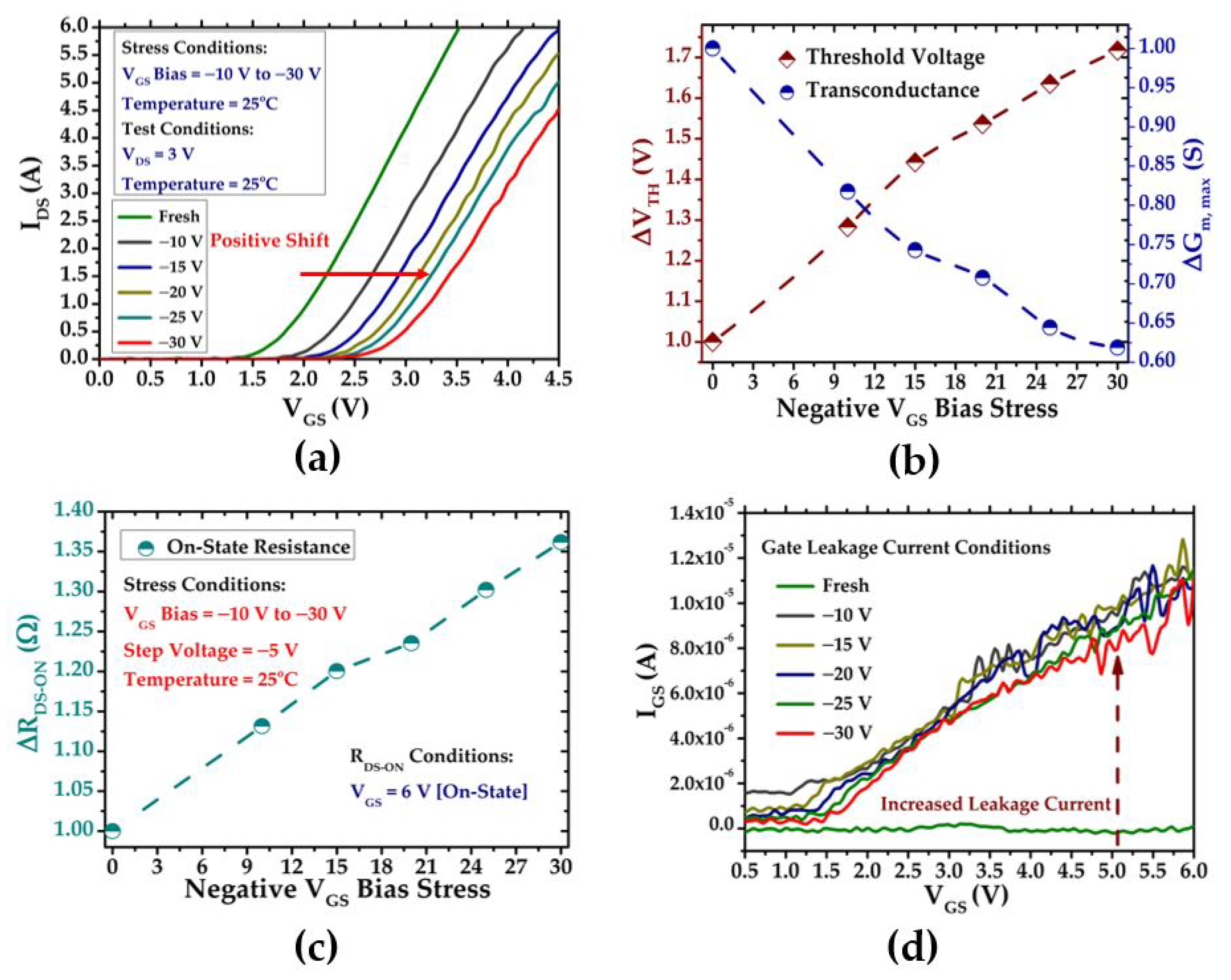

3.1. Degradation of Electrical Parameters under Pulsed VGS Bias Stress

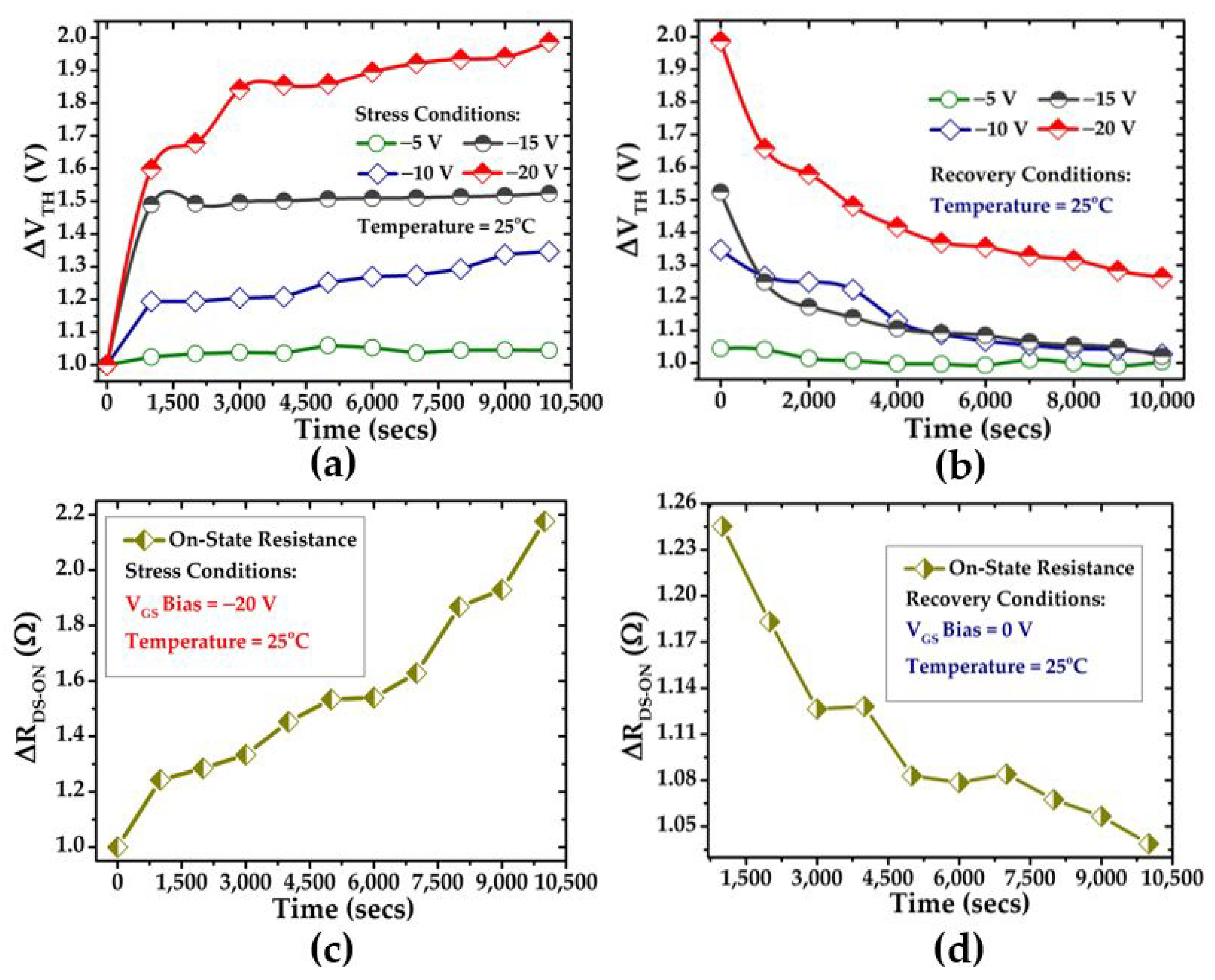

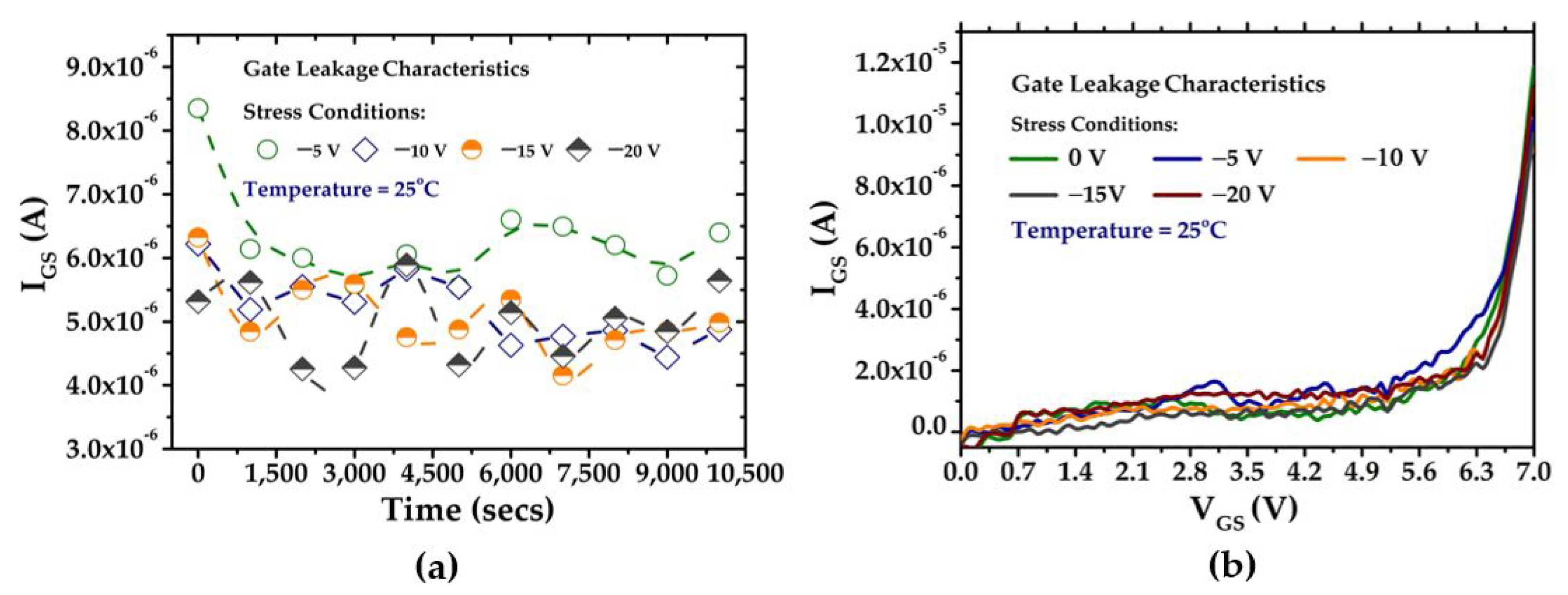

3.2. Influence of Stress Time Evolution on Negative VGS Bias Stresses

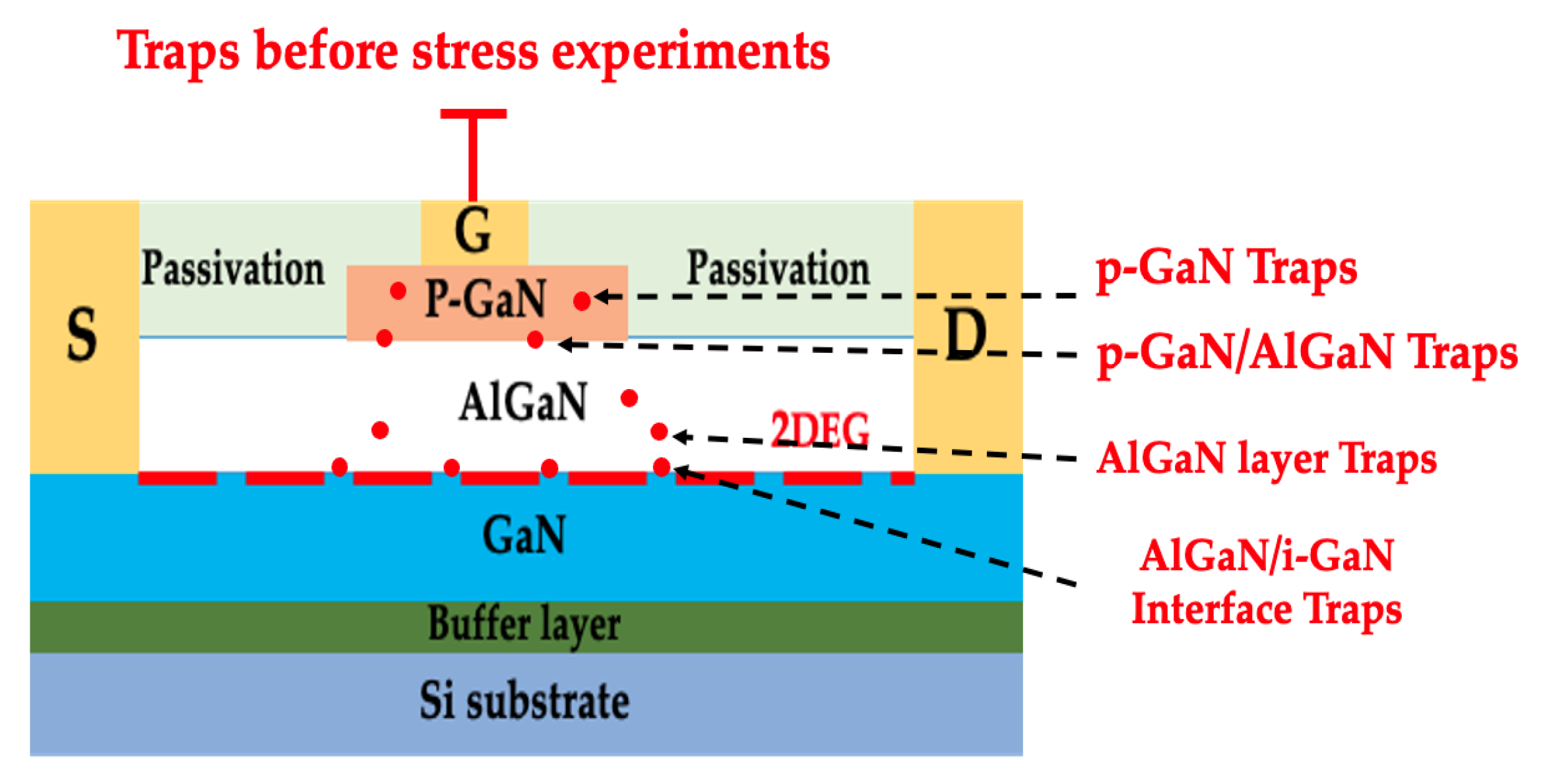

3.3. Influenced Degradation Mechanism and Analyzations

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Mishra, U.K.; Shen, L.; Kazior, T.E.; Wu, Y.F. GaN-based RF power devices and amplifiers. Proc. IEEE 2008, 96, 287–305. [Google Scholar] [CrossRef]

- Tang, Y.; Shinohara, K.; Regan, D.; Corrion, A.; Brown, D.; Wong, J.; Schmitz, A.; Fung, H.; Kim, S.; Micovic, M. Ultrahigh-speed GaN high-electron-mobility transistors with fT/fmax of 454/444 GHz. IEEE Electron Device Lett. 2015, 36, 549–551. [Google Scholar] [CrossRef]

- Wu, Y.F.; Moore, M.; Saxler, A.; Wisleder, T.; Parikh, P. 40-W/mm double field-plated GaN HEMTs. In Proceedings of the 2006 64th Device Research Conference, State College, PA, USA, 26–28 June 2006; pp. 151–152. [Google Scholar]

- Lu, B.; Palacios, T. High Breakdown (>1500 V) AlGaN/GaN HEMTs by Substrate-Transfer Technology. IEEE Electron Device Lett. 2010, 31, 951–953. [Google Scholar] [CrossRef]

- Pengelly, R.S.; Wood, S.M.; Milligan, J.W.; Sheppard, S.T.; Pribble, W.L. A review of GaN on SiC high electron-mobility power transistors and MMICs. IEEE Trans. Microw. Theory Tech. 2012, 60, 1764–1783. [Google Scholar] [CrossRef]

- Oeder, T.; Castellazzi, A.; Pfost, M. Experimental study of the short-circuit performance for a 600V normally-off p-gate GaN HEMT. In Proceedings of the 2017 29th International Symposium on Power Semiconductor Devices and IC’s (ISPSD), Sapporo, Japan, 28 May–1 June 2017; pp. 211–214. [Google Scholar]

- Li, H.; Li, X.; Wang, X.; Lyu, X.; Cai, H.; Alsmadi, Y.M.; Liu, L.; Bala, S.; Wang, J. Robustness of 650-V enhancement-mode GaN HEMTs under various short-circuit conditions. IEEE Trans. Ind. Appl. 2018, 55, 1807–1816. [Google Scholar] [CrossRef]

- Fernández, M.; Perpiñá, X.; Vellvehi, M.; Jorda, X.; Roig, J.; Bauwens, F.; Tack, M. Short-circuit capability in p-GaN HEMTs and GaN MISHEMTs. In Proceedings of the 2017 29th International Symposium on Power Semiconductor Devices and IC’s (ISPSD), Sapporo, Japan, 28 May–1 June 2017; pp. 455–458. [Google Scholar]

- Fernández, M.; Perpiñà, X.; Roig, J.; Vellvehi, M.; Bauwens, F.; Jordà, X.; Tack, M. P-GaN HEMTs drain and gate current analysis under short-circuit. IEEE Electron Device Lett. 2017, 38, 505–508. [Google Scholar] [CrossRef]

- Del Alamo, J.A.; Joh, J. GaN HEMT reliability. Microelectron. Reliab. 2009, 49, 1200–1206. [Google Scholar] [CrossRef]

- Meneghini, M.; Rossetto, I.; Rizzato, V.; Stoffels, S.; Van Hove, M.; Posthuma, N.; Wu, T.L.; Marcon, D.; Decoutere, S.; Meneghesso, G.; et al. Gate stability of GaN-based HEMTs with p-type gate. Electronics 2016, 5, 14. [Google Scholar] [CrossRef]

- Wu, T.L.; Marcon, D.; De Jaeger, B.; Van Hove, M.; Bakeroot, B.; Lin, D.; Stoffels, S.; Kang, X.; Roelofs, R.; Groeseneken, G.; et al. The impact of the gate dielectric quality in developing Au-free D-mode and E-mode recessed gate AlGaN/GaN transistors on a 200mm Si substrate. In Proceedings of the 2015 IEEE 27th International Symposium on Power Semiconductor Devices & IC’s (ISPSD), Hong Kong, China, 10–14 May 2015; pp. 225–228. [Google Scholar]

- Huang, X.; Liu, Z.; Li, Q.; Lee, F.C. Evaluation and application of 600 V GaN HEMT in cascode structure. IEEE Trans. Power Electron. 2013, 29, 2453–2461. [Google Scholar] [CrossRef]

- Chen, S.H.; Chou, P.C.; Cheng, S. Evaluation of thermal performance of packaged GaN HEMT cascode power switch by transient thermal testing. Appl. Therm. Eng. 2016, 98, 1003–1012. [Google Scholar] [CrossRef]

- Wu, C.H.; Han, P.C.; Liu, S.C.; Hsieh, T.E.; Lumbantoruan, F.J.; Ho, Y.H.; Chen, J.Y.; Yang, K.S.; Wang, H.C.; Lin, Y.K.; et al. High-performance normally-OFF GaN MIS-HEMTs using hybrid ferroelectric charge trap gate stack (FEG-HEMT) for power device applications. IEEE Electron Device Lett. 2018, 39, 991–994. [Google Scholar] [CrossRef]

- Hung, T.H.; Park, P.S.; Krishnamoorthy, S.; Nath, D.N.; Rajan, S. Interface charge engineering for enhancement-mode GaN MISHEMTs. IEEE Electron Device Lett. 2014, 35, 312–314. [Google Scholar] [CrossRef]

- Uemoto, Y.; Hikita, M.; Ueno, H.; Matsuo, H.; Ishida, H.; Yanagihara, M.; Ueda, T.; Tanaka, T.; Ueda, D. Gate injection transistor (GIT)—A normally-off AlGaN/GaN power transistor using conductivity modulation. IEEE Trans. Electron Devices 2007, 54, 3393–3399. [Google Scholar] [CrossRef]

- Zanandrea, A.; Bahat-Treidel, E.; Rampazzo, F.; Stocco, A.; Meneghini, M.; Zanoni, E.; Hilt, O.; Ivo, P.; Wuerfl, J.; Meneghesso, G. Single-and double-heterostructure GaN-HEMTs devices for power switching applications. Microelectron. Reliab. 2012, 52, 2426–2430. [Google Scholar] [CrossRef]

- Moens, P.; Vanmeerbeek, P.; Banerjee, A.; Guo, J.; Liu, C.; Coppens, P.; Salih, A.; Tack, M.; Caesar, M.; Uren, M.; et al. On the impact of carbon-doping on the dynamic Ron and off-state leakage current of 650V GaN power devices. In Proceedings of the 2015 IEEE 27th International Symposium on Power Semiconductor Devices & IC’s (ISPSD), Hong Kong, China, 10–14 May 2015; pp. 37–40. [Google Scholar]

- Mahajan, D.; Khandelwal, S. Impact of p-GaN layer doping on switching performance of enhancement mode GaN devices. In Proceedings of the 2018 IEEE 19th Workshop on Control and Modeling for Power Electronics (COMPEL), Padua, Italy, 25–28 June 2018; pp. 1–4. [Google Scholar]

- He, J.; Tang, G.; Chen, K.J. VTH Instability of p-GaN Gate HEMTs Under Static and Dynamic Gate Stress. IEEE Electron Device Lett. 2018, 39, 1576–1579. [Google Scholar]

- Efthymiou, L.; Murukesan, K.; Longobardi, G.; Udrea, F.; Shibib, A.; Terrill, K. Understanding the threshold voltage instability during OFF-state stress in p-GaN HEMTs. IEEE Electron Device Lett. 2019, 40, 1253–1256. [Google Scholar] [CrossRef]

- Wang, H.; Xie, R.; Liu, C.; Wei, J.; Tang, G.; Chen, K.J. Maximizing the performance of 650 V p-GaN gate HEMTs: Dynamic ron characterization and gate-drive design considerations. In Proceedings of the 2016 IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, USA, 18–22 September 2016; pp. 1–6. [Google Scholar]

- Vetury, R.; Zhang, N.Q.; Keller, S.; Mishra, U.K. The impact of surface states on the DC and RF characteristics of AlGaN/GaN HFETs. IEEE Trans. Electron Devices 2001, 48, 560–566. [Google Scholar] [CrossRef]

- Nguyen, C.; Nguyen, N.; Grider, D. Drain current compression in GaN MODFETs under large-signal modulation at microwave frequencies. Electron. Lett. 1999, 35, 1380–1382. [Google Scholar] [CrossRef]

- Chen, Y.; Feng, J.; Wang, J.; Xu, X.; He, Z.; Li, G.; Lei, D.; Chen, Y.; Huang, Y. Degradation behavior and mechanisms of E-mode GaN HEMTs with p-GaN gate under reverse electrostatic discharge stress. IEEE Trans. Electron Devices 2020, 67, 566–570. [Google Scholar] [CrossRef]

- Xu, X.; Li, B.; Chen, Y.; Wu, Z.; He, Z.; En, Y.; Huang, Y. Analysis of trap and recovery characteristics based on low-frequency noise for E-mode GaN HEMTs with p-GaN gate under repetitive short-circuit stress. J. Phys. D Appl. Phys. 2020, 53, 175101. [Google Scholar] [CrossRef]

- Guo, A.; del Alamo, J.A. Negative-bias temperature instability of GaN MOSFETs. In Proceedings of the 2016 IEEE International Reliability Physics Symposium (IRPS), Pasadena, CA, USA, 17–21 April 2016; pp. 4A-1-1–4A-1-6. [Google Scholar]

- Yen, C.T.; Hung, H.T.; Hung, C.C.; Lee, C.Y.; Lee, H.Y.; Lee, L.S.; Huang, Y.F.; Cheng, C.Y.; Chuang, P.J.; Hsu, F.J. Negative Bias Temperature Instability of SiC MOSFET. In Materials Science Forum; Trans Tech Publications Ltd.: Stafa-Zurich, Switzerland, 2016; Volume 858, pp. 595–598. [Google Scholar]

- Chen, J.; Hua, M.; Wei, J.; He, J.; Wang, C.; Zheng, Z.; Chen, K.J. OFF-state Drain-voltage-stress-induced VTH Instability in Schottky-type p-GaN Gate HEMTs. IEEE J. Emerg. Sel. Top. Power Electron. 2020. [Google Scholar] [CrossRef]

- Zhang, C.; Liu, S.; Li, S.; Li, N.; Tao, X.; Hou, B.; Zhou, B.; Wei, J.; Chen, Y.; Sun, W. Electrical performances degradations and physics based mechanisms under negative bias temperature instability stress for p-GaN gate high electron mobility transistors. Semicond. Sci. Technol. 2020, 36, 014007. [Google Scholar] [CrossRef]

- Elangovan, S.; Cheng, S.; Chang, E.Y. Reliability characterization of gallium nitride MIS-HEMT based cascode devices for power electronic applications. Energies 2020, 13, 2628. [Google Scholar] [CrossRef]

- Santarelli, A.; Cignani, R.; Gibiino, G.P.; Niessen, D.; Traverso, P.A.; Florian, C.; Schreurs, D.M.P.; Filicori, F. A double-pulse technique for the dynamic I/V characterization of GaN FETs. IEEE Microw. Wirel. Components Lett. 2013, 24, 132–134. [Google Scholar] [CrossRef]

- Guo, A.; del Alamo, J.A. Unified mechanism for positive-and negative-bias temperature instability in GaN MOSFETs. IEEE Trans. Electron Devices 2017, 64, 2142–2147. [Google Scholar] [CrossRef]

- Wu, T.L.; Marcon, D.; You, S.; Posthuma, N.; Bakeroot, B.; Stoffels, S.; Van Hove, M.; Groeseneken, G.; Decoutere, S. Forward bias gate breakdown mechanism in enhancement-mode p-GaN gate AlGaN/GaN high-electron mobility transistors. IEEE Electron Device Lett. 2015, 36, 1001–1003. [Google Scholar] [CrossRef]

- Chang, T.F.; Hsiao, T.C.; Huang, C.F.; Kuo, W.H.; Lin, S.F.; Samudra, G.S.; Liang, Y.C. Phenomenon of drain current instability on p-GaN gate AlGaN/GaN HEMTs. IEEE Trans. Electron Devices 2014, 62, 339–345. [Google Scholar] [CrossRef]

- Rossetto, I.; Meneghini, M.; Rizzato, V.; Ruzzarin, M.; Favaron, A.; Stoffels, S.; Van Hove, M.; Posthuma, N.; Wu, T.L.; Marcon, D.; et al. Study of the stability of e-mode GaN HEMTs with p-GaN gate based on combined DC and optical analysis. Microelectron. Reliab. 2016, 64, 547–551. [Google Scholar] [CrossRef]

- Li, S.; Liu, S.; Tian, Y.; Zhang, C.; Wei, J.; Tao, X.; Li, N.; Zhang, L.; Sun, W. High-temperature electrical performances and physics-based analysis of p-GaN HEMT device. IET Power Electron. 2019, 13, 420–425. [Google Scholar] [CrossRef]

- Ma, X.H.; Zhu, J.J.; Liao, X.Y.; Yue, T.; Chen, W.W.; Hao, Y. Quantitative characterization of interface traps in Al2O3/AlGaN/GaN metal-oxide-semiconductor high-electron-mobility transistors by dynamic capacitance dispersion technique. Appl. Phys. Lett. 2013, 103, 033510. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Elangovan, S.; Chang, E.Y.; Cheng, S. Analysis of Instability Behavior and Mechanism of E-Mode GaN Power HEMT with p-GaN Gate under Off-State Gate Bias Stress. Energies 2021, 14, 2170. https://doi.org/10.3390/en14082170

Elangovan S, Chang EY, Cheng S. Analysis of Instability Behavior and Mechanism of E-Mode GaN Power HEMT with p-GaN Gate under Off-State Gate Bias Stress. Energies. 2021; 14(8):2170. https://doi.org/10.3390/en14082170

Chicago/Turabian StyleElangovan, Surya, Edward Yi Chang, and Stone Cheng. 2021. "Analysis of Instability Behavior and Mechanism of E-Mode GaN Power HEMT with p-GaN Gate under Off-State Gate Bias Stress" Energies 14, no. 8: 2170. https://doi.org/10.3390/en14082170

APA StyleElangovan, S., Chang, E. Y., & Cheng, S. (2021). Analysis of Instability Behavior and Mechanism of E-Mode GaN Power HEMT with p-GaN Gate under Off-State Gate Bias Stress. Energies, 14(8), 2170. https://doi.org/10.3390/en14082170