1. Introduction

To meet the future energy needs and to address environmental concerns, it is necessary to utilize renewable energy resources and minimize the usage of fossil fuel. There has been an extensive growth and development of the renewable energy resources in recent years. Integration of the renewable energy resources into existing power system presents many technical challenges such as voltage stability, power quality problems. Today, more than 340,000 wind turbines are installed all over the world [

1]. With fixed speed wind turbine, all the fluctuations in the wind speed are transmitted as fluctuations in the mechanical torque into electrical power in the grid, which causes severe voltage fluctuations. As a result, curtailment is often in order as a necessary measure to reduce the grid impact.

Traditionally, switched capacitors and/or compensation inductors have been applied to the power grid to provide reactive power compensation for voltage support, which can reduce voltage fluctuations in the transmission line. However, these passive compensators, switched capacitors and inductors are not effective for voltage support since their response time is slow, they may produce either over-compensation or under-compensation. They are discrete in nature and less VAR is available when the voltage is low. To overcome these shortcomings, static synchronous compensator (STATCOM) has been introduced as an effective dynamic shunt compensator in transmission and distribution systems [

2,

3,

4,

5,

6,

7,

8,

9,

10,

11,

12,

13,

14,

15,

16]. Based on solid-state converter topologies, the STATCOMs present fast response time, less space requirement, higher operational flexibility, and excellent dynamic characteristics under various operating conditions.

For medium voltage (MV) applications, multilevel topologies become attractive for high power STATCOMs using commercially available switching devices, such as insulated gate bipolar transistor (IGBT) and integrated gate commutated thyristor (IGCT) [

14]. Since multilevel converter-based STATCOMs provide less harmonic generation and higher voltage capability, multilevel STATCOM configuration is a key for the direct connection to the power grid. The number of the STATCOM voltage levels should be maximized to obtain sinusoidal output waveforms and be minimized to make the STATCOM less complicated for reliable power stage and simple control purposes. For high power systems, three-level diode-clamped multilevel converter (DCMC)-based STATCOMs have been extensively adopted in high voltage power systems.

To reduce harmonic injection into the power grid and realize the transformerless direct connection, five-level DCMC-based STATCOMs have been receiving more attention recently [

15,

16]. However, the primary obstacle of the five-level DCMC-based STATCOMs is control complexity to control 24 switching devices and achieve charge balance of four dc-link capacitors, for example, by using a modified space vector pulse width modulation (SVPWM) and a capacitor current prediction algorithm with or without additional hardware [

15,

16]. As far as the implementation of the SVPWM technique is concerned, it is computationally very difficult to realize. For example, there are 125 switching state vectors to operate the five-level DCMC-based STATCOM in [

15].

A SVPWM-based switching strategy for a five-level DCMC-based STATCOM was presented without auxiliary power circuits for dc-link capacitor voltage balancing in [

15]. The proposed SVPWM method used the redundant switching vectors to mitigate dc-link capacitor voltage drift. However, this SVPWM method had limits of dc-link capacitor voltage balancing, depending on its modulation index. For example, when AC-side current angle was below 10 degrees, the proposed SVPWM method could not provide dc-link voltage balancing for the operating points above 0.55 modulation index. During the transient period, the proposed STATCOM operating point also passed through the region in which dc-link capacitor voltage balancing was not guaranteed.

In [

16], a SVPWM switching method for a DCMC-based STATCOM was proposed with a dc-link capacitor current prediction algorithm. First, the proposed SVPWM switching vectors were transferred into the 2-D elliptical plane (α’β’ frame) instead of the traditional αβ frame to simplify non-integer calculation. Similar to [

15], the redundant switching vectors were used for dc-link capacitor voltage balancing with the help of the additional high-density FPGA-based hardware to accomplish the complex calculation of the proposed SVPWM algorithm. In simulation results, the proposed SVPWM algorithm showed better performance of dc-link capacitor voltage balancing compared to the previous SVPWM-based switching methods. However, the time delay generated by the optimal value calculation algorithm would make an effect in the total performance of dc-link voltage balancing. And it is really difficult to apply the proposed SVPWM algorithm to high-level DCMC-based STATCOMs.

In [

17], a modified SPWM method was proposed in order to balance the two dc-link capacitor voltages for the three-level diode-clamped inverters. It is based on changing the boundary offset on the middle point of two carrier signals, which can control the neutral-point current to ensure balanced dc-link capacitor voltages. However, the boundary offset on the middle point restricts the compensation capability of the neutral-point potential when the modulation index is high and this modulation method cannot be directly applicable to the higher level DCMCs, for example, a five-level DCMC since there are more inner junctions between the dc-link capacitors. In addition, the main drawback in this approach is also the restricted stability in order to obtain a simple control strategy.

In [

18], a new carrier-based SPWM method with voltage balancing capability was proposed for the five-level diode-clamped back-to-back converter. For the back-to-back configuration, the unbalance tendencies of both sides (a rectifier and an inverter) have a potential to compensate each other because of the symmetry. By controlling proper offset voltages on both rectifier and inverter sides, the average current flowing into the inner junction can be adjusted to be equal to that flowing out from it. Then, the voltage balancing of the inner junction can be achieved. However, this voltage balancing method can be only applied to the back-to-back configuration, not the single type five-level DCMCs. In addition, the switch angles cannot be directly controlled in the proposed SPWM control. Instead, the offset voltage of each inner junction should be calculated and added to the phase voltage reference, which is not the sinusoidal reference.

A closed-loop neutral-point voltage balancing method based on carrier-overlapped pulse width modulation (COPWM) is proposed for the five-level diode-clamped multilevel inverters in [

19]. The COPWM method is a new carrier-based PWM modulation method, which satisfies the volt-second balance principle and has the voltage balancing ability for neutral-point-clamped (diode-clamped) multilevel converters. All the switching signals are obtained by comparing one reference voltage with four carrier signals. However, the generation of the four carrier signals require complex calculation by a DSP chip. Most of all, the four dc-link capacitor voltage balancing is achieved by three steps: (1) voltage balancing between the two outer capacitors, (2) voltage balancing between the two inner capacitors, and (3) voltage balancing between the two inner and the two outer capacitors, which also require complicated calculation and control procedure by the DSP chip. In addition, the harmonic performance of the COPWM method is worse than the phase-disposition PWM methods with the same voltage levels and carrier frequency. Finally, the proposed COPWM method is only applicable when each dc-link capacitance is the same.

In [

20], a modified inner-hexagon-vector-decomposition-based space-vector modulation (VDSVM-H1) method was introduced in order to obtain the capacitor voltage balancing with high modulation index and high-power factor by introducing six new vector sequences to each triangle and applying a new vector selection rule. However, the VDSVM-H1 control method has two drawbacks in practice. First, the power factor is very small when the converter works as an active power filter, which brings little challenge to the voltage balancing control. Second, since an error exists between the reference vector and the actual synthesized vector, the magnitude and phase errors increase with the increasing dwelling time of transitional vectors.

A new hybrid voltage balance method was proposed for the five-level DCMCs in [

21], where additional flying-capacitor-based auxiliary circuits were used to balance the upper or lower two capacitors, along with a zero-sequence injection method to balance the midpoint voltage. Based on this hybrid approach, the voltage stresses of power devices can be equalized, and the current ripples of inductors can also be suppressed. However, the proposed hybrid voltage balance method requires the auxiliary circuits to balance the upper or lower two capacitors, which need two flying capacitors and inductors, and eight IGBTs with freewheeling diodes for each phase.

As mentioned above, when the voltage level of the DCMC-based STATCOMs increases, the real-time SVPWM balancing control of the dc-link capacitors becomes an enormous challenge. Since thousands of switching space vectors require real-time process, it is extremely time consuming and burden for real-time controller implementation.

The main motivation of this paper on the five-level DCMC-based STATCOMs focuses on developing a simple control method which provides automatic voltage balancing of the dc-link capacitors and dynamic voltage regulation for the power grid. The proposed control method can be easily extended to the high-level DCMC-based STATCOMs by increasing the number of the voltage compensators and the control core circuits and be applicable to other multilevel converter-based STATCOMs, for example, a cascaded multilevel converter (CMC)-based STATCOM.

In this paper, a new five-level DCMC-based STATCOM is proposed using a simple one-cycle control (OCC) [

22,

23,

24,

25,

26] based on the level-shifted multilevel control, which presents a simple multilevel control approach with automatic dc-link voltage balancing. Compared to the conventional level-shifted control, the proposed level-shifted OCC of the five-level DCMC-based STATCOM has the variable amplitudes of four carrier signals instead of the fixed amplitudes. With variable amplitude control of the four carrier signals, the dc-link capacitor voltages automatically become balanced and equal to the reference voltage (

VDC/4) for the five-level DCMC-based STATCOM. Applying the proposed multilevel OCC method, voltage regulation at the point of common coupling (PCC) is achieved by dynamically changing the control reference for proper reactive power compensation. The most important merit of the proposed multilevel OCC method is to reduce a heavy computing burden. Especially, this merit is very effective in controlling high-level DCMC-based STATCOMs. In this paper, the voltage regulation equations of the proposed multilevel OCC for the five-level DCMC-based STATCOM are derived to describe its capability of voltage regulation at the PCC. Simulation and experimental results are presented to verify the proposed five-level STATCOM operation and the multilevel OCC performance during steady-state and dynamic operation modes.

2. Principle of One-Cycle Control for STATCOMs

STATCOMs improve the power factor and the power quality by providing the compensation current for the power grid. To accomplish this goal, the grid voltages are sensed and synchronized in generating the compensation current of the STATCOMs.

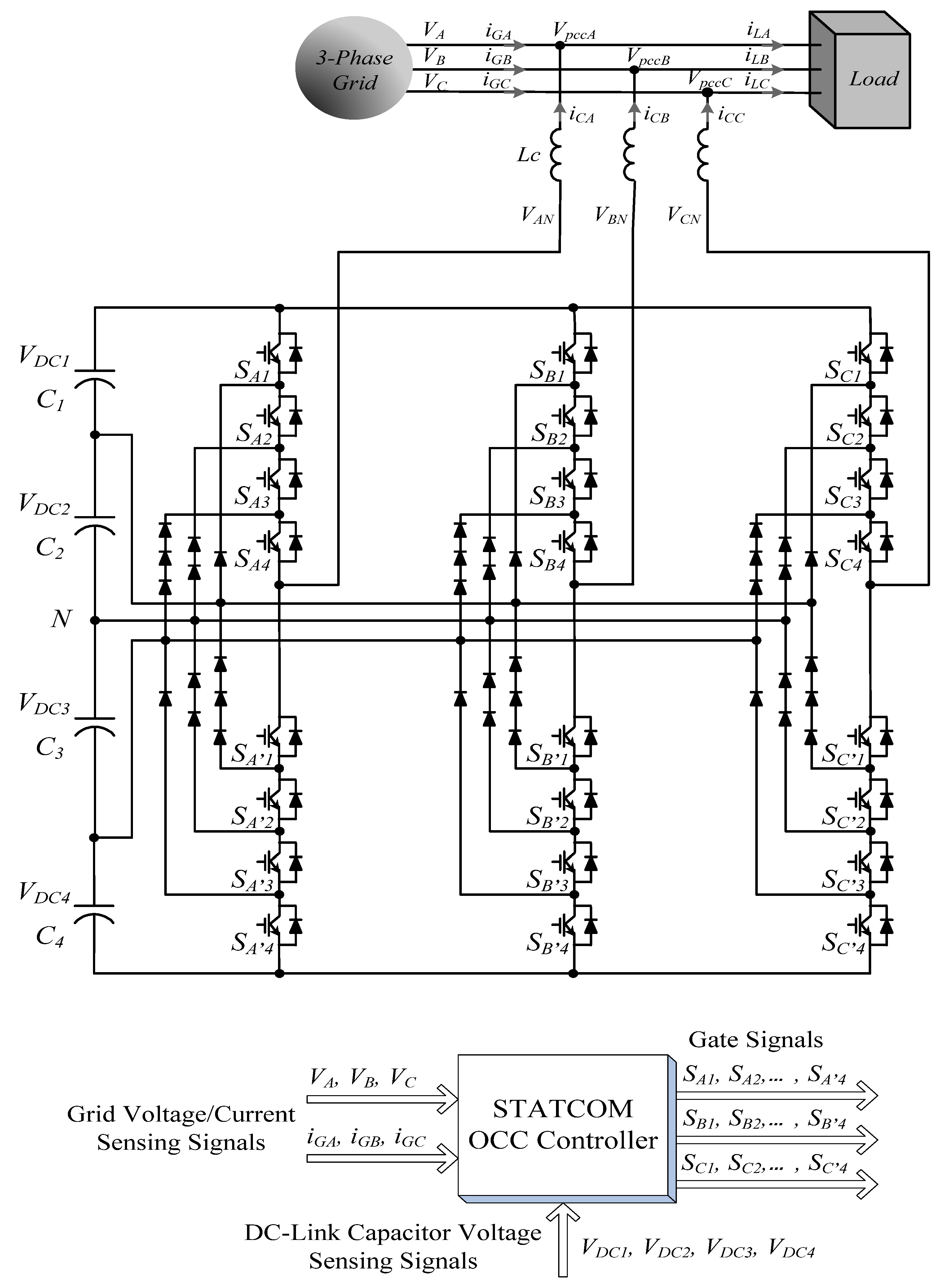

Figure 1 shows a five-level DCMC-based STATCOM configuration. The MV grid is represented by a three-phase voltage source and a three-phase load with the proposed five-level STATCOM connected in the PCC. However, if needed, the STATCOM can also be connected through the step-up transformer to high voltage transmission systems. The proposed five-level STATCOM system is comprised of three main parts: a five-level DCMC, a set of coupling inductors or a step-up transformer, and a STATCOM controller. First, the five-level DCMC has four dc-link capacitors (

C1-

C4) to produce a five-level output phase voltage (

VAN). In each phase leg, there are four complementary main switches (

SA1-

SA4 and

SA’1-

SA’4 for the phase-A leg,

SB1-

SB4 and

SB’1-

SB’4, and etc.). The voltage stress of each main switch is limited to one dc-link capacitor voltage (

VDC/4) thanks to the clamping diodes. Second, the main purpose of the coupling inductors is to filter out the harmonic components of the injected reactive current, which are generated by the pulsating output voltage of the five-level DCMC. Third, the STATCOM controller performs reactive power compensation by controlling the gate signals of the main switches, based on the measured grid phase voltages, grid phase currents, and dc-link capacitor voltages.

The proposed control method of the five-level DCMC-based STATCOM is based on injecting the compensation current into the power grid using the OCC controller. To derive the multi-carrier level-shifted OCC control equation of the five-level DCMC-based STATCOM, the main principle of the OCC method for a two-level voltage source converter (VSC) is reviewed first. For the three-phase two-level VSC, the relationship between the duty ratios of the VSC switches and the grid phase voltages can be defined as follows [

25]:

where

dSA’,

dSB’,

dSC’ are the duty ratios of the bottom switches (

SA’,

SB’,

SC’) in the two-level VSC and

VDC is the dc bus voltage, and

VA,

VB,

VC are the grid phase voltages.

One possible solution for (1), containing singular matrix and thus having no unique solution can be defined as follows:

Assume

K2 = −1, then from 0 ≤

d ≤ 1,

K1 can be defined as:

where

VA/

VDC is a modulation index and for the three-phase VSC with sinusoidal PWM, its maximum value is equal to 1/

. Thus, based on the defined

K1 and

K2, (2) can be rewritten by:

The control goal of the reactive compensation for the STATCOM is to realize the following relationship between the grid phase voltages and the grid phase currents to achieve power factor correction (PFC) operation for the power grid by the reactive currents of the STATCOM:

where

RE is the emulated resistance,

VA,

VB,

VC are the grid phase voltages and

iGA,

iGB,

iGC are the grid phase currents, and

i*CA~

i*CC are the STATCOM current references which can be defined as follows:

where

GR is the reference conductance related to the voltage fluctuation at the point of the STATCOM connection,

KP and

KI are the proportional and integral coefficients related to the grid impedances, and Δ

VpccA, Δ

VpccB, Δ

VpccC are the voltage variations at the PCC.

Combining (4) and (5) yields the control key equation of the three-phase two-level STATCOM, of which the reactive compensation strategy can be achieved by controlling the VSC switches in such a way that the duty ratios, the grid phase currents, and the compensation currents satisfy the following equation:

where

Vm =

VDC RS/

RE,

RS is the sensing resistance of the grid phase current and

iGA,

iGB,

iGC are the grid phase currents, and

VICjref =

RS ·

i*Cj at

j =

A,

B,

C.

In (7), the emulated resistance (RE) of the STATCOM system is adjusted by the duty ratios of the bottom switches in the two-level VSC during each switching cycle to keep the dc bus voltage (VDC) at the constant level.

A similar approach is developed for the higher-level DCMC-based STATCOMs with the level-shifted carrier signals. For the five-level DCMC-based STATCOM, four level-shifted carrier signals (Vcar1-Vcar4) are arranged so that they fully occupy contiguous bands in the range of (−VDC3 − VDC4) to (VDC1 + VDC2). The three-phase sinusoidal control references are then compared with these carrier signals to determine the switched voltage level. The five-level STATCOM is switched to (VDC1 + VDC2) when the control reference is greater than four carrier signals by switching the first upper switch (SA1, SB1, SC1) and its complementary switch (SA’1, SB’1, SC’1). Then the STATCOM is switched to +VDC2 when the control reference is greater than three lower carrier signals (Vcar2, Vcar3, Vcar4) but less than the upper carrier signal (Vcar1) by switching the second upper switch (SA2, SB2, SC2) and its complementary switch (SA’2, SB’2, SC’2). The STATCOM is switched to zero (N) when the control reference is greater than two lower carrier signals (Vcar3, Vcar4) but less than two upper carrier signals (Vcar1, Vcar2) by switching the third upper switch (SA3, SB3, SC3) and its complementary switch (SA’3, SB’3, SC’3). Similarly, the STATCOM is switched to −VDC3 when the control reference is greater than the lower carrier signal (Vcar4) but less than three upper carrier signals (Vcar1, Vcar2, Vcar3) by switching the fourth upper switch (SA4, SB4, SC4) and its complementary switch (SA’4, SB’4, SC’4). Finally, the STATCOM is switched to (−VDC3 − VDC4) when the control reference is less than four carrier signals.

Based on the above five-level carrier-based modulation, the control key equation of the three-phase five-level STATCOM can be represented by the following equations:

where

Vm1-

Vm4 are the carrier amplitudes of four level-shifted carrier signals, depending on each dc-link capacitor voltage (

VDC1-

VDC4),

RS is the sensing resistance of the grid phase current and

iGA,

iGB,

iGC are the grid phase currents, and

VICjref =

RS ·

i*Cj at

j =

A,

B,

C.

For the three-phase five-level DCMC-based STATCOM, the OCC control equation can be expressed as follows:

where

j = 1,2,3,4 and

Vmj =

VDCj RS/

RE, and

dSA’j,

dSB’j,

dSC’j are the duty ratios of the bottom switches in the three-phase five-level DCMC-based STATCOM.

Figure 2 shows the proposed level-shifted OCC control of the five-level DCMC-based STATCOM, based on (9). The three sinusoidal control references are compared with four level-shifted carrier signals (

Vcar1-

Vcar4) to determine the output voltage levels for each phase: (

VDC1 +

VDC2), +

VDC2, 0, −

VDC3, (−

VDC3 −

VDC4). The eight main switches per phase are controlled as complementary pairs (

SA1,

SA’1, etc.). As shown in

Figure 2, the first upper carrier signal

Vcar1 has

Vm1 amplitude and determines the switching status of the first upper switch (

SA1,

SB1,

SC1) and its complementary switch (

SA’1,

SB’1,

SC’1). Similarly, the second upper carrier signal

Vcar2 has

Vm2 amplitude and decides the switching status of the second upper switch (

SA2,

SB2,

SC2) and its complementary switch (

SA’2,

SB’2,

SC’2). For the other two carrier signals (

Vcar3,

Vcar4), the same control approach is applied to determine the switching condition of the related main switches.

For the sinusoidal control reference of Phase-A, the line period is divided into four operation regions, according to where the control reference signal lands, named as I, II, III, and IV.

Table 1 shows the five-level STATCOM output voltages (

VAN) and their switching states of Phase A. In region I in

Figure 2, the STATCOM output voltage is switched between

VDC1 +

VDC2 and

VDC2 by the first upper switch

SA1 and its complementary switch

SA’1. In addition, the other upper switches (

SA2-

SA4) are kept on in region I. Similarly, in region II, the second upper switch

SA2 and its complementary switch

SA’2 are switched to provide the STATCOM output voltage between

VDC2 and 0. In this region, the first upper switch

SA1 is turned off, and the other two upper switches (

SA3,

SA4) are always turned on to provide the neutral point connection (0 or N) in

Figure 1. For region III and IV, the same switching approach is applied to produce the negative STATCOM output voltages. From

Section 2, the control key equations of the five-level DCMC-based STATCOM for four operation regions of Phase A can be derived in

Table 2.

3. OCC Controller for DCMC-Based STATCOMs

The proposed OCC controller for the five-level DCMC-based STATCOM is shown in

Figure 3. The four-carrier level-shifted OCC controller is realized using a clock signal (CLK), four integrators, four comparators, four RS flip-flops, and four reset switches for PWM generation. The four-channel voltage compensators and the level-shifted carrier generators produce four carrier ramps and four level-shifted carrier signals. In detail, the four identical voltage compensators (

GDC1-

GDC4) determine four carrier amplitudes (

Vm1-

Vm4) depending on deviation of each dc-link capacitor voltage (

VDC1-

VDC4) from the reference voltage

V*DC (=

VDC/4). To compensate the dc-link capacitor voltage variations, the equivalent STATCOM resistance (

RE) is adjusted by each carrier amplitude (

Vm1-

Vm4) in (9).

The transfer function of the four identical voltage compensators

GDCi(

s) can be obtained as follows [

26]:

where

Kmi is the proportional coefficient,

ωzmi is the zero far below the zero crossover frequency, and

ωpmi is the pole located right at the zero crossover frequency.

Using the four integrators with reset and three adders, the four level-shifted carrier signals (

Vcar1-

Vcar4) are generated with the different amplitudes and dc-level shifts. The proposed level-shifted carrier signals can be respectively represented as follows:

where 0 <

t ≤

TS,

TS is the period of the carrier signals, and

Vm1-

Vm4 are the amplitudes of the four carrier signals.

The maximum amplitude of the four carrier signals can be decided by the supply voltage or the maximum differential input voltage of the comparators. Since the maximum input voltage of the (−) input terminal (

Vcar1) of the first upper comparator in

Figure 3 is (

Vm1 +

Vm2), one-quarter of the supply voltage can be selected for the maximum amplitude of the four carrier signals. For example, if the supply voltage of the comparators is ±15 V~±18 V, the maximum amplitude of the four carrier signals is 3.75 V~4.5 V. The minimum amplitude of the four carrier signals can be the minimum output voltage of the op-amps in the OCC controller or zero. When the amplitude of the carrier signal reaches its minimum value, the voltage control of the related dc-link capacitor by the carrier signal is somewhat limited during minimum value operation cycles but the total dc-link capacitor voltage balancing would be continuously handled by the other carrier signals and dc-link capacitors.

The resulting level-shifted carrier signals (

Vcar1-

Vcar4) with variable amplitudes and dc-level shifts are shown in

Figure 2. When the four dc-link capacitor voltages (

VDC1-

VDC4) are out of balance due to any reason or there are dynamic load changes, the four-channel voltage compensators continuously adjust the amplitudes of the four carrier signals (

Vm1-

Vm4) to stabilize each dc-link capacitor voltage based on the reference voltage (

VDC/4). In addition, OCC double-edge modulation can be also used in the proposed OCC controller for the DCMC-based STATCOM to provide high-quality output voltage with reduced harmonics.

With the proposed variable amplitude control of the carrier signals, each dc-link capacitor voltage can be properly balanced and equal to the reference voltage even under different dc-link capacitances (C1-C4). The actual duty ratios of the main switches for the phase-A leg (SA1-SA’4) are achieved by comparing the control reference (RS·iGA + VICAref) with the four level-shifted carrier signals in the level-shifted PWM block. When the amplitude of the carrier signals reaches its maximum value, the voltage control capability of the related dc-link capacitors is limited, including overmodulation condition.

The control system of the five-level DCMC-based STATCOM is shown in

Figure 4. The proposed level-shifted OCC controller produces the control references for the current control loop and generates the gate signals for the five-level STATCOM. In addition, the voltage control loop generates the STATCOM current references for the reactive compensation which is implemented with proportional and integral (PI) control algorithm. For voltage regulation in the power system, the reactive power compensation is realized by controlling the injected or absorbed reactive current of the five-level STATCOM.

Assuming that there is a voltage sag (+ΔVpccA) in Phase A, the five-level STATCOM tries to regulate the grid voltage and make it come back to normal. From the multilevel OCC control Equation (9) of the five-level STATCOM, the following control equations can be derived to compensate the voltage sag and regulate the grid voltage within the standard.

In region I of

Figure 2, since the STATCOM output voltage is only switched between

VDC1 +

VDC2 and

VDC2 by the first upper switch

SA1 and the other upper switches (

SA2-

SA4) are kept on from

Table 1, the voltage regulation is only controlled by the first upper switch

SA1 in region I as follows:

From above, the duty ratios of the first upper switch

SA1 (

dSA1) and its complementary switch

SA’1 (

dSA’1) can be derived as follows:

From (17), it is clear that the duty ratio of the first upper switch SA1 (dSA1) increases by the voltage sag (+ΔVpccA) in Phase A and the STATCOM output voltage (VAN) can be increased by the duty ratio (dSA1) to inject the reactive power into the power grid for the voltage regulation.

In region II, since the second upper switch

SA2 and its complementary switch

SA’2 are only switched to provide the STATCOM output voltage between

VDC2 and 0 as shown in

Table 1, the voltage regulation is achieved by the second upper switch

SA2 in region II as follows:

Similarly, the duty ratios of the second upper switch

SA2 (

dSA2) and its complementary switch

SA’2 (

dSA’2) can be expressed as follows:

From (20), it is also clear that the duty ratio of the second upper switch SA2 (dSA2) increases by the voltage sag (+ΔVpccA) in Phase A and the STATCOM output voltage (VAN) can be also increased by the duty ratio (dSA2) to inject the reactive power for the voltage regulation in region II.

In addition, the voltage regulation of the proposed STATCOM in region II can be also explained by

Table 2. In region II, the control key equation of the STATCOM is given by:

From above, the duty ratio of the second upper switch

SA2 (

dSA2) can be expressed as follows:

From (22), when there is the voltage sag (+ΔVpccA) in Phase A, the STATCOM output voltage (VAN) can be increased by the duty ratio (dSA2) to inject the reactive power into the power grid for the voltage regulation in region II.

For the diode-clamped multilevel converters, a major challenge is to keep all dc-link capacitor voltages balanced, which was achieved with an extra voltage-balancing circuitry or a specific voltage-balancing control previously. For example, a modified SPWM method was proposed in [

17] in order to balance the two dc-link capacitor voltages for the three-level diode-clamped inverters. It is based on changing the boundary offset on the middle point of two carrier signals, which can control the neutral-point current to ensure balanced dc-link capacitor voltages. However, the main drawback in this approach is the restricted stability in order to obtain a simple control strategy.

Figure 5 shows the proposed four-carrier level-shifted OCC control algorithm of the proposed five-level STATCOM to maintain the dc-link capacitor voltage balance in region I and II.

For the detailed analysis of the dc-link capacitor voltage balance, the two dc-link capacitor currents (

iC1,

iC2) in region I can be described by the following expressions:

Similarly, the two dc-link capacitor currents in region II can be expressed as:

Assuming that the four dc-link capacitors (

C1-

C4) have the same capacitance, when a disturbance causes imbalance in the two upper dc-link capacitor voltages (

VDC1 >

V*DC >

VDC2), a state variable ∆

V is defined as half the difference between the two upper dc-link capacitor voltages (

VDC1,

VDC2), which should converge to zero with the proposed OCC control. In the unbalanced condition, each dc-link capacitor voltage can be defined as a function of the voltage difference ∆

V by:

where

In order to maintain the dc-link capacitor voltage balance, the proposed control of the five-level STATCOM in region I and II is shown in

Figure 5. From

Figure 5a, the duty ratios of the

SA1 switch under an unbalanced dc-link condition can be described as follows:

where

dSA1(n) and

dSA1(n+1) are the duty ratios of the

SA1 switch at the (

n)

th and (

n + 1)

th switching cycles, and

From (27) and (28), the duty ratio variation of the

SA1 switch (∆

dSA1) to compensate the unbalanced dc-link capacitor voltages can be obtained by:

Assuming

VDC1(n) >> ∆

VDC1(n), the above equation can be simplified as:

From (23) and (30), it is possible to define the relationship between the duty ratio variation of the

Vcr1 carrier signal and the compensation for the dc-link capacitor voltage unbalance. The voltage variations of the two upper dc-link capacitors (

C1,

C2) in region I are given by:

When VDC1 > V*DC > VDC2, ∆dSA1 is negative and ∆IDIS1 is positive in region I. Therefore, the over-charged C1 capacitor voltage (VDC1) will decrease and the under-charged or over-discharged C2 capacitor voltage (VDC2) will increase to reduce the dc-link capacitor voltage deviation, depending on the difference between ∆IDIS1 and ∆IDIS2. In this unbalanced condition, ∆VDC1 is decreasing during each switching cycle to reach the nominal dc-link capacitor voltage.

Since ∆

VDC1(n) − ∆

VDC1(n+1) = (1 −

A1)·∆

VDC1(n) −

A2·∆

VDC2(n) −

AC1 −

AC2 > 0, the following compensation control is obtained:

In this unbalanced condition, ∆

VDC1 is decreasing during each switching cycle to reach the nominal dc-link capacitor voltage. From

Figure 5b, similarly, the duty ratios of the

SA2 switch under an unbalanced dc-link condition can be described as follows:

where

dSA2(n) and

dSA2(n+1) are the duty ratios of the

SA2 switch at the (

n)

th and (

n + 1)

th switching cycles, and

From (33) and (34), the duty ratio variation of the

SA2 switch (∆

dSA2) to adjust the unbalanced dc-link capacitor voltages can be obtained by:

Assuming

VDC2(n) >> ∆

VDC2(n), the duty ratio variation of the

SA2 switch can be simplified as:

From (24) and (36), the voltage variations of the two upper dc-link capacitors (

C1,

C2) in region II are given by:

When VDC1 > V*DC > VDC2, ∆dSA2 is positive and ∆IDIS1 is also positive in region II, the over-charged C1 capacitor voltage (VDC1) will decrease and the under-charged C2 capacitor voltage (VDC2) will increase to eliminate the dc-link capacitor voltage deviation.

Finally, the voltage variations of the four dc-link capacitors (

C1-

C4) can be described as follows:

Using (38), the voltage variation vector Δ

VDC(n) can be written by a 4 × 4 matrix

A and the initial voltage variation vector Δ

VDC(0):

where

From (38)–(40), it is clear that the voltage variations of the four dc-link capacitors become zero in steady state, even though there are some voltage variations of the dc-link capacitors in the beginning or induced by some perturbation. Based on the proposed four-carrier level-shifted OCC control, dc-link capacitor voltage balance can be successfully achieved. It is also clear that the stabilizing time required to eliminate the dc-link voltage unbalance is proportional to the dc-link capacitance and inversely proportional to the amplitude of the input current. However, the proposed multilevel OCC controller may have limited control capability of the dc-link voltage balance during AC network failures since the low AC voltage over a long period prevents the proposed multilevel OCC controller from switching the first upper switches in region I to control the upper dc-link capacitor (C1) voltage. During the low AC voltage condition, the proposed multi-carrier level-shifted OCC control loses its controllability of the dc-link voltage balance.

For region III and IV, the same control approach is applied to regulate the grid voltage from the voltage variation at the PCC, for example, the voltage sag (or swell). Finally, it is concluded that the voltage variation (sag or swell) can be automatically compensated by the proposed five-level STATCOM with the multilevel OCC controller for all operation regions.