1. Introduction

Battery-based industrial applications (including drones, electrical vehicles, and mobile robots) require high-quality DC power supply systems to ensure improved reliability during operation [

1,

2,

3]. To address these industrial needs, DC/DC power converters are considered to be a reasonable solution. These converters are equipped with devised that provide major advantages, such as power factor correction. Moreover, a carefully designed feedback controller can dramatically improve the closed-loop robustness to variations in the load and operating conditions [

4,

5,

6].

The cascade-type control strategy is typically adopted to ensure high-performance DC/DC power conversion, and the inner and outer loops should regulate the inductor current and output capacitor-side voltage, respectively [

7,

8]. The introduction of a fast current loop provides practical advantages. First, it improves the output voltage control performance by kicking off the unstable zero through the high-current loop cut-off frequency settings. Secondly, it limits the inductor current by using software to regulate the current reference signal obtained from the outer loop controller. To ahieve the two above-mentioned benefits, proportional-integral (PI) controllers were mainly been adopted for each loop. The selected PI gains assign the cut-off frequencies for the current and voltage loops to satisfy the desired closed-loop performance and robustness described in the frequency domain. Typically, the current cut-off frequency is set to be greater than that of the voltage loop, which makes the current loop faster compared with the voltage loop. This closed-loop setting may limit the output voltage control performance based on the current cut-off frequency specification. Increasing the current cut-off frequency to increase the admissible output voltage cut-off frequency can result in the increase of the current ripples or even instability [

7,

9,

10]. To limit the current cut-off frequency, a feed-forward compensation technique was developed with consideration to the converter current dynamics. This technique requires the true converter inductance and capacitance values to vary in accordance with the operating conditions [

11]. The resulting closed-loop accuracy can be greatly improved by adopting additional novel online parameter identifiers (as in [

12,

13]).

There are several novel methods for ensuring the high output voltage control performance while avoiding the increase of the current cut-off frequency: for example, predictive [

14], deadbeat [

15], adaptive [

16], sliding mode [

17], backstepping [

18], and nonlinear robust methods [

19]. These methods achieve true converter parameter dependence level reduction for the feed-forward compensation terms. However, the control actions keep the current cut-off frequency constant, although it must be increased to achieve rapid output voltage dynamics. The recently proposed cascade-type feedback linearization (FL) controller stabilizes the current and voltage at the desired values, and the optimal feedback gains determine the constant current and voltage cut-off frequencies [

20]. The differential inclusion technique based on the discontinuous switching function has been applied to ensure the global tracking property without controlled error integrators and a pulse-wide modulation (PWM) process [

21]. The state-feedback controllers collaborate with the disturbance observer (DOB) used for the feed-forward compensator to stabilize the error dynamics; the feasibility of this method has been experimentally demonstrated [

22,

23]. The recent cascade-type proportional current and voltage controller systematically adopts nonlinear DOBs in the feed-forward loop with a rigorous proof of the offset-free property without control error integral actions [

24]. Moreover, DOB-based energy-shaping controllers solve the parameter and load uncertainty problem by solving a partial differential equation, which ensures the removal of the steady-state error caused by the DOB dynamics. Model predictive control (MPC) has been proposed as a solution to the numerical solver dependence problem, which requires the true converter parameter and load information to ensure closed-loop optimality [

25,

26]. The analytic form self-tuner was incorporated into a DOB-based proportional-type outer loop controller to achieve a dynamic cut-off frequency [

27]. For this technique, the constant inner loop cut-off frequency must be sufficiently increased to achieve the desired closed-loop performance. The voltage-derivative observer-based nonlinear PD controller removes the current feedback loop and solves the converter parameter and load dependence problem in the control and observer [

28].

According to the literature review, the constant current-loop cut-off frequency assigned by the feedback gain must increase proportionally to the output voltage loop cut-off frequency to improve the transient dynamic performance, which is desirable only for the transient operations and can increase current ripple level and limit the closed-loop relative stability. The so-called “constant current cut-off frequency problem” corresponds to the main challenge faced by this study. This paper proposes a solution to this problem based on the following contributions:

An online auto-tuner for the current cut-off frequency to be dynamically updated according to the transient and steady state operation mode;

A DOB-based pole-zero cancellation current controller driven by the dynamic current cut-off frequency from the online auto-tuner;

An active damping outer loop speed controller leading to a first-order closed-loop system with time-varying disturbance suppression capability by the active damping coefficient.

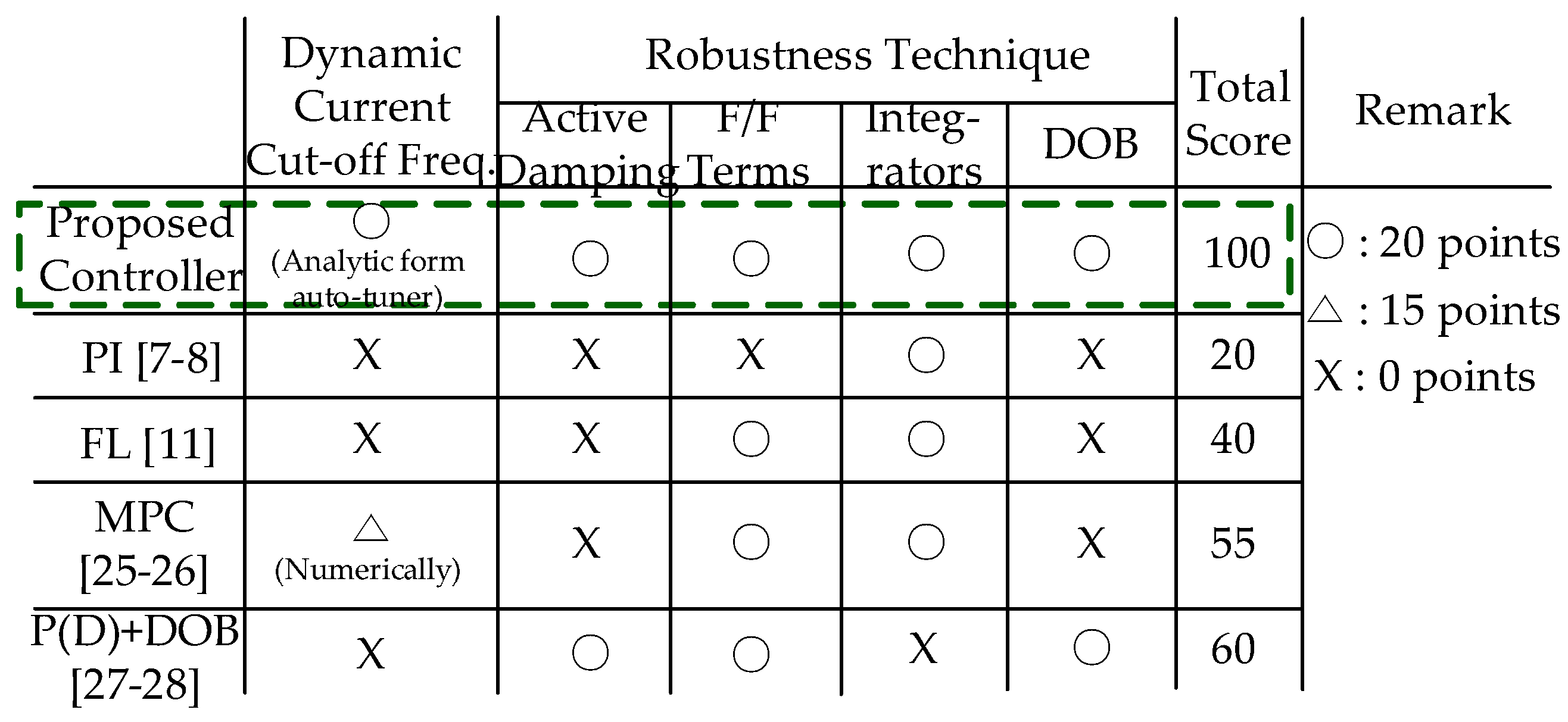

Convergence analysis is also carried out to highlight the contributions by investigating the closed-loop dynamics. A 3-kW DC/DC buck converter is used in the experiments to demonstrate that the proposed solution addresses the constant current cut-off frequency problem based on the dynamic current cut-off frequency from the online auto-tuner. The qualitative comparison results obtained by the above-mentioned studies are summarized in the table in

Figure 1.

2. DC/DC Buck Converter Model

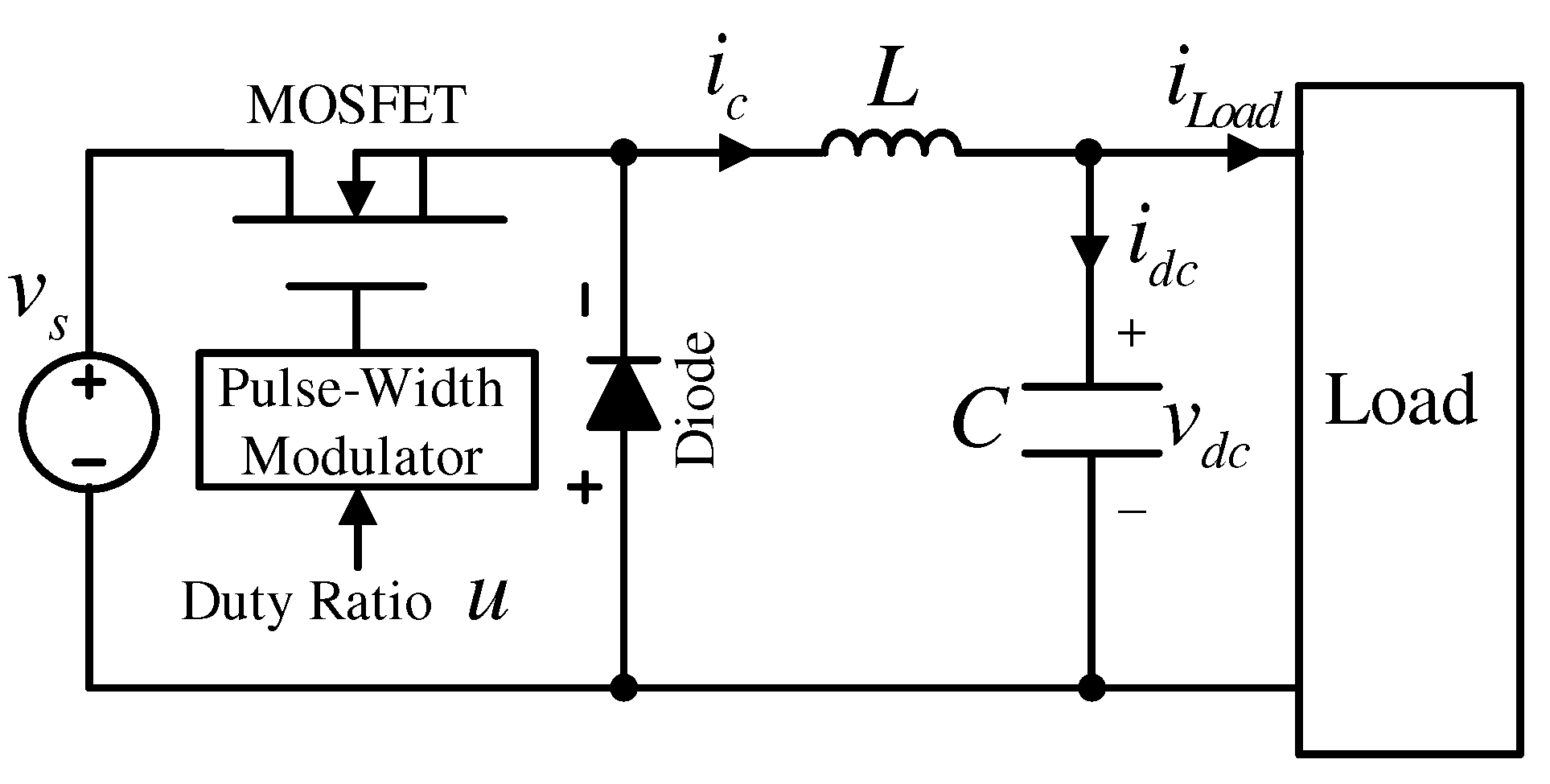

This study considers the standard DC/DC buck converter depicted in

Figure 2, where the inductor current

(in A) and output voltage

(in V) are the state variables excited by the duty ratio

(control input) applied to the switching device (MOSFET). The input source voltage and load current are represented as

(in V) and

(in A), respectively. The application of the averaging technique to the circuit dynamics obtained from each switching state (ON and OFF) yields the second-order differential equations:

with

L and

C denoting the inductance and capacitance values, respectively.

The operation mode uncertainty validates the assumption stating that the true values of

L and

C and the load current

are unknown. Moreover, to reduce the number of sensors, the uncertainty of the input source voltage

is also considered, except for its initial value

. Thus, the introduction of the nominal values

and

results in another version of the original converter dynamics (

1) and (

2):

with the lumped disturbances

and

to be treated as unknown time-varying signals, which are used to design the control law in the following sections. Notably, the equivalent series resistance (ESR) of the inductor and capacitor are also included in the perturbed disturbances

and

.

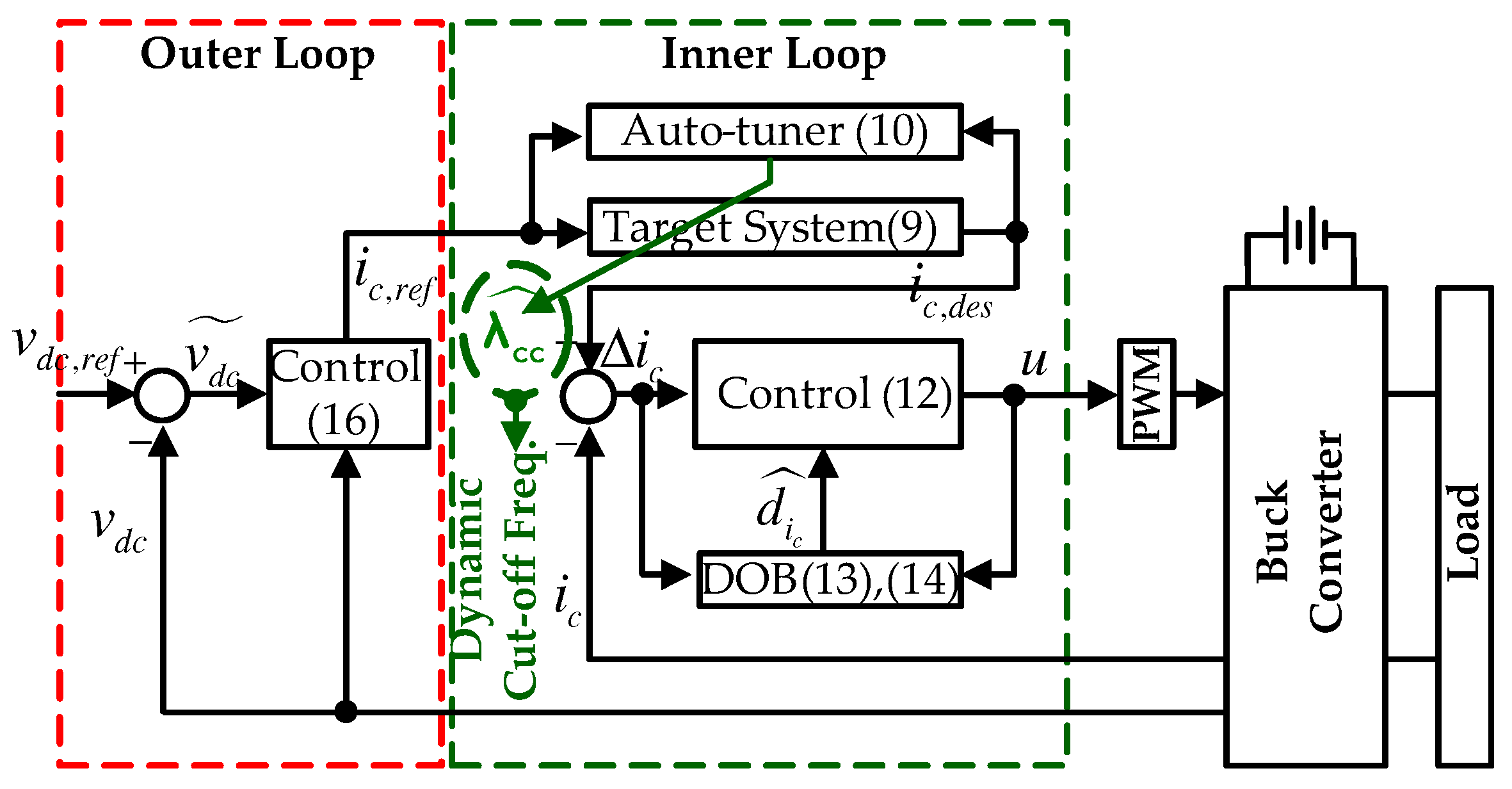

3. Proposed Control Algorithm

This section presents the cascade-type solution proposed for actual implementations as clearly as possible. The main results discussed in this section are presented in

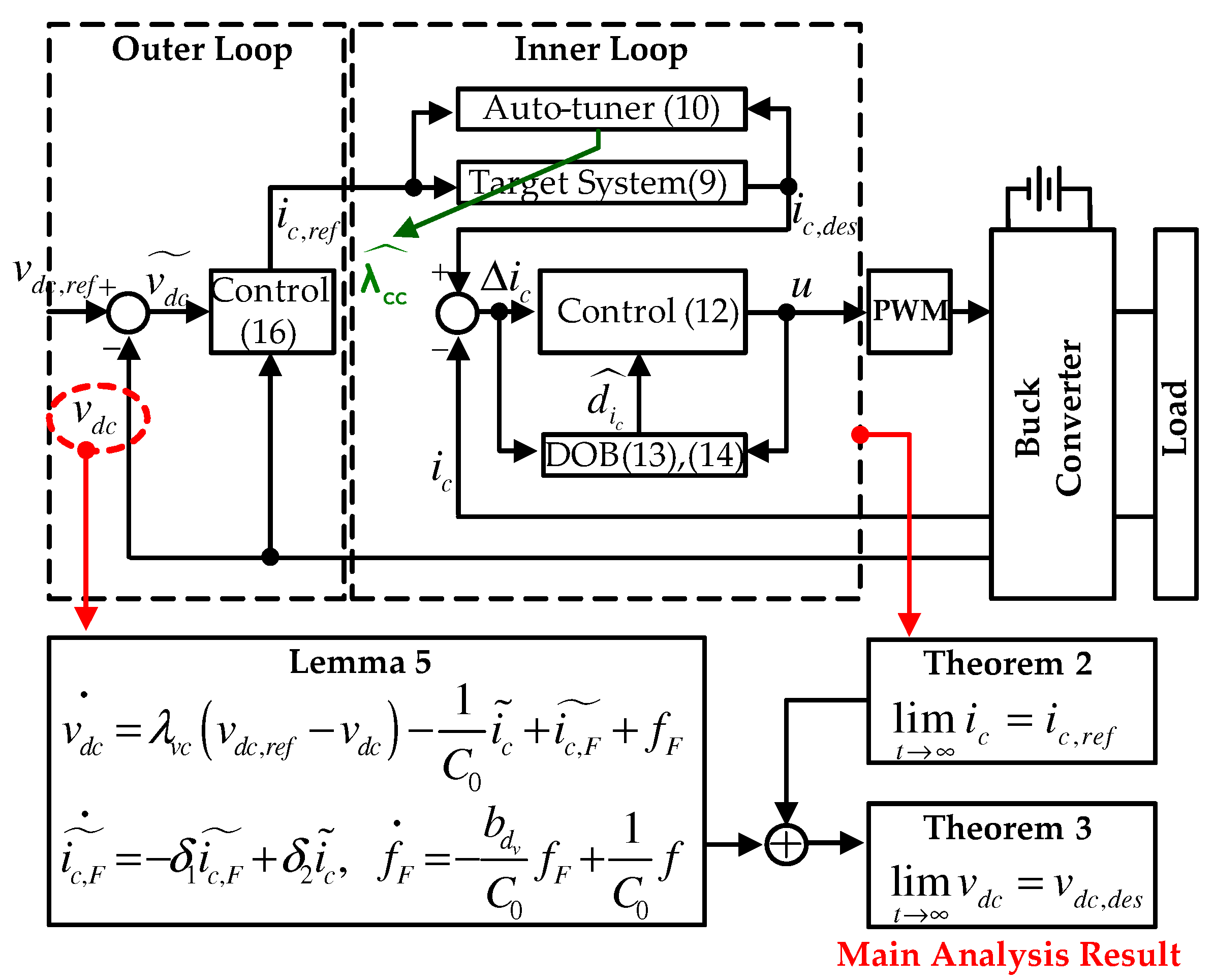

Figure 3.

Section 3.1 and

Section 3.2 give the corresponding detailed subsystem descriptions. The closed-loop analysis results are included in

Section 4.

Before presenting the control algorithm, it is necessary to clarify the control objective of this study. Consider the desired output voltage trajectory

for a given reference

with the Laplace transformations

and

, and define the target closed-loop transfer function as

with the output voltage cut-off frequency

(

in rad/s, corresponding to

in Hz). Based on the desired system (

5), the control objective is formulated as exponential convergence:

where

denotes the inverse Laplace transform for the target system (

5):

3.1. Inner Loop for Current Control

3.1.1. Current Cut-off Frequency Auto-Tuner

For a given current reference

from the outer loop, define the target current dynamics as

with the current cut-off frequency

(

in rad/s corresponding to

in Hz); its transfer function is identical to (

5) with the replacement

with

. For a rapid output voltage transient response, the current cut-off frequency

must to be proportional to the increase in

.

To boost the current cut-off frequency only during transient periods, a slight modification of the target current dynamics (

8) with a dynamic current cut-off frequency

is suggested as

with the auto-tuning rule for

:

with the errors defined as

and

, gains

and

, and initial condition

.

Remark 1. The nonlinear error term excites the dynamic current cut-off frequency whose boosting level is adjusted by , and the stabilization term exponentially restores the boosted cut-off frequency to its initial value according to the decay rate . The corresponding formal analysis is presented in Section 4. 3.1.2. Control Law

The error

is defined to accomplish the convergence

with

representing the solution to the desired system (

9). Then, it follows from (

3) that

with the re-defined lumped disturbance

. This study proposes the control law for stabilizing the open-loop system (

11) as

, with gains

and

, where the DOB for updating

is given by

with gain

.

This study introduces the structured feedback gain structure in (

12) to improve the inner loop current control accuracy through closed-loop order reduction caused by pole-zero cancellation. Further details are given in

Section 4.

3.2. Outer Loop for Voltage Control

Consider an equivalent form for the output voltage dynamics (

4):

with the error defined as

; its control variable

(current reference) is designed to stabilize the error

:

with gain

. The stabilization action tries to ensure the exponential convergence

by adding artificial damping (

) to the closed-loop. This results in pole-zero cancellation, with the collaboration of the particularly structured feedback gain structure. A detailed analysis of this statement is presented in

Section 4.

4. Closed Loop Analysis

This section begins with the inner loop analysis (

Section 4.2) carried out to analyze the entire closed-loop system (

Section 4.2).

4.1. Inner Loop

Lemmas 1–3 investigate the subsystem dynamics acting on the dynamic cut-off frequency update and disturbance estimation mechanisms in the inner loop.

Lemma 1. The auto-tuner (10) ensures the existence of a minimum dynamic cut-off frequency with an initial value . i.e., Proof. Integration on both side of the auto-tuner (

10) yields

which is bounded from below by

, owing to the positivity of

. □

As mentioned in Remark 1, the stability issue for the dynamic cut-off frequency update mechanism (

9) and (

10) originates from the nonlinear excitation term

in (

10), which is addressed in Lemma 2 with the dynamic cut-off frequency magnification characteristics (

17).

Lemma 2. The target system (9) with the dynamic cut-off frequency driven by (10) ensures the two boundedness properties. For a dynamic cut-off frequency: For the target current trajectory:for some , , where , . Proof. It follows from the errors

and

and relationships (

9) and (

10) that

Thus, the positive definite function

can be written as

with

. This completes the proof based on the comparison principle in [

29]. □

The results of Lemma 2 address the stability issue of the dynamic cut-off frequency update mechanism (

9) and (

10) with the positive definite function

. Considering the inequality (

18), one can roughly conclude that

, because the dynamic cut-off frequency magnification property (

17) leads to

for some gain setting

and

.

The DOB dynamics (

13) do not explicitly describe the disturbance estimation behavior, and their ambiguity can be clarified with additional analysis based on combining their output with the dynamic Equations (

13) and (

14). See Lemma 3 for details.

Lemma 3. The DOB (13) and (14) estimate the lumped disturbance in accordance with the LPF dynamics: Proof. By using the DOB dynamics (

13), the DOB output (

14) yields its dynamical relationship:

where the relationship (

11) confirms the last equation. This completes the proof. □

The resultant dynamics (

19) provide the error dynamics:

with

and

,

, as will be considered in the subsequent analysis.

Before analyzing the controlled current error (), Lemma 4 derives the closed-loop order reduction capability of the structured feedback gain structure, which leads to pole-zero cancellation. The dummy signal (hence ) is introduced in this analysis. See Lemma 4 for details.

Lemma 4. The proposed controller (12) drives the current error to satisfywith the filtered signal for some , . Proof. After substituting (

12) into (

11), the additional derivative on both sides yields

with the Laplace transform:

which shows that (after factorization

)

with

,

. This completes the proof. □

Theorem 1 analyzes the convergence behavior of the controlled current error (

) with a combination of closed-loop error trajectories from systems (

20)–(

22).

Theorem 1. The closed-loop system depicted in Figure 3 ensuresfor some , . Proof. Defining the vector

, it follows from

, (

20)–(

22) that

with

and the positive definite matrix

. This completes the proof based on the comparison principle in [

29]. □

The inner loop control objective accomplishment is confirmed with Theorem 1 by roughly showing the convergence

with the DOB gain setting:

(see the inequality (

23)). However, there is still ambiguity with regard to the actual current error convergence

, which is used to prove the entire closed-loop convergence

. Theorem 2 addresses this issue based on the analysis results of Theorem 1 and Lemmas 1 and 4.

Theorem 2. The closed-loop system depicted in Figure 3 guaranteesfor some , , where , . Proof. The current error

satisfying

gives its dynamics (using (

9) and (

21)):

with

, which makes the composite-type Lyapunov function candidate

become:

; the dynamic cut-off frequency that lowers the boundedness (proven in Lemma 1) and the inequality (

24) are used to obtain the inequality, and

,

. The constant

yields the upper bound of

:

where

. This completes the proof based on the comparison principle in [

29]. □

The boosting nature of the cut-off frequency (

,

) in Lemma 1 provides the rationale for assuming that

by tuning the auto-tuner parameters

and

such that

,

. This is used in subsequent analysis.

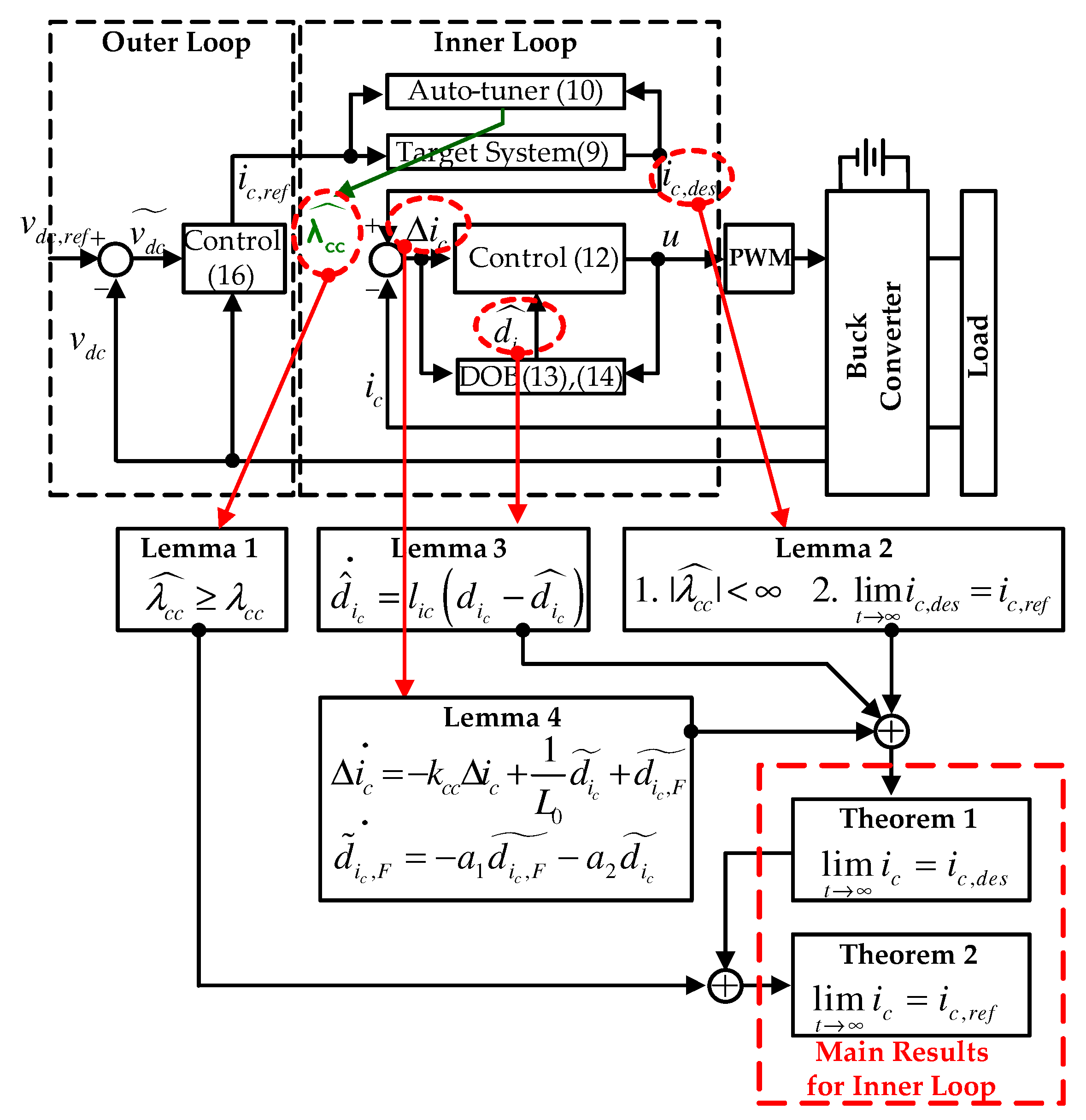

Figure 4 visualizes the reasoning process of the inner loop analysis.

4.2. Entire Loop

Before the convergence analysis of the entire closed-loop (to show that ), Lemma 5 derives the closed-loop order reduction caused by the collaboration between the active damping injection and the structured feedback gain structure, which leads to pole-zero cancellation. See Lemma 5 for details.

Lemma 5. The proposed outer loop controller (16) drives the output voltage to satisfywith the filtered signalsfor some , . Proof. After substituting the outer loop control law (

16) into the output voltage dynamics (

15), the additional derivative operation on both sides gives

, with

denoting the time-varying rate of the AC component of disturbance

, which leads to

. The corresponding Laplace transform results in

its equivalent form can be obtained based on pole-zero cancellation from the factorization

:

with

and

. The application of the inverse Laplace transform to both sides completes the proof. □

Finally, Theorem 3 provides an essential closed-loop property showing the control objective accomplishment. The two results of Lemma 5 and inequality , , (obtained from Theorem 2) play an essential role in proving this theorem.

Theorem 3. The closed-loop system depicted in Figure 3 guarantees thatfor some , , where , . Proof. Defining the error

, it holds that

with the use of (

26) and considering a composite-type Lyapunov function candidate for vector

:

with

; its time derivative is given by (with (

25), (

27), and (

28)):

where

and

,

. The coefficient

leads to

with

. This completes the proof based on the comparison principle in [

29]. □

Theorem 3 roughly concludes that the proposed controller accomplishes the control objective (

6) (

, exponentially, with the solution

to the desired system (

7)) by setting the active damping coefficient

to satisfy

such that

,

. The reasoning process for the inner loop analysis is visualized in

Figure 5.

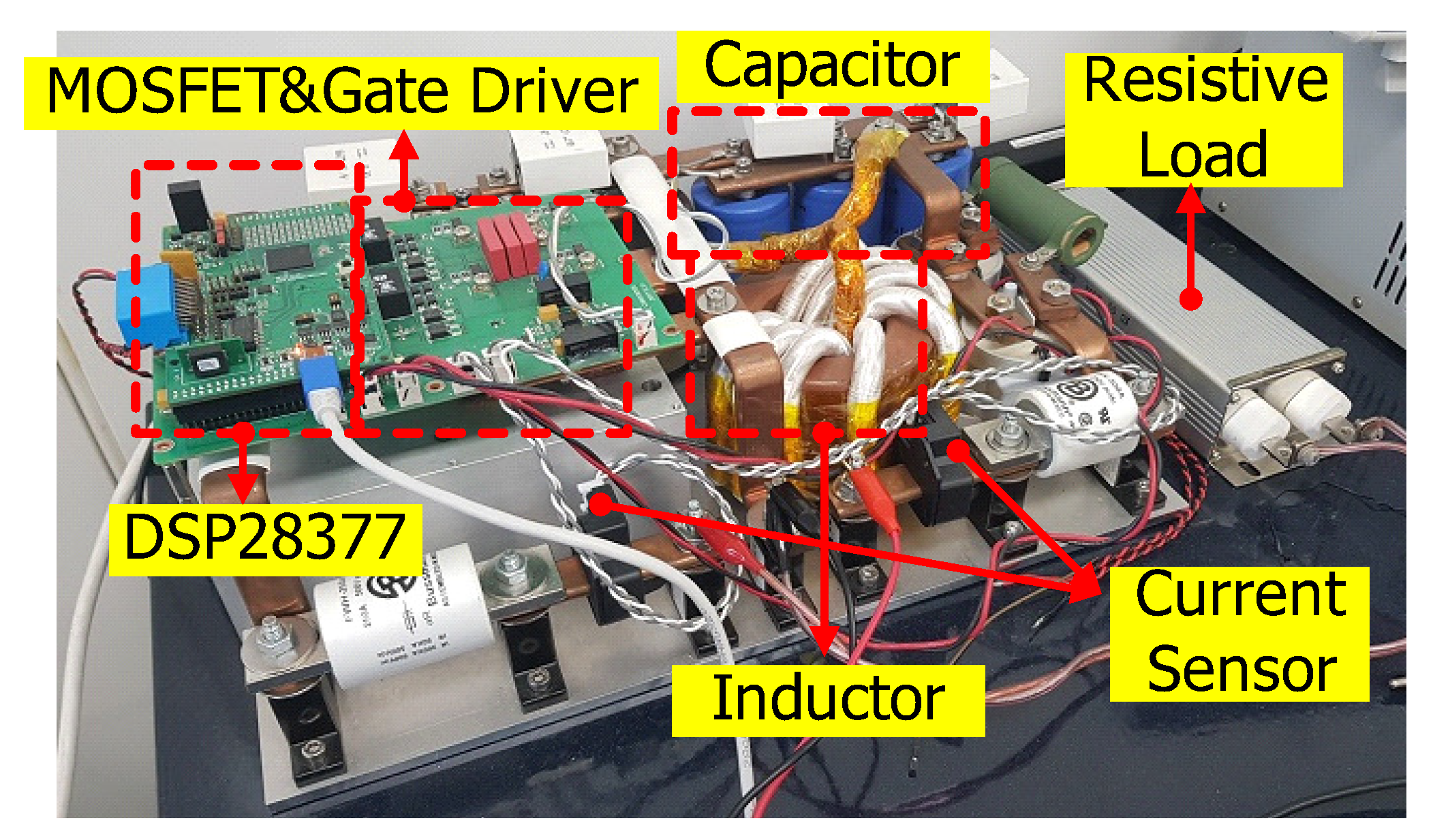

5. Experimental Results

Figure 6 presents the 3-kW bi-directional DC/DC converter testbed used to verify the feasibility of the proposed solution; A Texas Instrument (TI) digital signal processor (TI DSP28377) was used for feedback control at the constant input DC voltage level

V (provided by the DC power supply) with the sampling and PWM periods of

ms. The inductor and output capacitor values were identified

mH and

µF. To consider the model-plant mismatch causing the lumped disturbances, their nominal values

= 0.75

L and

= 1.35

C were used for the implementation of the control law. A resistive load of

was initially connected to the output port to implement the load of the converter.

The inner and outer loops controlled by the proposed controller were tuned as: (inner loop) Hz ( rad/s), , , , , , (outer loop) Hz ( rad/s), and .

A comparative investigation was conducted by replacing the proposed controller with a conventional PI controller reinforced by a DOB and the active damping term: (control) , (DOB) , and . The design parameters are identical to those in the proposed solution.

5.1. Piece-Wise Constant Reference Tracking Mode

The initial output voltage reference

V was increased and decreased to 70 and 30 V in a sequential manner with an initial resistive load

.

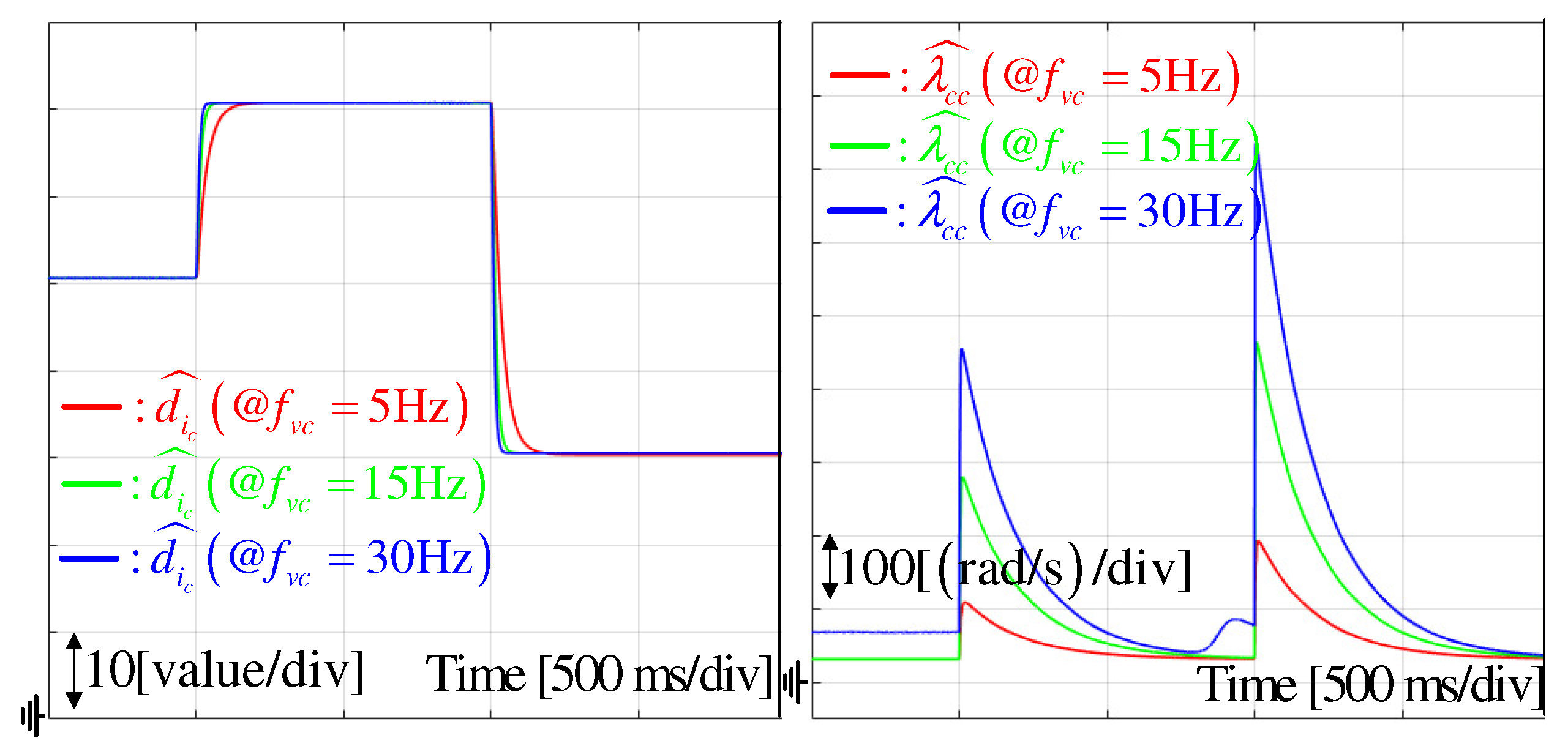

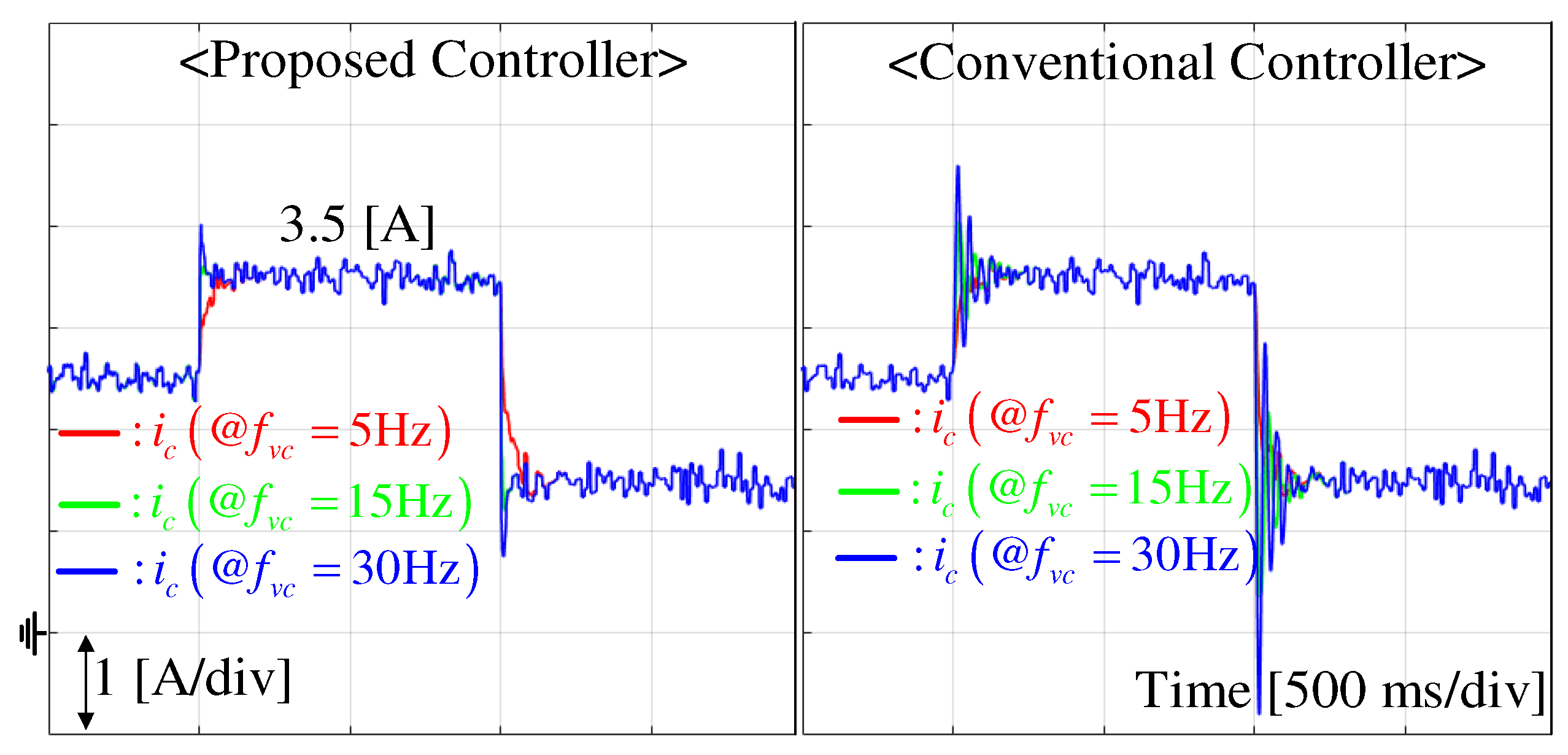

Figure 7 shows the controlled output voltages obtained using the proposed and conventional techniques. Unlike the conventional controller, the proposed controller successfully drives the output voltage to its reference value without any over/undershoots. Moreover, the proposed controller successfully assigns the desired tracking behavior to the resultant feedback system in accordance with the performance (

5) achieved with the increased output voltage cut-off frequencies

, 15, and 30 Hz. The exponential convergence (

6) (proven by Theorem 3) and nature of the current-loop cut-off frequency boosting (resulting in

proven by Theorem 2) provide this advantage without the drawback of performance degradation. Notably, the advantage originates from the dynamic current cut-off frequency (boosting and restoration) presented on the right side of

Figure 8. As expected, the proposed controller removes the unnecessary current oscillation and reduces the current overshoot level, as shown in

Figure 9. The DOB responses are presented on the left side of

Figure 8.

5.2. Constant Reference Regulation Mode

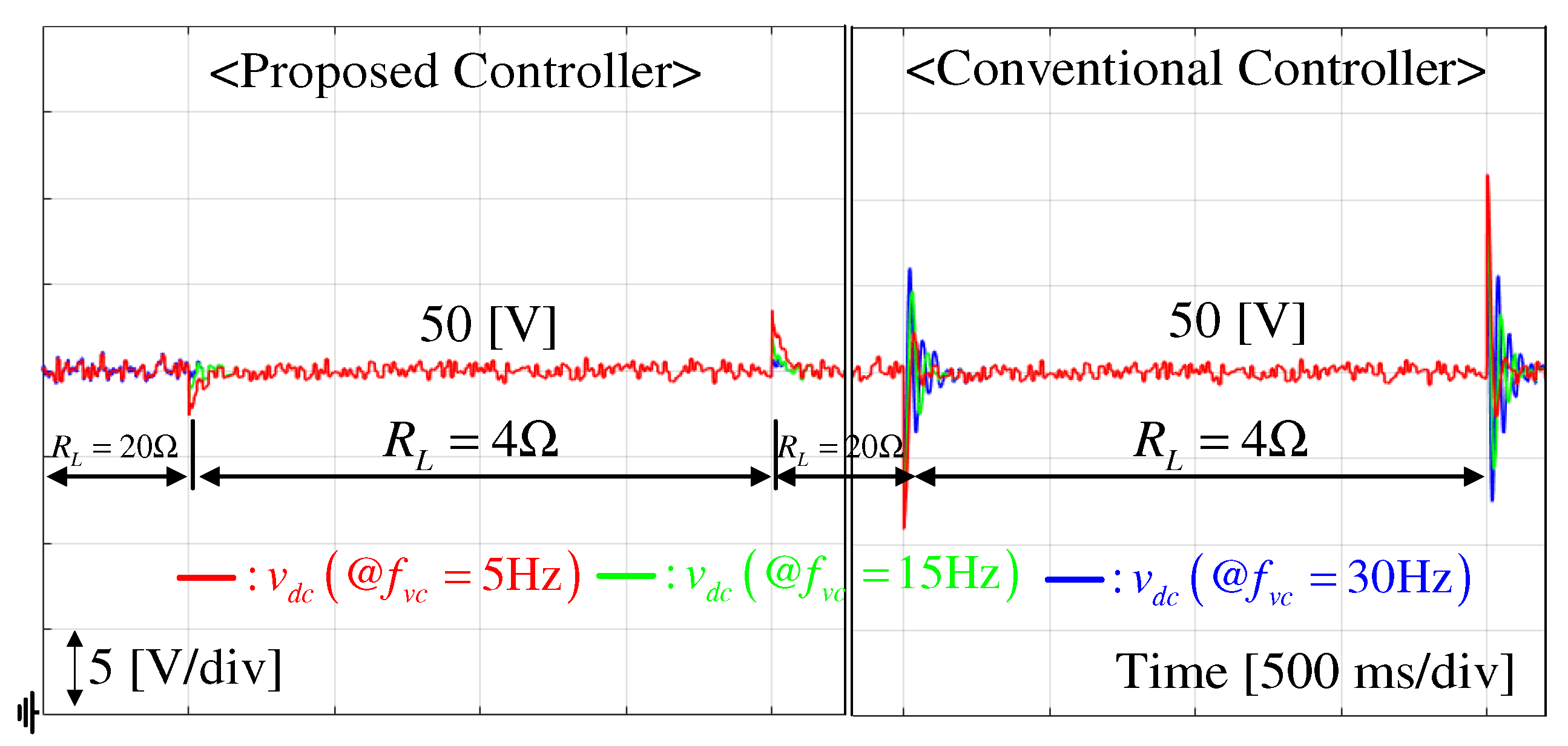

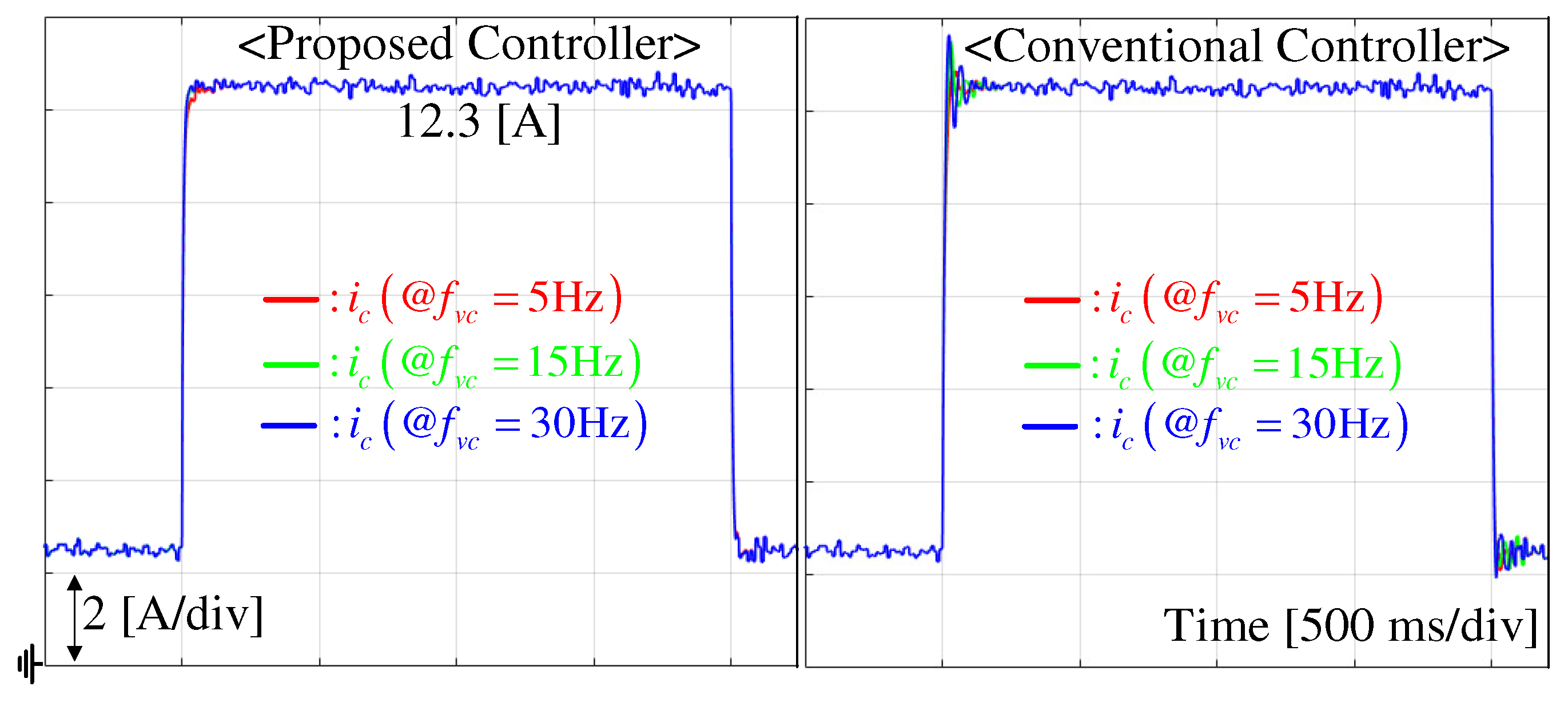

5.2.1. Transient Performance Comparison

This stage demonstrates the constant reference regulation performance at the output voltage level of 50 V with an abrupt variation in the resistive load (decreasing to

and restoring to

). The three output voltage cut-off frequencies

, 15, and 30 Hz were applied to clarify the advantages of the proposed controller. As shown in

Figure 10, the proposed controller can effectively attenuate the over/undershoot level and the performance deviations caused by the variation of the operating conditions. The removal of the current oscillation and overshoot can also be observed in

Figure 11. As intended, the collaboration of two beneficial properties, namely, the cut-off frequency magnification (Lemma 1) and exponential current convergence (Theorem 1), resulted in this beneficial feature.

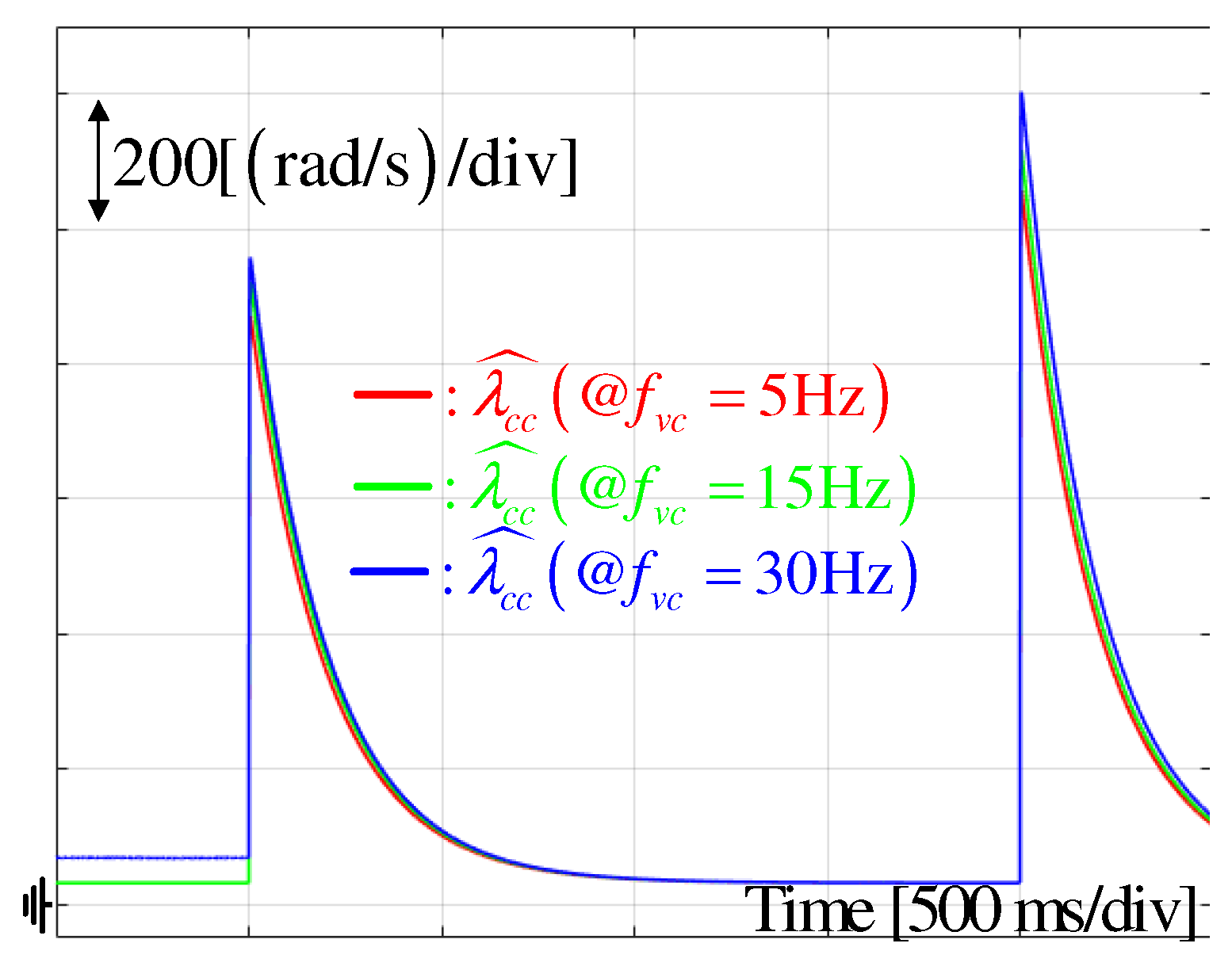

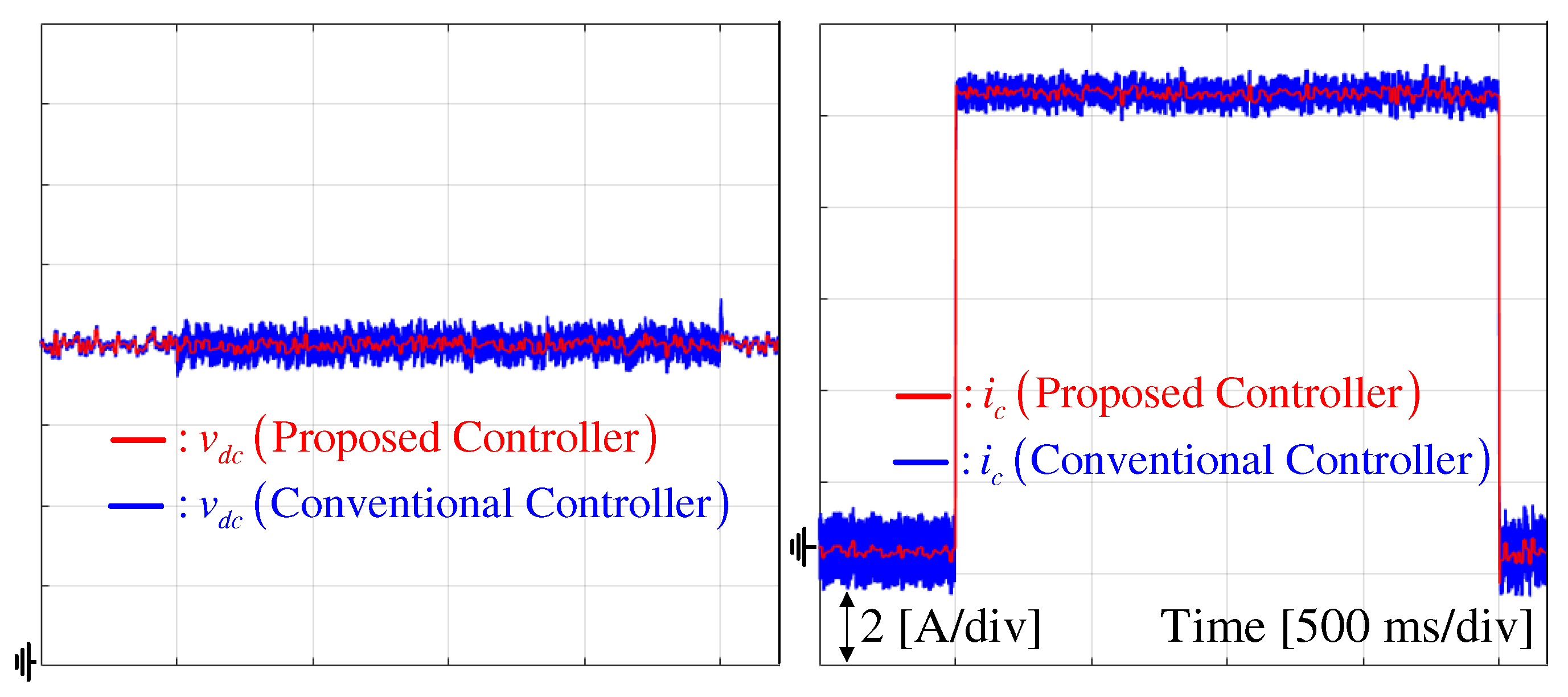

5.2.2. Steady-State Behavior Comparison

This stage shows the current ripple reduction effect from the proposed current cut-off frequency auto-tuner at the same operating mode of the previous subsection, except for the constant cut-off frequency for the conventional DOB-based controller. To secure the improved closed-loop performance, the current cut-off frequency (fixed) for the conventional controller was increased from its initial setting

to 190 Hz that is equal to the peak value of the dynamic current cut-off frequency shown in

Figure 12. As presented in

Figure 13, the increased current cut-off frequency successfully attenuates the over/undershoots but it involves the current ripple magnification in the steady-state operation unlike the proposed controller. The dynamic current cut-off frequency behavior shown in

Figure 12 offers this beneficial current ripple reduction characteristics increasing the power efficiency for a long term operation.

5.3. Discussion

5.3.1. Computational Time

The proposed controller comprising novel subsystems, such as the auto-tuner (

10) and target dynamics (

9), requires additional computational time compared with that of the conventional DOB controller used for the comparison study in this section. To confirm this, the execution time for these two controllers was determined for 3000 randomly generated 3000 reference signals using the DSP28377, based on the pulse length for the whole control algorithm code. The proposed and conventional DOB controllers elapsed

and 30.75 µs, respectively, on an average. This implies that only additional

of computational time is required for the proposed controller compared with that of the conventional DOB controller. On the basis of these comparisons for the performance and computational complexity, the proposed controller can be considered as an alternative to previous solutions without the need for additional hardware (compared with the full-state feedback results) under the use of 32-bit DSPs.

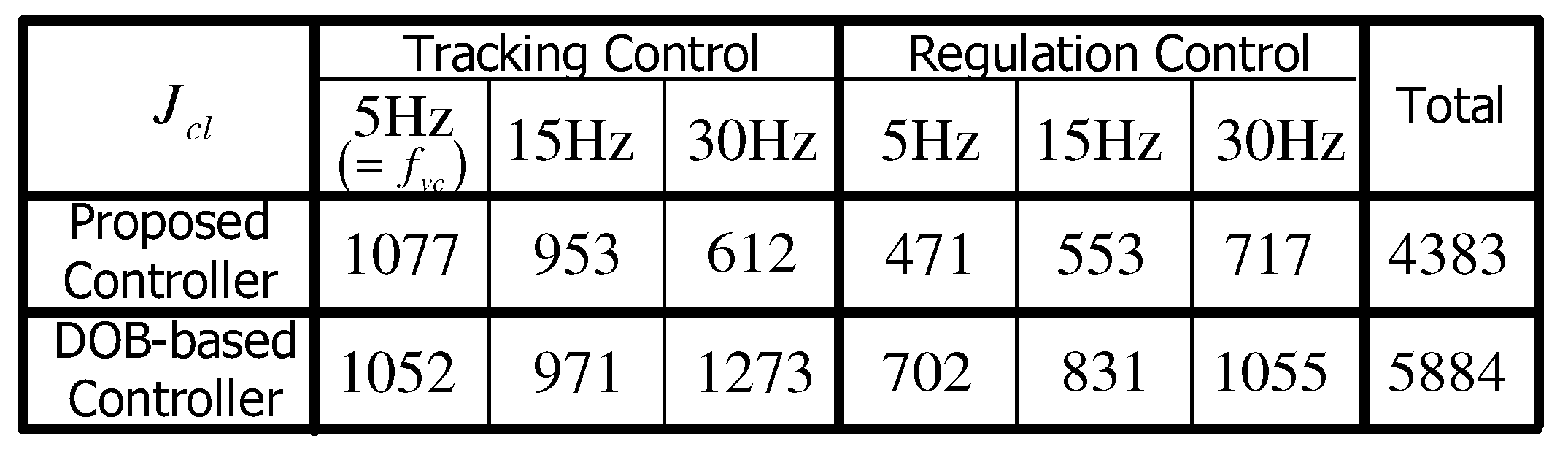

5.3.2. Quantitative Comparison

Section 5.1 and

Section 5.2 present the qualitative differences between the closed-loop responses. To clarify the performance improvement, the metric function is adopted regarding the output voltage error integration during the operation time (for both the tracking and regulation modes), which is given by

. The table in

Figure 14 presents the comparison result with the proposed technique achieving a

performance enhancement owing to its improved controller structure and novel inner loop subsystems (leading to the beneficial closed-loop properties in

Section 4).