A New SVPWM Strategy for Three-Phase Isolated Converter with Current Ripple Reduction

Abstract

:1. Introduction

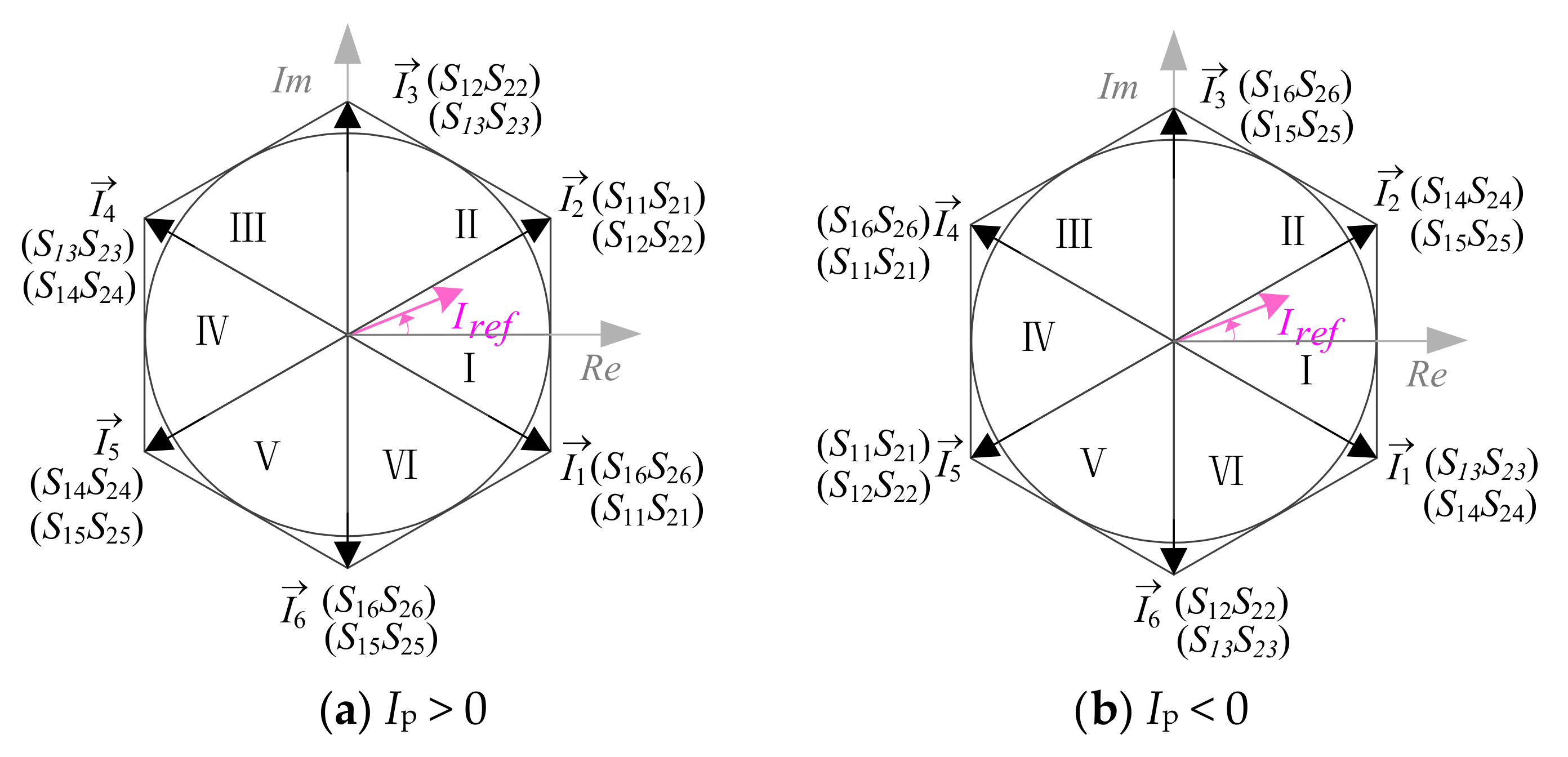

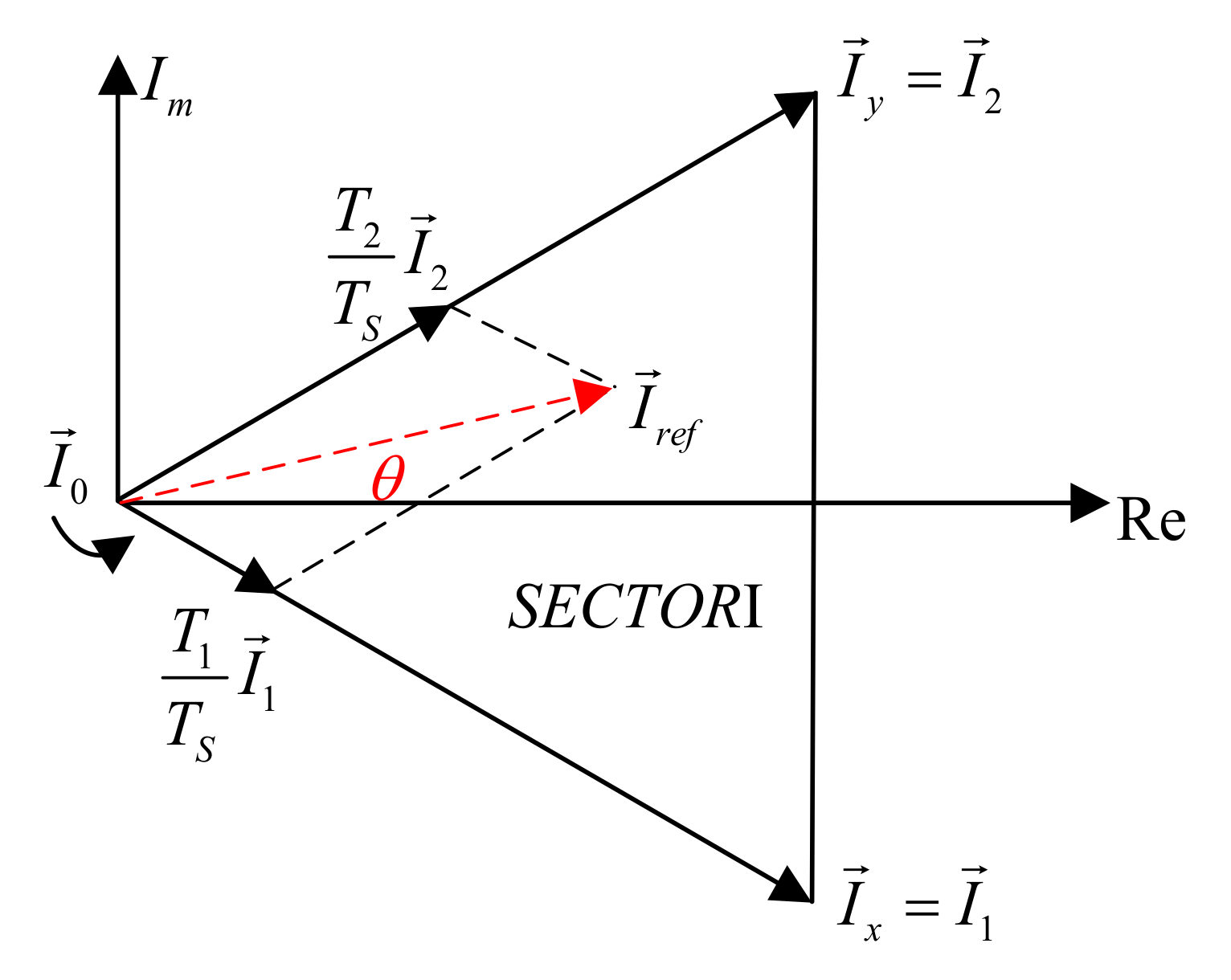

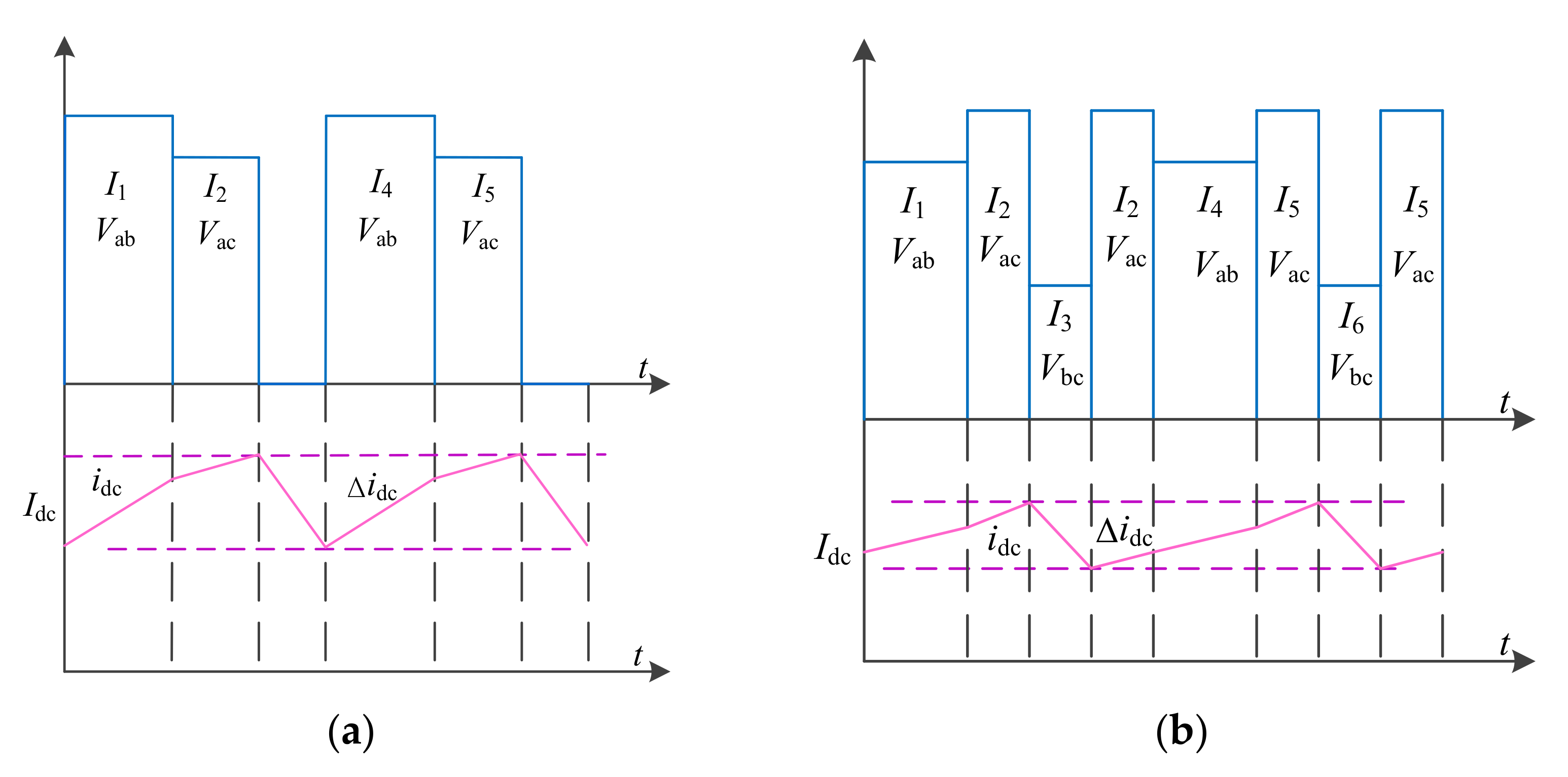

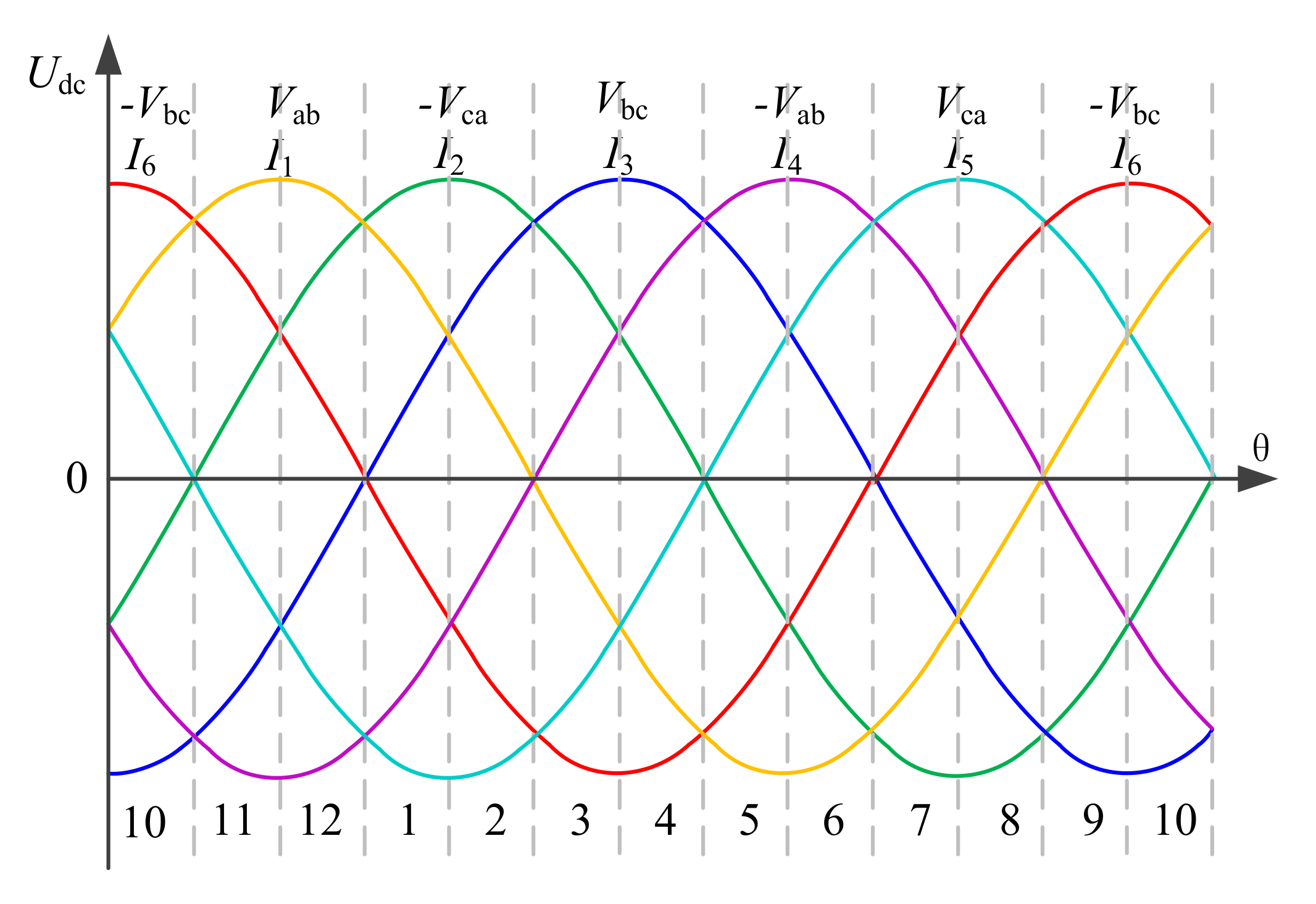

2. DC-Link Current Ripple Analysis

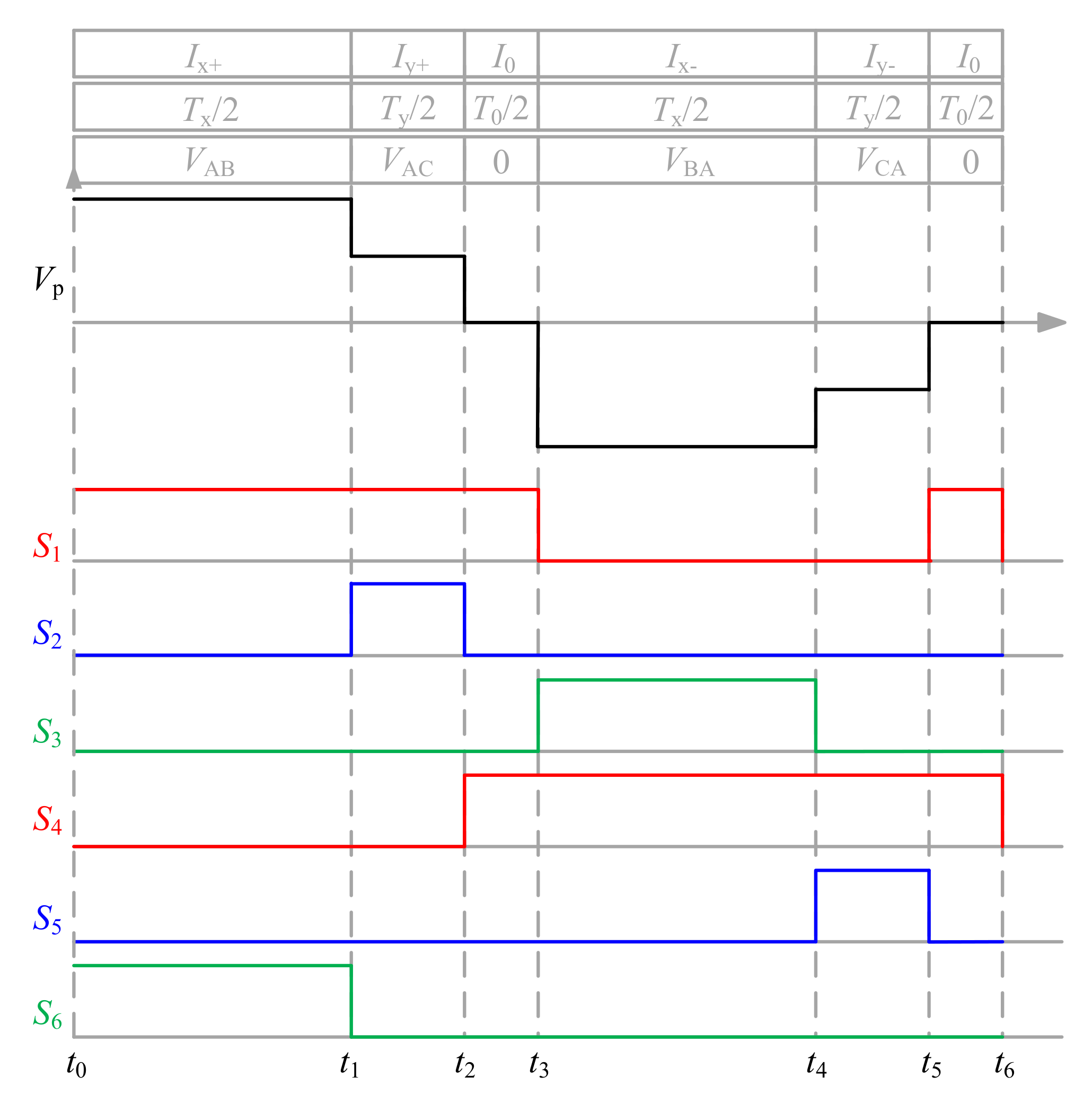

2.1. System Configuration and Working Principle

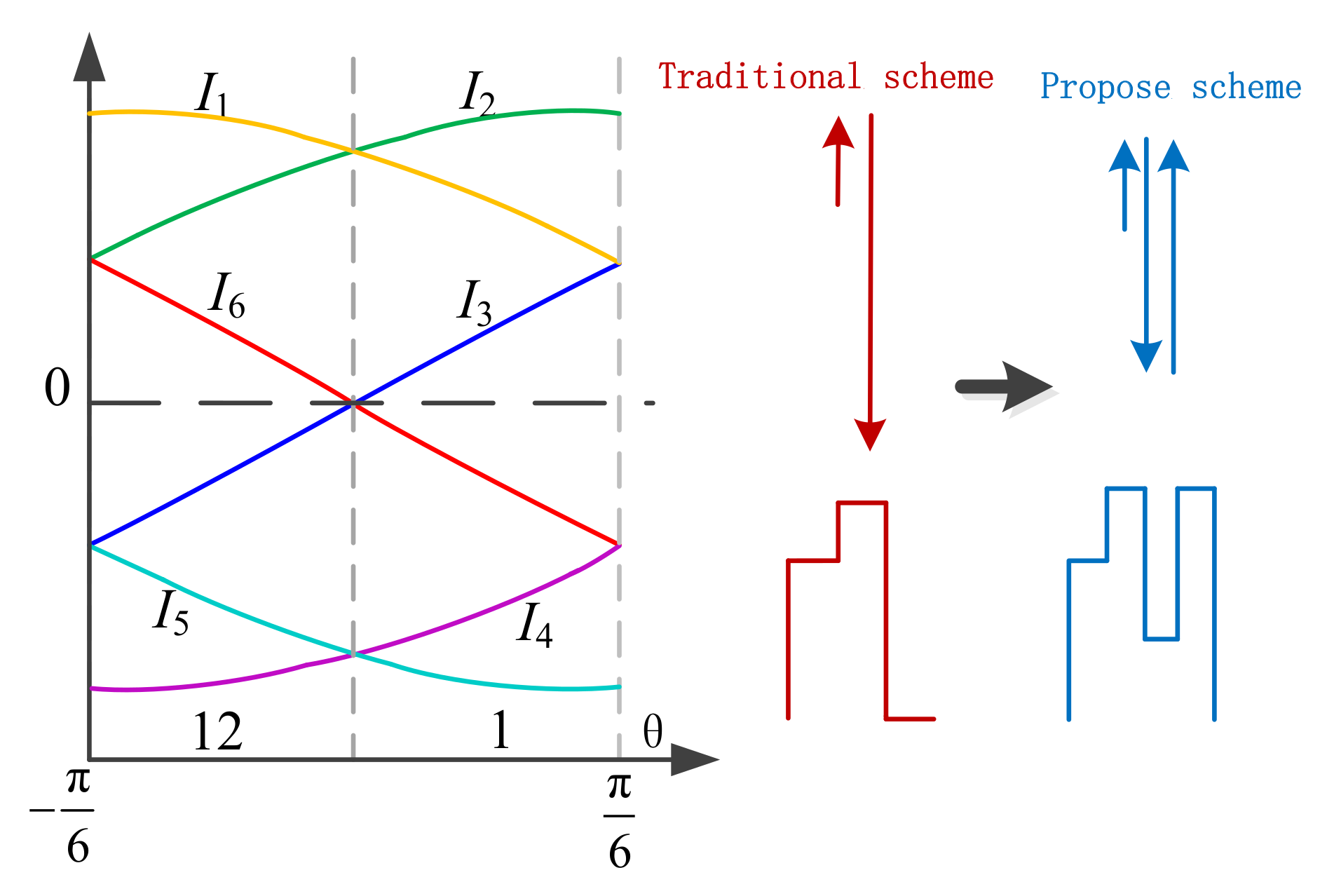

2.2. DC-Link Current Ripple Analysis of Traditional Scheme

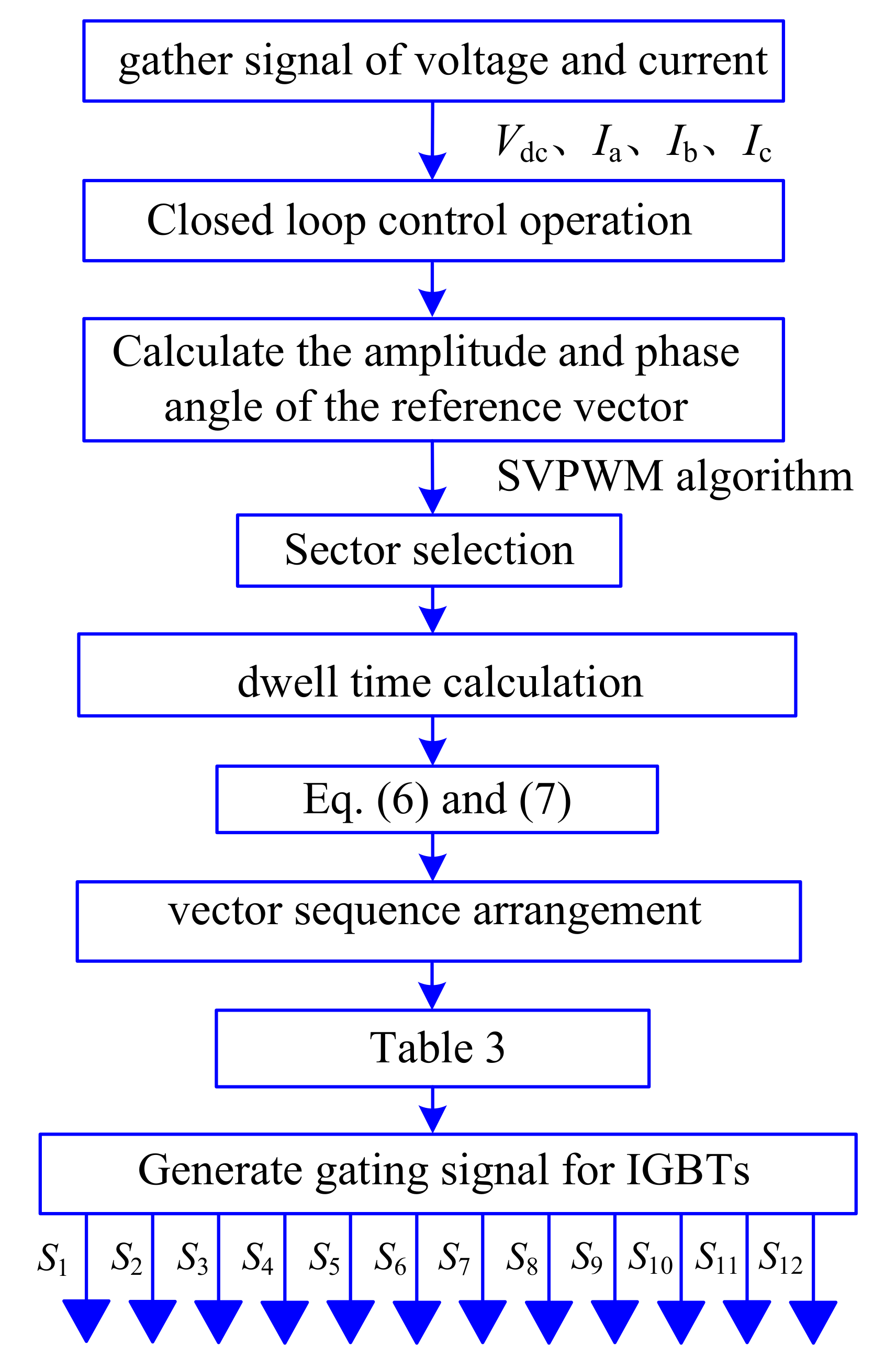

3. Proposed Solution

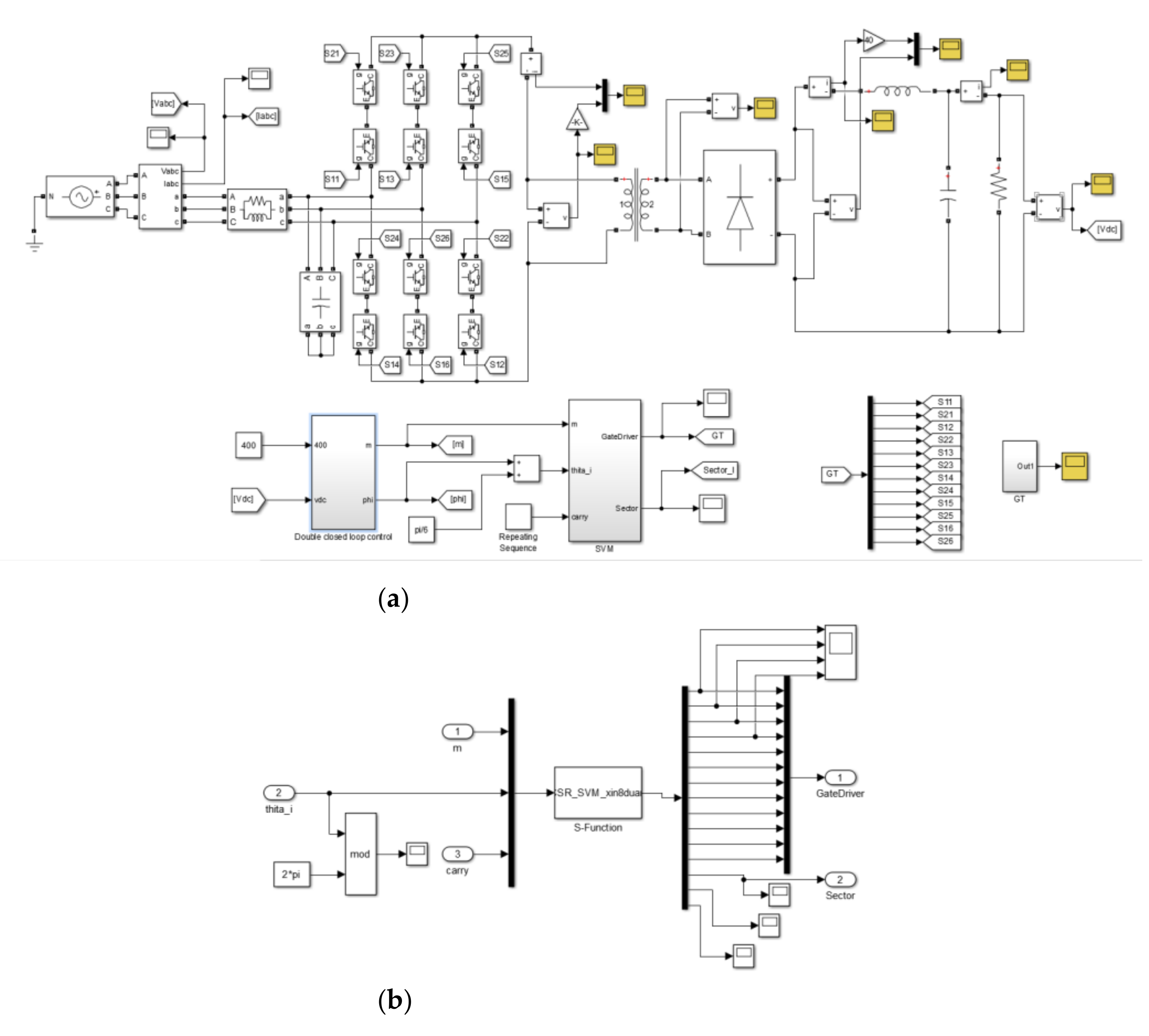

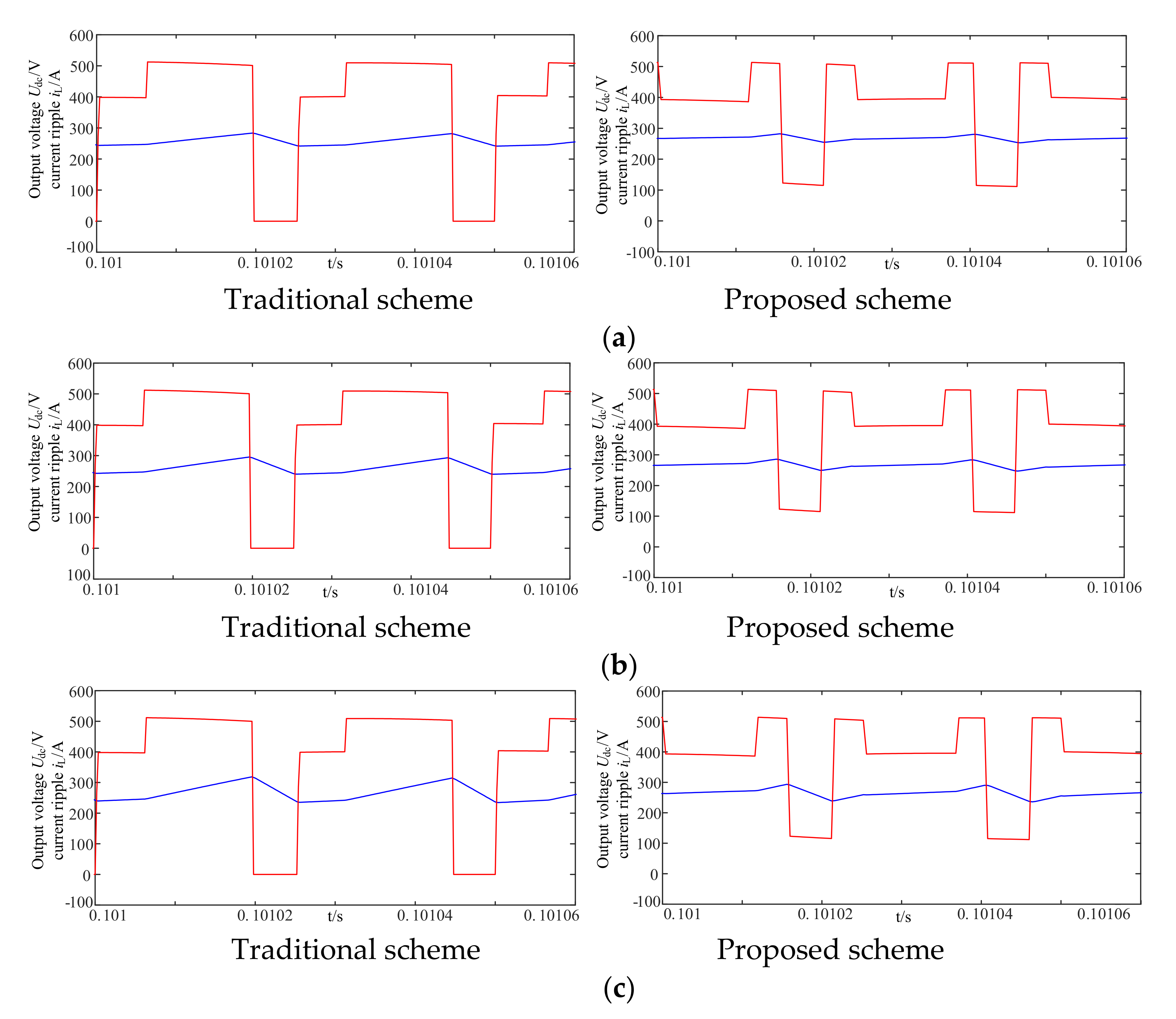

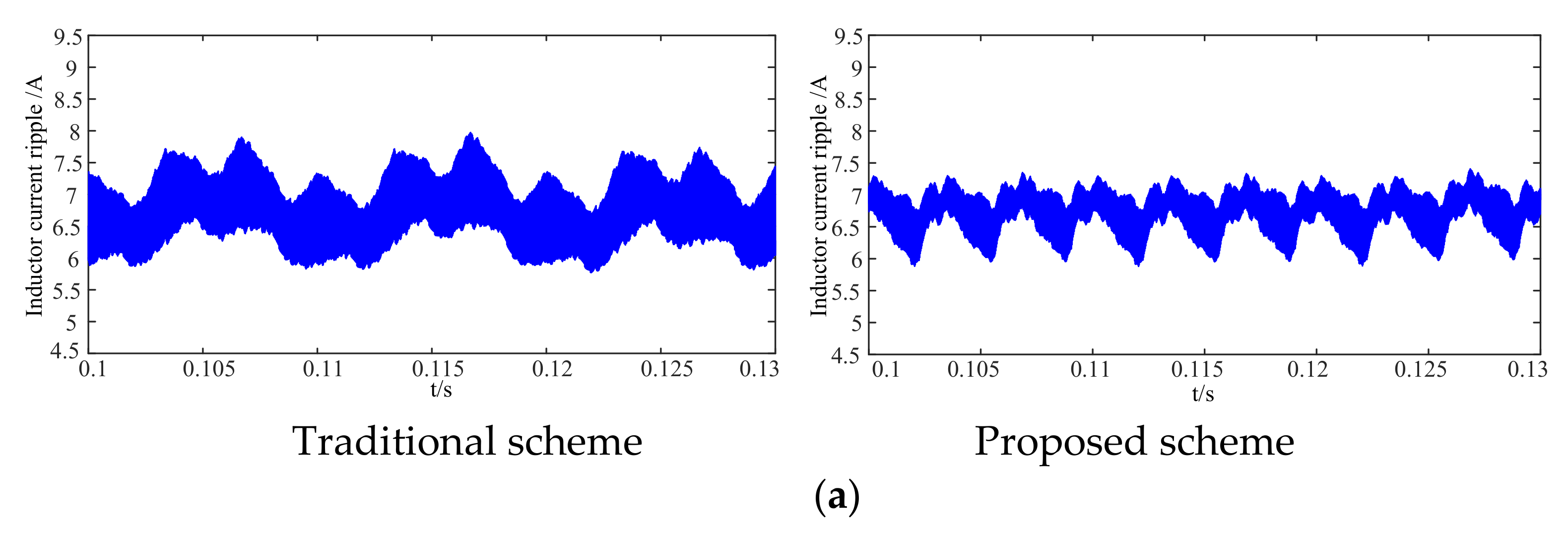

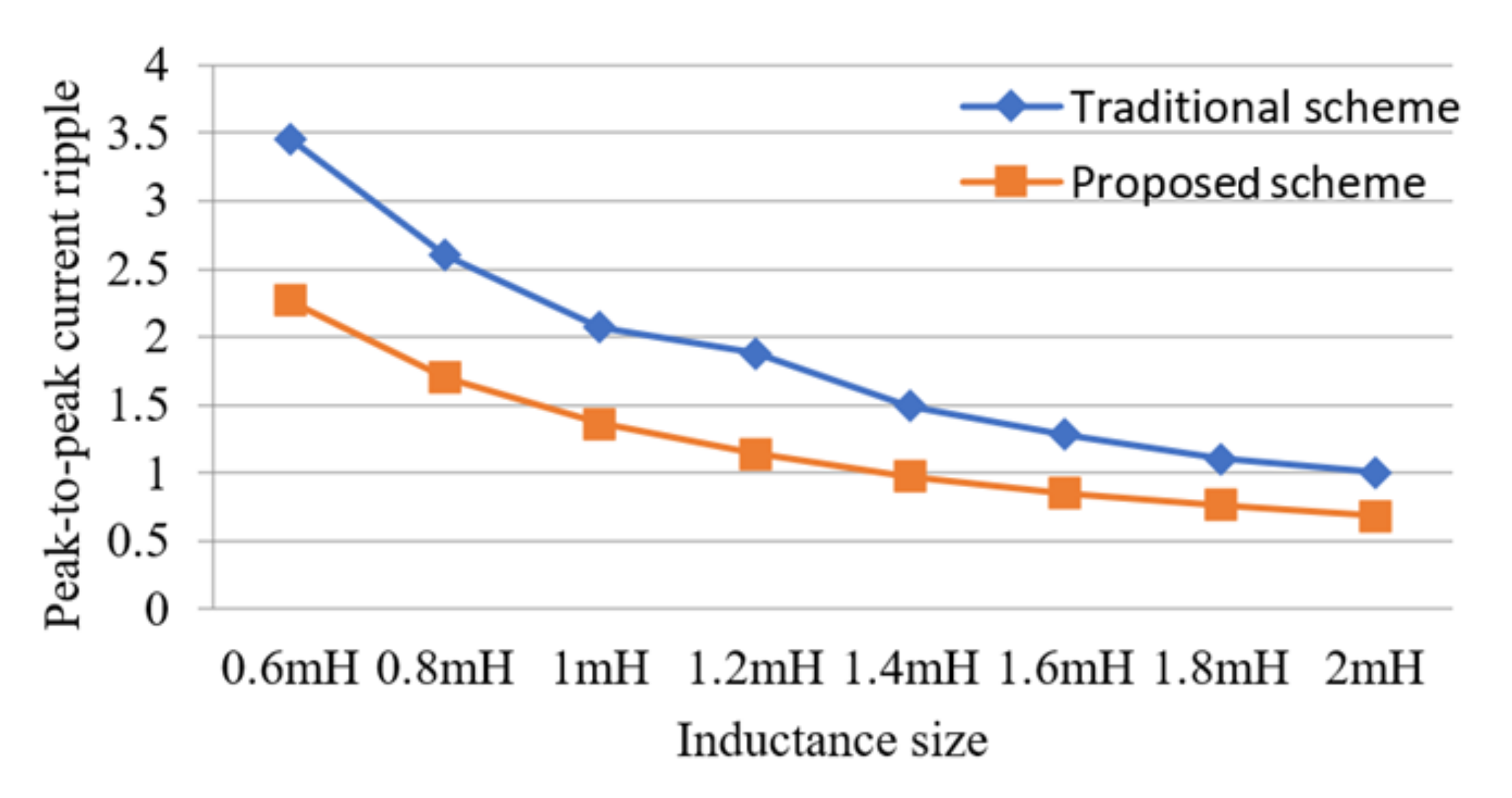

4. Simulation Results

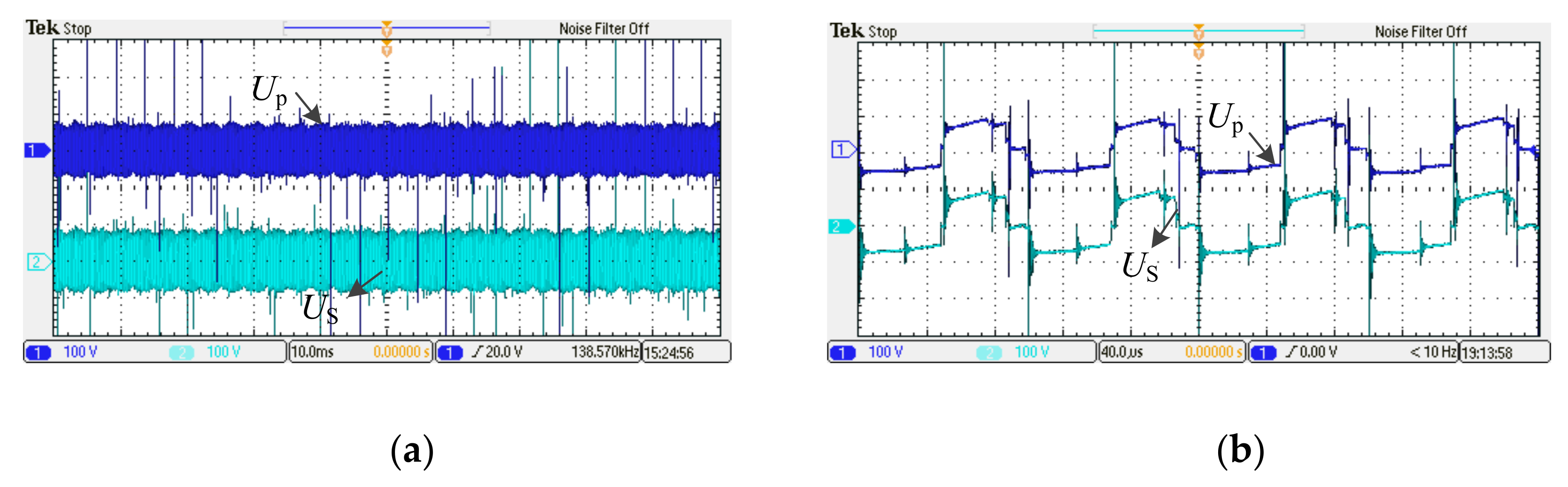

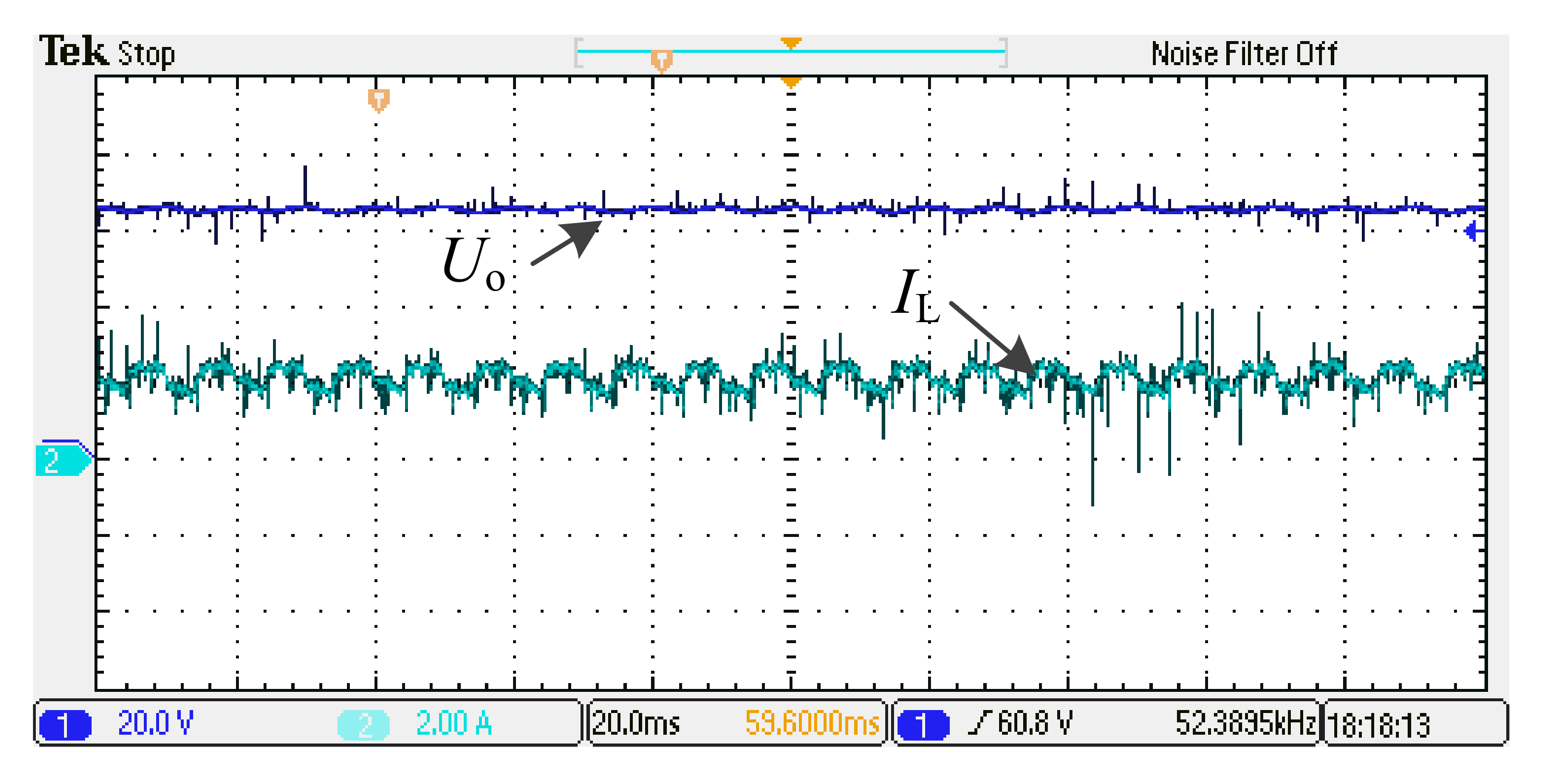

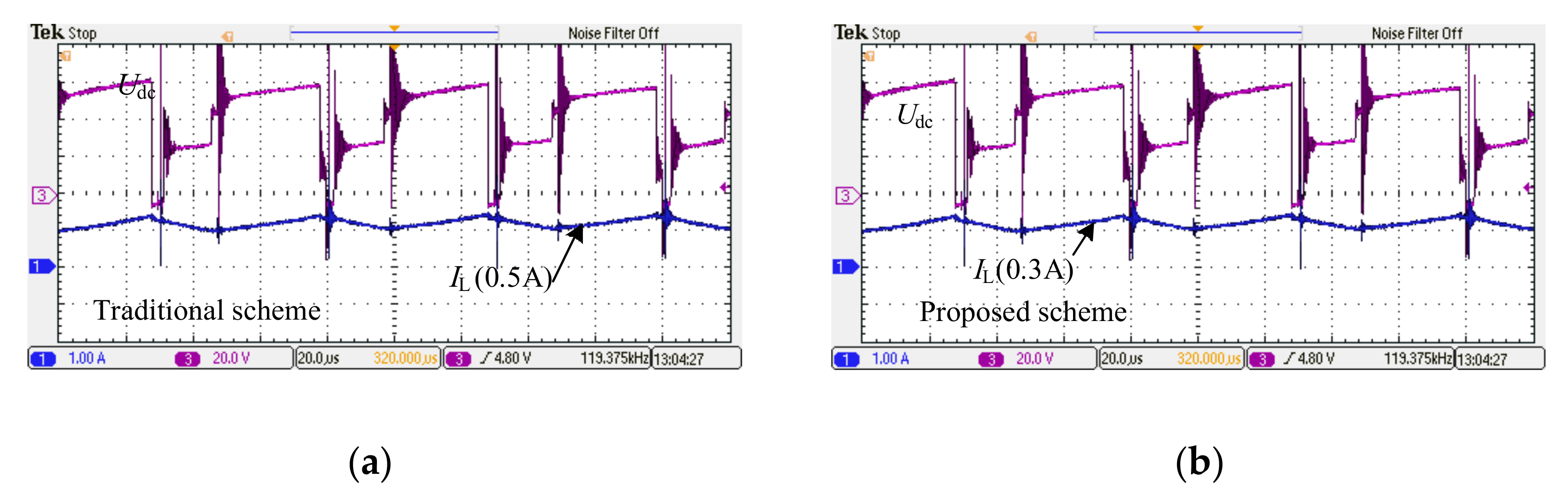

5. Experimental Results

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Data Availability Statement

Conflicts of Interest

Nomenclature

| SVPWM | Space vector pulse width modulation |

| FACTS | Flexible ac transmission system |

| FPGA | Field-programmable gate array |

| IGBT | Insulated gate bipolar transistor |

| HVDC | High voltage direct current |

| HFT | High-frequency transformer |

| THD | Total harmonic distortion |

| DSP | Digital signal processor |

| MC | Matrix converter |

References

- Kadem, K.; Bensetti, M.; Le Bihan, Y.; Labouré, E.; Debbou, M. Optimal Coupler Topology for Dynamic Wireless Power Transfer for Electric Vehicle. Energies 2021, 14, 3983. [Google Scholar] [CrossRef]

- Monjo, L.; Sainz, L.; Mesas, J.J.; Pedra, J. State-Space Model of Quasi-Z-Source Inverter-PV Systems for Transient Dynamics Studies and Network Stability Assessment. Energies 2021, 14, 4150. [Google Scholar]

- Xiao, G.; Na, W.; Bao, W.; Lu, Z.; Frede, B. Evaluation of Three-Phase Transformerless DC-Bypass PV Inverters for Leakage Current Reduction. IEEE Trans. Power. Electron. 2020, 35, 5918–5927. [Google Scholar]

- Duran, A.; Ibaceta, E.; Diaz, M.; Rojas, F.; Cardenas, R.; Chavez, H. Control of a Modular Multilevel Matrix Converter for Unified Power Flow Controller Applications. Energies 2020, 13, 953. [Google Scholar] [CrossRef] [Green Version]

- Casadei, D.; Serra, G.; Tani, A.; Zari, L. Matrix Converter Modulation Strategies: A New General Approach Based on Space-Vector Representation of The Switching State. IEEE Trans. Ind. Electron. 2002, 49, 370–381. [Google Scholar] [CrossRef]

- Nguyen, T.D.; Lee, H. Modulation Strategies to Reduce Common-Mode Voltage for Indirect Matrix converters. IEEE Trans. Ind. Electron. 2012, 59, 129–140. [Google Scholar] [CrossRef]

- Rivera, M.; Wilson, A.; Rojas, C.A.; Rodrigez, J.; Espinoza, J.R.; Wheeler, P.W.; Empringham, L. A Comparative Assessment Of Model Predictive Current Control And Space Vector Modulation In A Direct Matrix Converter. IEEE Trans. Ind. Electron. 2013, 60, 578–588. [Google Scholar] [CrossRef]

- Rodriguez, J.; Rivera, M.; Kolar, J.W.; Wheeler, P.W. A Review of Control and Modulation Methods for Matrix Converters. IEEE Trans. Ind. Electron. 2012, 59, 58–70. [Google Scholar] [CrossRef]

- Alesina, A.; Venturini, M.G.B. Analysis and Design of Optimum-Amplitude Nine-Switch Direct AC-AC Converter. IEEE Trans. Power. Electron. 1989, 4, 101–112. [Google Scholar] [CrossRef]

- Vazquez, S.; Lukic, S.M.; Galvan, E.; Franquelo, L.G.; Carrasco, J.M. Energy Storage Systems For Transport and Grid Applications. IEEE Trans. Ind. Electron. 2010, 57, 3881–3895. [Google Scholar] [CrossRef] [Green Version]

- Bhuiyan, F.A.; Yazdani, A. Energy Storage Technologies for Grid Connected and Off-Grid Power System Applications. In Proceedings of the IEEE Electrical Power and Energy Conference, London, ON, Canada, 10–12 October 2012; pp. 303–310. [Google Scholar]

- Al-Tameemi, M.; Miura, Y.; Liu, J.; Bevrani, H.; Ise, T. A Novel Control Scheme for Multi-Terminal Low-Frequency AC Electrical Energy Transmission Systems Using Modular Multilevel Matrix Converters and Virtual Synchronous Generator Concept. Energies 2020, 13, 747. [Google Scholar] [CrossRef] [Green Version]

- Yilmaz, M.; Krein, P. Review of Battery Charger Topologies, Charging Power Levels and Infrastructure for Plug-In Electric and Hybrid Vehicles. IEEE Trans. Power Electron. 2013, 28, 2151–2169. [Google Scholar] [CrossRef]

- Afsharian, J.; David, X.; Gong, B.; Yang, Z. Space Vector Demonstration And Analysis Of Zero-Voltage Switching Transitions In Three-Phase Isolated PWM Rectifier. In Proceedings of the IEEE Energy Conversion Congress and Exposition, Montreal, QC, Canada, 20–24 September 2015; pp. 2477–2484. [Google Scholar]

- Feng, B.; Lin, H.; Wang, X.; An, X.; Liu, B. Optimal Zero-Vector Configuration For Space Vector Modulated AC-DC Matrix Converter. In Proceedings of the IEEE Energy Conversion Congress and Exposition, Montreal, CA, Canada, 20–24 September 2012; pp. 291–297. [Google Scholar]

- Baumann, M.; Kolar, J. Minimization of the Dc Current Ripple of a Three-Phase Buck-Boost PWM Unity Power Factor Rectifier. In Proceedings of the Power Conversion Conference-Osaka 2002, Osaka, Japan, 2–5 April 2002; pp. 472–477. [Google Scholar]

- Guo, X.; Yang, Y.; Wang, X. Optimal Space Vector Modulation of Current Source Converter for DC Link Current Ripple Reduction. IEEE Trans. Ind. Electron. 2019, 66, 1671–1680. [Google Scholar] [CrossRef]

- Shuai, D.; Zhang, Q.; Cheng, S. Inductor Current Ripple Comparison between ZSVM4 and ZSVM2 for Z-source Inverters. IEEE Trans. Power. Electron. 2016, 31, 7592–7597. [Google Scholar]

- He, Y.; Xu, Y.; Chen, J. New Space Vector Modulation Strategies to Reduce Inductor Current Ripple of Z-source Inverters. IEEE Trans. Power. Electron. 2018, 33, 2643–2654. [Google Scholar] [CrossRef]

- Guo, X.; Xu, D.; Guerrero, J.M.; Wu, B. Space Vector Modulation For Dc-Link Current Ripple Reduction In Back-To-Back Current-Source Converters For Microgrid Applications. IEEE Trans. Ind. Electron. 2015, 62, 6008–6013. [Google Scholar] [CrossRef]

- Afsharian, J.; Xu, D.; Gong, B.; Yang, Z. Reduced Duty-Cycle Loss and Output Inductor Current Ripple in A ZVS Switched Three-Phase Isolated PWM Rectifier. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition, Long Beach, CA, USA, 20–24 March 2016; pp. 33–37. [Google Scholar]

- Afsharian, J.; Xu, D.; Wu, B.; Gong, B.; Yang, Z. The Optimal PWM Modulation and Commutation Scheme For A Three-Phase Isolated Buck Matrix-Type Rectifier. IEEE Trans. Power Electron. 2018, 33, 110–124. [Google Scholar] [CrossRef]

- Li, X.; Wu, F.; Yang, G.; Liu, H.; Meng, F. Precise Calculation Method of Vector Dwell Times for Single-Stage Isolated Three-Phase Buck-Type Rectifier to Reduce Grid Current Distortions. IEEE Emerg. Sel. Top. Power Electron. 2020, 8, 4457–4466. [Google Scholar] [CrossRef]

- Fang, F.; Tian, H.; Li, Y. Coordination Control of Modulation Index and Phase Shift Angle for Current Stress Reduction in Isolated AC–DC Matrix Converter. IEEE Trans. Power Electron. 2021, 36, 4585–4596. [Google Scholar] [CrossRef]

| Space Vector | Switch State | Output Voltage | |||||

|---|---|---|---|---|---|---|---|

| S1 | S4 | S3 | S6 | S5 | S2 | ||

| I1+/I4− | 1 | 0 | 0 | 1 | 0 | 0 | UAB |

| I2+/I5− | 1 | 0 | 0 | 0 | 0 | 1 | UAC |

| I3+/I6− | 0 | 0 | 1 | 0 | 0 | 1 | UBC |

| I4+/I1− | 0 | 1 | 1 | 0 | 0 | 0 | UBA |

| I5+/I2− | 0 | 1 | 0 | 0 | 1 | 0 | UCA |

| I6+/I3− | 0 | 0 | 0 | 0 | 1 | 1 | UCB |

| I7 | 1 | 1 | 0 | 0 | 0 | 0 | 0 |

| I8 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| I9 | 0 | 0 | 1 | 1 | 0 | 0 | 0 |

| VP > 0, IP > 0 | VP < 0, IP < 0 | ||||

|---|---|---|---|---|---|

| Vector | Switches | Line Voltage | Vector | Switches | Line Voltage |

| I1 | (S11,S21)(S16,S26) | Uab | I1 | (S13,S23)(S14,S24) | −Uab |

| I2 | (S11,S21)(S12,S22) | Uac | I2 | (S14,S24)(S15,S25) | −Uac |

| I3 | (S12,S22)(S13,S23) | Ubc | I3 | (S15,S25)(S16,S26) | −Ubc |

| I4 | (S13,S23)(S14,S24) | −Uab | I4 | (S11,S21)(S16,S26) | Uab |

| I5 | (S14,S24)(S15,S25) | −Uac | I5 | (S11,S21)(S12,S22) | Uac |

| I6 | (S15,S25)(S16,S26) | −Ubc | I6 | (S12,S22)(S13,S23) | Ubc |

| Sector | Vector Action Sequence |

|---|---|

| 1 | I1-I2-I3-I2-I4-I5-I6-I5 |

| 2 | I3-I2-I1-I2-I6-I5-I4-I5 |

| 3 | I2-I3-I4-I3-I5-I6-I1-I6 |

| 4 | I4-I3-I2-I3-I1-I6-I5-I6 |

| 5 | I3-I4-I5-I4-I6-I1-I2-I1 |

| 6 | I5-I4-I3-I4-I2-I1-I6-I1 |

| 7 | I4-I5-I6-I5-I1-I2-I3-I2 |

| 8 | I6-I5-I4-I5-I3-I2-I1-I2 |

| 9 | I5-I6-I1-I6-I2-I3-I4-I3 |

| 10 | I1-I6-I5-I6-I4-I3-I2-I3 |

| 11 | I6-I1-I2-I1-I3-I4-I5-I4 |

| 12 | I2-I1-I6-I1-I5-I4-I3-I4 |

| Parameters | Value |

|---|---|

| Power voltage Uref | 380 V |

| AC inductance Lf | 2.5 mH |

| AC capacitance Cf | 10 μF |

| Switching frequency fs | 20 kHz |

| DC inductance Ldc | 1 mH |

| DC capacitance Cdc | 940 μF |

| Load resistance R | 50 Ω |

| Transformer leakage inductance Llk | 3.6 μH |

| Parameters | Value |

|---|---|

| Power voltage Uref | 50 V |

| AC inductance Lf | 2.5 mH |

| AC capacitance Cf | 10 μF |

| Switching frequency fs | 10 kHz |

| DC inductance Ldc | 1 mH |

| DC capacitance Cdc | 940 μF |

| Load Rdc | 30 Ω |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, S.; Wang, H.; Ding, H.; Xun, L.; Wu, S. A New SVPWM Strategy for Three-Phase Isolated Converter with Current Ripple Reduction. Energies 2021, 14, 4966. https://doi.org/10.3390/en14164966

Wang S, Wang H, Ding H, Xun L, Wu S. A New SVPWM Strategy for Three-Phase Isolated Converter with Current Ripple Reduction. Energies. 2021; 14(16):4966. https://doi.org/10.3390/en14164966

Chicago/Turabian StyleWang, Sheng, Huaibao Wang, Hao Ding, Ligen Xun, and Sifan Wu. 2021. "A New SVPWM Strategy for Three-Phase Isolated Converter with Current Ripple Reduction" Energies 14, no. 16: 4966. https://doi.org/10.3390/en14164966

APA StyleWang, S., Wang, H., Ding, H., Xun, L., & Wu, S. (2021). A New SVPWM Strategy for Three-Phase Isolated Converter with Current Ripple Reduction. Energies, 14(16), 4966. https://doi.org/10.3390/en14164966