Temperature Estimation of SiC Power Devices Using High Frequency Chirp Signals

Abstract

1. Introduction

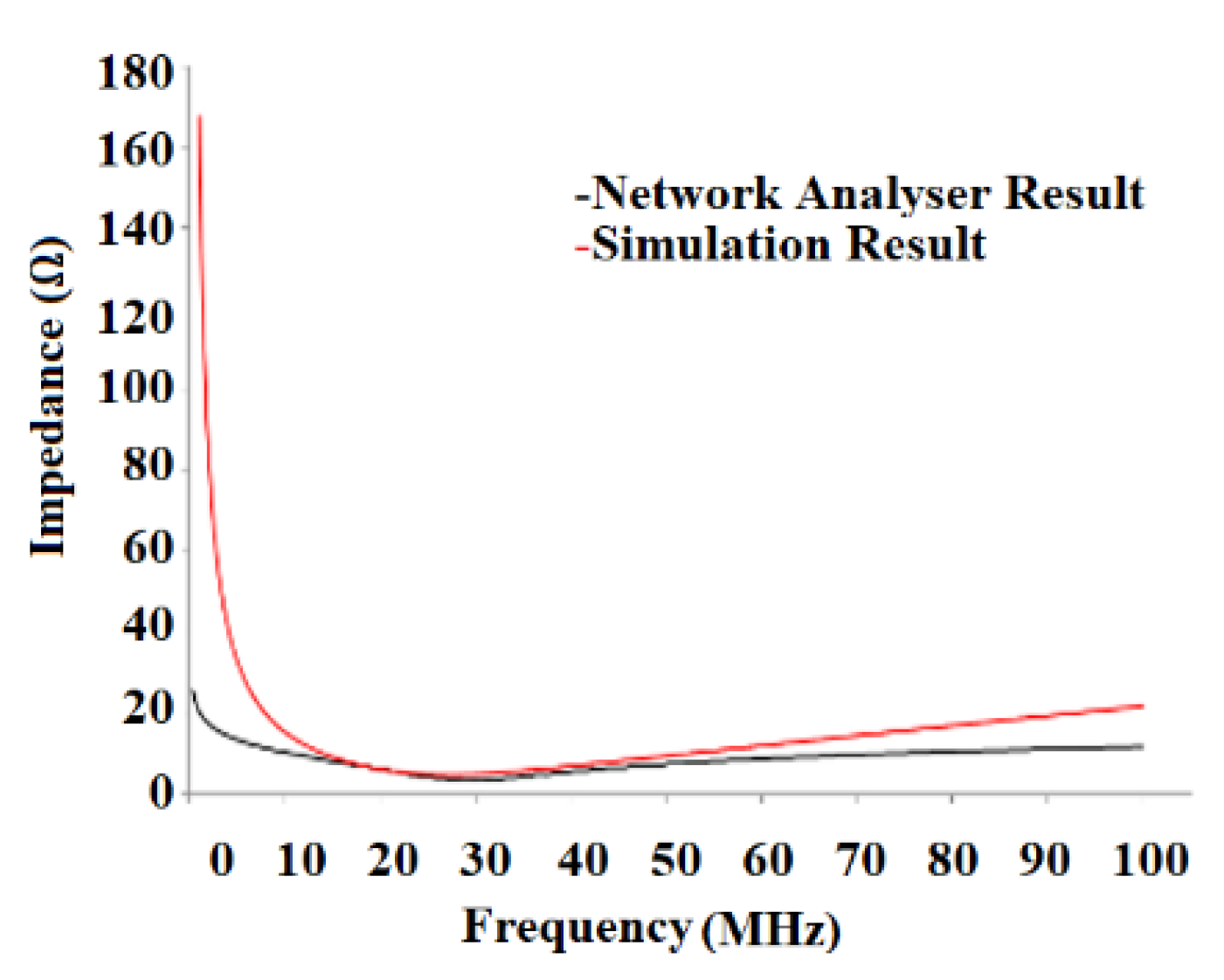

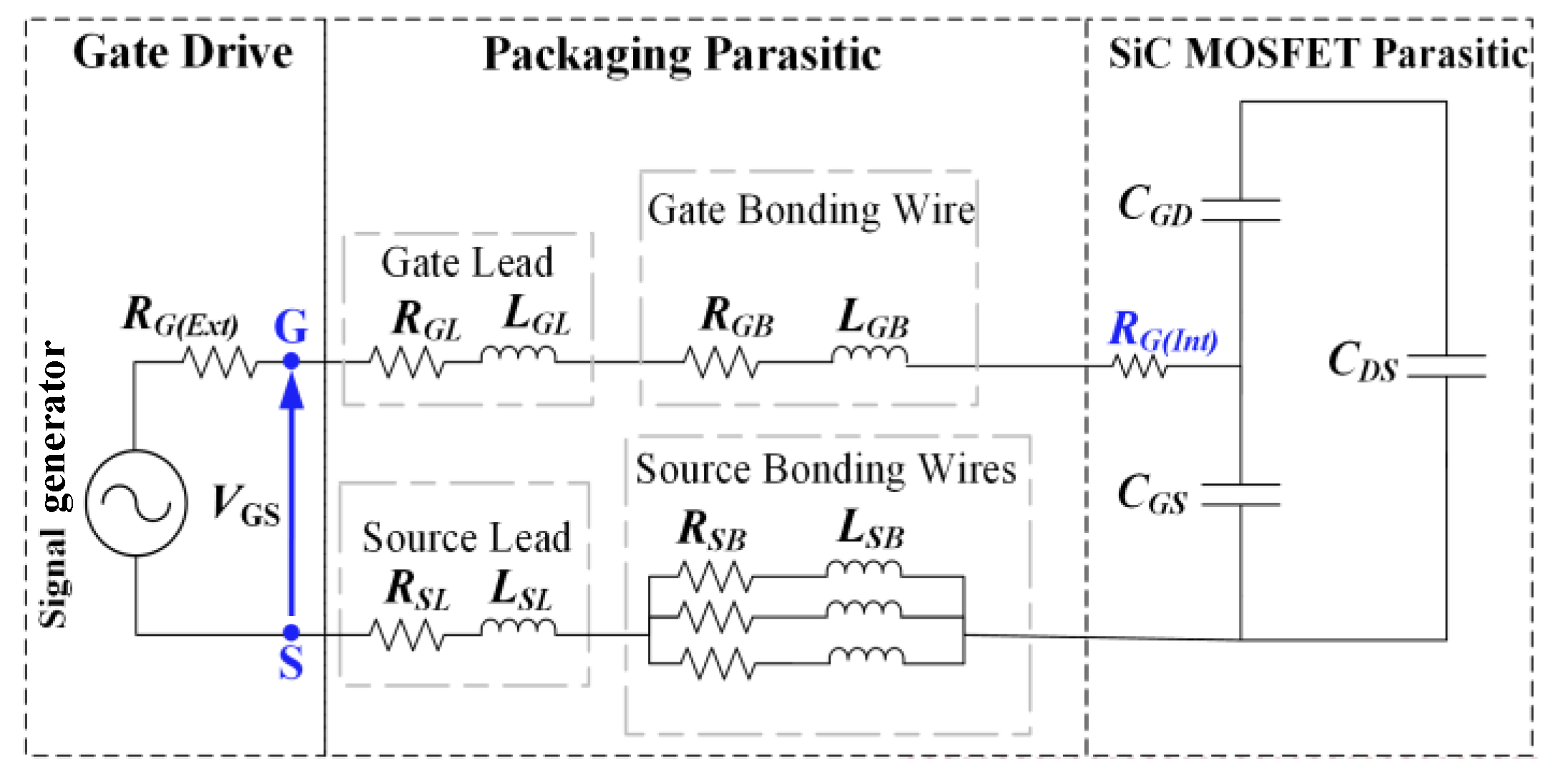

2. Small-Signal Modelling of the SiC MOSFET Power Device

2.1. Packaging Parasitics

2.2. SiC MOSFET Parasitic

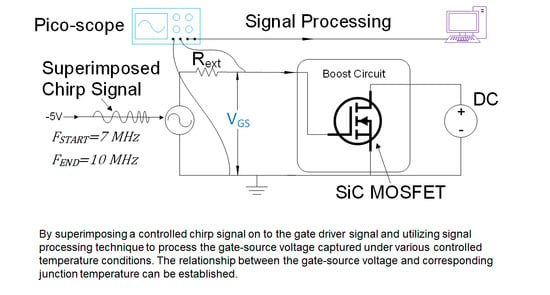

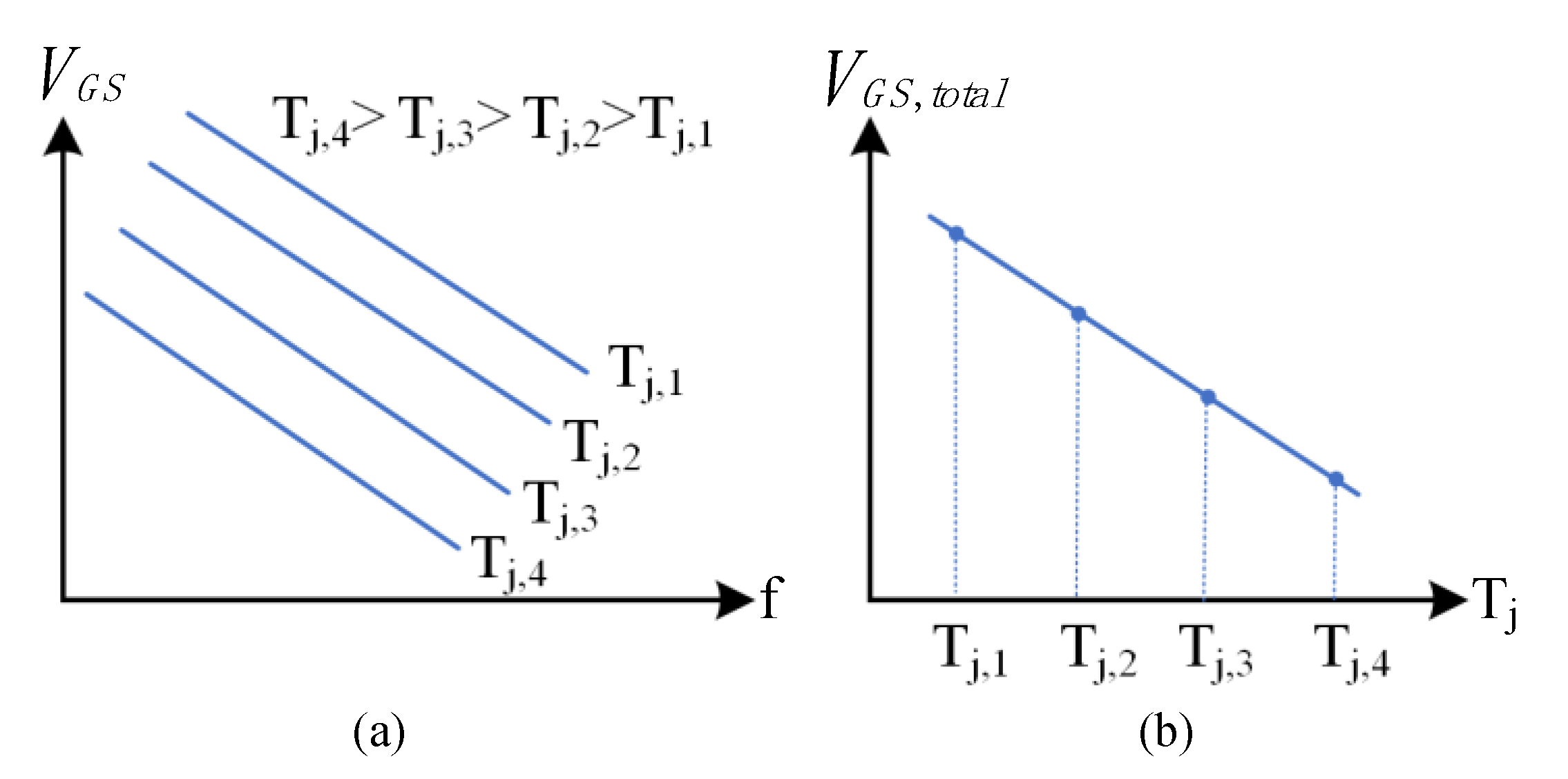

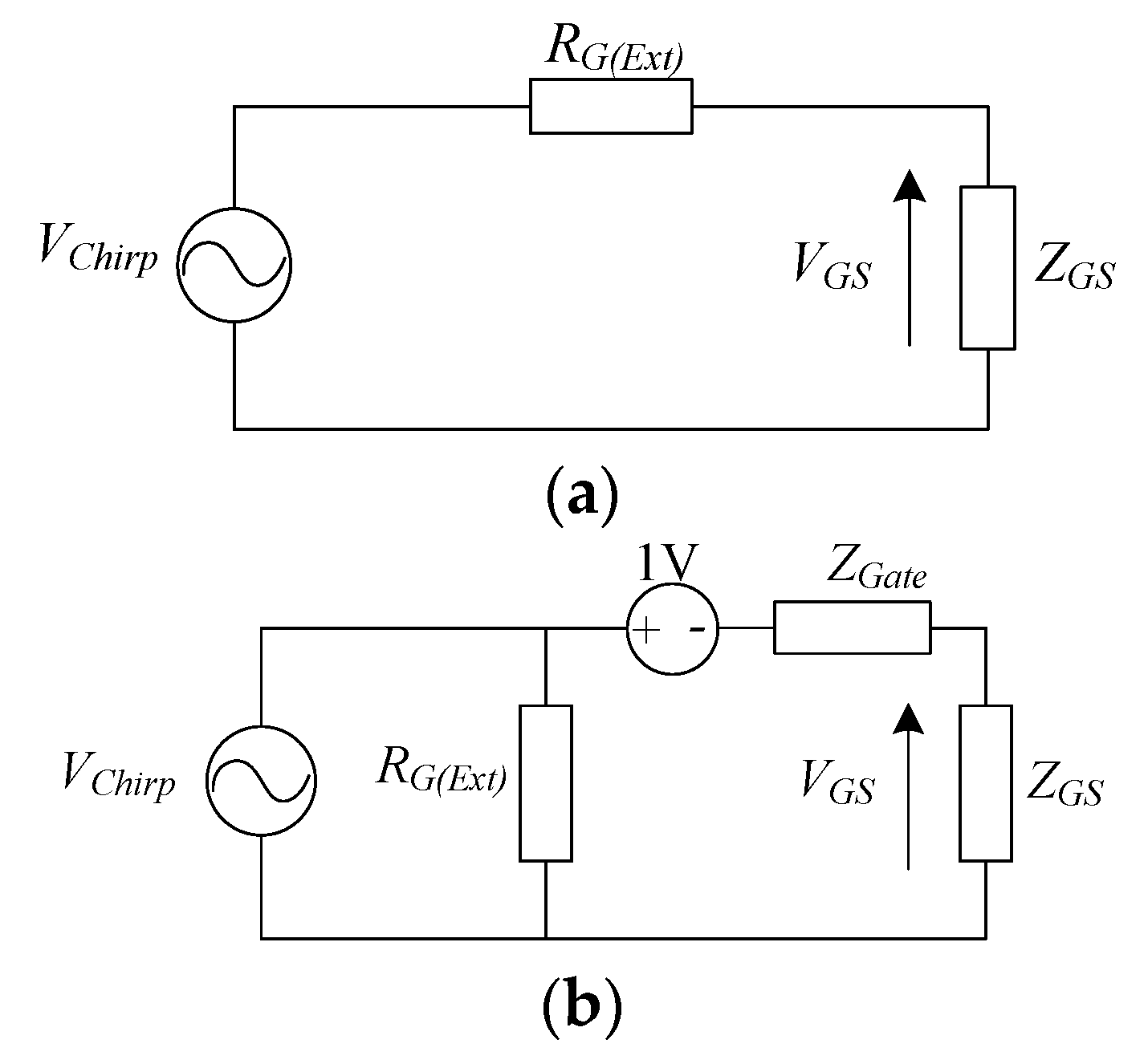

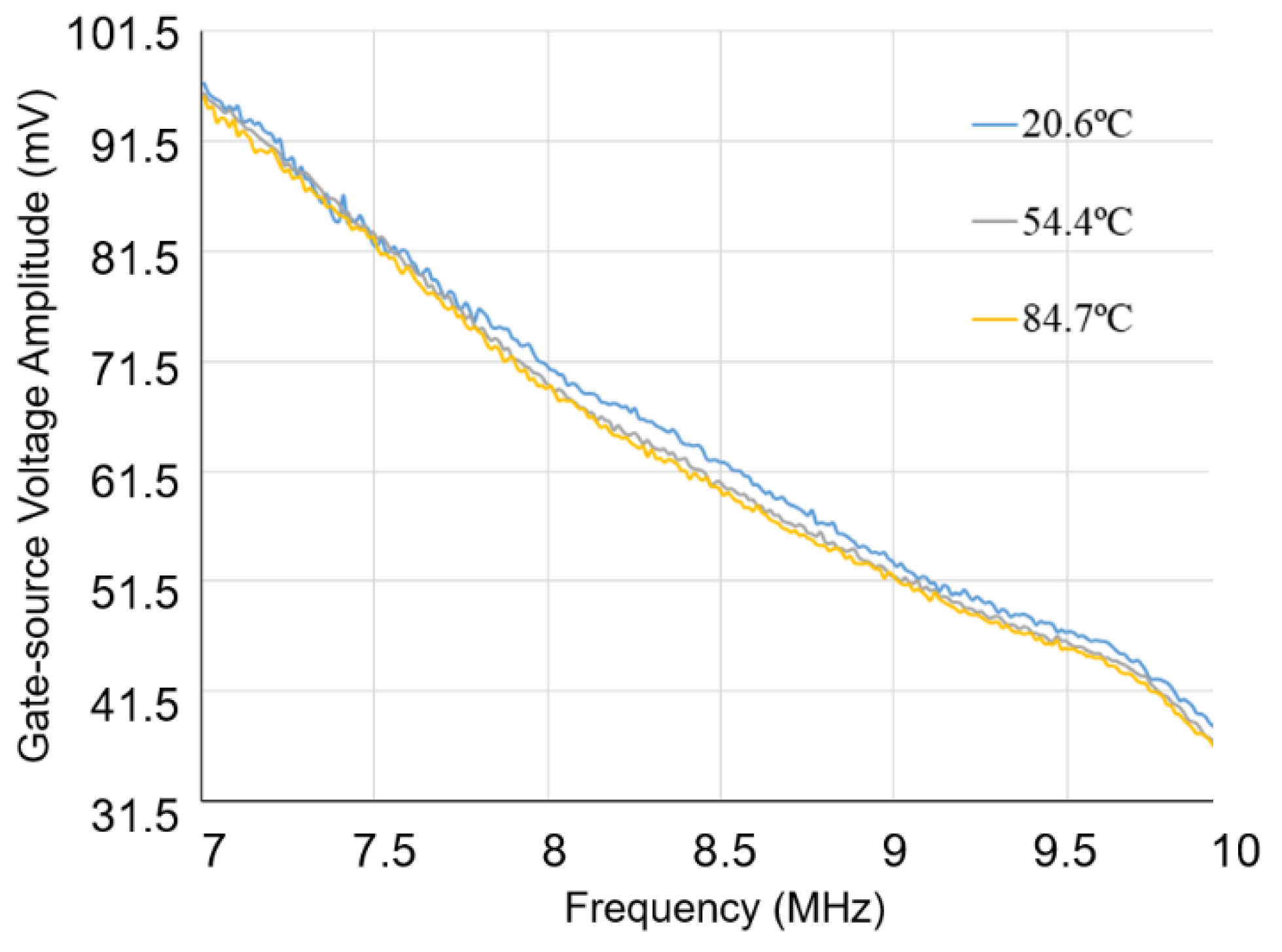

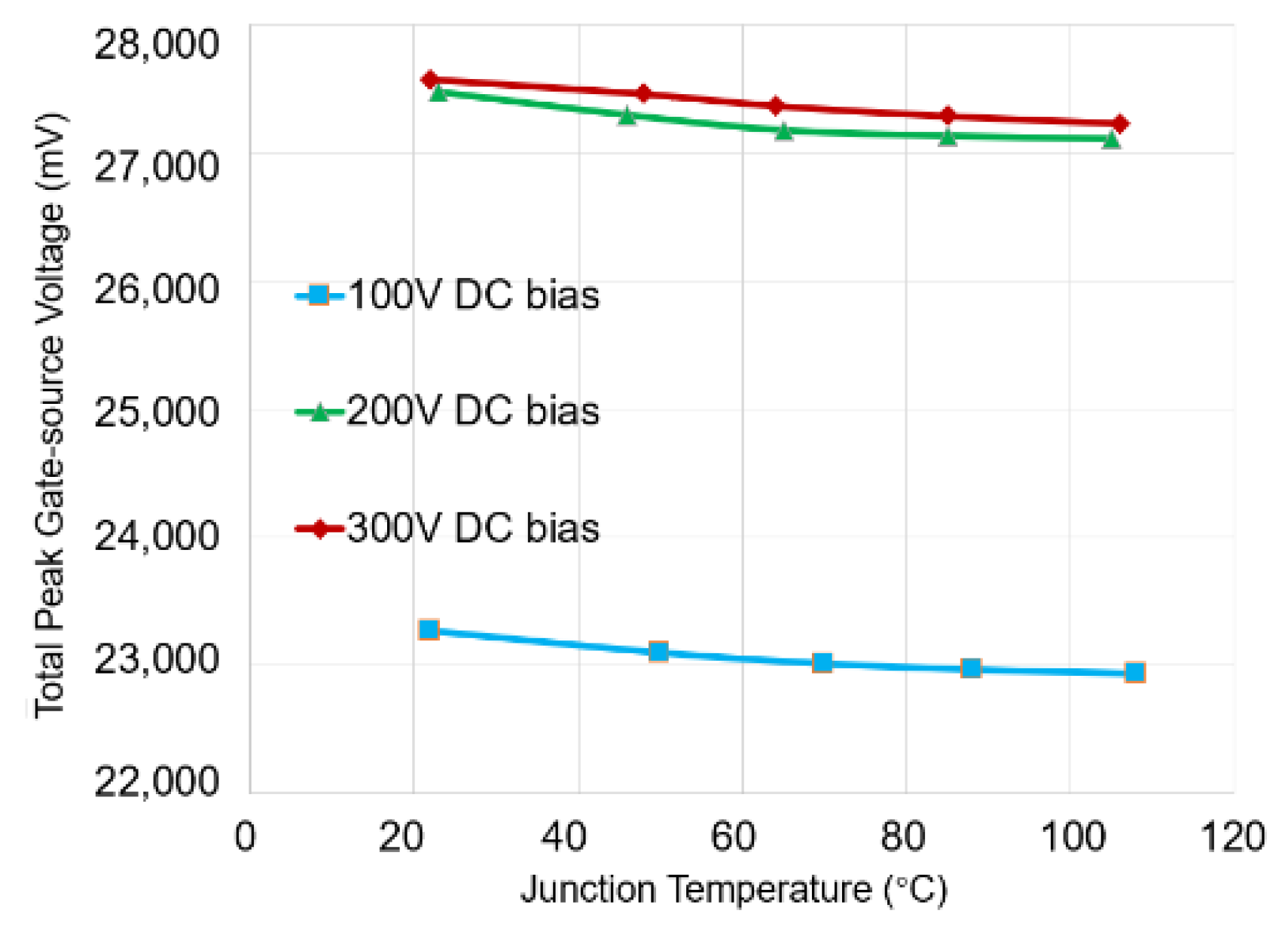

3. Principle of the Proposed TSEP

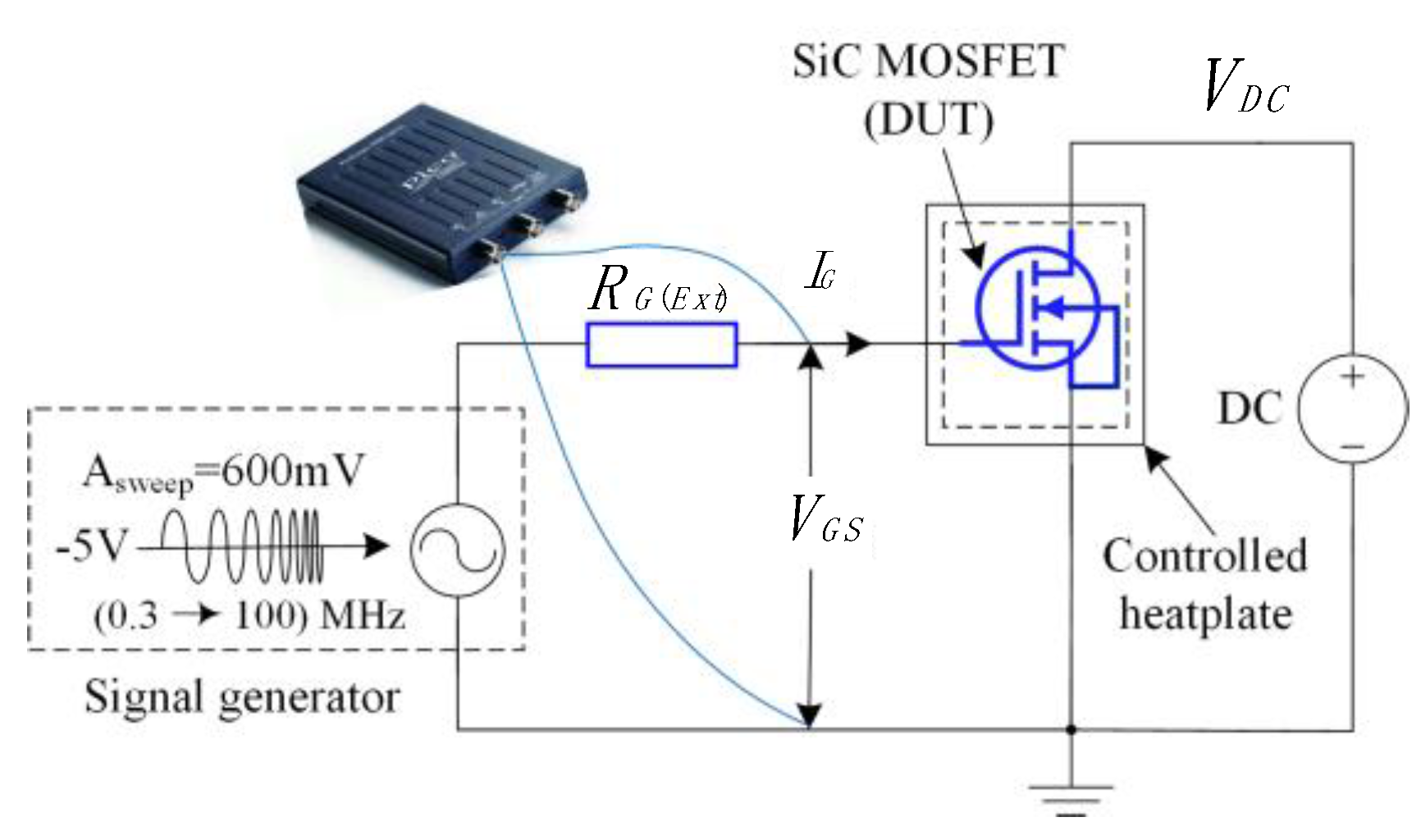

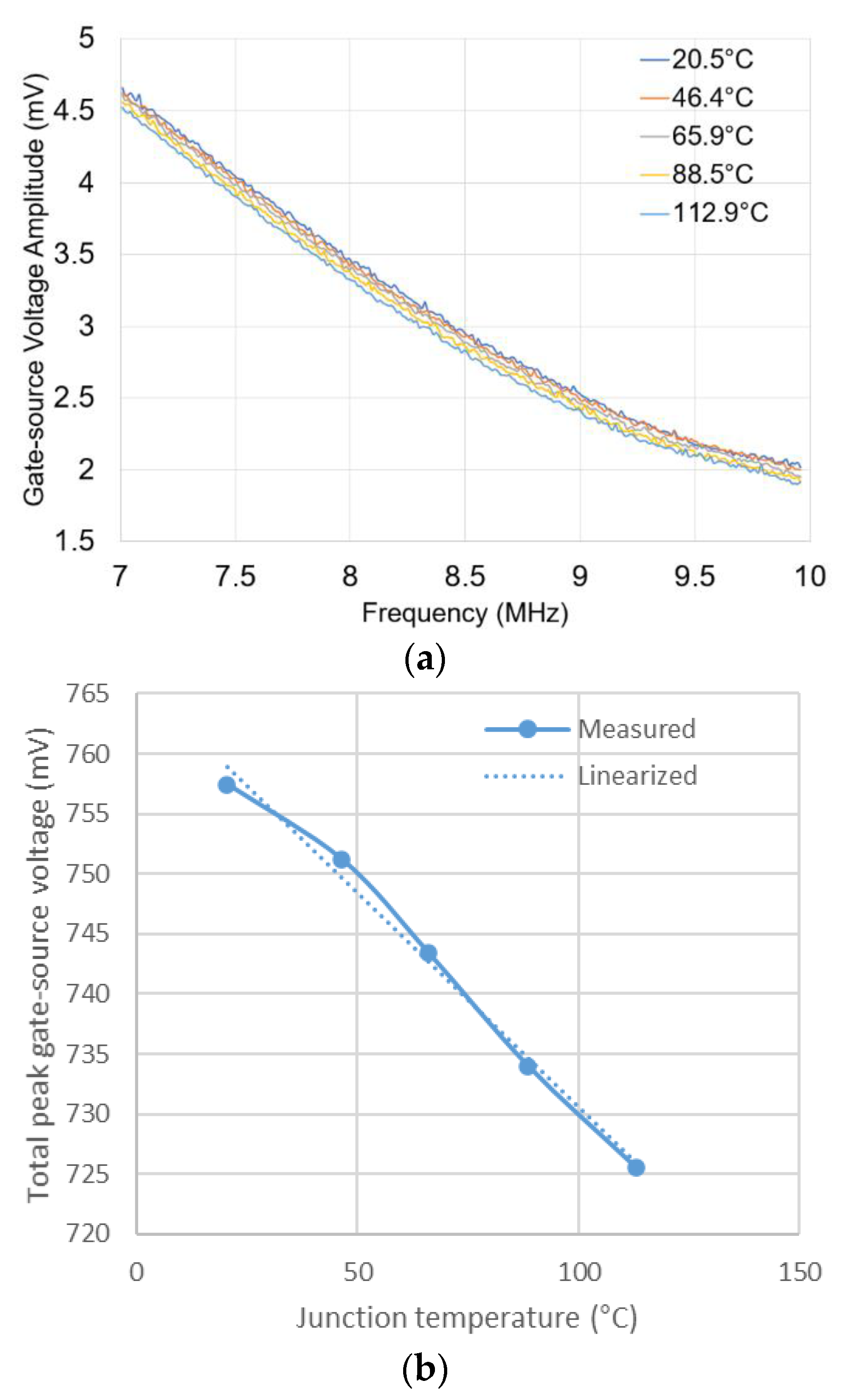

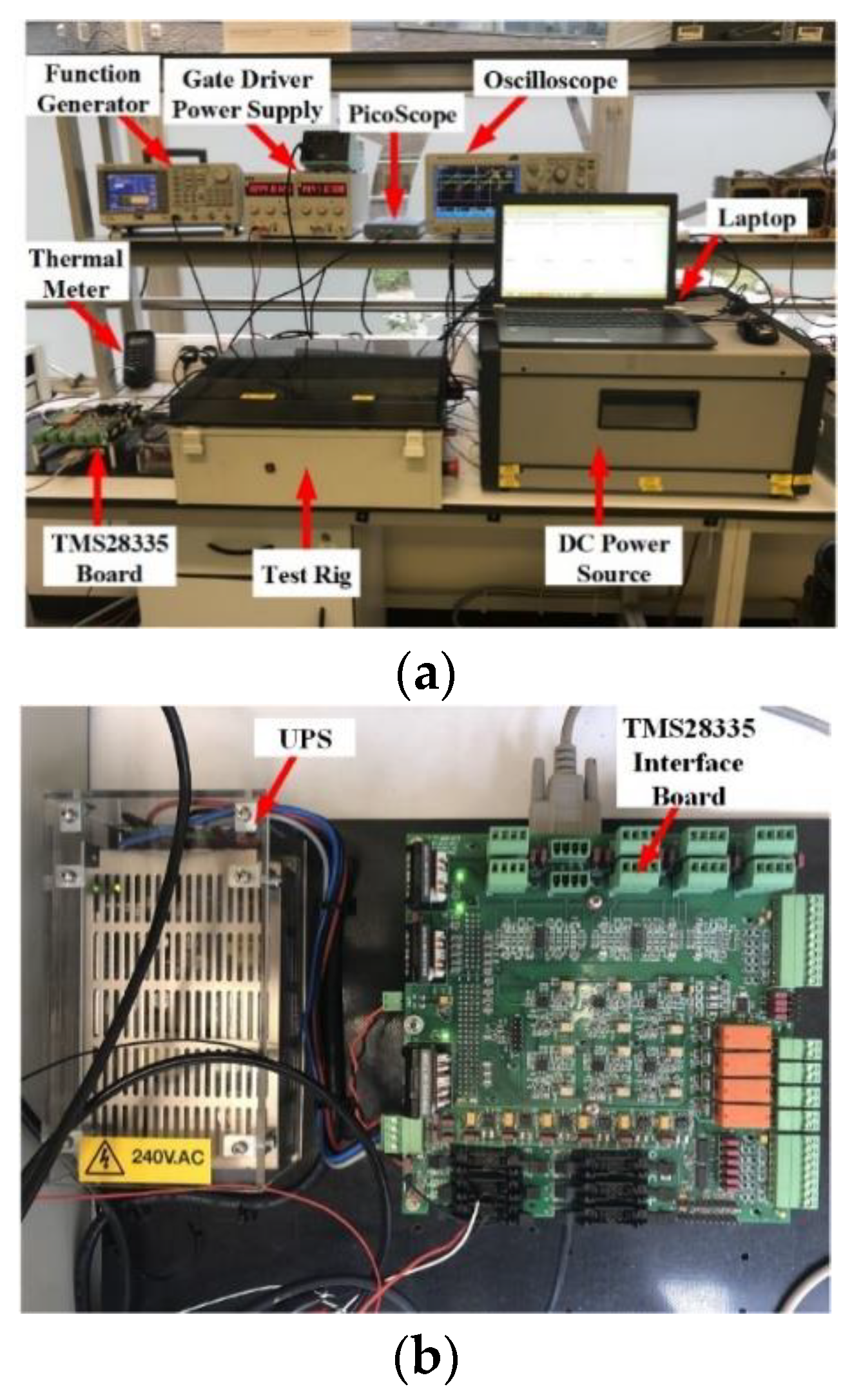

4. Proposed TSEP Applied in the Laboratory Environment

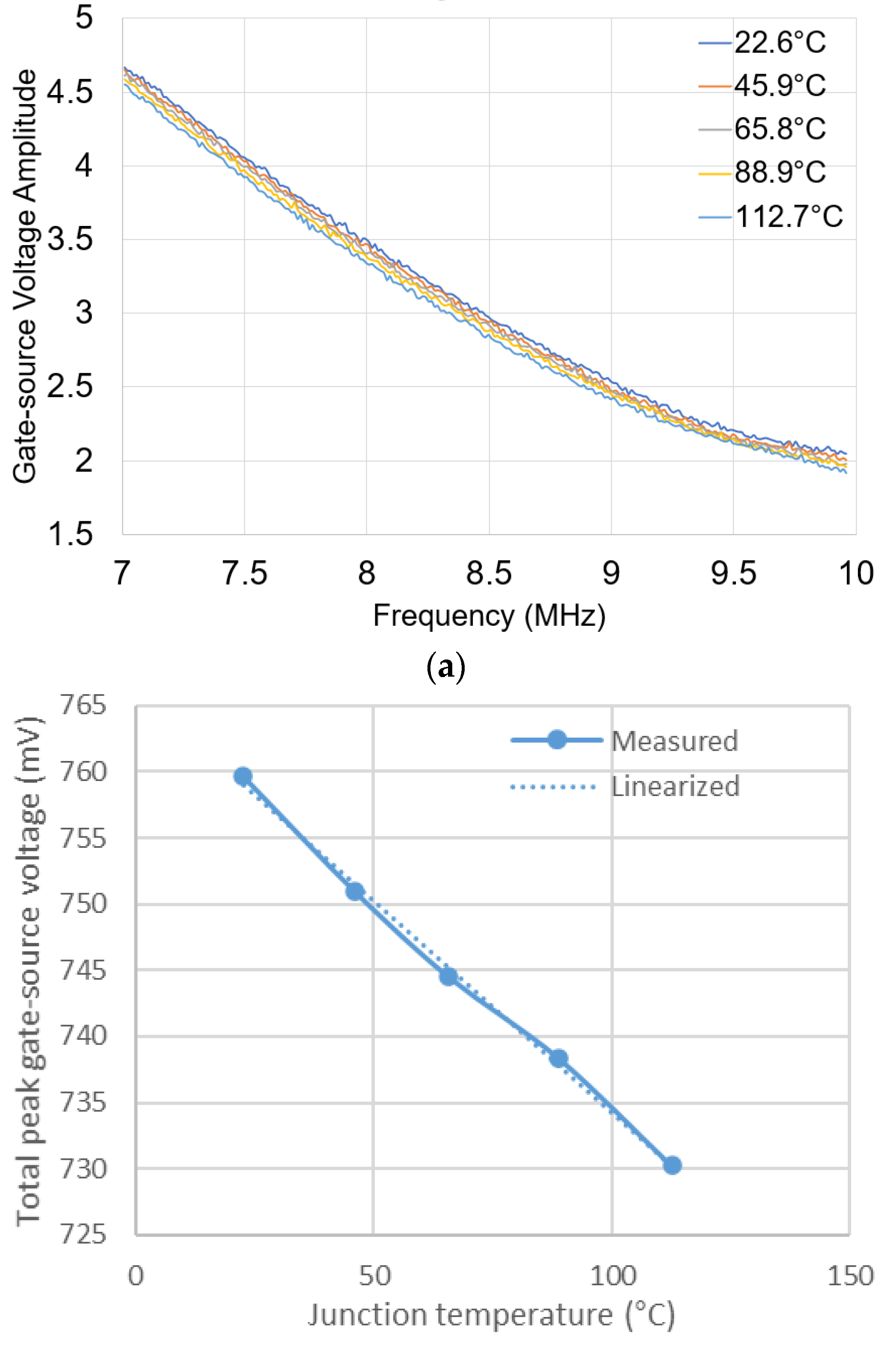

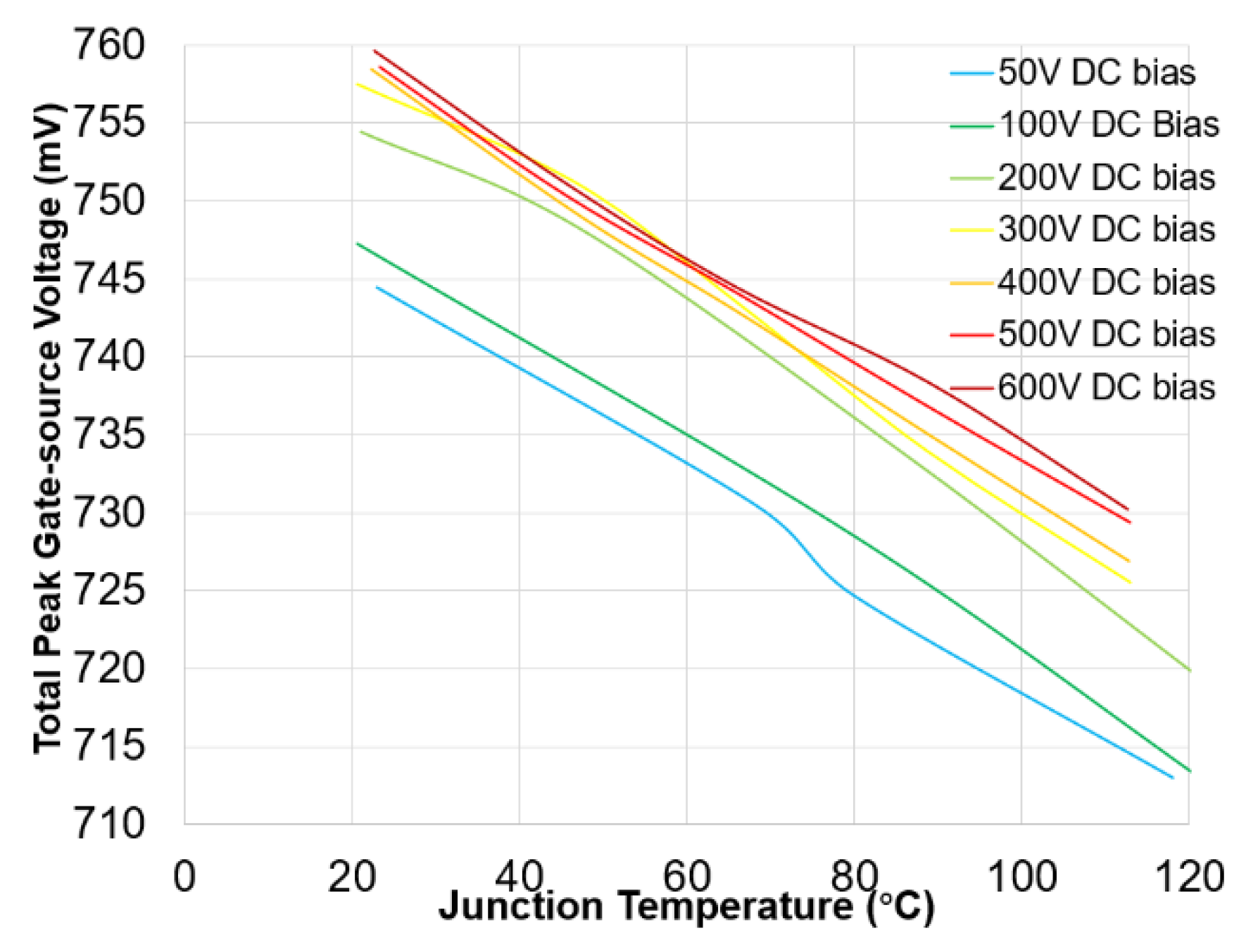

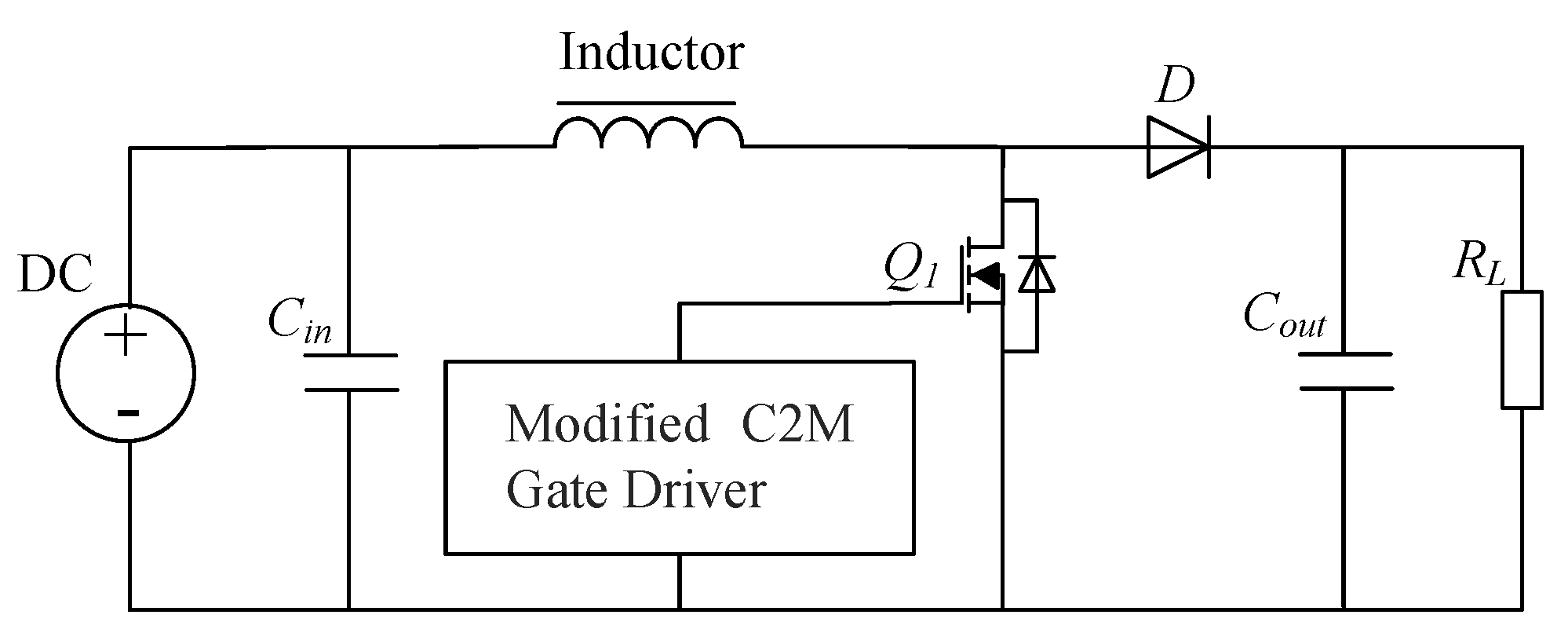

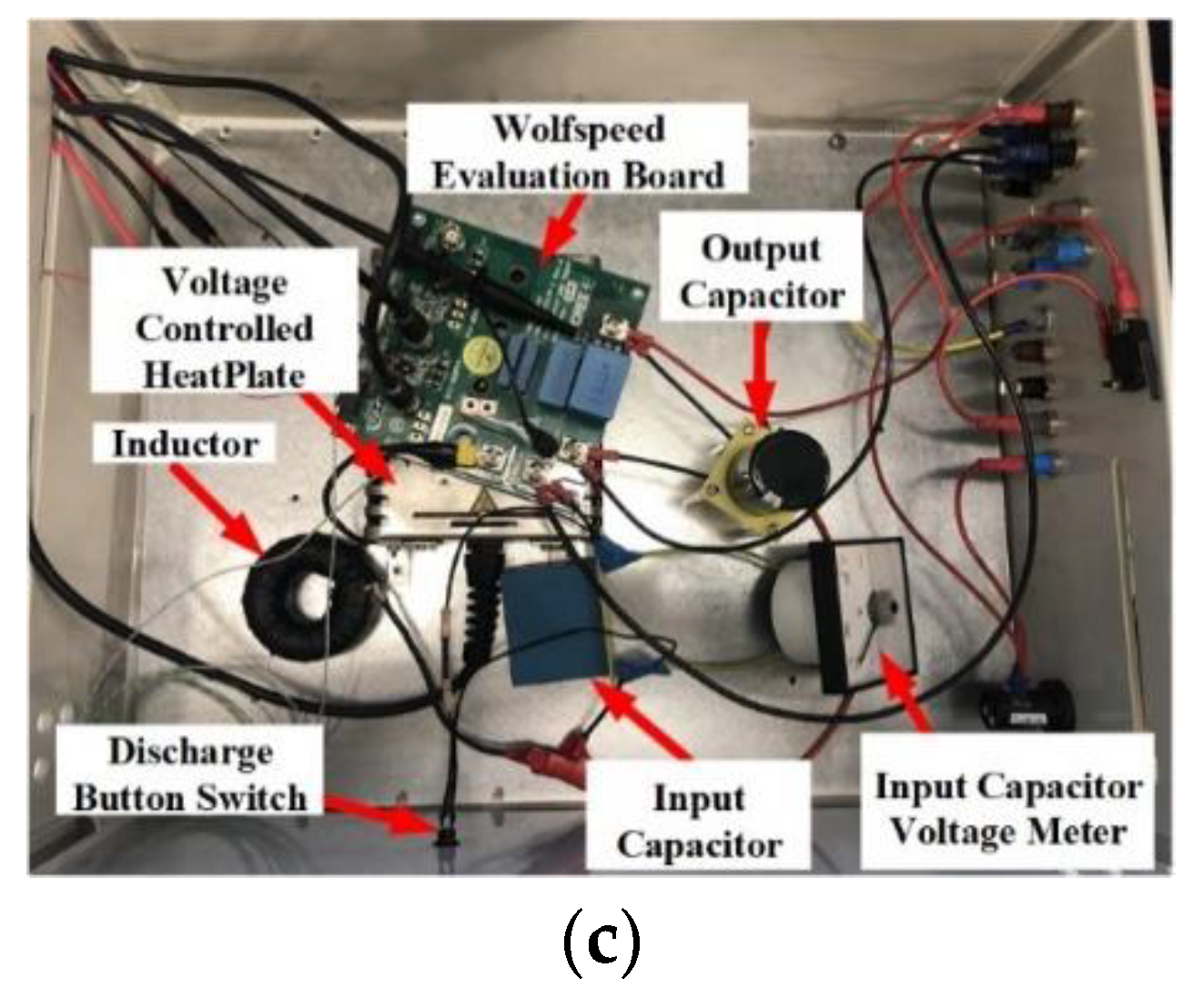

5. Proposed TSEP Applied in a DC/DC Converter

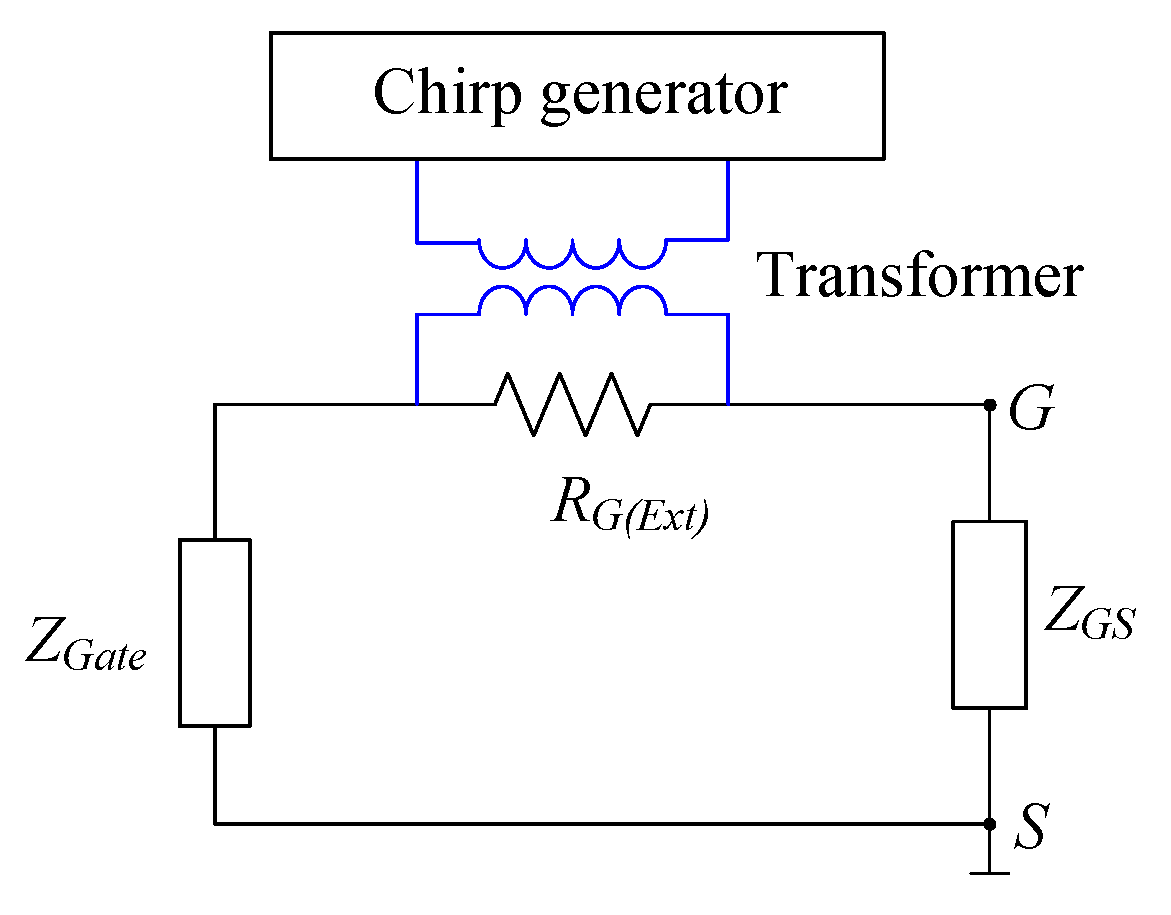

5.1. Integration of the Chirp Signal with the Gate Driver Circuit

5.2. Online Estimation

6. Discussion

7. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

Abbreviations

| EV | Electric Vehicle |

| DFT | Discrete Fourier Transform |

| FFT | Fast Fourier Transform |

| GaN | Gallium Nitride |

| IR | Infrared Thermal Camera |

| LSWA | Least-Squares Wavelet Analysis |

| MOSFET | Metal–Oxide–Semiconductor Field-Effect Transistor |

| PWM | Pulse Width Modulated |

| Si | Silicon |

| SiC | Silicon Carbide |

| TSEP | Temperature Sensitive Electrical Parameter |

References

- Zhong, X.; Wu, X.; Zhou, W.; Sheng, K. An all-SiC high-frequency boost DC–DC converter operating at 320 °C junction temperature. IEEE Trans. Power Electron. 2014, 29, 5091–5096. [Google Scholar] [CrossRef]

- Rajput, P.; Malvoni, M.; Kumar, N.M.; Sastry, O.S.; Jayakumar, A. Operational Performance and Degradation Influenced Life Cycle Environmental–Economic Metrics of mc-Si, a-Si and HIT Photovoltaic Arrays in Hot Semi-arid Climates. Sustainability 2020, 12, 1075. [Google Scholar] [CrossRef]

- Yang, S.; Xiang, D.; Bryant, A.; Mawby, P.; Ran, L.; Tavner, P. Condition Monitoring for Device Reliability in Power Electronic Converters: A Review. IEEE Trans. Power Electron. 2010, 25, 2734–2752. [Google Scholar] [CrossRef]

- Musallam, M.; Johnson, C.M. Real-time compact thermal models for health management of power electronics. IEEE Trans. Power Electron. 2010, 25, 1416–1425. [Google Scholar] [CrossRef]

- Dupont, L.; Avenas, Y.; Jeannin, P.-O. Comparison of junction temperature evaluations in a power IGBT module using an IR camera and three thermosensitive electrical parameters. IEEE Trans. Ind. Appl. 2013, 49, 1599–1608. [Google Scholar] [CrossRef]

- Liu, P.; Chen, C.; Zhang, X.; Huang, S. Online Junction Temperature Estimation Method for SiC Modules With Built-in NTC Sensor. CPSS Trans. Power Electron. Appl. 2019, 4, 94–99. [Google Scholar] [CrossRef]

- Gonzalez, J.O.; Alatise, O.; Hu, J.; Ran, L.; Mawby, P.A. An Investigation of Temperature-Sensitive Electrical Parameters for SiC Power MOSFETs. IEEE Trans. Power Electron. 2017, 32, 7954–7966. [Google Scholar] [CrossRef]

- Liao, X.; Li, H.; Hu, Y.; Huang, Z.; Song, E.; Xiao, H. Analysis of SiC MOSFET dI/dt and its temperature dependence. IET Power Electron. 2017, 11, 491–500. [Google Scholar] [CrossRef]

- Mandeya, R.; Chen, C.; Pickert, V.; Naayagi, R.T.; Ji, B. Gate–Emitter Pre-threshold Voltage as a Health-Sensitive Parameter for IGBT Chip Failure Monitoring in High-Voltage Multichip IGBT Power Modules. IEEE Trans. Power Electron. 2019, 34, 9158–9169. [Google Scholar] [CrossRef]

- Chen, C.; Pickert, V.; Al-Greer, M.; Jia, C.; Ng, C. Localization and Detection of Bond Wire Faults in Multichip IGBT Power Modules. IEEE Trans. Power Electron. 2020, 35, 7804–7815. [Google Scholar] [CrossRef]

- Chen, Z.; Boroyevich, D.; Burgos, R. Experimental parametric study of the parasitic inductance influence on MOSFET switching characteristics. In Proceedings of the 2010 International Power Electronics Conference-ECCE ASIA-, Sapporo, Japan, 21–24 June 2010; pp. 164–169. [Google Scholar]

- Lemmon, A.; Mazzola, M.S.; Gafford, J.; Parker, C. Stability Considerations for Silicon Carbide Field-Effect Transistors. IEEE Trans. Power Electron. 2012, 28, 4453–4459. [Google Scholar] [CrossRef]

- She, X.; Huang, A.Q.; Lucia, O.; Ozpineci, B. Review of Silicon Carbide Power Devices and Their Applications. IEEE Trans. Ind. Electron. 2017, 64, 8193–8205. [Google Scholar] [CrossRef]

- Stella, F.; Pellegrino, G.; Armando, E.; Dapra, D. Online Junction Temperature Estimation of SiC Power mosfets Through On-State Voltage Mapping. IEEE Trans. Ind. Appl. 2018, 54, 3453–3462. [Google Scholar] [CrossRef]

- Li, L.; Ning, P.; Zhang, N.; Wen, X. An exploration of thermo-sensitive electrical parameters to estimate the junction temperature of silicon carbide mosfet. In Proceedings of the 2017 IEEE Transportation Electrification Conference and Expo, Asia-Pacific (ITEC Asia-Pacific), Harbin, China, 7–10 August 2017; pp. 1–5. [Google Scholar] [CrossRef]

- Stella, F.; Pellegrino, G.; Armando, E.; Dapra, D. Advanced testing of SiC power MOSFET modules for electric motor drives. In Proceedings of the 2017 IEEE International Electric Machines and Drives Conference (IEMDC), Miami, FL, USA, 21–24 May 2017; pp. 1–8. [Google Scholar] [CrossRef][Green Version]

- Zhang, Q.; Yang, Y.; Zhang, P. A Novel Method for Monitoring the Junction Temperature of SiC MOSFET On-line Based on On-state Resistance. In Proceedings of the 2019 22nd International Conference on Electrical Machines and Systems (ICEMS), Harbin, China, 11–14 August 2019; pp. 1–5. [Google Scholar] [CrossRef]

- Wang, Z.; Shi, X.; Tolbert, L.; Wang, F.; Liang, Z.; Costinett, D.; Blalock, B.J. A high temperature silicon carbide mosfet power module with integrated silicon-on-insulator-based gate drive. IEEE Trans. Power Electron. 2015, 30, 1432–1445. [Google Scholar] [CrossRef]

- Hologne, M.; Bevilacqua, P.; Allard, B.; Clerc, G.; Morel, H.; Razik, H.; Barriere, A.; Karode, V.; Devadass, N. An experimental approach to the health-monitoring of a silicon carbide MOSFET-based power module. In Proceedings of the 2017 IEEE International Electric Machines and Drives Conference (IEMDC), Miami, FL, USA, 21–24 May 2017; pp. 1–7. [Google Scholar] [CrossRef]

- Griffo, A.; Wang, J.; Colombage, K.; Kamel, T. Real-Time Measurement of Temperature Sensitive Electrical Parameters in SiC Power MOSFETs. IEEE Trans. Ind. Electron. 2018, 65, 2663–2671. [Google Scholar] [CrossRef]

- Du, M.; Xin, J.; Wang, H.; Ouyang, Z.; Wei, K. Estimating Junction Temperature of SiC MOSFET Using Its Drain Current During Turn-On Transient. IEEE Trans. Electron Devices 2020, 67, 1911–1918. [Google Scholar] [CrossRef]

- Zhang, Z.; Wang, F.; Costinett, D.J.; Tolbert, L.M.; Blalock, B.J.; Wu, X. Online junction temperature monitoring using turn-off delay time for silicon carbide power devices. In Proceedings of the 2016 IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, USA, 18–22 September 2016; pp. 1–7. [Google Scholar] [CrossRef]

- Denk, M.; Bakran, M. An IGBT Driver Concept with Integrated Real-Time Junction Temperature Measurement. In Proceedings of the PCIM Europe 2014, International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 20–22 May 2014; pp. 1–8. [Google Scholar]

- Lu, X. Online Junction Temperature Estimation of SiC Power MOSFETS. School of Engineering, Newcastle University, Newcastle upon Tyne, UK. Available online: https://www.ncl.ac.uk/engineering/staff/profile/volkerpickert.html (accessed on 7 August 2021).

- Cree. C2M0080120D Silicon Carbide Power Mosfet Datasheet; 4600 Silicon Drive, Cree, Inc.: Durham, NC, USA, 2014. [Google Scholar]

- Huang, J.; Corzine, K.A.; Belkhayat, M. Small-Signal Impedance Measurement of Power-Electronics-Based AC Power Systems Using Line-to-Line Current Injection. IEEE Trans. Power Electron. 2009, 24, 445–455. [Google Scholar] [CrossRef]

- Blackburn, D. Temperature measurements of semiconductor devices—A review. In Proceedings of the Twentieth Annual IEEE Semiconductor Thermal Measurement and Management Symposium (IEEE Cat. No. 04CH37545), San Jose, CA, USA, 11 March 2004; pp. 70–80. [Google Scholar]

- Avenas, Y.; Dupont, L.; Khatir, Z. Temperature Measurement of Power Semiconductor Devices by Thermo-Sensitive Electrical Parameters—A Review. IEEE Trans. Power Electron. 2011, 27, 3081–3092. [Google Scholar] [CrossRef]

- Chemandy Electronics. Round Wire Inductance Calculator. Available online: https://chemandy.com/calculators/round-wire-inductance-calculator.htm (accessed on 30 October 2019).

- Sinha, S.; Routh, P.S.; Anno, P.D.; Castagna, J.P. Spectral decomposition of seismic data with continuous-wavelet transform. Geophysics 2005, 70, P19–P25. [Google Scholar] [CrossRef]

- Ghaderpour, E.; Pagiatakis, S.D. Least-Squares Wavelet Analysis of Unequally Spaced and Non-stationary Time Series and Its Applications. Math. Geol. 2017, 49, 819–844. [Google Scholar] [CrossRef]

- Ghaderpour, E. JUST: MATLAB and python software for change detection and time series analysis. GPS Solut. 2021, 25, 85. [Google Scholar] [CrossRef]

- IXYS. IXD_609 9-Ampere Low-Side Ultrafast MOSFET Drivers. Available online: https://www.ixysic.com/home/pdfs.nsf/www/IXD_609.pdf/$file/IXD_609.pdf (accessed on 25 October 2017).

- Coilcraft. PWB1010-1LC Wide-Band RF Transformer 1:1 0.03-250 MHz Datasheet. Available online: https://www.mouser.co.uk/ProductDetail/Coilcraft/PWB1010-1LC?qs=ZYnrCdKdyeeLEU%252bd2fZp%252bw== (accessed on 7 August 2021).

- Cree/Wolfspeed. KIT8020CRD8FF1217P-1 CREE Silicon Carbide MOSFET Evaluation Kit. Available online: https://media.digikey.com/pdf/Data%20Sheets/CREE%20Power/KIT8020CRD8FF1217P-1_UM.pdf (accessed on 6 August 2015).

| Parameter | Value |

|---|---|

| Lead resistance () | |

| Lead inductance () | |

| Internal gate resistance ()) | [24] |

| Gate-Source capacitance () | [24] |

| Single bond wire resistance () | |

| Single bond wire inductance () |

| DC Biasing Voltage | |

|---|---|

| . | |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lu, X.; Pickert, V.; Al-Greer, M.; Chen, C.; Wang, X.; Tsimenidis, C. Temperature Estimation of SiC Power Devices Using High Frequency Chirp Signals. Energies 2021, 14, 4912. https://doi.org/10.3390/en14164912

Lu X, Pickert V, Al-Greer M, Chen C, Wang X, Tsimenidis C. Temperature Estimation of SiC Power Devices Using High Frequency Chirp Signals. Energies. 2021; 14(16):4912. https://doi.org/10.3390/en14164912

Chicago/Turabian StyleLu, Xiang, Volker Pickert, Maher Al-Greer, Cuili Chen, Xiang Wang, and Charalampos Tsimenidis. 2021. "Temperature Estimation of SiC Power Devices Using High Frequency Chirp Signals" Energies 14, no. 16: 4912. https://doi.org/10.3390/en14164912

APA StyleLu, X., Pickert, V., Al-Greer, M., Chen, C., Wang, X., & Tsimenidis, C. (2021). Temperature Estimation of SiC Power Devices Using High Frequency Chirp Signals. Energies, 14(16), 4912. https://doi.org/10.3390/en14164912